# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Xilinx Generic Interface (XGI) SuperClock Module

User Guide

UG091 (v1.1) March 2, 2007

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2005–2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                         |  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 06/28/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                          |  |

| 07/28/05 | 1.0.1   | Title update.                                                                                                                                                                                                                                                    |  |

| 03/02/07 | 1.1     | <ul> <li>Updated Figure 4, page 13, Figure 5, page 13, and Figure 6, page 13 and related text.</li> <li>Added "Package Contents," page 7.</li> <li>Additional minor typographical edits.</li> <li>Updated schematics for RoHS compliance (Version C).</li> </ul> |  |

# Table of Contents

### Preface: About This Guide

| Additional Resources | . 5 |

|----------------------|-----|

| Conventions          |     |

| Typographical        |     |

| Online Document      | . 6 |

## Xilinx Generic Interface (XGI) SuperClock Module

| Package Contents          |

|---------------------------|

| Introduction              |

| Functional Description 99 |

| Power Supply Options      |

| LED Representation        |

| Master Reset              |

| <b>References</b>         |

# Preface

# About This Guide

The *Xilinx Generic Interface (XGI) SuperClock Module User Guide* provides an overview of functionality, operation, and configuration of the SuperClock module add-on board.

## **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

## **Conventions**

This document uses the following conventions. An example illustrates each convention.

#### Typographical

The following typographical conventions are used in this document:

| Convention     | Meaning or Use                                                      | Example              |  |

|----------------|---------------------------------------------------------------------|----------------------|--|

| Courier font   | Messages, prompts, and<br>program files that the system<br>displays | speed grade: - 100   |  |

| Courier bold   | Literal commands that you enter in a syntactical statement          | ngdbuild design_name |  |

| Helvetica bold | Commands that you select from a menu                                | $File \to Open$      |  |

|                | Keyboard shortcuts                                                  | Ctrl+C               |  |

| Convention                  | Meaning or Use                                                                                                        | Example                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                             | Variables in a syntax statement<br>for which you must supply<br>values                                                | ngdbuild design_name                                                                                     |

| Italic font                 | References to other manuals                                                                                           | See the <i>Development System</i><br><i>Reference Guide</i> for more<br>information.                     |

|                             | Emphasis in text                                                                                                      | If a wire is drawn so that it<br>overlaps the pin of a symbol, the<br>two nets are <i>not</i> connected. |

| Square brackets []          | An optional entry or parameter.<br>However, in bus specifications,<br>such as <b>bus</b> [7:0], they are<br>required. | <b>ngdbuild</b> [option_name]<br>design_name                                                             |

| Braces { }                  | A list of items from which you must choose one or more                                                                | lowpwr ={on off}                                                                                         |

| Vertical bar                | Separates items in a list of choices                                                                                  | lowpwr ={on off}                                                                                         |

| Vertical ellipsis<br>•<br>• | Repetitive material that has been omitted                                                                             | IOB #1: Name = QOUT'<br>IOB #2: Name = CLKIN'                                                            |

| Horizontal ellipsis         | Repetitive material that has been omitted                                                                             | allow block block_name loc1<br>loc2 locn;                                                                |

#### **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                         |  |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |  |

| Red text              | Cross-reference link to a location in another document     | See Figure 2-5 in the Virtex-II Platform FPGA User Guide.                                                       |  |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <u>http://www.xilinx.com</u><br>for the latest speed files.                                               |  |

# Xilinx Generic Interface (XGI) SuperClock Module

### **Package Contents**

- SuperClock module

- User guide and schematic

- Two 12-inch SMA-to-SMA cable assemblies

## Introduction

The SuperClock module is a highly flexible clock source designed to meet the common needs of today's applications. It covers a broad, intermediate frequency spectrum, and its versatility provides a single-source solution for most standard clock source requirements. The SuperClock module employs a Xilinx Generic Interface (XGI) connector, as used on the ML52*x* [Ref 1] and ML42*x* [Ref 2] series of RocketIO characterization platforms and others.

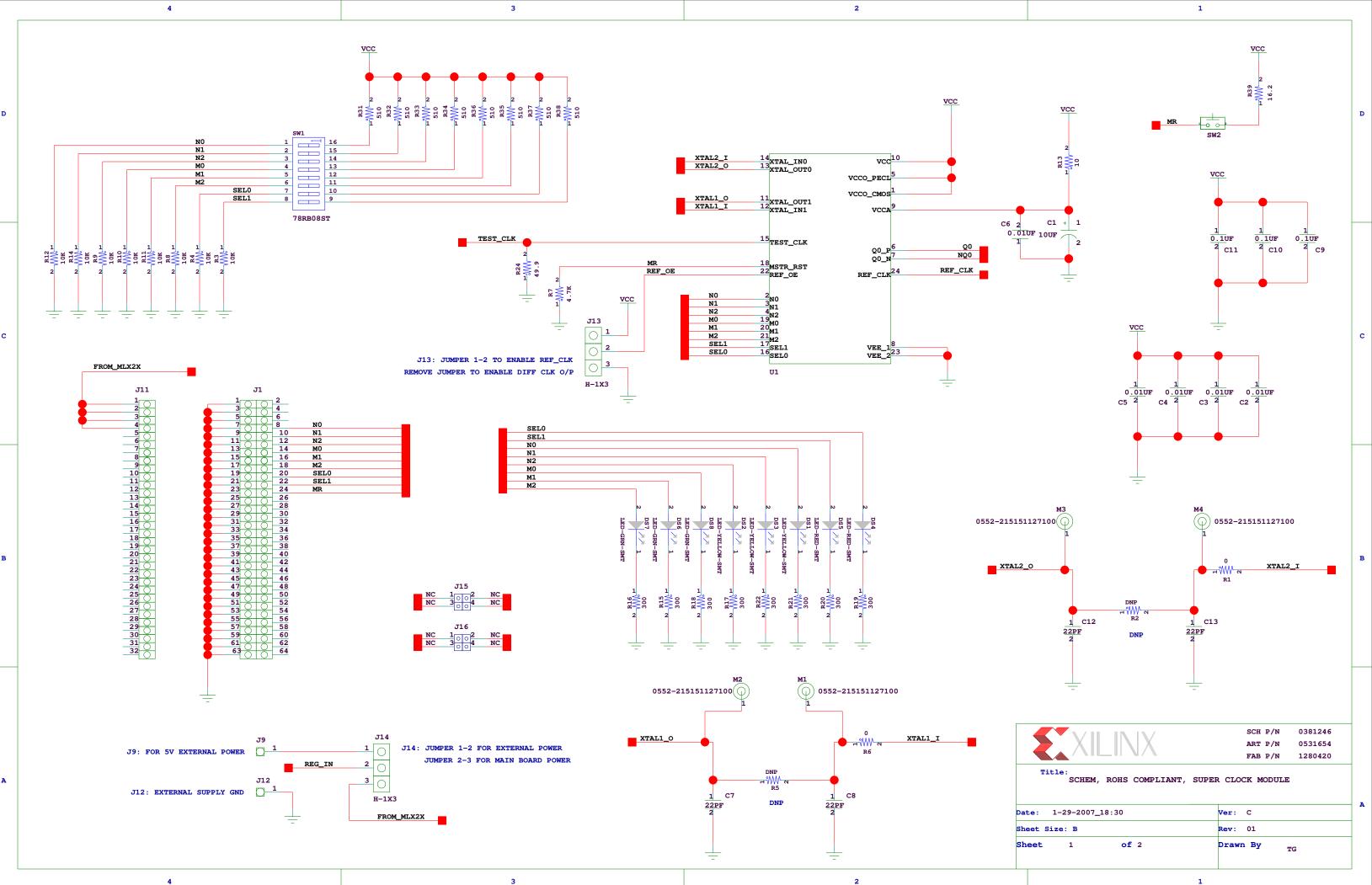

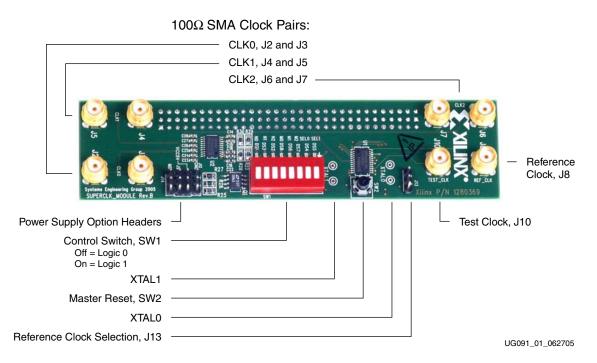

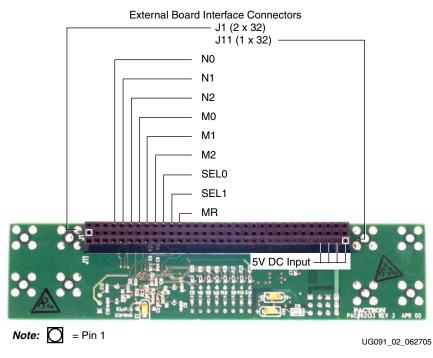

Figure 1 and Figure 2 show the front and back views of the SuperClock module.

*Note:* Images are intended for reference purposes only and might not reflect the current version of the board.

# **Functional Description**

The SuperClock module generates stable, low phase noise,  $100\Omega$  differentially terminated reference clock outputs utilizing a crystal-to-3.3V LVPECL frequency synthesizer (843001AG-22) from Integrated Device Technology (IDT) [Ref 3]. The dual-crystal interface provides a platform capable of supporting two selectable clock rate outputs with a voltage-controlled oscillator (VCO) range of 490 MHz to 640 MHz. Control is provided through onboard switch selection (SW1) or the 2 x 32 external board interface connector (J1) when connected to a host board. A list of selectable I/O associations is presented in Table 1. Power is supplied externally at 5V DC from a stand-alone supply, or optionally through the 1 x 32 external board interface connector (J1), and is regulated onboard at 3.3V DC.

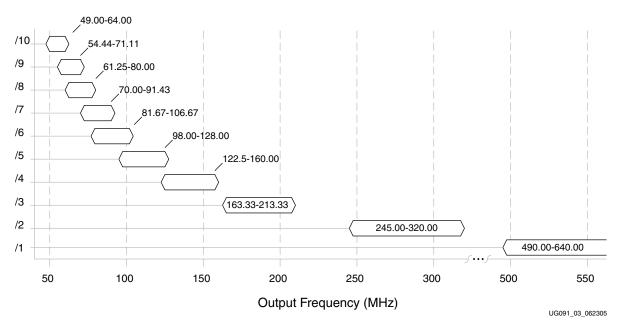

The synthesizer rate is determined using the fundamental crystal or externally supplied test clock (TEST\_CLK) frequency (Table 2, page 10) multiplied by the feedback divider setting of M0, M1, and M2 (Table 3, page 10). The output clock rate is then determined by dividing the synthesizer rate by the output divider selection of N0, N1, and N2 (Table 4, page 10). Full range output clock capability is from 49 MHz to 640 MHz (with minimal coverage gaps as shown in Figure 3, page 11). LEDs on the board indicate the corresponding configuration selections. Coupled to the output differential pair is an 8543, low skew, 1-to-4 differential fan-out buffer that is used as a clock splitter and PECL-to-LVDS driver. The fan-out buffer configuration is preselected.

| Signal<br>Name | Function                                 | Opera      | LED        |     |

|----------------|------------------------------------------|------------|------------|-----|

| N0             |                                          | SW1, pin 1 | J1, pin 8  | DS1 |

| N1             | Output divider select. Default is /4.    | SW1, pin 2 | J1, pin 10 | DS3 |

| N2             |                                          | SW1, pin 3 | J1, pin 12 | DS2 |

| M0             |                                          | SW1, pin 4 | J1, pin 14 | DS8 |

| M1             | Feedback divider select. Default is /32. | SW1, pin 5 | J1, pin 16 | DS6 |

| M2             |                                          | SW1, pin 6 | J1, pin 18 | DS7 |

| SEL0           | Input clock source select.               | SW1, pin 7 | J1, pin 20 | DS4 |

| SEL1           | input clock source select.               | SW1, pin 8 | J1, pin 22 | DS5 |

| MR             | Master reset.                            | SW2        | J1, pin 24 | N/A |

| REF_OE         | Reference clock OE.                      | J13        | N/A        | N/A |

Table 1: Selectable I/O Associations

The LVPECL frequency synthesizer receives a stable fundamental frequency from one of two populated crystal oscillators (XTAL0, XTAL1) or by using the test clock input at SMA J10. Reference clock input selection is set according to the input state of SEL0 and SEL1 as defined in Table 2.

XILINX

| Inp  | uts  | Reference   | PLL Mode |  |

|------|------|-------------|----------|--|

| SEL0 | SEL1 | Therefielde |          |  |

| 0    | 0    | XTAL0       | Active   |  |

| 1    | 0    | XTAL1       | Active   |  |

| 0    | 1    | TEST_CLK    | Active   |  |

| 1    | 1    | TEST_CLK    | Bypass   |  |

Table 2: Reference Clock Selection

The feedback divider, using the states of M0, M1, and M2 as defined in Table 3, determines the VCO output frequency. Floating inputs result in a default divisor of 32.

Table 3: M Divider Selection

|    | Inputs |    | M Divider Value | Input Frequency |         |  |

|----|--------|----|-----------------|-----------------|---------|--|

| MO | M1     | M2 |                 | Minimum         | Maximum |  |

| 0  | 0      | 0  | 18              | 27.22           | 35.56   |  |

| 1  | 0      | 0  | 22              | 22.27           | 29.09   |  |

| 0  | 1      | 0  | 24              | 20.41           | 26.67   |  |

| 1  | 1      | 0  | 25              | 19.60           | 25.60   |  |

| 0  | 0      | 1  | 32              | 15.31           | 20.00   |  |

| 1  | 0      | 1  | 40              | 12.25           | 16.00   |  |

The reference clock output is divided by the states of inputs N0, N1, and N2 as defined in Table 4. Floating inputs result in a default divisor of 4.

Table 4: N Divider Selection

|    | Inputs | N Divider Value |   |

|----|--------|-----------------|---|

| N0 | N1     | N2              |   |

| 0  | 0      | 0               | 1 |

| 1  | 0      | 0               | 2 |

| 0  | 1      | 0               | 3 |

| 1  | 1      | 0               | 4 |

| 0  | 0      | 1               | 5 |

| 1  | 0      | 1               | 6 |

|    | Inputs |    |                 |  |

|----|--------|----|-----------------|--|

| N0 | N1     | N2 | N Divider Value |  |

| 0  | 1      | 1  | 8               |  |

| 1  | 1      | 1  | 10              |  |

Table 4:

N Divider Selection (Continued)

Figure 3 shows the output frequencies supported by the SuperClock module.

Figure 3: Supported Output Frequencies

Table 5 lists examples of commonly used applications and the corresponding SuperClock module configuration to achieve them. It introduces the user to the proper metrics involved to achieve the desired output clock frequency range.

Table 5:

Common Configurations

| Input<br>Reference<br>Clock | M<br>Divider | N<br>Divider | VCO<br>(MHz) | Output<br>Frequency<br>(MHz) | Application |

|-----------------------------|--------------|--------------|--------------|------------------------------|-------------|

| 27                          | 22           | 4            | 594          | 148.5                        | HDTV        |

| 22.4                        | 25           | 4            | 560          | 140                          |             |

| 24.75                       | 24           | 4            | 594          | 148.5                        | HDTV        |

| 25                          | 24           | 3            | 600          | 200                          |             |

| 14.8351649                  | 40           | 4            | 593.4066     | 148.351649                   | HDTV        |

| 19.44                       | 32           | 4            | 622.08       | 155.52                       | SONET       |

| 19.44                       | 32           | 4            | 622.08       | 155.52                       | SONET       |

| 19.44                       | 32           | 1            | 622.08       | 622.08                       | SONET       |

| Input<br>Reference<br>Clock | M<br>Divider | N<br>Divider | VCO<br>(MHz) | Output<br>Frequency<br>(MHz) | Application              |

|-----------------------------|--------------|--------------|--------------|------------------------------|--------------------------|

| 19.44                       | 32           | 2            | 622.08       | 311.04                       | SONET                    |

| 19.53125                    | 32           | 4            | 625          | 156.25                       | 10-Gigabit Ethernet      |

| 20                          | 25           | 2            | 500          | 250                          | Ethernet, PCI Express    |

| 25                          | 25           | 2            | 625          | 312.5                        | 10-Gigabit Ethernet      |

| 25                          | 25           | 5            | 625          | 125                          | 1-Gigabit Ethernet       |

| 25                          | 24           | 6            | 600          | 100                          | PCI Express              |

| 25                          | 24           | 4            | 600          | 150                          | SATA                     |

| 26.5625                     | 24           | 6            | 637.5        | 106.25                       | Fibre Channel 1          |

| 26.5625                     | 24           | 3            | 637.5        | 212.5                        | 4-Gigabit Fibre Channel  |

| 26.5625                     | 24           | 4            | 637.5        | 159.375                      | 10-Gigabit Fibre Channel |

| 31.25                       | 18           | 3            | 562.5        | 187.5                        | 12-Gigabit Ethernet      |

| Table 5: | Common   | Configurations                        | (Continued)                             |

|----------|----------|---------------------------------------|-----------------------------------------|

| 10010 01 | •••••••• | • • • • • • • • • • • • • • • • • • • | ( ••••••••••••••••••••••••••••••••••••• |

#### Notes: User Tips

1. REF\_CLK \* M divider value = VCO frequency

2. VCO Frequency / N Divider = Output frequency

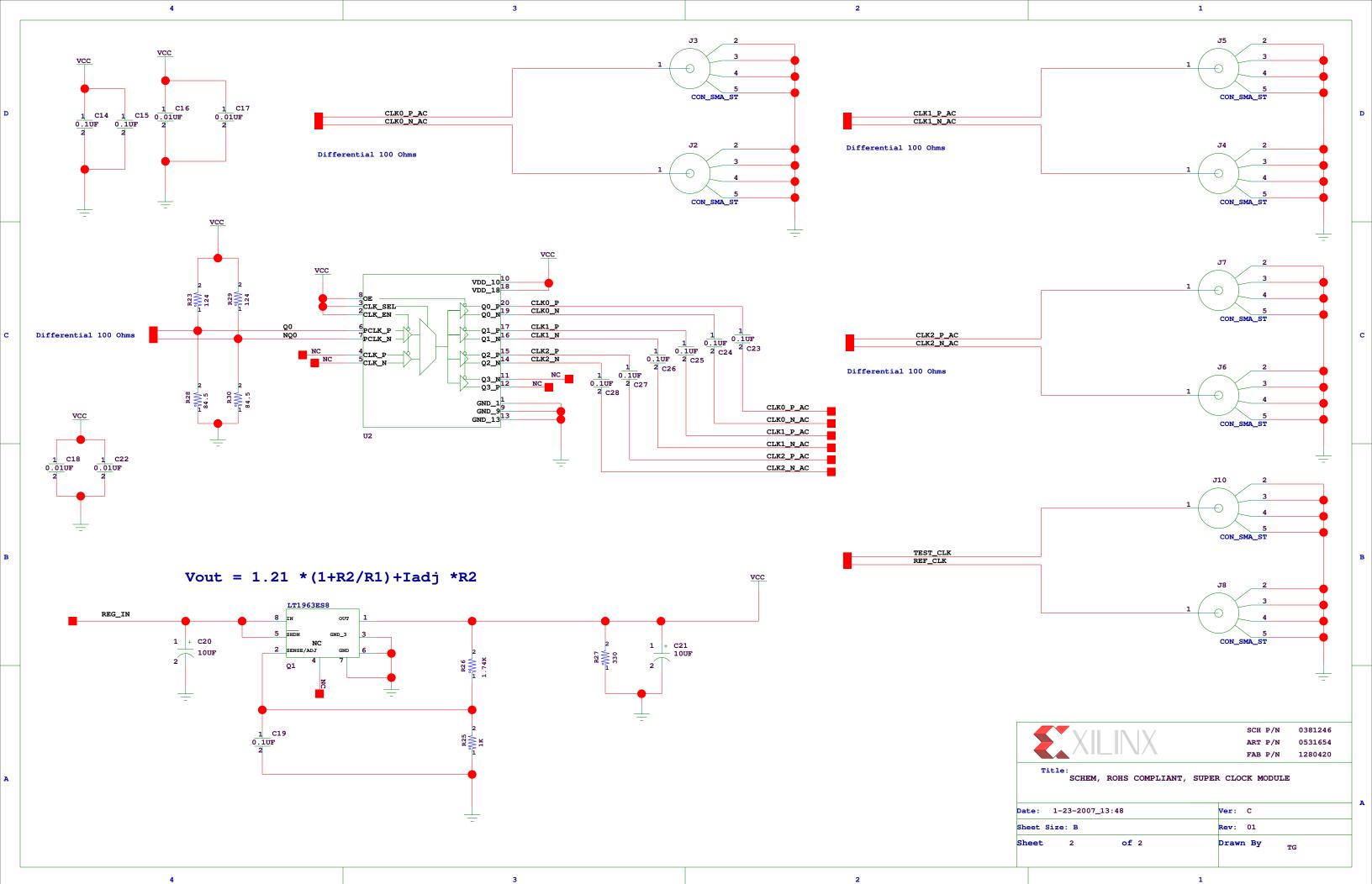

The resultant output frequency is delivered by way of differential pair Q0 and NQ0 to a 1-to-4 differential LVDS fan-out buffer. This establishes three,  $100\Omega$  differential pair outputs at CLK0, CLK1, and CLK2, and is A/C coupled to corresponding SMA pairs (J2, J3), (J4, J5), and (J6, J7), respectively.

The REF\_CLK output at SMA J8 is enabled when the reference clock output enable (REF\_OE) at J13 is pulled High or when a jumper is placed across pins 1 and 2 of J13. With REF\_OE enabled, the differential outputs are disabled. For normal operation, leave J13 open.

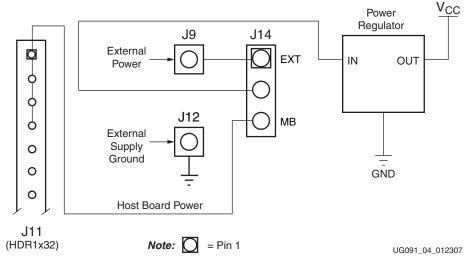

#### **Power Supply Options**

The SuperClock module runs off of 5V DC. It can be powered up either through the 1 x 32 J11 board interface connector when connected to a compatible host board or through an external power supply. Figure 4 shows a block diagram of the power circuitry on the SuperClock module.

Figure 4: Power Circuitry Block Diagram

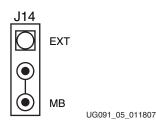

To power the SuperClock module from the  $V_{CC}$  pins of a host board through the J11 header, the jumper on J14 must connect pins 2 and 3 as shown in Figure 5.

Figure 5: Jumper Setting to Power Up from a Host Board

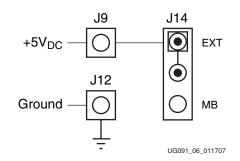

To power the SuperClock module from an external 5V power supply unit, 5V DC is connected to J9, Ground is connected to J12, and the jumper on J14 is placed across pins 1 and 2 as shown in Figure 6.

Figure 6: Jumper Setting to Power Up from an External Supply

#### **LED** Representation

Control line register status can be viewed through onboard LEDs, as shown in Table 1, page 9.

#### **Master Reset**

A master reset option is available using either the onboard momentary switch (SW2) or by using control line J1, pin 24 (MR - Master Reset). Active with a logic-High, divider functions are inoperative, and outputs Q0 and NQ0 default to a Low and High state, respectively.

### References

- 1. UG225, ML52x User Guide, Virtex-4 LXT RocketIO Characterization Platform

- 2. UG087, ML42x User Guide, Virtex-4 FX RocketIO Characterization Platform

- 3. <u>Integrated Device Technology, Inc.</u>, 843001-22 FemtoClocks Crystal-to-3.3V LVPECL Frequency Synthesizer Data Sheet