Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IA82510 <u>Asynchronous Serial Controller</u> Data Sheet

Copyright © 2008 by Innovasic Semiconductor, Inc. Published by Innovasic Semiconductor, Inc. 3737 Princeton Drive NE, Suite 130, Albuquerque, NM 87107

Intel<sup>®</sup> is a registered trademark of Intel Corporation MILES<sup>™</sup> is a trademark of Innovasic Semiconductor, Inc.

## **TABLE OF CONTENTS**

| List | of Figures                            | ∠  |

|------|---------------------------------------|----|

|      | of Tables                             |    |

| 1.   | Features                              |    |

| 2.   | Description                           |    |

| 3.   | Functional Overview                   |    |

|      | 3.1 Transmitter                       |    |

|      | 3.2 Receiver                          | 10 |

|      | 3.3 Bus Interface                     | 10 |

|      | 3.4 Register Description              | 11 |

| 4.   | Maximum Ratings and AC/DC Parameters  |    |

| 5.   | Packaging Information                 |    |

|      | 5.1 PDIP Package                      |    |

|      | 5.2 PLCC Package                      |    |

| 6.   | Innovasic Part Number Cross-Reference |    |

| 7.   | Errata                                | 18 |

|      | 7.1 Summary                           | 18 |

|      | 7.2 Detail                            |    |

| 8.   | Revision History                      | 24 |

| 9.   | For Additional Information            |    |

|      |                                       |    |

## **LIST OF FIGURES**

| Figure 1. | Package Pinout                   |   |

|-----------|----------------------------------|---|

| Figure 2. | Functional Block Diagram         | ( |

| _         | PDIP Physical Package Dimensions |   |

| _         | PLCC Physical Package Dimensions |   |

#### **LIST OF TABLES**

| Table 1. | Register Summary                                   | 1  |

|----------|----------------------------------------------------|----|

|          | Absolute Maximum Ratings                           |    |

|          | AC Parameters                                      |    |

| Table 5. | DC Parameters                                      | 14 |

| Table 6. | Innovasic Part Number Cross-Reference for the PDIP | 1  |

| Table 7. | Innovasic Part Number Cross-Reference for the PLCC | 1  |

| Table 8. | Summary of Errata                                  | 18 |

| Table 9  | Revision History                                   | 24 |

#### 1. Features

- Form, Fit, and Function Compatible with the Intel<sup>®</sup> 82510

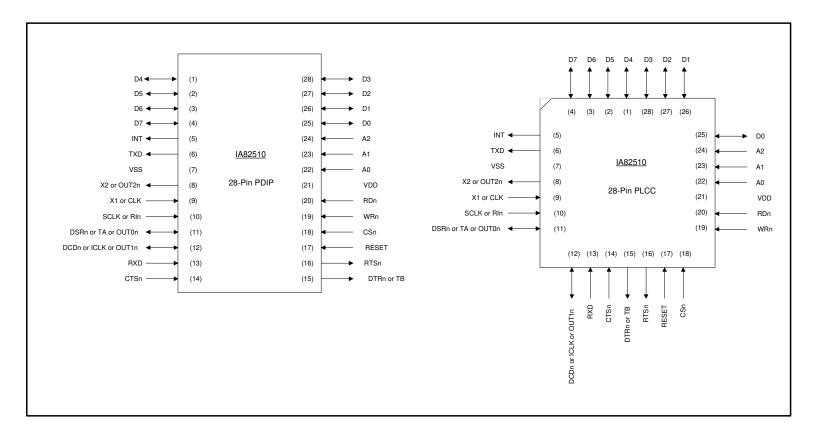

- Packaging options available: 28-Pin Plastic (PDIP) or, 28-Lead Plastic Leaded Chip Carrier (PLCC), Leaded or RoHS packages available (see Figure 1, Package Pinout)

- Asynchronous Serial Channel Operation

- Separate Transmit and Receive FIFOs with Programmable Threshold

- Programmable Baud Rate Generators up to 288K Baud

- Special Protocol Features

- Control Character Recognition

- Auto Echo and Loopback Modes

- 9-Bit Protocol Support

- 5 to 9 Bit Character Format

These devices are produced using Innovasic's Managed IC Lifetime Extension System (MILES<sup>TM</sup>). This cloning technology, which produces replacement ICs beyond simple emulations, is designed to achieve compatibility with the original device, including any "undocumented features." Please note that there may be some functional differences between the Innovasic device and the original device and customers should thoroughly test the device in system to ensure compatibility. Innovasic reports all known functional differences in the Errata section of this data sheet. Additionally, MILES<sup>TM</sup> captures the clone design in such a way that production of the clone can continue even as silicon technology advances.

Figure 1. Package Pinout

## 2. Description

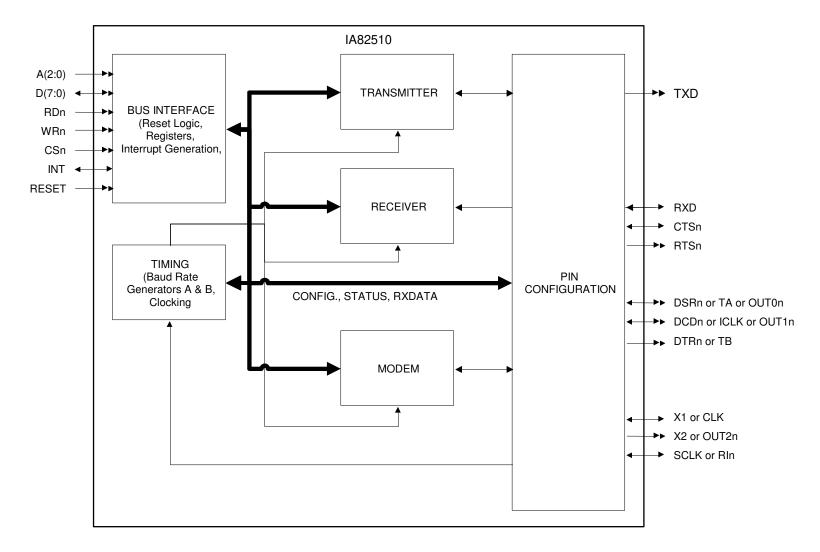

The IA82510 is an asynchronous serial controller that provides a CPU interface to one transmit and one receive channel. It is Form, Fit, and Function compatible with the Intel 82510. Configuration registers are used to control the serial channel, interrupts, and modes of operation. The CPU controls this device via address and data lines with read/write control. The CPU also uses this interface to read and write data to receive and transmit data through the serial channel. FIFOs and various serial modes can be used to help off-load the CPU from transmitting and receiving data. An interrupt line provides an indication to the CPU that the device requires servicing. The device can be configured for 8250A/16450 compatibility. See Figure 2, Functional Block Diagram.

Figure 2. Functional Block Diagram

#### **Functional Overview** 3.

#### 3.1 **Transmitter**

The Transmit function consists of a  $4 \times 11$  bit FIFO, and a Transmit Engine. The  $4 \times 11$  FIFO is configurable as any depth between one and four words inclusive. The transmit engine is responsible for reading the data out of the FIFO and placing it in the proper order on the TXD pin. The transmit engine is highly configurable to be compatible with numerous formats, including 16450 and 8250 modes of communication. Transmit Communication parameters that can be programmed include:

- Parity modes

- Stop Bits

- Character Length

- FIFO Depth

- Clocking Options

- RTS and CTS modes

For more details, see Section 3.4, Register Description.

#### 3.2 Receiver

The Receiver function consists of a  $4 \times 11$  configurable FIFO and a Receive Engine. The receive engine is responsible for sampling the data on the RXD input pin, formatting the data, and placing the data in the FIFO. The receive engine is highly configurable with parameters that include:

- Parity modes

- Stop Bits

- Character Length

- FIFO Depth

- Clocking Options

- Address Matching Options

- Control Character Detection

- RTS and CTS modes

For more details, see Section 3.4, Register Description.

#### 3.3 **Bus Interface**

The Bus Interface is a simple interface that allows a micro-processor or micro-controller to read and write the IA82510 Registers. It consists of the following I/O lines:

A0, A1, A2: 3 Bit AddressD0-D7: 8 Bit Data

RDn: Active Low Read Enable

WRn: Active Low Write Enable

CSn: Active Low Chip Select

INT: Interrupt Output RESET: Chip Reset

#### 3.4 Register Description

Table 1 presents the register summary.

**Table 1. Register Summary**

| Register | ADDR | Bank | DLAB | Mode | Default  |

|----------|------|------|------|------|----------|

| ACR0     | 111  | 00   | Χ    | R/W  | 00000000 |

| ACR1     | 101  | 10   | Χ    | R/W  | 00000000 |

| BACF     | 001  | 11   | 0    | R/W  | 00000100 |

| BAH      | 001  | 00   | 1    | R/W  | 00000000 |

| BAL      | 000  | 00   | 1    | R/W  | 00000010 |

| BANK     | 010  | Χ    | Χ    | W    | 00000000 |

| BBCF     | 011  | 11   | Χ    | R/W  | 10000100 |

| BBH      | 001  | 11   | 1    | R/W  | 00000000 |

| BBL      | 000  | 11   | 1    | R/W  | 00000101 |

| CLCF     | 000  | 11   | 0    | R/W  | 00000000 |

| FLR      | 100  | 01   | Χ    | R    | 00000000 |

| FMD      | 001  | 10   | Χ    | R/W  | 00000000 |

| GER      | 001  | 00   | 0    | R/W  | 00000000 |

| GIR_BANK | 010  | Χ    | Χ    | R    | 0000001  |

| GSR      | 111  | 01   | Χ    | R    | 00010010 |

| ICM      | 111  | 01   | Χ    | W    | N/A      |

| IMD      | 100  | 10   | Χ    | R/W  | 00001100 |

| LCR      | 011  | 00   | Χ    | R/W  | 00000000 |

| LSR      | 101  | 00   | Χ    | R/W  | 01100000 |

| MCR      | 100  | 00   | Χ    | R/W  | 00000000 |

|          | 100  | 01   | Χ    | W    |          |

| MIE      | 101  | 11   | Χ    | R/W  | 00001111 |

| MSR      | 110  | 00   | Χ    | R/W  | 00000000 |

|          | 110  | 01   | Χ    | R    |          |

| PMD      | 100  | 11   | Χ    | R/W  | 11111100 |

| RCM      | 101  | 01   | Χ    | W    | N/A      |

| RIE      | 110  | 10   | Χ    | R/W  | 00011110 |

| RMD      | 111  | 10   | Χ    | R/W  | 00000000 |

**Table 2. Register Summary** (Continued)

| Register | ADDR | Bank | DLAB | Mode | Default  |

|----------|------|------|------|------|----------|

| RST      | 101  | 01   | Χ    | R    | 00000000 |

| RXDATA   | 000  | 00   | 0    | R    | Unknown  |

|          |      | 01   | Χ    |      |          |

| RXF      | 001  | 01   | Χ    | R    | Unknown  |

| TCM      | 110  | 01   | Χ    | W    | N/A      |

| TMCR     | 011  | 01   | Χ    | W    | N/A      |

| TMD      | 011  | 10   | Χ    | R/W  | 00000000 |

| TMIE     | 110  | 11   | Χ    | R/W  | 00000000 |

| TMST     | 011  | 01   | Χ    | R    | 00110000 |

| TXDATA   | 000  | 00   | 0    | W    | N/A      |

|          |      | 01   | Χ    |      |          |

| TXF      | 001  | 01   | Χ    | W    | N/A      |

## 4. Maximum Ratings and AC/DC Parameters

Stresses beyond those listed in Table 2 may cause permanent damage to the device. Operating the device beyond the conditions indicated in the "recommended operating conditions" section is not recommended. Operation at the "absolute maximum ratings" may adversely affect device reliability.

**Table 3. Absolute Maximum Ratings**

| Parameter                       | Rating                           |  |  |

|---------------------------------|----------------------------------|--|--|

| Supply Voltage, V <sub>DD</sub> | -0.3V to +6.0V                   |  |  |

| Input Voltage, V <sub>IN</sub>  | $-0.3V$ to $V_{DD}$ $+0.3V$      |  |  |

| Input Pin Current, IIN          | ±10 mA, 25° C                    |  |  |

| Operating Temperature Range     | -40° C to +85°C                  |  |  |

| Ambient temperature under bias  | -40°C to +85°C *                 |  |  |

| Storage temperature             | -55°C to +150°C                  |  |  |

| Lead Temperature                | +300°C, 10 sec.                  |  |  |

| Power dissipation               | 155 mW, 125°C, 25MHz, 15% Toggle |  |  |

<sup>\*</sup> The input and output parametric values are directly related to ambient temperature and DC supply voltage. A temperature or supply voltage range other than those specified in the Operating Conditions above will affect these values and part performance is not guaranteed by Innovasic.

#### **Table 4. AC Parameters**

| Parameter                                | Min                        | Max                    | Notes                                                        |

|------------------------------------------|----------------------------|------------------------|--------------------------------------------------------------|

| CLK period                               | 54 ns                      | 250 ns                 | Divide by Two                                                |

| CLK period                               | 54 ns                      | 108 ns                 | No Divide by                                                 |

| CLK Low Time                             | 25 ns                      | _                      | _                                                            |

| CLK High Time                            | 25 ns                      | _                      | _                                                            |

| CLK Rise Time                            | _                          | 10 ns                  | Divide by Two                                                |

|                                          |                            |                        | Measured between 0.3 * VDD and 0.7 * VDD                     |

| CLK Fall Time                            | _                          | 10 ns                  | Divide by Two<br>Measured between 0.3 * VDD<br>and 0.7 * VDD |

| CLK Rise Time                            | _                          | 15 ns                  | No Divide by                                                 |

| CLK Fall Time                            | _                          | 15 ns                  | No Divide by                                                 |

| Crystal Frequency                        | 1 Mhz                      | 20 Mhz                 | _                                                            |

| Reset Width                              | 8 * Clock Period           | _                      | _                                                            |

| RTS/DTR Low Setup to Reset inactive      | 6 * Clock Period           | _                      | -                                                            |

| RTS/DTR Low Hold after<br>Reset inactive | _                          | Clock Period<br>–20 ns | -                                                            |

| RDn Active Width                         | 2* clock period<br>+65 ns  | _                      | -                                                            |

| Address/CSn Setup Time to RDn Active     | 7 ns                       | _                      | -                                                            |

| Address/CSn Hold after RDn Inactive      | 0 ns                       | _                      | -                                                            |

| RDn or WRn Inactive to Active Delay      | Clock Period<br>+15 ns     | _                      | -                                                            |

| Data Out Float Delay after RDn Inactive  | _                          | 40 ns                  | -                                                            |

| WRn Active Width                         | 2 * Clock Period<br>+15 ns | _                      | -                                                            |

| Address CSn Setup Time to WRn Active     | 7 ns                       | _                      | -                                                            |

| Address and CSn hold Time after WRn      | 0 ns                       | _                      | -                                                            |

| Data in Setup Time to WRn Inactive       | 90 ns                      | -                      | -                                                            |

| Data In Hold Time after WRn Inactive     | 12 ns                      | _                      | _                                                            |

| SCLK Period                              | 216 ns                     | _                      | 16x Clocking Mode                                            |

| SCLK Period                              | 3500 ns                    | _                      | 1x Clocking Mode                                             |

| RXD Setup Time to SCLK High              | 250 ns                     | _                      | _                                                            |

| RXD Hold Time after SCLK<br>High         | 250 ns                     | _                      | -                                                            |

| TXD Valid after SCLK Low                 | _                          | 170 ns                 | _                                                            |

| TXD Delay after RXD                      | _                          | 170 ns                 | Remote Loopback                                              |

#### **Table 5. DC Parameters**

| Symbol            | Parameter                    | Notes   | Min   | Max         | Unit   |

|-------------------|------------------------------|---------|-------|-------------|--------|

| V <sub>IL</sub>   | Input Low Voltage            | (1)     | -0.5  | 0.3         | V      |

| V <sub>IH1</sub>  | Input High Voltage-Cerdip    | (1)     | 2.1   | $V_{DD}+.3$ | V      |

| $V_{IH2}$         | Input High Voltage-LCC       | (2)     | 2.1   | $V_{DD}+.3$ | V      |

| $V_{OL}$          | Output Low Voltage           | (2),(8) |       | 0.4         | V      |

| V <sub>OH</sub>   | Output High Voltage          | (3),(8) | 2.4   |             | V      |

| ILI               | Input Leakage Current        | (4)     |       | ±1          | μΑ     |

| I <sub>LO</sub>   | 3-State Leakage Current      | (5)     |       | ±10         | μΑ     |

| I <sub>CC</sub>   | Power Supply Current         | (6)     |       | 1.12        | mA/MHz |

| I <sub>PU</sub>   | Strapping Pullup Resistor    | (12)    | -28.3 | -137        | μΑ     |

| I <sub>STBY</sub> | Standby Supply Current       | (9)     |       | 100         | μА     |

| I <sub>OHR</sub>  | RTSn, DTRn Strapping Current | (10)    |       | 1.92        | mA     |

| I <sub>OLR</sub>  | RTSn, DTRn Strapping Current | (11)    | N/A   |             | mA     |

| C <sub>IN</sub>   | Input Capacitance            | (7)     |       | 5           | pF     |

| C <sub>IO</sub>   | I/O Capacitance              | (7)     |       | 6           | pF     |

| $C_{XTAL}$        | X1, X2 Load                  |         |       | 6           | pF     |

#### Notes:

- 1. Does not apply to CLK/X1 pin, when configured as crystal oscillator input (X1).

- 2.  $@I_{OL} = 1.92 \text{ mA}.$

- 3.  $@I_{OH} = 1.92 \text{ mA}.$

- 4.  $0 < V_{IN} < V_{CC}$ .

- 5.  $0.4V < V_{OUT} < V_{CC} 0.4V$ . 6.  $V_{DD} = 5.5V$ ,  $V_{IL} = 0.7V$  (max),  $V_{IH} = V_{DD} 0.7V$  (min), Typ. Val = 1.12 mA/MHz (Not Tested), Ext. 1X CLK,  $I_{OL} = I_{OH} = 0$ .

- 7. Freq. = 1 MHz.

- 8. Does not apply to OUT2/X2 pin, when configured as crystal oscillator output (X2).

- 9. Freq. = 1 MHz, but input clock not running. Static IDD current is exclusive of input/output drive requirements and is measured with the clocks stopped and all inputs tied to VDD or VSS, configured to draw minimum current.

- 10. Applies only during hardware reset for clock configuration options. Strapping current for logic HIGH.

- 11. Applies only during hardware reset for clock configuration options. Strapping current for logic LOW.

- 12. Inputs (RTSn, DTRn, TB) with Pullups tested @  $V_{in} = 0.0V$ ,  $V_{DD} = 5.5V$ .

## 5. Packaging Information

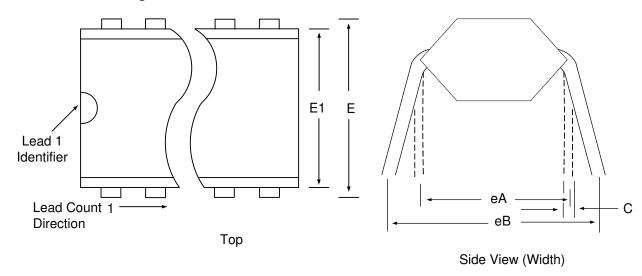

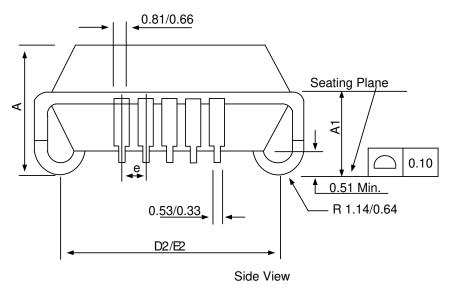

## 5.1 PDIP Package

Legend: 28 (in Inches) Symbol Min Max 0.200 Α **A1** 0.015 В 0.015 0.020 B1 0.050 0.070 С 0.008 0.012 Ε 0.580 0.610 E1 0.520 0.560 0.100 TYP е 0.580 eА eВ 0.686 0.100 Min B2 S -

Figure 3. PDIP Physical Package Dimensions

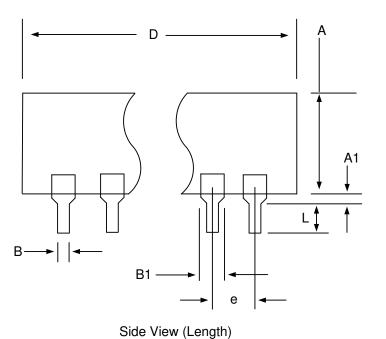

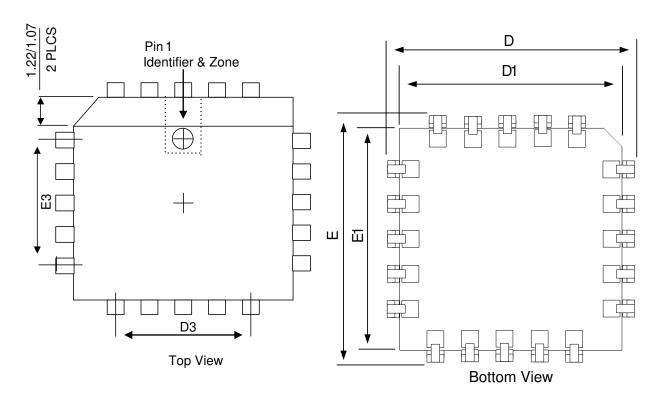

## 5.2 PLCC Package

Legend:

| Symbol | Min      | Max   |  |  |

|--------|----------|-------|--|--|

| Α      | 4.20     | 4.57  |  |  |

| A1     | 2.29     | 3.04  |  |  |

| D      | 12.32    | 12.57 |  |  |

| D1     | 11.43    | 11.58 |  |  |

| D2     | 9.91     | 10.92 |  |  |

| D3     | 7.62 BSC |       |  |  |

| е      | 1.27     | BSC   |  |  |

| Е      | 12.32    | 12.57 |  |  |

| E1     | 11.43    | 11.58 |  |  |

| E2     | 9.91     | 10.92 |  |  |

| E3     | 7.62 BSC |       |  |  |

|        | •        |       |  |  |

Note: Controlling dimension in millimeters.

Figure 4. PLCC Physical Package Dimensions

## 6. Innovasic Part Number Cross-Reference

#### Table 6. Innovasic Part Number Cross-Reference for the PDIP

| Innovasic Part Number                             | Intel Part Number | Package Type                                                               | Temperature Grades |

|---------------------------------------------------|-------------------|----------------------------------------------------------------------------|--------------------|

| IA82510-PDW28I-R-01<br>lead-free (RoHS-compliant) |                   | 28-Pin <u>Plastic Dual In-</u><br>Line <u>Package</u> (PDIP)<br>(600 mils) | Industrial         |

#### Table 7. Innovasic Part Number Cross-Reference for the PLCC

| Innovasic Part Number                         | Intel Part Number | Package Type                                         | Temperature Grades |

|-----------------------------------------------|-------------------|------------------------------------------------------|--------------------|

| IA82510PLC28IR2<br>lead-free (RoHS-compliant) |                   | 28-Lead <u>Plastic Leaded</u><br>Chip Carrier (PLCC) | Industrial         |

#### 7. Errata

The following errata are known problems with the IA82510. This is inclusive of all package types and environment grades. A workaround to the identified problem has been provided where possible. All errata listed in production Version 00 have been fixed in Version 01 of the device unless otherwise noted. Version 02 is the result of a migration to a new fab process to ensure long-term supply. It retains the same functionality and errata as the Version 01 device.

#### 7.1 Summary

Table 8 presents a summary of errata.

**Table 8. Summary of Errata**

| Errata<br>No. | Problem                                                                                                                                     | Ver. 00 | Ver. 01 | Ver. 02 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

| 1             | Scrambled data during boot code shuts down UART, however device works for application code.                                                 | Exists  | Fixed   | Fixed   |

| 2             | Device does not operate at 8 MHz in divide-by-one mode.                                                                                     | Exists  | Fixed   | Fixed   |

| 3             | Setting CLCF to x30, which effectively generates the TX clock from the incoming SCLK signal, kills all transmits.                           | Exists  | Fixed   | Fixed   |

| 4             | Receiving streamed data has many framing errors and corrupt data when connected to some modems.                                             | Exists  | Fixed   | Fixed   |

| 5             | Transmission of streamed data does not return interrupt.                                                                                    | Exists  | Fixed   | Fixed   |

| 6             | Receiving streamed data has many framing errors at fast baud rates (divisor=6) through bad modem lines.                                     | Exists  | Fixed   | Fixed   |

| 7             | Difficulty starting oscillator with crystal.                                                                                                | Exists  | Fixed   | Fixed   |

| 8             | Intermittent and temperature sensitive crystal oscillator operation when cycling power.                                                     | Exists  | Fixed   | Fixed   |

| 9             | Auto-acknowledge of interrupts via writing of LSR does not work.                                                                            | Exists  | Fixed   | Fixed   |

| 10            | ICM Status Clear command does not clear LSR/RST overrun error.                                                                              | Exists  | Fixed   | Fixed   |

| 11            | In semi-automatic/uLAN mode, the RX FIFO is only opened when an address character matches the ACR1 or ACR0 registers (like full auto mode). | Exists  | Fixed   | Fixed   |

**Table 7. Summary of Errata** (Continued)

| Errata<br>No. | Problem                                                                                              | Ver. 00 | Ver. 01 | Ver. 02 |

|---------------|------------------------------------------------------------------------------------------------------|---------|---------|---------|

| 12            | Device fails to reset interrupt signal in auto acknowledge mode when character is read from RX FIFO. | Exists  | Fixed   | Fixed   |

| 13            | RX FIFO locks up unexpectedly just after configuration and before starting reception.                | NA      | Exists  | Exists  |

| 14            | Unreliable transmits in AUTO TX mode.                                                                | NA      | Exists  | Exists  |

#### 7.2 Detail

#### Errata No. 1

**Problem:** Scrambled data during boot code shuts down UART, however device works for application code.

**Description:** The RX FIFO is locked, configuration of all registers is done, then the RX FIFO is unlocked just before entering loopback mode in both boot and application code before normal operations begin. Boot code additionally does a blind block read of all registers before normal operations including two reads from the unwritten RX Data FIFO. RX unlock command is inadvertently incrementing the write pointer. For boot code, the two reads of RX data cause the read/write pointers to be permanently out of sync. For application code, the pointers end up synched to the same location, only because the code waits for four characters before reading. This ends up causing an RX overrun, but to our favor because the pointers are now synched.

**Workaround:** Execute a "Flush RX FIFO" command (via RCM register) after configuration and block read is complete.

#### Errata No. 2

**Problem:** Device does not operate at 8 MHz in divide-by-one mode.

**Description:** System testing revealed this operational deficiency.

**Workaround:** Switch to divide-by-two mode using 2X clock input.

**Problem:** Setting CLCF to x30, which effectively generates the TX clock from the incoming SCLK signal, kills all transmits.

**Description:** Configuration of PMD inadvertently set so RI function is selected instead of SCLK function. Original Intel device allows SCLK through anyway, IA82510 suppresses it.

**Workaround:** Set correct configuration for PMD allows TX clock generation.

Errata No. 4

**Problem:** Receiving streamed data has many framing errors and corrupt data when connected to some modems.

**Description:** Shortened stop bit followed immediately by next start bit does not correctly detect that start bit.

**Workaround:** Configure external modem to transmit two stop bits.

Errata No. 5

**Problem:** Transmission of streamed data does not return interrupt.

**Description:** Stray read of GIR sets TX FIFO interrupt hold logic, but this logic does not reset when GER[1] is de-asserted.

**Workaround:** Reset logic with write to TX data or avoid stray reads of GIR.

Errata No. 6

**Problem:** Receiving streamed data has many framing errors at fast baud rates (divisor=6) through bad modem lines.

**Description:** DPLL is not robust for RXD signal with more than 1/16 bit time of variation.

Workaround: None.

**Problem:** Difficulty starting oscillator with crystal.

**Description:** No internal feedback resistor between X1 and X2.

**Workaround:** Install external 1-10Mohm resistor.

Errata No. 8

**Problem:** Intermittent and temperature sensitive crystal oscillator operation when cycling power.

**Description:** Strapping state elements apparently transparent latches instead of flip flops. If flip flop powers up to wrong state, crystal oscillator is disabled while reset is active. OK after first reset following power-up.

Workaround: None.

Errata No. 9

**Problem:** Auto-acknowledge of interrupts via writing of LSR does not work.

**Description:** Writing LSR directly sets/resets bits 4 through 0. Also writing 0 to LSR(0) - RX FIFO - clears the RX FIFO level as seen by FLR. Writing zero to any other LSR bits clears the corresponding LSR/RST flag, but also corrupts the FIFO location the write pointer is set to, then increments both the write and read pointers.

**Workaround:** Use other means to service interrupts, such as read of RST or RXD.

Errata No. 10

**Problem:** ICM Status Clear command does not clear LSR/RST overrun error.

**Description:** ICM Status Clear command should clear everything in RST/LSR, MSR, and TMST except RST/LSR(0). Overrun error was missed.

**Workaround:** Use other means to service interrupts.

**Problem:** In semi-automatic/uLAN mode, the RX FIFO is only opened when an address character matches the ACR1 or ACR0 registers (like full auto mode).

**Description:** In semi-auto mode, the RX FIFO should open on any address character.

Workaround: None.

#### Errata No. 12

**Problem:** Device fails to reset interrupt signal in auto acknowledge mode when character is read from RX FIFO.

**Description:** RD strobe is outside the CS enable, which is outside of the Intel datasheet, but apparently still works in the Intel device. Such a bus cycle allows the read data out, but fails to generate the necessary internal strobe to change pointers. The same problem is found on write accesses.

**Workaround:** Force bus interface to bracket RD strobe inside the CS enable.

#### Errata No. 13

**Problem:** RX FIFO locks up unexpectedly just after configuration and before starting reception.

**Description:** An RCM command is executed with data of xB8. This is an "enable RX", "flush RX machine", "flush RX FIFO", and "lock RX FIFO" command done in a single instruction. The "flush RX machine" should unlock the RX FIFO, creating a conflict with the simultaneous "lock RX FIFO" command. The original Intel device apparently ignores or gives the "lock RX FIFO" command lower priority in this case. The IA82510 has this priority reversed. Apparently, the application software in this case expected the "lock RX FIFO" command to fail.

**Workaround:** Do not execute a "flush RX FIFO" and "lock RX FIFO" command simultaneously. Break up into separate RCM commands.

**Problem:** Unreliable transmits in AUTO TX mode.

**Description:** Many systems use the RTS output to activate the line transceiver. When the Transmit Mode field in the TMD register is set to semi-auto or automatic mode, RTS is controlled by the TX state machine. On the first character, RTS asserts at the same time as the start bit on the TXD output, whereas the original Intel device asserts RTS a full bit time before assertion of the start bit on TXD. At full temperature range, the width of the start bit can be altered to the point of confusing the downstream receiver.

Workaround: Change firmware to Manual TX mode to control RTS vs. start of character.

# 8. Revision History

Table 9 presents the sequence of revisions to document IA211001219.

**Table 9. Revision History**

| Date              | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page(s) |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| August 19, 2008   | 03       | Corrected control number and reformatted some elements to meet publication standards.                                                                                                                                                                                                                                                                                                                                                                                                                                | NA      |

| October 8, 2008   | 04       | Corrected part number on cover page, enlarged package pinout and functional block diagram figures, corrected trademark references (p. 2), changed "pin" to "lead" in PLCC package pinout figure, changed "lead" to "pin" in PDIP physical page dimensions figure and part number table, formatted part cross-reference table and errata to meet publication standards, changed part number from "IA82510-PLC28I-R-01" to "IA82510PLC28IR2" to reflect current inventory, added "For Additional Information" chapter. | All     |

| February 25, 2011 | 05       | Removed packaging options to support the elimination of SnPb lead plating options.                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17      |

| January 9, 2015   | 06       | Modified chip compatibility statement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6       |

#### 9. For Additional Information

The IA82510 is a "plug-and-play" drop-in replacement for the original IC. This data sheet documents all necessary engineering information about the IA82510 including functional and I/O descriptions, electrical characteristics, and applicable timing.

The Innovasic Support Team is continually planning and creating tools for your use. Visit <a href="http://www.Innovasic.com">http://www.Innovasic.com</a> for up-to-date documentation and software. Our goal is to provide timely, complete, accurate, useful, and easy-to-understand information. Please feel free to contact our experts at Innovasic at any time with suggestions, comments, or questions.

Innovasic Support Team 3737 Princeton NE Suite 130 Albuquerque, NM 87107

(505) 883-5263 Fax: (505) 883-5477

Toll Free: (888) 824-4184 E-mail: support@innovasic.com

Website: http://www.Innovasic.com