# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

CoolSET™ F3R80 ICE3AR1580VJZ

Off-Line SMPS Current Mode Controller with integrated 800V CoolMOS<sup>™</sup> and Startup cell (input OVP & frequency jitter) in DIP-7

Data Sheet V2.0 2014-01-20

Power Management & Multimarket

Edition 2014-01-20 Published by Infineon Technologies AG, 81726 Munich, Germany. © 2014 Infineon Technologies AG All Rights Reserved.

#### LEGAL DISCLAIMER

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE INFINEON TECHNOLOGIES COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE INFINEON TECHNOLOGIES COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. INFINEON TECHNOLOGIES HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## Trademarks of Infineon Technologies AG

AURIX<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CIPURSE<sup>™</sup>, EconoPACK<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CORECONTROL<sup>™</sup>, CROSSAVE<sup>™</sup>, DAVE<sup>™</sup>, DI-POL<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPIM<sup>™</sup>, EconoPACK<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, I<sup>2</sup>RF<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, POWERCODE<sup>™</sup>; PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PRO-SIL<sup>™</sup>, PROFET<sup>™</sup>, RASIC<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SINDRION<sup>™</sup>, SIPMOS<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>.

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL<sup>™</sup>, REALVIEW<sup>™</sup>, THUMB<sup>™</sup>, µVision<sup>™</sup> of ARM Limited, UK. AUTOSAR<sup>™</sup> is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO<sup>™</sup> of Microsoft Corporation. FlexRay<sup>™</sup> is licensed by FlexRay Consortium. HYPERTERMINAL<sup>™</sup> of Hilgraeve Incorporated. IEC<sup>™</sup> of Commission Electrotechnique Internationale. IrDA<sup>™</sup> of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS<sup>™</sup> of Sun Microsystems, Inc. SPANSION<sup>™</sup> of Spansion LLC Ltd. Symbian<sup>™</sup> of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ<sup>™</sup> of Texas Instruments Incorporated. VXWORKS<sup>™</sup>, WIND RIVER<sup>™</sup> of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-11-11

# **Revision History**

| Date Version Changed By |     | Change Description |                          |

|-------------------------|-----|--------------------|--------------------------|

| 20 Jan 2014             | 2.0 |                    | Release of first version |

|                         |     |                    |                          |

|                         |     |                    |                          |

|                         |     |                    |                          |

# We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of our documentation. Please send your proposal (including a reference to this document title/number) to:

# ctdd@infineon.com

# **Table of Contents**

| Revision H | listory                                                                                                            | 4  |

|------------|--------------------------------------------------------------------------------------------------------------------|----|

| Table of C | ontents                                                                                                            | 5  |

| Off-Line S | MPS Current Mode Controller with integrated 800V CoolMOS™ and Startup cell (input OVP & frequency jitter) in DIP-7 |    |

| 1          | Pin Configuration and Functionality                                                                                | 8  |

| 1.1        | Pin Configuration with PG-DIP-7                                                                                    |    |

| 1.2        | Pin Functionality                                                                                                  |    |

| 2          | Representative Block Diagram                                                                                       | 10 |

| 3          | Functional Description                                                                                             | 11 |

| 3.1        | Introduction                                                                                                       | 11 |

| 3.2        | Power Management                                                                                                   | 11 |

| 3.3        | Improved Current Mode                                                                                              | 12 |

| 3.3.1      | PWM-OP                                                                                                             | 14 |

| 3.3.2      | PWM-Comparator                                                                                                     | 14 |

| 3.4        | Startup Phase                                                                                                      | 14 |

| 3.5        | PWM Section                                                                                                        | 17 |

| 3.5.1      | Oscillator                                                                                                         | 17 |

| 3.5.2      | PWM-Latch FF1                                                                                                      | 17 |

| 3.5.3      | Gate Driver                                                                                                        | 17 |

| 3.6        | Current Limiting                                                                                                   | 18 |

| 3.6.1      | Leading Edge Blanking                                                                                              | 19 |

| 3.6.2      | Propagation Delay Compensation (patented)                                                                          | 19 |

| 3.7        | Control Unit                                                                                                       | 20 |

| 3.7.1      | Basic and Extendable Blanking Mode                                                                                 | 20 |

| 3.7.2      | Active Burst Mode (patented)                                                                                       | 21 |

| 3.7.2.1    | Selectable burst entry level                                                                                       | 22 |

| 3.7.2.2    | Entering Active Burst Mode                                                                                         | 23 |

| 3.7.2.3    | Working in Active Burst Mode                                                                                       | 23 |

| 3.7.2.4    | Leaving Active Burst Mode                                                                                          | 23 |

| 3.7.3      | Protection Modes                                                                                                   | 24 |

| 3.7.3.1    | Vcc OVP, OTP and Vcc under voltage                                                                                 |    |

| 3.7.3.2    | Over load, open loop protection                                                                                    | 26 |

| 3.7.4      | Input OVP Mode                                                                                                     |    |

| 3.7.5      | Action sequence at BV pin                                                                                          |    |

| 4          | Electrical Characteristics                                                                                         |    |

| 4.1        | Absolute Maximum Ratings                                                                                           |    |

| 4.2        | Operating Range                                                                                                    |    |

| 4.3        | Characteristics                                                                                                    |    |

| 4.3.1      | Supply Section                                                                                                     |    |

| 4.3.2      | Internal Voltage Reference                                                                                         |    |

| 4.3.3      | PWM Section                                                                                                        |    |

| 4.3.4      | Soft Start time                                                                                                    |    |

| 4.3.5      | Control Unit                                                                                                       |    |

| 4.3.6      | Current Limiting                                                                                                   | 34 |

| 4.3.7 | CoolMOS™ Section                               | 34 |

|-------|------------------------------------------------|----|

| 5     | Typical Controller Performance Characteristics | 35 |

| 6     | CoolMOS™ Performance Characteristics           | 36 |

| 7     | Input Power Curve                              | 38 |

| 8     | Outline Dimension                              | 39 |

| 9     | Marking                                        | 40 |

| 10    | Schematic for recommended PCB layout           | 41 |

# Off-Line SMPS Current Mode Controller with integrated 800V CoolMOS<sup>™</sup> and Startup cell (input OVP & frequency jitter) in DIP-7

# **Product Highlights**

- 800V avalanche rugged CoolMOS™ with startup cell

- Active Burst Mode to reach the lowest Standby Power <100mW

- Selectable entry and exit burst mode level

- · Adjustable blanking Window for high load jumps

- Frequency jitter and soft driving for low EMI

- Adjustable input OVP

- Auto Restart protection for over load, over temperature and over voltage

- Low Operating temperature down to -40°C

- Pb-free lead plating, halogen free mold compound, RoHS compliant

#### Features

- 800V avalanche rugged CoolMOS™ with Startup Cell

- Active Burst Mode for lowest Standby Power

- Selectable entry and exit burst mode level

- 100kHz internally fixed switching frequency with jittering feature

- Auto Restart Protection for Over load, Open Loop, VCC Under voltage & Over voltage and Over temperature

- Over temperature protection with 50°C hysteresis

- Built-in 10ms Soft Start

- Built-in 20ms and extendable blanking time for short duration peak power

- Propagation delay compensation for both maximum load and burst mode

- Adjustable input OVP

- Overall tolerance of Current Limiting < ±5%</li>

- BiCMOS technology for low power consumption and wide VCC voltage range

- Soft gate drive with 50Ω turn on resistor

#### Description

The ICE3AR1580VJZ is a modified version of ICE3ARxx80JZ (CoolSET<sup>™</sup>-F3R 800V) in DIP-7 package. It adds in the input OVP feature but removes the brownout feature and external protection enable feature. In summary, the ICE3AR1580VJZ is a device running at 100kHz, implemented with input OVP feature, installed with 800V MOSFET with startup cell and housed in DIP-7 package. It provides good voltage margin of MOSFET, lowest standby power, selectable burst level, reduced output ripple during burst mode, robust protection with input OVP feature, accurate maximum power control for both maximum power and burst power, low EMI with frequency jittering and soft gate drive, built-in and flexible protections, etc.

#### Applications

- Adapter/Charger

- Blue Ray/DVD player, Set-top Box, Digital Photo Frame

- Auxiliary power supply for Server, PC, Printer, TV, Home theater/Audio System, White Goods, etc

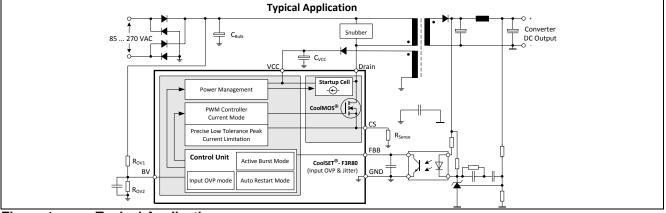

#### Figure 1: Typical Application

| Туре          | Package  | Marking    | V <sub>DS</sub> | Fosc   | R <sub>DSon</sub> <sup>1)</sup> | <b>230VAC ±15%</b> <sup>2)</sup> | 85-265 VAC <sup>2)</sup> |

|---------------|----------|------------|-----------------|--------|---------------------------------|----------------------------------|--------------------------|

| ICE3AR1580VJZ | PG-DIP-7 | 3AR1580VJZ | 800V            | 100kHz | 1.5                             | 57W                              | 36W                      |

1) typ @ T=25°C

2) Calculated maximum input power rating at T\_a=50°C, Ti=125°C and without copper area as heat sink.

**Pin Configuration and Functionality**

# **1** Pin Configuration and Functionality

# 1.1 Pin Configuration with PG-DIP-7

| Pin | Symbol | Function                            |  |

|-----|--------|-------------------------------------|--|

| 1   | BV     | extended Blanking time & input OVP  |  |

| 2   | FBB    | Feedback & Burst entry/exit control |  |

| 3   | CS     | Current Sense/ 800V CoolMOS™ Source |  |

| 4   | n.c.   | not connected                       |  |

| 5   | Drain  | 800V CoolMOS™ Drain                 |  |

| 6   | -      | (no pin)                            |  |

| 7   | VCC    | Controller Supply Voltage           |  |

| 8   | GND    | Controller Ground                   |  |

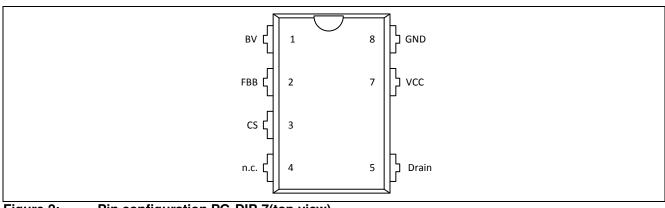

Figure 2: Pin configuration PG-DIP-7(top view)

# 1.2 Pin Functionality

# BV (extended Blanking time & input OVP)

The BV pin combines the functions of input OVP and extendable blanking time for over load protection. The input OVP feature is to stop the switching pulse when the input line voltage is higher than the  $V_{\text{OVP}\_ref}$  after the resistor divider (Refer to Figure 3). The extendable blanking time function is to extend the built-in 20 ms blanking time for over load protection by adding an external capacitor to ground.

# FBB (Feedback & Burst entry control)

The FBB pin combines the feedback function and the burst entry/exit control. The regulation information is provided by the FBB pin to the internal Protection Unit and the internal PWM-Comparator to control the duty cycle. The FBB-signal is the only control signal in case of light load at the Active Burst Mode. The burst entry/ exit control provides an access to select the entry/exit burst mode level.

#### CS (Current Sense)

The Current Sense pin senses the voltage developed on the shunt resistor inserted in the source of the integrated CoolMOS<sup>™</sup>. If CS reaches the internal threshold of the Current Limit Comparator, the Driver output is immediately switched off. Furthermore the current information is provided for the PWM comparator to realize the Current Mode.

## Pin Configuration and Functionality

# Drain (Drain of integrated CoolMOS™)

Pin Drain is the connection to the Drain of the integrated CoolMOS<sup>™</sup>.

# VCC (Power Supply)

The VCC pin is the positive supply of the IC. The operating range is between 10.5V and 25V.

## GND (Ground)

The GND pin is the ground of the controller.

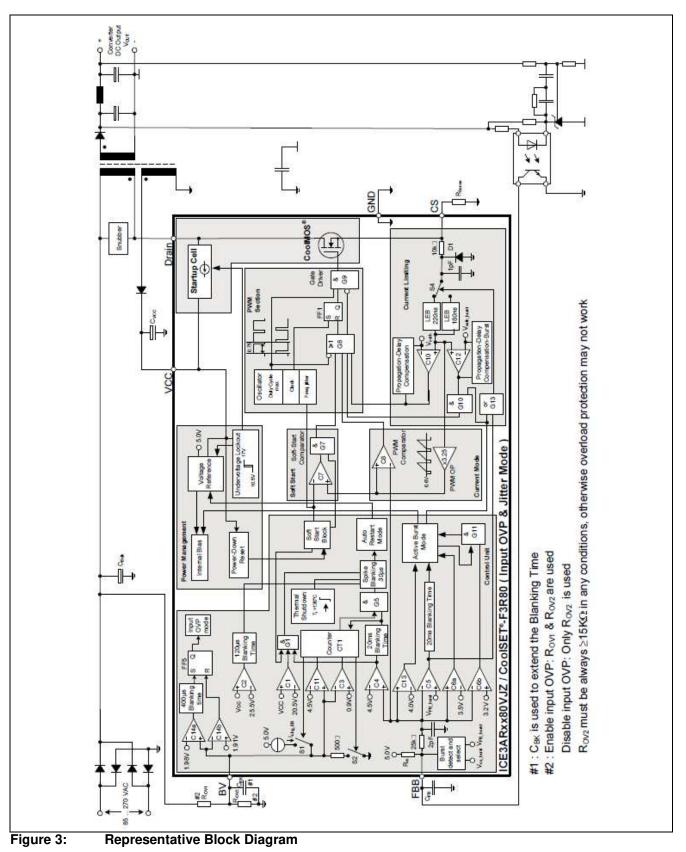

**Representative Block Diagram**

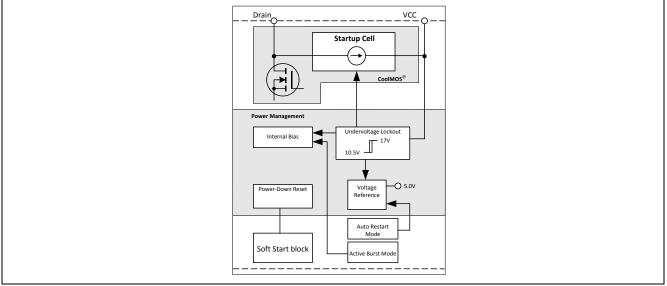

# 2 Representative Block Diagram

# 3 Functional Description

All values which are used in the functional description are typical values. For calculating the worst cases the min/max values which can be found in section 4 Electrical Characteristics have to be considered.

# 3.1 Introduction

ICE3AR1580VJZ input OVP and jitter 800V version is the modified version of the ICE3ARxx80JZ. It is particular good for high voltage margin low power SMPS application such as white goods, auxiliary power supply for PC and server. The major characteristics are that the IC is developed with 800V CoolMOS<sup>™</sup> with start up cell, having adjustable input OVP feature, running at 100kHz switching frequency and packed in DIP-7 package.

The familiar features are BiCMOS technology to reduce power consumption and increase the Vcc voltage range, cycle by cycle current mode control, built-in 10ms soft start to reduce the stress of switching elements during start up, built-in 20ms and extended blanking time for short period of peak power before entering protection, active burst mode for lowest standby power and propagation delay compensation for close power limit between high line and low line, frequency jittering for low EMI performance, the built-in auto-restart mode protections for open loop, over load, Vcc OVP, Vcc under voltage, etc.

Besides, it also includes narrowing the feedback voltage swing from 0.5V to 0.3V during burst mode so that the output voltage ripple can be reduced by 40%, reduction of the fast voltage fall time of the MOSFET by increasing the soft turn-on time and addition of  $50\Omega$  turn-on resistor, faster start up time by optimizing the Vcc capacitor to 10uF and over temperature protection with  $50^{\circ}$ C hysteresis.

Furthermore, it includes adjustable input OVP to suppress the abnormal input stress to damage the device, selectable entry and exit burst mode for smaller entry/exit power to burst mode or even no burst mode is possible and the propagation delay compensation for burst mode so that the entry/exit burst mode power is close between high line and low line.

In summary, the ICE3AR1580VJZ provides good voltage margin of MOSFET, lowest standby power, flexible burst level, reduced output ripple during burst mode, robust for abnormal input stress with input OVP feature, accurate power limit for both maximum power and burst power, low EMI with frequency jittering and soft gate drive, built-in and flexible protections, etc. Therefore, ICE3AR1580VJZ is a complete solution for the low power SMPS application typically for white goods.

# 3.2 Power Management

#### Figure 4: Power Management

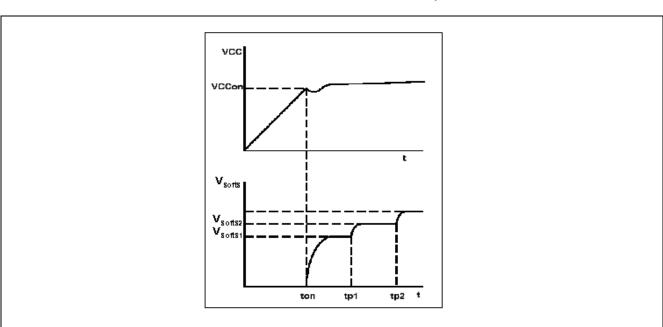

The Undervoltage Lockout monitors the external supply voltage  $V_{VCC}$ . When the SMPS is plugged to the main line the internal Startup Cell is biased and starts to charge the external capacitor  $C_{VCC}$  which is connected to the VCC pin. This

VCC charge current is controlled to 0.9mA by the Startup Cell. When the  $V_{VCC}$  exceeds the on-threshold  $V_{CCon}$ =17V the bias circuit are switched on. Then the Startup Cell is switched off by the Undervoltage Lockout and therefore no power losses present due to the connection of the Startup Cell to the Drain voltage. To avoid uncontrolled ringing at switch-on, a hysteresis start up voltage is implemented. The switch-off of the controller can only take place when Vvcc falls below 10.5V after normal operation was entered. The maximum current consumption before the controller is activated is about 200 $\mu$ A.

When  $V_{VCC}$  falls below the off-threshold  $V_{CCoff}=10.5V$ , the bias circuit is switched off and the soft start counter is reset. Thus it ensures that at every startup cycle the soft start starts at zero.

The internal bias circuit is switched off if Auto Restart Mode is entered. The current consumption is then reduced to 320µA.

Once the malfunction condition is removed, this block will then turn back on. The recovery from Auto Restart Mode does not require re-cycling the AC line.

When Active Burst Mode is entered, the internal Bias is switched off most of the time but the Voltage Reference is kept alive in order to reduce the current consumption below 620µA.

# 3.3 Improved Current Mode

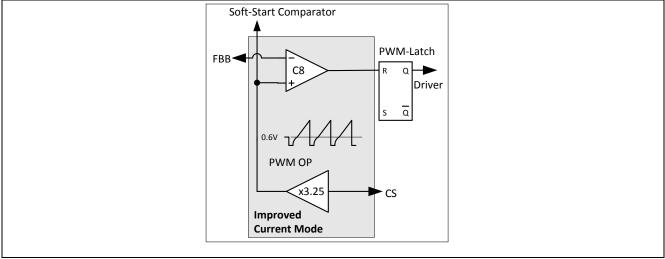

# Figure 5: Current Mode

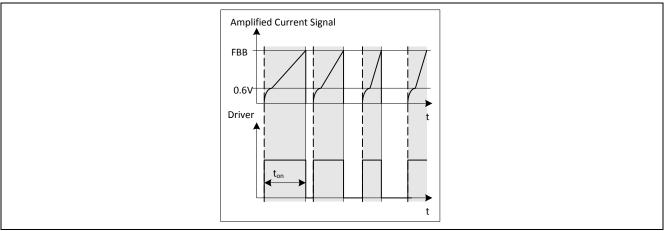

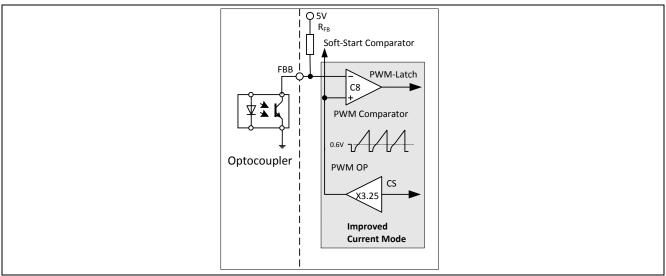

Current Mode means the duty cycle is controlled by the slope of the primary current. This is done by comparing the FBB signal with the amplified current sense signal.

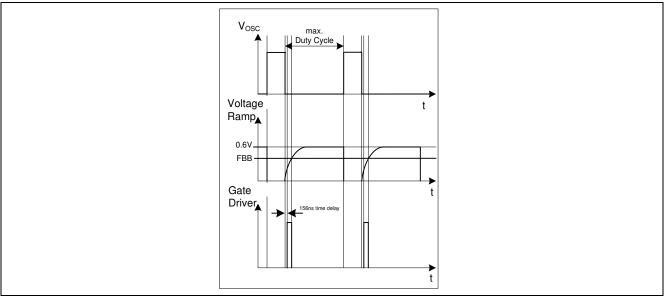

Figure 6: Pulse Width Modulation

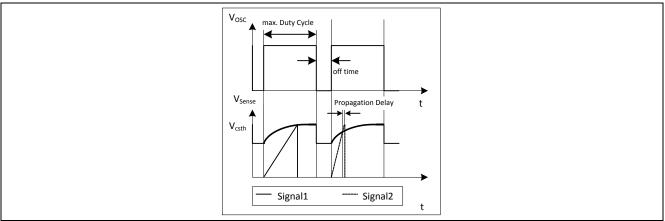

In case the amplified current sense signal exceeds the FBB signal the on-time  $t_{on}$  of the driver is finished by resetting the PWM-Latch (Figure 6).

#### Data Sheet

The primary current is sensed by the external series resistor  $R_{Sense}$  inserted in the source of the integrated CoolMOS<sup>TM</sup>. By means of Current Mode regulation, the secondary output voltage is insensitive to the line variations. The current waveform slope will change with the line variation, which controls the duty cycle.

The external  $R_{Sense}$  allows an individual adjustment of the maximum source current of the integrated CoolMOS<sup>TM</sup>.

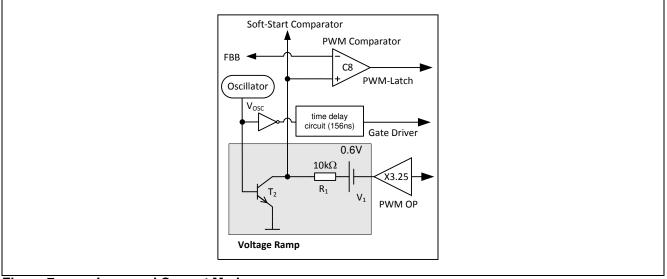

To improve the Current Mode during light load conditions the amplified current ramp of the PWM-OP is superimposed on a voltage ramp, which is built by the switch T2, the voltage source V1 and a resistor R1 (see Figure 7). Every time the oscillator shuts down for maximum duty cycle limitation the switch T2 is closed by  $V_{OSC.}$  When the oscillator triggers the Gate Driver, T2 is opened so that the voltage ramp can start.

#### Figure 7: Improved Current Mode

In case of light load the amplified current ramp is too small to ensure a stable regulation. In that case the Voltage Ramp is a well defined signal for the comparison with the FBB-signal. The duty cycle is then controlled by the slope of the Voltage Ramp.

By means of the time delay circuit which is triggered by the inverted Vosc signal, the Gate Driver is switched-off until it reaches approximately 156ns delay time (Figure 8). It allows the duty cycle to be reduced continuously till 0% by decreasing VFBB below that threshold.

Figure 8: Light Load Conditions

# 3.3.1 **PWM-OP**

The input of the PWM-OP is applied over the internal leading edge blanking to the external sense resistor  $R_{Sense}$  connected to pin CS.  $R_{Sense}$  converts the source current into a sense voltage. The sense voltage is amplified with a gain of 3.25 by PWM OP. The output of the PWM-OP is connected to the voltage source V<sub>1</sub>. The voltage ramp with the superimposed amplified current signal is fed into the positive inputs of the PWM-Comparator C8 and the Soft-Start-Comparator (Figure 9).

# 3.3.2 **PWM-Comparator**

The PWM-Comparator compares the sensed current signal of the integrated CoolMOS<sup>TM</sup> with the feedback signal V<sub>FBB</sub> (Figure 9). V<sub>FBB</sub> is created by an external optocoupler or external transistor in combination with the internal pull-up resistor R<sub>FB</sub> and provides the load information of the feedback circuitry. When the amplified current signal of the integrated CoolMOS<sup>TM</sup> exceeds the signal V<sub>FBB</sub> the PWM-Comparator switches off the Gate Driver.

# 3.4 Startup Phase

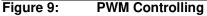

Figure 10: Soft Start

In the Startup Phase, the IC provides a Soft Start period to control the primary current by means of a duty cycle limitation. The Soft Start function is a built-in function and it is controlled by an internal counter.

Figure 11: Soft Start Phase

When the  $V_{VCC}$  exceeds the on-threshold voltage, the IC starts the Soft Start mode (Figure 10).

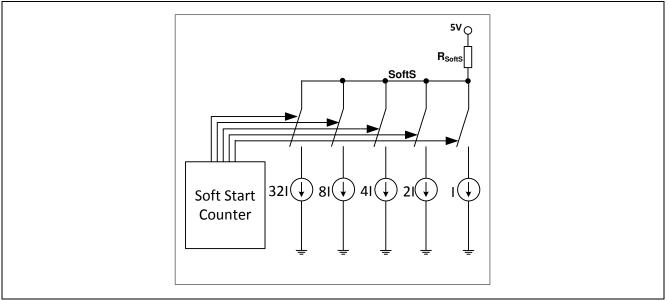

The function is realized by an internal Soft Start resistor, a current sink and a counter. And the amplitude of the current sink is controlled by the counter (Figure 12).

Figure 12: Soft Start Circuit

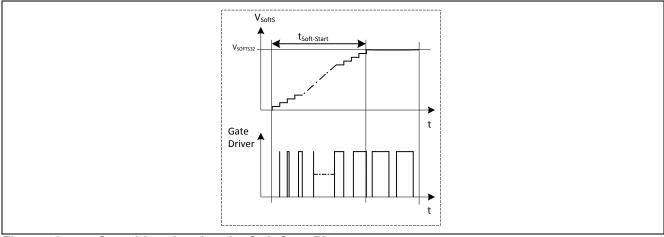

After the IC is switched on, the  $V_{SoftS}$  voltage is controlled such that the voltage is increased step-wisely (32 steps) with the increase of the counts. The Soft Start counter would send a signal to the current sink control in every 300µs such that the current sink decrease gradually and the duty ratio of the gate drive increases gradually. The Soft Start will be finished in 10ms ( $t_{Soft-Start}$ ) after the IC is switched on. At the end of the Soft Start period, the current sink is switched off.

Within the soft start period, the duty cycle is increasing from zero to maximum gradually (see Figure 13).

Figure 13: Gate drive signal under Soft-Start Phase

In addition to Start-Up, Soft-Start is also activated at each restart attempt during Auto Restart.

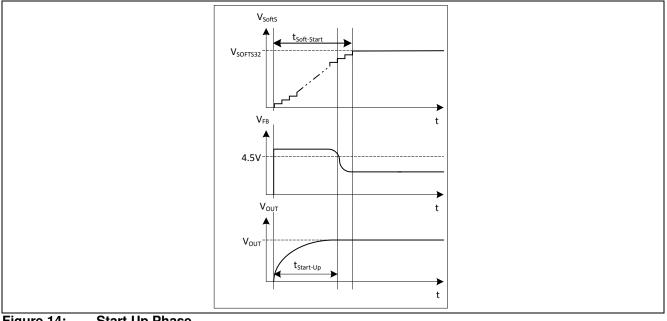

Figure 14: Start Up Phase

The Start-Up time  $t_{\text{Start-Up}}$  before the converter output voltage  $V_{\text{OUT}}$  is settled, must be shorter than the Soft-Start Phase  $t_{\text{Soft-Start}}$  (Figure 14). By means of Soft-Start there is an effective minimization of current and voltage stresses on the integrated CoolMOS<sup>TM</sup>, the clamp circuit and the output rectifier and it helps to prevent saturation of the transformer during Start-Up.

## 3.5 **PWM Section**

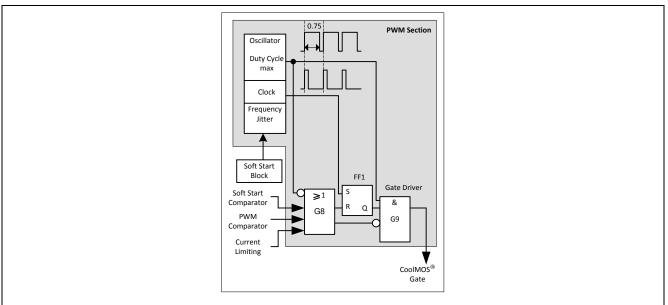

Figure 15: PWM Section Block

# 3.5.1 Oscillator

The oscillator generates a fixed frequency of 100kHz with frequency jittering of  $\pm$ 4% (which is  $\pm$ 4KHz) at a jittering period of 4ms.

A capacitor, a current source and current sink which determine the frequency are integrated. The charging and discharging current of the implemented oscillator capacitor are internally trimmed in order to achieve a very accurate switching frequency. The ratio of controlled charge to discharge current is adjusted to reach a maximum duty cycle limitation of  $D_{max}=0.75$ .

Once the Soft Start period is over and when the IC goes into normal operating mode, the switching frequency of the clock is varied by the control signal from the Soft Start block. Then the switching frequency is varied in range of 100kHz ± 4KHz at period of 4ms.

# 3.5.2 PWM-Latch FF1

The output of the oscillator block provides continuous pulse to the PWM-Latch which turns on/off the integrated CoolMOS<sup>™</sup>. After the PWM-Latch is set, it is reset by the PWM comparator, the Soft Start comparator or the Current -Limit comparator. When it is in reset mode, the output of the driver is shut down immediately.

# 3.5.3 Gate Driver

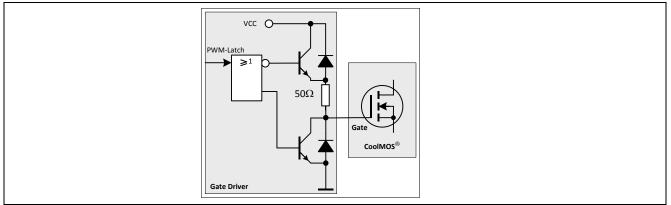

Figure 16: Gate Driver

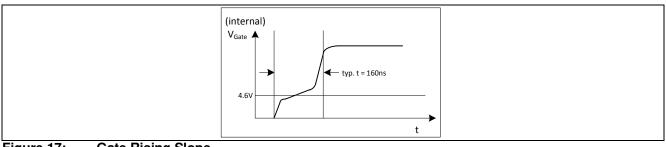

The driver-stage is optimized to minimize EMI and to provide high circuit efficiency. This is done by reducing the switch on slope when exceeding the integrated CoolMOS<sup>TM</sup> threshold. This is achieved by a slope control of the rising edge at the driver's output (Figure 17) and adding a 50 $\Omega$  gate turn on resistor (Figure 15). Thus the leading switch on spike is minimized.

Figure 17: Gate Rising Slope

Furthermore the driver circuit is designed to eliminate cross conduction of the output stage.

During power up, when VCC is below the undervoltage lockout threshold  $V_{VCCoff}$ , the output of the Gate Driver is set to low in order to disable power transfer to the secondary side.

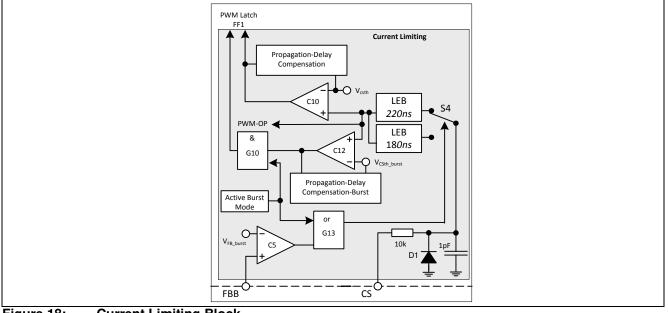

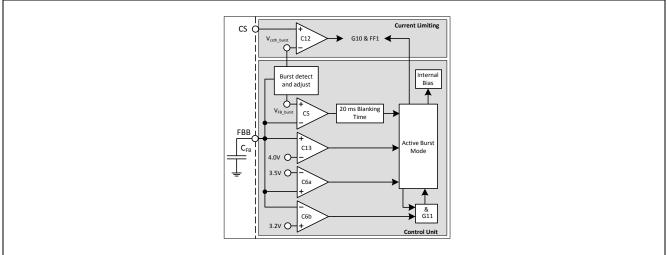

# 3.6 Current Limiting

Figure 18: Current Limiting Block

There is a cycle by cycle peak current limiting operation realized by the Current-Limit comparator C10. The source current of the integrated CoolMOS<sup>TM</sup> is sensed via an external sense resistor  $R_{Sense}$ . By means of  $R_{Sense}$  the source current is transformed to a sense voltage  $V_{Sense}$  which is fed into the pin CS. If the voltage  $V_{Sense}$  exceeds the internal threshold voltage  $V_{coth}$ , the comparator C10 immediately turns off the gate drive by resetting the PWM Latch FF1.

A Propagation Delay Compensation is added to support the immediate shut down of the integrated CoolMOS<sup>™</sup> with very short propagation delay. Thus the influence of the AC input voltage on the maximum output power can be reduced to minimal. This compensation applies to both the peak load and burst mode.

In order to prevent the current limit from distortions caused by leading edge spikes, a Leading Edge Blanking (LEB) is integrated in the current sense path for the comparators C10, C12 and the PWM-OP.

The output of comparator C12 is activated by the Gate G10 if Active Burst Mode is entered. When it is activated, the current limiting is reduced to  $V_{csth\_burst}$ . This voltage level determines the maximum power level in Active Burst Mode.

# 3.6.1 Leading Edge Blanking

Figure 19: Leading Edge Blanking

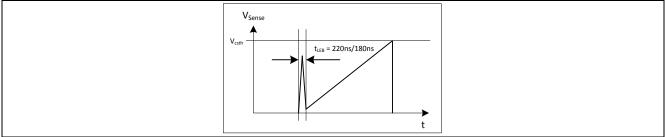

Whenever the integrated CoolMOS<sup>TM</sup> is switched on, a leading edge spike is generated due to the primary-side capacitances and reverse recovery time of the secondary-side rectifier. This spike can cause the gate drive to switch off unintentionally. In order to avoid a premature termination of the switching pulse, this spike is blanked out with a time constant of  $t_{LEB} = 220$ ns for normal load and  $t_{LEB} = 180$ ns for burst mode.

# 3.6.2 **Propagation Delay Compensation (patented)**

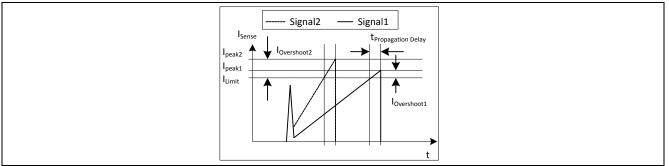

In case of overcurrent detection, there is always propagation delay to switch off the integrated CoolMOS<sup>TM</sup>. An overshoot of the peak current <sub>lpeak</sub> is induced to the delay, which depends on the ratio of dl/ dt of the peak current (Figure 20).

Figure 20: Current Limiting

The overshoot of Signal2 is larger than of Signal1 due to the steeper rising waveform. This change in the slope is depending on the AC input voltage. Propagation Delay Compensation is integrated to reduce the overshoot due to dl/dt of the rising primary current. Thus the propagation delay time between exceeding the current sense threshold <sub>Vcsth</sub> and the switching off of the integrated CoolMOS<sup>™</sup> is compensated over temperature within a wide input range. Current Limiting is then very accurate.

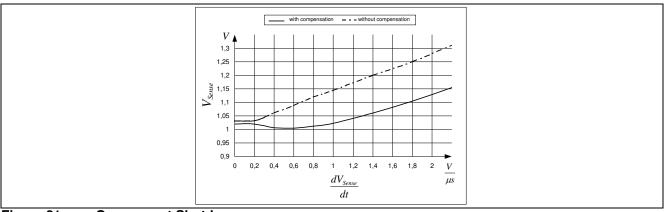

For example,  $I_{peak} = 0.5A$  with  $R_{Sense} = 2$ . The current sense threshold is set to a static voltage level  $V_{csth}=1V$  without Propagation Delay Compensation. A current ramp of dl/dt = 0.4A/µs, or dV\_{Sense}/dt = 0.8V/µs, and a propagation delay time of  $t_{Propagation Delay} = 180$ ns leads to an  $I_{peak}$  overshoot of 14.4%. With the propagation delay compensation, the overshoot is only around 2% (Figure 21).

Figure 21: Overcurrent Shutdown

The Propagation Delay Compensation is realized by means of a dynamic threshold voltage  $V_{csth}$  (Figure 22). In case of a steeper slope the switch off of the driver is earlier to compensate the delay.

Figure 22: Dynamic Voltage Threshold Vcsth

Similarly, the same concept of propagation delay compensation is also implemented in burst mode with reduced level,  $V_{csth\_burst}$  (Figure 18). With this implementation, the entry and exit burst mode power can be very close between low line and high line input voltage.

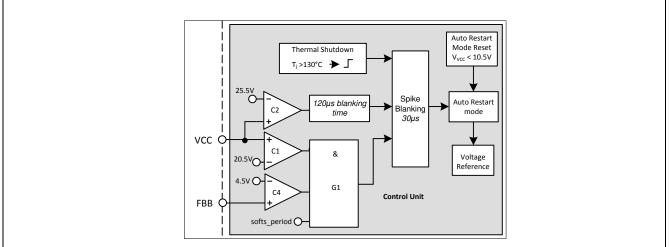

# 3.7 Control Unit

The Control Unit contains the functions for Active Burst Mode and Auto Restart Mode. The Active Burst Mode and the Auto Restart Mode both have 20ms internal blanking time. For the over load Auto Restart Mode, the 20ms blanking time can be further extended by adding an external capacitor at BV pin. With the blanking time, the IC avoids entering into those two modes accidentally. That buffer time is very useful for the application which works in short duration of peak power occasionally.

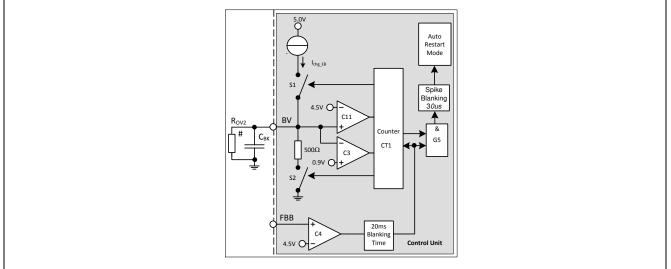

# 3.7.1 Basic and Extendable Blanking Mode

#### Figure 23: Basic and Extendable Blanking Mode

There are 2 kinds of Blanking mode; basic mode and the extendable mode. The basic mode is a built-in 20ms blanking time while the extendable mode can extend this blanking time by connecting an external capacitor to the BV pin. For the extendable mode, the gate G5 remains blocked even though the 20ms blanking time is reached. After reaching the 20ms blanking time the counter is activated and the switch S1 is turned on to charge the voltage of BV pin by the constant current source,  $I_{chg EB}$ . When the voltage of BV pin hits 4.5V, which is sensed by

comparator C11, the counter will increase the counter by 1. Then it switches off the switch S1 and turns on the switch S2. The voltage at BV pin will be discharged through a  $500\Omega$  resistor. When the voltage drops to 0.9V which is sensed by comparator C3, the switch S2 will be turned off and the switch S1 will be turned on. Then the constant current I<sub>chg\_EB</sub> will charge the C<sub>BK</sub> capacitor again. When the voltage at BV hits 4.5V which is sensed by comparator C11, the counter will increase the count to 2. The process repeats until it reaches total count of 256 (Figure 24). Then the counter will release a high output signal. When the AND gate G5 detects both high signals at the inputs, it will activate the 30µs spike blanking circuit and finally the auto-restart mode will be activated.

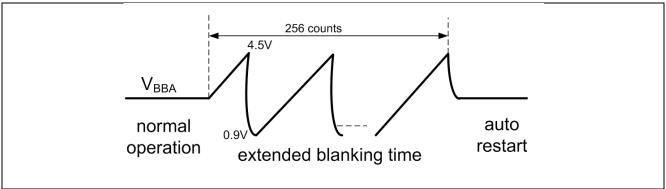

Figure 24: Waveform at extended blanking time

For example, if  $C_{BK}=0.1\mu$ F,  $I_{chg\_EB}=720\mu$ A,  $R_{OV2}=15K\Omega$ ,  $I_{chg\_EB}'=I_{chg\_EB}-(4.5V+0.9V)/(2^*R_{OV2})=540 \mu$ A

Extended blanking time =  $256^{*}(C_{BK}^{*}(4.5V-0.9V)/I_{chg EB}^{*}+C_{BK}^{*}500^{*}ln(4.5/0.9)) = 192ms$

Total blanking time = 20ms+192 = 212ms

where  $I_{chg EB}$ '=net charging current to  $C_{BK}$

Note: The above calculation does not include the effect of the input OVP circuit where there is extra biasing current flowing from the input. That means the extended blanking time will be shortened with the line voltage change if input OVP circuit is implemented.

# 3.7.2 Active Burst Mode (patented)

To increase the efficiency of the system at light load, the most effective way is to operate at burst mode. Starting from CoolSET<sup>™</sup> F3, the IC has been employing the active burst mode and it can achieve the lowest standby power. ICE3AR1580VJZ adopts the same concept with some more innovative improvements to the feature. It includes the adjustable entry burst level, close power control between high line and low line and the smaller output ripple during burst mode.

Most of the burst mode design in the market will provide a fixed entry burst mode level which is a ratio to the maximum power of the design. ICE3AR1580VJZ provides a more flexible level which can be selected externally. The provision also includes not entering burst mode.

Propagation delay is the major contributor for the power control variation for DCM flyback converter. It is proved to be effective in the maximum power control. ICE3AR1580VJZ also apply the same concept in the burst mode. Therefore, the entry and exit burst mode power is also finely controlled during burst mode.

The feedback control swing during burst mode will affect the output ripple voltage directly. ICE3AR1580VJZ reduces the swing from 0.5V to 0.3V. Therefore, it would have around 40% improvement for the output ripple.

# Figure 25: Active Burst Mode

The Active Burst Mode is located in the Control Unit. Figure 24 shows the related components.

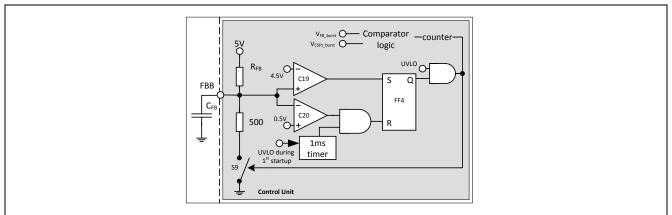

# 3.7.2.1 Selectable burst entry level

The burst mode entry level can be selected by changing the different capacitor  $C_{FB}$  at FBB pin. There are 4 levels to be selected with different capacitor which are targeted for 10%, 6.67%, 4.38% and 0% of the maximum input power. At the same time, the exit burst levels are targeted to 20%, 13.3%, 9.6% and 0% of the maximum power accordingly. The corresponding capacitance range is from 6.8nF to 100pF. The below table is the recommended capacitance range for the entry and exit level with the  $C_{FB}$  capacitor.

| CFB                  | Entry le     | vel       | Exit level   |             |  |

|----------------------|--------------|-----------|--------------|-------------|--|

|                      | % of Pin_max | VFB_burst | % of Pin_max | Vcsth_burst |  |

| >=6.8nF (5%,X7R)     | 10%          | 1.60V     | 20%          | 0.45V       |  |

| 1nF~2.2nF (1%,COG)   | 6.67%        | 1.42V     | 13.3%        | 0.37V       |  |

| 220pF~470pF (1%,COG) | 4.38%        | 1.27V     | 9.6%         | 0.31V       |  |

| <=100pF (1%,COG)     | 0%           | never     | 0%           | always      |  |

The selection is at the 1st 1ms of the UVLO "ON" (Vcc > 17V) during the 1st start up but it does not detect in the subsequent re-start due to auto-restart protection. In case there is protection triggered such as input OVP before starts up, the detection will be held until the protection is removed. When the Vcc reaches the UVLO "ON" in the 1st start up, the capacitor  $C_{FB}$  at FBB pin is charged by a 5V voltage source through the R<sub>FB</sub> resistor. When the voltage at FBB pin hits 4.5V, the FF4 will be set, the switch S9 is turned "ON" and the counter will increase by 1. Then the C<sub>FB</sub> is discharged through a 500 $\alpha$  resistor. After reaching 0.5V, the FF4 is reset and the switch S9 is turned "OFF". Then the C<sub>FB</sub> capacitor is charged by the 5V voltage source again until it reaches 4.5V. The process repeats until the end of 1ms. Then the detection is ended. After that, the total number of count in the counter is compared and the V<sub>FB-burst</sub> and the V<sub>cs</sub> burst are selected accordingly (Figure 26)

# 3.7.2.2 Entering Active Burst Mode

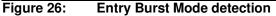

The FBB signal is kept monitoring by the comparator C5 (Figure 25). During normal operation, the internal blanking time counter is reset to 0. When FBB signal falls below  $V_{FB\_burst}$ , it starts to count. When the counter reaches 20ms and FBB signal is still below  $V_{FB\_burst}$ , the system enters the Active Burst Mode. This time window prevents a sudden entering into the Active Burst Mode due to large load jumps.

After entering Active Burst Mode, a burst flag is set and the internal bias is switched off in order to reduce the current consumption of the IC to about 620µA.

It needs the application to enforce the VCC voltage above the Undervoltage Lockout level of 10.5V such that the Startup Cell will not be switched on accidentally. Or otherwise the power loss will increase drastically. The minimum VCC level during Active Burst Mode depends on the load condition and the application. The lowest VCC level is reached at no load condition.

# 3.7.2.3 Working in Active Burst Mode

After entering the Active Burst Mode, the FBB voltage rises as  $V_{OUT}$  starts to decrease, which is due to the inactive PWM section. The comparator C6a monitors the FBB signal. If the voltage level is larger than 3.5V, the internal circuit will be activated; the Internal Bias circuit resumes and starts to provide switching pulse. In Active Burst Mode the gate G10 is released and the current limit is reduced to  $V_{csth_burst}$  (Figure 3 and Figure 25). In one hand, it can reduce the conduction loss and the other hand, it can reduce the audible noise. If the load at  $V_{OUT}$  is still kept unchanged, the FBB signal will drop to 3.2V. At this level the C6b deactivates the internal circuit again by switching off the Internal Bias. The gate G11 is active again as the burst flag is set after entering Active Burst Mode. In Active Burst Mode, the FBB voltage is changing like a saw tooth between 3.2V and 3.5V (Figure 27).

# 3.7.2.4 Leaving Active Burst Mode

The FBB voltage will increase immediately if there is a high load jump. This is observed by the comparator C13 (Figure 25). Since the current limit is reduced to 31%~45% of the maximum current during active burst mode, it needs a certain load jump to raise the FBB signal to exceed 4.0V. At that time the comparator C5 resets the Active Burst Mode control which in turn blocks the comparator C12 by the gate G10. The maximum current can then be resumed to stabilize V<sub>OUT</sub>.

# CoolSET™ F3R80 ICE3AR1580VJZ

## **Functional Description**

Figure 27: Signals in Active Burst Mode

# 3.7.3 Protection Modes

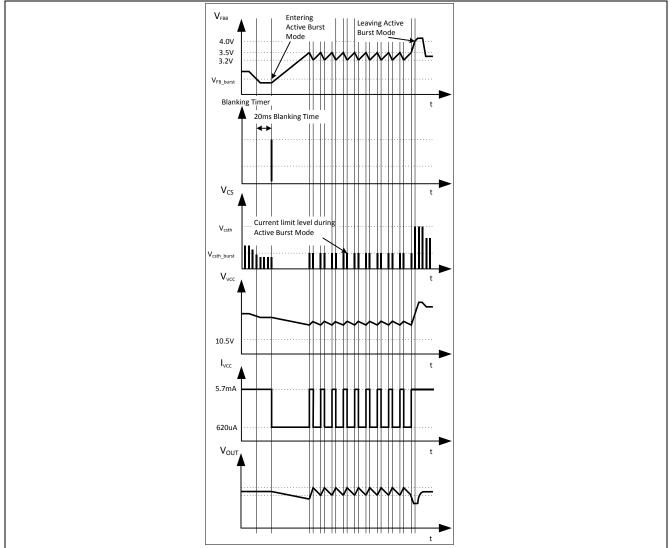

The IC provides Auto Restart mode as the major protection feature. Auto Restart mode can prevent the SMPS from destructive states. There are 3 kinds of auto restart mode; normal auto restart mode, odd skip auto restart mode and non switch auto restart mode. Odd skip auto restart mode is that there is no detect of fault and no switching pulse for the odd number restart cycle. At the even number of restart cycle the fault detect and soft start switching pulses maintained. If the fault persists, it would continue the auto-restart mode. However, if the fault is removed, it can release to normal operation only at the even number auto restart cycle (Figure 28).

Figure 28: Odd skip auto restart waveform

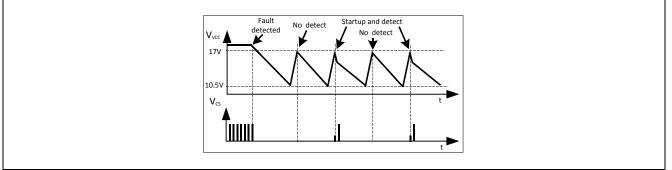

Non switch auto restart mode is similar to odd skip auto restart mode except the start up switching pulses are also suppressed at the even number of the restart cycle. The detection of fault still remains at the even number of the restart cycle. When the fault is removed, the IC will resume to normal operation at the even number of the restart cycle (Figure 29).

Figure 29: Non switch auto restart waveform

The main purpose of the odd skip auto restart is to extend the restart time such that the power loss during auto restart protection can be reduced. This feature is particularly good for smaller Vcc capacitor where the restart time is shorter.

The following table lists the possible system failures and the corresponding protection modes.

| VCC Over voltage (1) | Odd skip Auto Restart Mode   |  |  |

|----------------------|------------------------------|--|--|

| VCC Over voltage (2) | Odd skip Auto Restart Mode   |  |  |

| Over load            | Odd skip Auto Restart Mode   |  |  |

| Open Loop            | Odd skip Auto Restart Mode   |  |  |

| VCC Undervoltage     | Normal Auto Restart Mode     |  |  |

| Short Optocoupler    | Normal Auto Restart Mode     |  |  |

| Over temperature     | Non switch Auto Restart Mode |  |  |

# 3.7.3.1 Vcc OVP, OTP and Vcc under voltage

Figure 30: Vcc OVP and OTP

There are 2 types of Vcc over voltage protection; Vcc OVP (1) and Vcc OVP (2). The Vcc OVP (1) takes action only during the soft start period. The Vcc OVP (2) takes the action in any conditions.

Vcc OVP (1) condition is when Vvcc voltage is > 20.5V, V<sub>FBB</sub> voltage is > 4.5V and during soft start period, the IC enters into odd skip Auto Restart Mode. This condition likely happens during start up at open loop fault (Figure 30).