# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#

# HDTV AUDIO/VIDEO CLOCK SOURCE

#### DATASHEET

#### ICS662-03

#### Description

The ICS662-03 provides synchronous clock generation for audio sampling clock rates derived from an HDTV stream. The device uses the latest PLL technology to provide superior phase noise and long term jitter performance. The device also supports a 27 MHz output clock for video MPEG applications from an HDTV reference clock.

Please contact IDT if you have a requirement for an input and output frequency not included here.

#### **Features**

- Packaged in 8-pin SOIC

- Available in Pb (lead) free package

- HDTV clock input

- · Low phase noise

- Exact (0 ppm) multiplication ratios

- · Support for 256 and 384 times sampling rate

- Supports 27 MHz output for video (MPEG)

*NOTE: EOL for non-green parts to occur on 5/13/10 per PDN U-09-01*

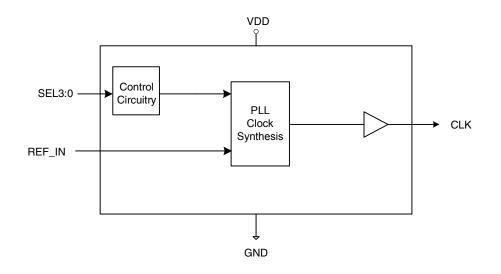

#### **Block Diagram**

1

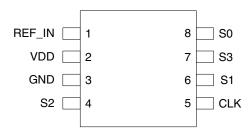

# **Pin Assignment**

8 pin (150 mil) SOIC

# **Output Clock Selection Table**

| S3 | S2 | S1 | S0 | Input<br>Frequency<br>(MHz) | Output<br>Frequency<br>(MHz) |

|----|----|----|----|-----------------------------|------------------------------|

| 0  | 0  | 0  | 0  | 74.175824                   | 8.192                        |

| 0  | 0  | 0  | 1  | 74.175824                   | 11.2896                      |

| 0  | 0  | 1  | 0  | 74.175824                   | 12.288                       |

| 0  | 0  | 1  | 1  | 74.175824                   | 24.576                       |

| 0  | 1  | 0  | 0  | 74.175824                   | 16.9344                      |

| 0  | 1  | 0  | 1  | 74.175824                   | 18.432                       |

| 0  | 1  | 1  | 0  | 74.175824                   | 36.864                       |

| 0  | 1  | 1  | 1  | 74.175824                   | 27                           |

| 1  | 0  | 0  | 0  | 74.25                       | 8.192                        |

| 1  | 0  | 0  | 1  | 74.25                       | 11.2896                      |

| 1  | 0  | 1  | 0  | 74.25                       | 12.288                       |

| 1  | 0  | 1  | 1  | 74.25                       | 24.576                       |

| 1  | 1  | 0  | 0  | 74.25                       | 16.9344                      |

| 1  | 1  | 0  | 1  | 74.25                       | 18.432                       |

| 1  | 1  | 1  | 0  | 74.25                       | 36.864                       |

| 1  | 1  | 1  | 1  | 74.25                       | 27                           |

### **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                                                                           |

|---------------|-------------|-------------|-------------------------------------------------------------------------------------------|

| 1             | REF_IN      | Input       | Connect this pin to a HDTV clock input.                                                   |

| 2             | VDD         | Power       | Connect to +3.3 V.                                                                        |

| 3             | GND         | Power       | Connect to ground.                                                                        |

| 4             | S2          | Input       | Output frequency selection. Determines output frequency per table above. On chip pull-up. |

| 5             | CLK         | Output      | Clock output.                                                                             |

| 6             | S1          | Input       | Output frequency selection. Determines output frequency per table above. On chip pull-up. |

| 7             | S3          | Input       | Output frequency selection. Determines output frequency per table above. On chip pull-up. |

| 8             | S0          | Input       | Output frequency selection. Determines output frequency per table above. On chip pull-up. |

## **Application Information**

#### **Series Termination Resistor**

Clock output traces should use series termination. To series terminate a  $50\Omega$  trace (a commonly used trace impedance), place a  $33\Omega$  resistor in series with the clock line, as close to the clock output pin as possible. The nominal impedance of the clock output is  $20\Omega$

#### **Decoupling Capacitors**

As with any high performance mixed-signal IC, the ICS662-03 must be isolated from system power supply noise to perform optimally.

Decoupling capacitors of  $0.01\mu$ F must be connected between VDD (pin 2) and the PCB ground plane (pin 3).

#### **PCB Layout Recommendations**

For optimum device performance and lowest output phase noise, the following guidelines should be observed.

1) Each  $0.01\mu$ F decoupling capacitor should be mounted on

#### **Absolute Maximum Ratings**

the component side of the board as close to the VDD pin as possible. No vias should be used between decoupling capacitor and VDD pin. The PCB trace to VDD pin should be kept as short as possible, as should the PCB trace to the ground via. Distance of the ferrite bead and bulk decoupling from the device is less critical.

2) To minimize EMI and obtain the best signal integrity, the  $33\Omega$  series termination resistor should be placed close to the clock output.

3) An optimum layout is one with all components on the same side of the board, minimizing vias through other signal layers (the ferrite bead and bulk decoupling capacitor can be mounted on the back). Other signal traces should be routed away from the ICS662-03. This includes signal traces just underneath the device, or on layers adjacent to the ground plane layer used by the device.

Stresses above the ratings listed below can cause permanent damage to the ICS662-03. These ratings, which are standard values for ICS commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                          | Rating              |

|-------------------------------|---------------------|

| Supply Voltage, VDD           | 5.5 V               |

| All Inputs and Outputs        | -0.5 V to VDD+0.5 V |

| Ambient Operating Temperature | 0 to +70° C         |

| Storage Temperature           | -65 to +150° C      |

| Junction Temperature          | 125°C               |

| Soldering Temperature         | 260° C              |

#### **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Units |

|---------------------------------------------------|------|------|------|-------|

| Ambient Operating Temperature                     | 0    |      | +70  | °C    |

| Power Supply Voltage (measured in respect to GND) | +3.0 |      | +3.6 | V     |

### **DC Electrical Characteristics**

| Parameter                 | Symbol           | Conditions               | Min.    | Тур. | Max. | Units |

|---------------------------|------------------|--------------------------|---------|------|------|-------|

| Operating Voltage         | VDD              |                          | 3.0     | 3.3  | 3.6  | V     |

| Supply Current            | IDD              | No Load, first 8 modes   |         | 25   | 29   | mA    |

|                           |                  | No Load, last 8 modes    |         | 16   | 21   | mA    |

| Input High Voltage        | V <sub>IH</sub>  |                          | 2       |      |      | V     |

| Input Low Voltage         | V <sub>IL</sub>  |                          |         |      | 0.8  | V     |

| Output High Voltage       | V <sub>OH</sub>  | I <sub>OH</sub> = -4 mA  | VDD-0.4 |      |      | V     |

| Output High Voltage       | V <sub>OH</sub>  | I <sub>OH</sub> = -12 mA | 2.4     |      |      | V     |

| Output Low Voltage        | V <sub>OL</sub>  | I <sub>OL</sub> = 12 mA  |         |      | 0.4  | V     |

| Short Circuit Current     | I <sub>OS</sub>  | Each output              |         | ±50  |      | mA    |

| Nominal Output Impedance  | Z <sub>OUT</sub> |                          |         | 20   |      | Ω     |

| Input Capacitance         | C <sub>IN</sub>  | input pins               |         | 7    |      | pF    |

| Internal pull-up resistor | R <sub>PU</sub>  | S2 pin                   |         | 510  |      | kΩ    |

|                           |                  | S3, S1, S0 pins          |         | 120  |      | kΩ    |

#### Unless stated otherwise, VDD = 3.3 V ±10%, Ambient Temperature 0 to +70° C

#### **AC Electrical Characteristics**

Unless stated otherwise, VDD = 3.3 V ±10%, Ambient Temperature 0 to +70°C

| Parameter                 | Symbol           | Conditions                                                     | Min. | Тур.        | Max. | Units |

|---------------------------|------------------|----------------------------------------------------------------|------|-------------|------|-------|

| Output Clock Rise Time    | t <sub>OR</sub>  | 20% to 80%, 15 pF load                                         |      | 1.2         | 1.5  | ns    |

| Output Clock Fall Time    | t <sub>OF</sub>  | 80% to 20%, 15 pF load                                         |      | 1.0         | 1.5  | ns    |

| Output Duty Cycle         | t <sub>OD</sub>  | at VDD/2, 15 pF load                                           | 45   |             | 55   | %     |

| Jitter, short term        | t <sub>P-P</sub> | 15 pF load                                                     |      | <u>+</u> 75 |      | ps    |

| Jitter, long term         |                  | 27M output, 15 pF load,<br>first 8 modes,<br>1000 cycles delay |      | 900         |      | ps    |

|                           |                  | 27M output, 15 pF load,<br>last 8 modes,<br>1000 cycles delay  |      | 600         |      | ps    |

| Frequency Synthesis Error |                  |                                                                |      | 0           |      | ppm   |

## **Thermal Characteristics**

| Parameter                           | Symbol          | Conditions     | Min. | Тур. | Max. | Units |

|-------------------------------------|-----------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to      | $\theta_{JA}$   | Still air      |      | 150  |      | ° C/W |

| Ambient                             | $\theta_{JA}$   | 1 m/s air flow |      | 140  |      | ° C/W |

|                                     | θ <sub>JA</sub> | 3 m/s air flow |      | 120  |      | ° C/W |

| Thermal Resistance Junction to Case | θ <sub>JC</sub> |                |      | 40   |      | ° C/W |

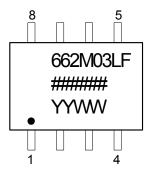

#### Marking Diagram (ICS662M-03)

# 8 5 662M-03 ####### YYWW\$\$ • 1 4

## Marking Diagram (ICS662M-03LF)

Notes:

- 1. ###### is the lot number.

- 2. YYWW is the last two digits of the year and week that the part was assembled.

- 3. "LF" denotes Pb (lead) free package.

- 4. Bottom marking: (origin). Origin = country of origin if not USA.

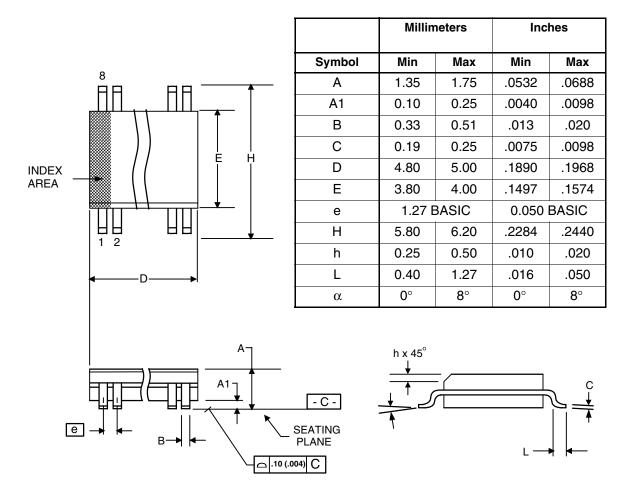

#### Package Outline and Package Dimensions (8-pin SOIC, 150 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

#### **Ordering Information**

| Part / Order Number | Marking    | Shipping Packaging | Package    | Temperature |  |

|---------------------|------------|--------------------|------------|-------------|--|

| 662M-03*            |            | Tubes              | 8-pin SOIC | 0 to +70° C |  |

| 662M-03T*           | ana naga F | Tape and Reel      | 8-pin SOIC | 0 to +70° C |  |

| 662M-03LF           | see page 5 | Tubes              | 8-pin SOIC | 0 to +70° C |  |

| 662M-03LFT          |            | Tape and Reel      | 8-pin SOIC | 0 to +70° C |  |

#### \*NOTE: EOL for non-green parts to occur on 5/13/10 per PDN U-09-01

#### Parts that are ordered with a "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

### Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

#### **For Sales**

800-345-7015 408-284-8200 Fax: 408-284-2775

## For Tech Support

www.idt.com/go/clockhelp

**Corporate Headquarters** Integrated Device Technology, Inc. www.idt.com

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA