Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PRECISION CLOCK GENERATOR OC-48 APPLICATIONS

IDT5T929

### PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES ON OCTOBER 28, 2014

#### FEATURES:

- Input frequency:

- For SONET non-FEC: 19.44MHz, 38.88MHz, 77.76MHz, 155.52MHz, 311.04MHz. or 622.08MHz

- For SONET FEC: 20.83MHz, 41.66MHz, 83.31MHz, 166.63MHz, 333.26MHz, or 666.52MHz

- For 10GE copper: 19.53MHz, 39.06MHz, 78.125MHz, 156.25MHz, 312.5MHz, or 625MHz

- For 10GE optical: 20.14MHz, 40.28MHz, 80.56MHz, 161.13MHz, 322.26MHz, or 644.53MHz

- · Output frequency range selection

- 1x, 2x, 4x, 8x, 16x, and 32x outputs on Qout

- Regenerated input clock on QREG

- Lock indicator

- · Power-down mode

- . LVPECL or LVDS outputs

- . Two modes of output frequency range

- Mode 0: Qout range 155.5 166.6MHz. Qreg is a regenerated version of the input clock.

- Mode 1: Qout range 622 666.5MHz. QREG is a regenerated version of the input clock frequency.

- · Hitless switchover

- · Differential LVPECL, LVDS, or single-ended LVTTL input interface

- 2.375 3.465V core and I/O

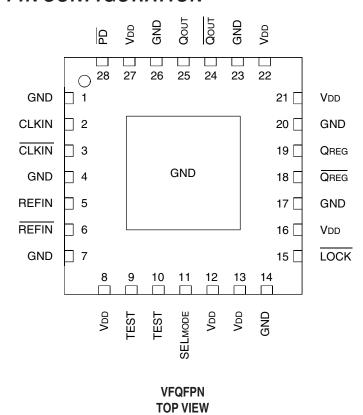

- Available in VFQFPN package

- use Replacement part: 8T49N222B-dddNLGI

### **DESCRIPTION:**

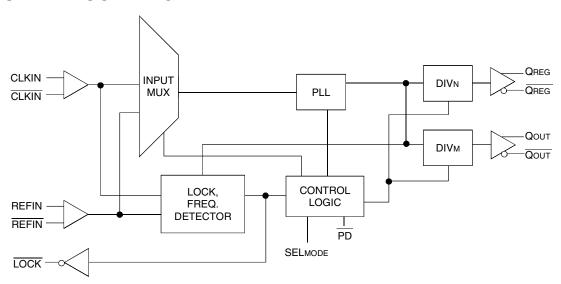

The IDT5T929 generates a high precision FEC (Forward Error Correction) or non-FEC source clock for SONET/SDH systems as well as a source clock for Gigabit Ethernet systems. This device also has clock regeneration capability: it creates a "clean" version of the clock input by using the internal oscillator to square the input clock's rising and falling edges and remove jitter. In the event that the main clock input fails, the device automatically locks to a backup reference clock using a hitless switchover mechanism.

This device detects loss of valid CLKIN and leaves the VCO of the PLL at the last valid frequency while an alternate input REFIN is selected. If CLKIN and REFIN are different frequencies, the multiplication factor will be adjusted to retain the same output frequency.

The IDT5T929 can act as a translator from a differential LVPECL, LVDS, or single-ended LVTTL input to LVPECL or LVDS outputs. The IDT5T929-10 has LVDS outputs and the IDT5T929-30 has LVPECL outputs.

The two modes of output frequency range are controlled by the SELmode. When SELmode is high or low, the Qout is a multiplied version of the input clock while QREG is a regenerated version of the input clock.

### **APPLICATIONS:**

- · Terabit routers

- · Gigabit ethernet systems

- SONET / SDH systems

- · Digital cross connects

- · Optical transceiver modules

### **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

MAY 2013

### **PIN CONFIGURATION**

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Description          | Max             | Unit |

|--------|----------------------|-----------------|------|

| VDD    | Power Supply Voltage | -0.5 to +4.1    | ٧    |

| Vı     | Input Voltage        | -0.5 to +4.1    |      |

| Vo     | Output Voltage       | -0.5 to VDD+0.5 | ٧    |

| TJ     | Junction Temperature | 150             | °C   |

| Tstg   | Storage Temperature  | -65 to +165     | °C   |

#### NOTE:

Stresses beyond those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

### CAPACITANCE(TA = +25°C, f = 1MHz, VIN = 0V)

| Parameter | Description        | Тур. | Max. | Unit |

|-----------|--------------------|------|------|------|

| CIN       | Input Capacitance  | 2.5  | 3    | pF   |

| Соит      | Output Capacitance | _    | _    | pF   |

#### NOTE:

1. Capacitance applies to all inputs except SELmode.

### RECOMMENDED OPERATING RANGE

| Symbol | Description                   | Min.  | Тур.  | Max.  | Unit |

|--------|-------------------------------|-------|-------|-------|------|

| TA     | Ambient Operating Temperature | -40   | +25   | +85   | °C   |

| VDD    | Power Supply Voltage          | 2.375 |       | 3.465 | V    |

| VT     | Termination Voltage (LVPECL)  | _     | VDD-2 | _     | V    |

|        | Termination Voltage (LVDS)    | _     | 1.2   | _     |      |

### INPUT FREQUENCY RANGE(1)

| 19.4MHz - 20.9MHz |

|-------------------|

| 38.8MHz - 41.7MHz |

| 77.7MHz - 83.4MHz |

| 155.5MHz - 167MHz |

| 311MHz - 334MHz   |

| 622MHz - 667MHz   |

|                   |

#### NOTE:

The PLL will automatically detect the input frequency and adjust the multiply ratio to generate the appropriate output frequency.

### **LOCK** FREQUENCY DETECTOR

The 5T929 will lock to, and track, a valid CLKIN signal;  $\overline{LOCK}$  will be low when this has occurred. If CLKIN fails, the 5T929 PLL will smoothly switch to lock to REFIN without generating any glitches on the output. The fact that the PLL is locked to REFIN rather than CLKIN is indicated by a high state on  $\overline{LOCK}$ . When a valid input is then applied to CLKIN, the 5T929 will smoothly switch back to locking on CLKIN, and  $\overline{LOCK}$  will go low.  $\overline{LOCK}$  will also switch to high should the frequency of CLKIN drift close to the limits of the VCO tuning range.

### **OUTPUT FREQUENCY RANGE**

| SELmode | Qout/Qout     | QREG/QREG               | Unit |

|---------|---------------|-------------------------|------|

| L       | 155.5 - 166.6 | regenerated CLKIN/CLKIN | MHz  |

| Н       | 622-666.5     | regenerated CLKIN/CLKIN | MHz  |

### PIN DESCRIPTION

| Pin Name        | I/O | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-----|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKIN, CLKIN    | I   | Adjustable <sup>(1)</sup> | Differential or single-ended clock input signal. For differential, LVPECL or LVDS supported. If left open-circuited, inputs will float to LVTTL threshold voltage so that either input may be used as a single-ended input. A capacitor to ground should be connected on the floating input.                                                                                                                      |

| REFIN, REFIN    | _   | Adjustable <sup>(1)</sup> | Differential reference clock input. The reference clock input is used as an input to the PLL when CLKIN/CLKIN fails. Differential or single-ended clock input signal. For differential, LVPECL or LVDS supported. If left open-circuited, inputs will float to LVTTL threshold voltage so that either input may be used as a single-ended input. A capacitor to ground should be connected on the floating input. |

| SELmode         | -   | 2-level <sup>(2)</sup>    | 2 level input to select output frequency range for Qout/Qout and Qred/Qred (see Output Frequency Range table)                                                                                                                                                                                                                                                                                                     |

| PD              | -   | LVTTL                     | Power Down Control. Shuts off entire chip when LOW.                                                                                                                                                                                                                                                                                                                                                               |

| Qout, Qout      | 0   | Adjustable <sup>(3)</sup> | Differential clock output. LVPECL or LVDS outputs.                                                                                                                                                                                                                                                                                                                                                                |

| Qreg, Qreg      | 0   | Adjustable <sup>(3)</sup> | Regenerated clock output from CLKIN/CLKIN, LVPECL, or LVDS outputs.                                                                                                                                                                                                                                                                                                                                               |

| LOCK            | 0   | LVTTL                     | LOW when PLL is locked to CLKIN, HIGH in all other conditions                                                                                                                                                                                                                                                                                                                                                     |

| TEST            |     |                           | Factory testing only. This pin should be left unconnected.                                                                                                                                                                                                                                                                                                                                                        |

| NC              |     |                           | No connection                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DD</sub> |     | PWR                       | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND             |     | PWR                       | Ground                                                                                                                                                                                                                                                                                                                                                                                                            |

### NOTES:

- Inputs are capable of translating the following interface standards:

Single-ended 3.3V LVTTL levels

Single-ended 2.5V LVTTL levels

Differential LVPECL levels

Differential LVDS levels

- 2. 2-level inputs are static inputs and must be tied to VDD or GND.

- 3. Outputs can be LVPECL or LVDS.

### **CLOCK INPUT/OUTPUT CONFIGURATION DESCRIPTION**

| Application  | REFIN (MHz)                          | CKIN (MHz) | SELmode     | QREG (MHz) | Qоит (МНz) |

|--------------|--------------------------------------|------------|-------------|------------|------------|

| Non-FEC      | 19.44, 38.88, 77.76, 155.52, 311.04, | 19.44      | LOW         | 19.44      | 155.52     |

|              | 622.08                               |            | HIGH        | 19.44      | 622.08     |

|              |                                      | 38.88      | LOW         | 38.88      | 155.52     |

|              |                                      |            | HIGH        | 38.88      | 622.08     |

|              |                                      | 77.76      | LOW         | 77.76      | 155.52     |

|              |                                      |            | HIGH        | 77.76      | 622.08     |

|              | ŀ                                    | 155.52     | LOW         | 155.52     | 155.52     |

|              |                                      |            | HIGH        | 155.52     | 622.08     |

|              | <br>                                 | 311.04     | LOW         | 311.04     | 155.52     |

|              |                                      |            | HIGH        | 311.04     | 622.08     |

|              | Ī                                    | 622.08     | LOW         | 622.08     | 155.52     |

|              |                                      |            | HIGH        | 622.08     | 622.08     |

| FEC          | 20.83, 41.66, 83.31, 166.63, 333.26, | 20.83      | LOW         | 20.83      | 166.63     |

| 0            | 666.52                               |            | HIGH        | 20.83      | 666.52     |

|              |                                      | 41.66      | LOW         | 41.66      | 166.63     |

|              |                                      |            | HIGH        | 41.66      | 666.52     |

|              |                                      | 83.31      | LOW         | 83.31      | 166.63     |

|              |                                      | 00.01      | HIGH        | 83.31      | 666.52     |

|              | <b>-</b>                             | 166.63     | LOW         | 166.63     | 166.63     |

|              |                                      | 100.00     | HIGH        | 166.63     | 666.52     |

|              | -                                    | 333.26     | LOW         | 333.26     | 166.63     |

|              |                                      | 000.20     | HIGH        | 333.26     | 666.52     |

|              | <b> </b>                             | 666.52     | LOW         | 666.52     | 166.63     |

|              |                                      | 000.32     | HIGH        | 666.52     | 666.52     |

| 10GE copper  | 19.53, 39.06, 78.12, 156.25, 312.5,  | 19.53      | LOW         | 19.53      | 156.25     |

| ToGEcoppei   | 625                                  | 19.55      | HIGH        | 19.53      | 625        |

|              | 023                                  | 39.06      | LOW         | 39.06      | 156.25     |

|              |                                      | 39.00      | HIGH        | 39.06      | 625        |

|              | <b> </b>                             | 78.12      | LOW         | 78.12      | 156.25     |

|              |                                      | 70.12      | HIGH        | 78.12      | 625        |

|              | -                                    | 156.25     | LOW         | 156.25     | 156.25     |

|              |                                      | 130.23     | HIGH        | 156.25     | 625        |

|              | -                                    | 010 5      | LOW         |            |            |

|              |                                      | 312.5      |             | 312.50     | 156.25     |

|              |                                      | COE        | HIGH        | 312.5      | 625        |

|              |                                      | 625        | LOW<br>HIGH | 625        | 156.25     |

| 10GE optical | 20.14.40.29.90.56.161.10.000.00      | 00.14      |             | 625        | 625        |

| rog⊏ optical | 20.14, 40.28, 80.56, 161.13, 322.26, | 20.14      | LOW         | 20.14      | 161.13     |

|              | 644.53                               | 40.00      | HIGH        | 20.14      | 644.53     |

|              |                                      | 40.28      | LOW         | 40.28      | 161.13     |

|              |                                      | 00.50      | HIGH        | 40.28      | 644.53     |

|              |                                      | 80.56      | LOW         | 80.56      | 161.13     |

|              |                                      | 101.10     | HIGH        | 80.56      | 644.53     |

|              |                                      | 161.13     | LOW         | 161.13     | 161.13     |

|              |                                      | 200.00     | HIGH        | 161.13     | 644.53     |

|              |                                      | 322.26     | LOW         | 322.26     | 161.13     |

|              |                                      |            | HIGH        | 322.26     | 644.53     |

|              |                                      | 644.53     | LOW         | 644.53     | 161.13     |

|              |                                      |            | HIGH        | 644.53     | 644.53     |

### POWER SUPPLY CHARACTERISTICS(1,2)

| Symbol | Parameter                           | Test Conditions                                            | Тур. | Max | Unit |

|--------|-------------------------------------|------------------------------------------------------------|------|-----|------|

| IDD_PD | Power Supply Current                | $V_{DD} = Max., \overline{PD} = GND, All outputs unloaded$ | ı    | 50  | μΑ   |

| Δldd   | Power Supply Current per Input HIGH | VDD = Max., VIN = 2.375V                                   | _    | 100 | μΑ   |

|        | (LVTTL inputs only)                 |                                                            |      |     |      |

| Ітот   | Total Power Supply Current          | VDD = Max., QOUT = 622MHz, All outputs unloaded            | 1    | 200 | mA   |

#### NOTES:

- 1. These power consumption characteristics are for all the valid input interfaces and cover the worst case input and output interface combinations.

- 2. As a general requirement, these parts must be capable of operating at the maximum frequency under a nominal load at a reasonable operating temperature. That means that these parts must not burn up under extended use in a typical application.

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol | Parameter                   | Test Conditions     |            | Min.      | Max | Unit |

|--------|-----------------------------|---------------------|------------|-----------|-----|------|

| Vihh   | Input HIGH Voltage Level(1) | 2-Level Inputs Only |            | VDD - 0.4 | ı   | V    |

| VILL   | Input LOW Voltage Level(1)  | 2-Level Inputs Only |            | ı         | 0.4 | V    |

| 12     | 2-Level Input DC Current    | VIN = VDD           | HIGH Level | _         | 200 | μΑ   |

|        |                             | Vin = GND           | LOW Level  | -200      | _   |      |

#### NOTE:

1. These inputs are normally wired to Vop or GND. If these inputs are switched dynamically after powerup, the function and timing of the outputs may be glitched, and the PLL may require additional tag time before all datasheet limits are achieved.

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR LVTTL

| Symbol | Parameter           | Test Conditions           | Min.  | Тур.  | Max    | Unit |

|--------|---------------------|---------------------------|-------|-------|--------|------|

| Іін    | Input HIGH Current  | VDD = 3.465V              | _     | -     | ±1     | μА   |

| lıL    | Input LOW Current   | VDD = 3.465V              | _     | -     | ±1     |      |

| Vık    | Clamp Diode Voltage | VDD = 2.375V, IIN = -18mA | _     | - 0.7 | - 1.2  | V    |

| Vin    | DC Input Voltage    |                           | - 0.3 | ı     | +3.465 | V    |

| ViH    | DC Input HIGH       |                           | 1.7   | ı     | _      | V    |

| VIL    | DC Input LOW        |                           | _     | _     | 0.7    | V    |

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR LVPECL(1)

| Symbol      | Parameter                                                                        | Test Conditions | Min.       | Тур. | Max.       | Unit |  |  |  |  |

|-------------|----------------------------------------------------------------------------------|-----------------|------------|------|------------|------|--|--|--|--|

| Input Chara | Input Characteristics                                                            |                 |            |      |            |      |  |  |  |  |

| lin         | Input Current (CLKIN, REFIN)                                                     | VDD = 3.465V    | -20        | _    | +20        | μΑ   |  |  |  |  |

| VCMR        | Common Mode Input Voltage                                                        |                 | 1          |      | VDD - 0.3  | V    |  |  |  |  |

| VDIF        | Differential Voltage Required to Toggle Input                                    |                 |            |      | _          | mV   |  |  |  |  |

| Output Cha  | racteristics                                                                     |                 |            |      |            |      |  |  |  |  |

| Voн         | Output Voltage HIGH (terminated through $50\Omega$ tied to VDD - $2V$ ) $^{(2)}$ |                 | VDD - 1.15 | _    | VDD - 0.9  | V    |  |  |  |  |

| Vol         | Output Voltage LOW (terminated through $50\Omega$ tied to Vdd - $2V$ ) (2)       |                 | VDD - 1.95 | _    | VDD - 1.61 | V    |  |  |  |  |

| Vswing      | Peak-to-Peak Output Voltage Swing                                                |                 | 0.55       | _    | 0.93       | V    |  |  |  |  |

#### NOTES:

- 1.  $V_{DD} = 2.375 3.645V$ .

- 2. Not to exceed  $V_{\text{DD}}$  0.05V.

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR LVDS

| Symbol        | Parameter                                                       | Test Conditions          | Min.  | Тур. | Max.                   | Unit |  |  |  |  |

|---------------|-----------------------------------------------------------------|--------------------------|-------|------|------------------------|------|--|--|--|--|

| Input Chara   | Input Characteristics                                           |                          |       |      |                        |      |  |  |  |  |

| lin           | Input Current (CLKIN, REFIN)                                    | VDD = 3.465V             | -20   | _    | +20                    | μΑ   |  |  |  |  |

| Vсм           | Common Mode Input Voltage Range(1)                              |                          | 0.9   | _    | V <sub>DD</sub> - 0.05 | V    |  |  |  |  |

| VDIF          | Differential Voltage Required to Toggle Input                   |                          | 100   | _    | _                      | mV   |  |  |  |  |

| Output Cha    | racteristics                                                    |                          |       |      |                        |      |  |  |  |  |

| VOT(+)        | Differential Output Voltage for the TRUE Binary State           |                          | 247   | _    | 454                    | mV   |  |  |  |  |

| Vot(-)        | Differential Output Voltage for the FALSE Binary State          |                          | -247  | _    | -454                   | mV   |  |  |  |  |

| $\Delta V$ от | $Change in Vo\intercal Between Complementary \ Output \ States$ |                          | _     | _    | 50                     | mV   |  |  |  |  |

| Vos           | Output Common Mode Voltage (Offset Voltage)                     |                          | 1.125 | 1.2  | 1.375                  | V    |  |  |  |  |

| ΔVos          | Change in Vos Between Complementary Output States               |                          | _     | _    | 50                     | mV   |  |  |  |  |

| los           | Outputs Short Circuit Current                                   | Vout(+) and Vout(-) = 0V | _     | 9    | 24                     | mA   |  |  |  |  |

| losd          | Differential Outputs Short Circuit Current                      | VOUT(+) = VOUT(-)        | _     | 6    | 12                     | mA   |  |  |  |  |

#### NOTE:

### INPUT TIMING REQUIREMENTS

| Symbol           | Parameter                                      | Min.                     | Тур.   | Max.     | Unit |

|------------------|------------------------------------------------|--------------------------|--------|----------|------|

| REFH             | Input Reference Clock Duty Cycle 40 50 60      |                          |        |          | %    |

| FREF             | Input Reference Clock Range                    | ock Range 19.44 — 666.52 |        | MHz      |      |

| REFTOL           | Input Reference Clock Frequency Tolerance -100 |                          | _      | 100      | ppm  |

| FCLKIN           | Clock in Frequency Range 19.44 — 666.52        |                          | 666.52 | MHz      |      |

| CLKINH           | Clock in Duty Cycle                            | 40                       | 50     | 60       | %    |

| taq              | Acquisition Time from Return of Valid CLKIN    | _                        | 60     | 150      | us   |

| LOCKTOL          | Frequency Tolerance for LOCK                   | -600                     | ±450   | ±450 600 |      |

| <b>t</b> лт(тог) | Tolerance to Input Jitter                      | GR-253 Sect. 5.6.2.2     |        |          | ·    |

### AC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol | Parameter                          |                                        | Min.   | Тур. | Max.   | Unit     |

|--------|------------------------------------|----------------------------------------|--------|------|--------|----------|

| Qout   | Multiplied Clock Output Frequency  | SELmode = LOW                          | 155.52 | _    | 166.63 | MHz      |

|        |                                    | SELmode = HIGH                         | 622.08 | _    | 666.52 |          |

| QREG   | Regenerated Clock Output Frequency |                                        | 19.44  | _    | 666.52 | MHz      |

| CLKIN  | Input Clock Frequency              |                                        | 19.44  | _    | 667    | MHz      |

| tr     | Output Rise Time                   | LVPECL                                 | _      | 150  | _      | ps       |

|        |                                    | LVDS                                   | _      | 100  | _      |          |

| t⊧     | Output Fall Time                   | LVPECL                                 | _      | 150  | _      | ps       |

|        |                                    | LVDS                                   | _      | 100  | _      |          |

| tsk    | Skew between Qout and Qreg         |                                        | _      | 10   | 20     | ps       |

| PLLBW  | PLLBandwidth                       |                                        | 250    | 305  | 500    | KHz      |

| †₽     | JitterTransferPeaking              |                                        | _      | 0.05 | 0.1    | dB       |

|        |                                    | Output frequency = 622MHz - 666.5MHz   | _      | 0.4  | 1      |          |

| tı     | Jitter Generation <sup>(1)</sup>   | Output frequency = 155.5MHz - 166.6MHz | _      | 0.8  | 3.4    | ps (RMS) |

|        | (with 12KHz to 20MHz filter)       | Output frequency = 77.7MHz - 83.4MHz   | _      | 1.2  | 3.5    |          |

| touty  | Output Duty Cycle                  |                                        | 45     | _    | 55     | %        |

#### NOTE:

<sup>1.</sup> Not to exceed VDD - 0.05V.

<sup>1.</sup> All input frequencies permitted by PLL bandwidth.

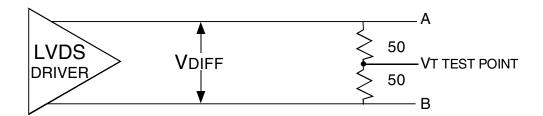

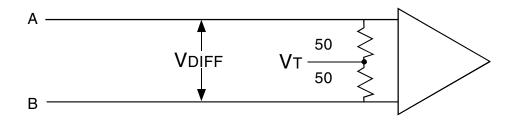

### **TEST CONDITIONS**

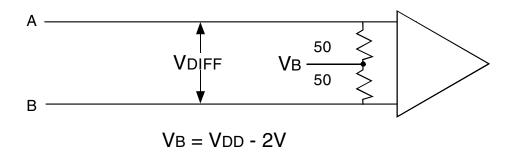

Test Circuit for LVDS Output Characteristics

Test Circuit for LVDS Input Characteristics

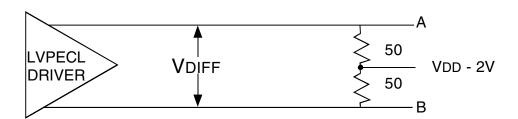

Test Circuit for LVPECL Output Characteristics

Test Circuit for LVPECL Input Characteristics

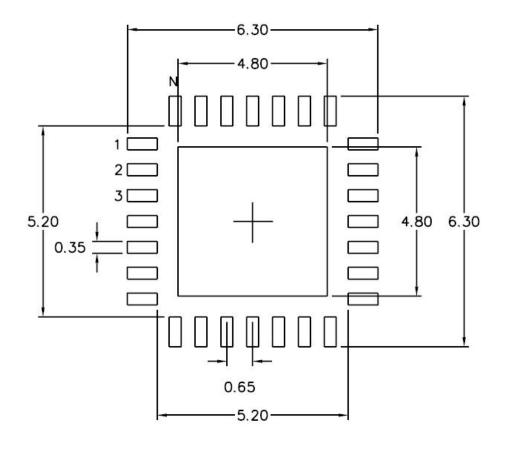

### RECOMMENDED LANDING PATTERN

NL 28 pin

NOTE: All dimensions are in millimeters.

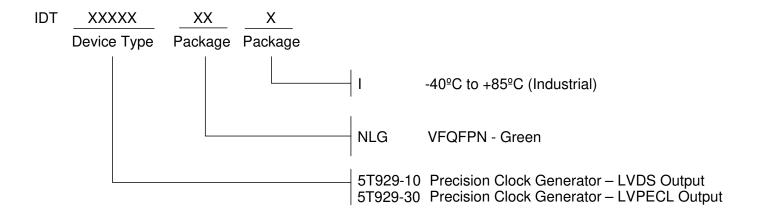

### **ORDERING INFORMATION**

### **REVISION HISTORY**

| Rev | Table | Page | Discription of Change                                                                     | Date     |

|-----|-------|------|-------------------------------------------------------------------------------------------|----------|

| А   |       | 1    | NRND - Not Recommended for New Designs                                                    | 5/5/13   |

| А   |       | 1    | Product Discontinuation Notice - Last Time Buy Expires on October 28, 2014, PDN# CQ-13-02 | 11/27/13 |

# We've Got Your Timing Solution.

6024 Silver Creek Valley Road San Jose, CA 95138 Sales

800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT Tech Support

netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2013. All rights reserved.