Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# QUAD OUTPUT CLOCK GENERATOR

IDT5V927

#### **FEATURES:**

- 3V to 3.6V operating voltage

- 50MHz to 160MHz output frequency range

- · Input from fundamental crystal oscillator or external source

- Internal PLL feedback (loading feedback output relative to other outputs, adjusts propagation delay between REF inputs and outputs)

- Select inputs (S[1:0]) for FB divide selection (multiply ratio of 2, 3, 4, 4.25, 5, 6, 6.25, and 8)

- · Low jitter

- PLL bypass for testing and power-down control (S1 = H, S0 = H, powers part down <500μA)</li>

- · Available in TSSOP package

#### **APPLICATIONS:**

- · Gigabit ethernet

- Router

- · Network switches

- SAN

- Instrumentation

- Fibre channel

#### **DESCRIPTION:**

The IDT5V927 is a low-cost, low skew, low jitter, and high-performance clock synthesizer. It has been specially designed to interface with Gigabit Ethernet (125MHz), Fibre Channel (106.25MHz), and OC-3 (155.52MHz) applications. It can be programmed to provide output frequencies ranging from 50MHz to 160MHz, with input frequencies ranging from 6.25MHz to 80MHz.

The IDT5V927 includes an internal RC filter that provides excellent jitter characteristics and eliminates the need for external components. When using the optional crystal input, the chip accepts a 10 - 40MHz fundamental mode crystal with a maximum equivalent series resistance of  $50\Omega$ .

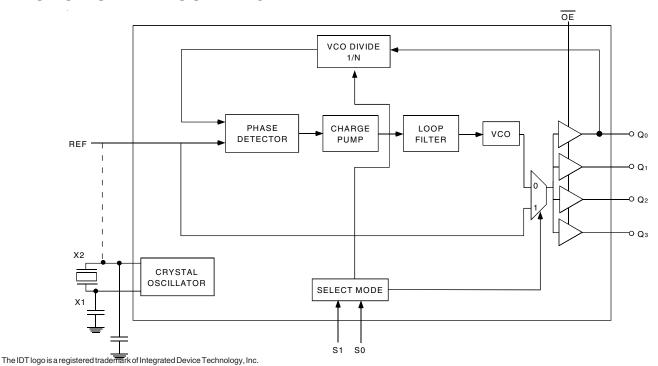

### **FUNCTIONAL BLOCK DIAGRAM**

INDUSTRIAL TEMPERATURE RANGE

OCTOBER 2008

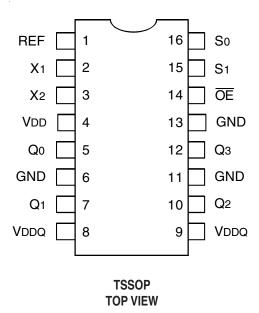

### **PIN CONFIGURATION**

### **CRYSTAL SPECIFICATION**

The crystal oscillators should be fundamental mode quartz crystals: overtone crystals are not suitable. Crystal frequency should be specified for parallel resonance with  $50\Omega$  maximum equivalent series resonance. Crystal tuning capacitors should be connected from X2/REF to GND and from X1 to GND.

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol   | Description              | Max.          | Unit |

|----------|--------------------------|---------------|------|

| VDD/VDDQ | Supply Voltage to Ground | - 0.5 to +4.6 | V    |

| Vı       | Input Voltage            | - 0.5 to +4.6 | V    |

| lo       | Output Current           | ±50           | mA   |

| Tstg     | Storage Temperature      | -65 to +150   | °C   |

| TJ       | Junction Temperature     | 150           | °C   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

#### PIN DESCRIPTION

| Pin Name | Туре | Description                                                                                                                                                                |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S[1:0]   | Ι    | Three level divider/mode select pins. Float to MID.                                                                                                                        |

| ŌĒ       | I    | Output enable bar. $\overline{\text{OE}}$ has a pull-down. Output Q[1:3] tristated when HIGH. Output Q0 remains running when in PLL mode and tri-states when in TEST mode. |

| X1       | Ι    | Crystaloscillatorinput.Connect toGNDifoscillatornotrequired.                                                                                                               |

| X2       | Ι    | Crystal oscillator output. Leave unconnected for clock input.                                                                                                              |

| REF      | Ι    | Input clock. Connect to X2 if crystal oscillator is used.                                                                                                                  |

| Q[1:3]   | 0    | Output at N*REF frequency                                                                                                                                                  |

| Q0       | 0    | Output at N*REF internally connected for PLL feedback                                                                                                                      |

| VDDQ     | PWR  | Power supply for the device outputs. Connect to VDD on PCB.                                                                                                                |

| VDD      | PWR  | Power supply for the device core and inputs. Connect to VDD on PCB.                                                                                                        |

| GND      | PWR  | Ground supply                                                                                                                                                              |

### **DIVIDE SELECTION TABLE**(1)

| S1 | S0 | Divide-by-N Value | Mode                |

|----|----|-------------------|---------------------|

| L  | L  | 2                 | PLL                 |

| L  | M  | 3                 | PLL                 |

| L  | Н  | 4                 | PLL                 |

| М  | L  | 4.25              | PLL                 |

| М  | М  | 5                 | PLL                 |

| M  | Н  | 6                 | PLL                 |

| Н  | L  | 6.25              | PLL                 |

| Н  | M  | 8                 | PLL                 |

| Н  | Н  | TEST              | TEST <sup>(2)</sup> |

#### NOTES:

- 1. H = HIGH

- M = MEDIUM I = I OW

- 2. Test mode for low frequency testing. In this mode, REF clock bypasses the VCO (VCO powered down) and the crystal oscillator is powered down.

### COMMON OUTPUT FREQUENCY EXAMPLES (MHz)

| Output                     | 50 | 60 | 64 | 72 | 75 | 80 | 90 | 100 |

|----------------------------|----|----|----|----|----|----|----|-----|

| Input                      | 25 | 10 | 16 | 12 | 25 | 10 | 15 | 20  |

| FB Divide Selection S[1:0] | Щ  | МН | LH | MH | LM | НМ | МН | MM  |

| Output                     | 106.25 | 106.25 | 120 | 125 | 125 | 125  | 150 | 155.52 |

|----------------------------|--------|--------|-----|-----|-----|------|-----|--------|

| Input                      | 17     | 25     | 15  | 20  | 25  | 62.5 | 25  | 19.44  |

| FB Divide Selection S[1:0] | HL     | ML     | НМ  | HL  | ММ  | Ш    | МН  | НМ     |

### **OPERATING CONDITIONS**

| Symbol   | Parameter                                            | Min. | Тур. | Max. | Unit |

|----------|------------------------------------------------------|------|------|------|------|

| VDD/VDDQ | Power Supply Voltage                                 | 3    | 3.3  | 3.6  | V    |

| TA       | Operating Temperature                                | - 40 | 25   | +85  | °C   |

| CL       | Output Load Capacitance                              | _    | -    | 15   | pF   |

| CIN      | Input Capacitance, OE, F = 1MHz, VIN = 0V, TA = 25°C | _    | 5    | 7    | pF   |

### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Industrial: TA = -40°C to +85°C, VDD/VDDQ = 3.3V  $\pm 0.3$ V

| Symbol | Parameter                              | Test Conditions              |            | Min.                     | Тур. | Max              | Unit |

|--------|----------------------------------------|------------------------------|------------|--------------------------|------|------------------|------|

| VIL    | Input LOW Voltage                      |                              |            | _                        | _    | 0.8              | V    |

| ViH    | Input HIGH Voltage                     |                              |            | 2                        | _    | _                | V    |

| Vihh   | Input HIGH Voltage                     | 3-level input only           |            | VDD - 0.6                | _    | _                | V    |

| Vimm   | Input MID Voltage                      | 3-level input only           |            | V <sub>DD</sub> /2 - 0.3 | _    | $V_{DD}/2 + 0.3$ | V    |

| VILL   | Input LOW Voltage                      | 3-level input only           |            |                          | _    | 0.6              | V    |

| lin    | Input Leakage Current (REF input only) | VIN = VDD or GND, VDD = Max. |            | -5                       | _    | +5               | μΑ   |

|        |                                        | VIN = VDD                    | HIGH Level | _                        | _    | +200             |      |

| l3     | 3-Level Input DC Current, S[1:0]       | VIN = VDD/2                  | MID Level  | - 50                     | _    | +50              | μΑ   |

|        |                                        | VIN = GND                    | LOW Level  | -200                     | _    | _                |      |

| Іін    | Input HIGH Current                     | VIN = VDD                    | ŌĒ         | _                        | _    | 100              | μΑ   |

|        |                                        | VIN = VDD, S[1:0] = HH       | X1         | _                        | 2    | 4                | mA   |

| Vol    | Output LOW Voltage                     | IoL = 12mA                   |            | _                        | _    | 0.4              | V    |

| Vон    | Output HIGH Voltage                    | Iон = -12mA                  |            | 2.4                      | _    | _                | V    |

### **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                | Test Conditions (1)                              | Min. | Тур. | Max | Unit |

|--------|--------------------------|--------------------------------------------------|------|------|-----|------|

| IDD_PD | Power Down Current       | VDD = Max.                                       | _    | _    | 500 | μΑ   |

|        |                          | S[1:0] = HH                                      |      |      |     |      |

|        |                          | $\overline{OE}$ = L; REF = L; X <sub>1</sub> = L |      |      |     |      |

|        |                          | Alloutputs unloaded                              |      |      |     |      |

| Δldd   | Supply Current per Input | VDD = Max., VIN = 3V                             | _    | _    | 30  | μΑ   |

| IDD    | Dynamic Supply Current   | VDD = 3.6V                                       | _    | _    | 130 | mA   |

|        |                          | S[1:0] = LL                                      |      |      |     |      |

|        |                          | $\overline{OE} = L$                              |      |      |     |      |

|        |                          | FOUT = 150MHz                                    |      |      |     |      |

|        |                          | All outputs unloaded                             |      |      |     |      |

#### NOTE:

### AC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol | Parameter                          | Test Conditions |                              | Min. | Тур. | Max. | Unit |

|--------|------------------------------------|-----------------|------------------------------|------|------|------|------|

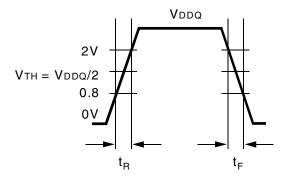

| tR,tF  | Rise Time, Fall Time               | 0.8V to 2V      | 0.8V to 2V                   |      | 0.7  | 1.5  | ns   |

| dτ     | Output/Duty Cycle                  | VT = VDDQ/2     |                              | 45   | 50   | 55   | %    |

|        | REF to Qo <sup>(1)</sup>           | VT = VDDQ/2     | fout ≥ 100MHz, all N         | -200 | _    | 200  | ps   |

| tPD    |                                    |                 | 50 < fout < 160MHz, N ≤ 4    | -200 | _    | 200  |      |

|        |                                    |                 | 50 < fout < 160MHz, N ≥ 4.25 | -350 | _    | 350  |      |

| tsk    | Output to Output Skew (Q0 to Q1:3) | Equalloads      | Equalloads                   |      | _    | 150  | ps   |

| tJ     | Cycle - Cycle Jitter               | fout ≥ 100MHz   |                              | -155 | _    | 155  | ps   |

| four   | Output Frequency                   |                 |                              | 50   | _    | 160  | MHz  |

#### NOTE:

### INPUT TIMING REQUIREMENTS

| Symbol | Description <sup>(1)</sup>                                  | Min. | Max.  | Unit |

|--------|-------------------------------------------------------------|------|-------|------|

| tR,tF  | Maximum input rise and fall time, 0.8V to 2V <sup>(2)</sup> | _    | 10    | ns/V |

| tPWC   | Input clock pulse, HIGH or LOW <sup>(2)</sup>               | 2    | _     | ns   |

| Dн     | Input duty cycle <sup>(2)</sup>                             | 10   | 90    | %    |

| fosc   | XTALoscillatorfrequency                                     | _    | 40    | MHz  |

| fiN    | Inputfrequency <sup>(2)</sup>                               | 50/N | 160/N | MHz  |

#### NOTES:

- 1. Where pulse width implied by  $\ensuremath{\mathsf{DH}}$  is less than the tPWC limit, tPWC limit applies,

- 2. When using a clock input.

<sup>1.</sup> For conditions shown as Min. or Max., use the appropriate values specified under DC Electrical Characteristics.

<sup>1.</sup> When using a clock input.

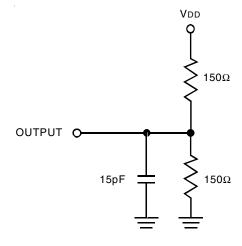

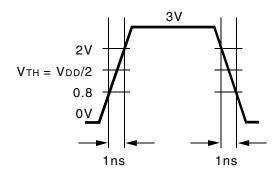

### **ACTEST LOADS AND WAVEFORMS**

AC Test Load

Input Test Waveform

Output Waveform

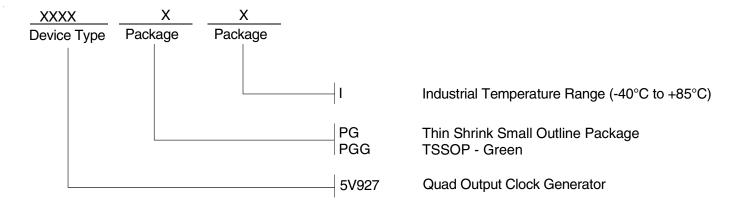

### **ORDERING INFORMATION**

6024 Silver Creek Valley Road San Jose, CA 95138 for SALES: 800-345-7015 or 40

800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com

for Tech Support: clockhelp@idt.com