Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 3.3V PROGRAMMABLE SKEW PLL CLOCK DRIVER TURBOCLOCK™

#### **FEATURES:**

- . REF is 5V tolerant

- · 4 pairs of programmable skew outputs

- · Low skew: 200ps same pair, 250ps all outputs

- Selectable positive or negative edge synchronization: Excellent for DSP applications

- · Synchronous output enable

- Output frequency: 3.75MHz to 85MHz

- 2x, 4x, 1/2, and 1/4 outputs

- · 3 skew grades:

IDT5V991A-2: tskewo<250ps IDT5V991A-5: tskewo<500ps IDT5V991A-7: tskewo<750ps

- · 3-level inputs for skew and PLL range control

- · PLL bypass for DC testing

- External feedback, internal loop filter

- · 12mA balanced drive outputs

- Low Jitter: <200ps peak-to-peak

- · Available in 32-pin PLCC Package

## **DESCRIPTION:**

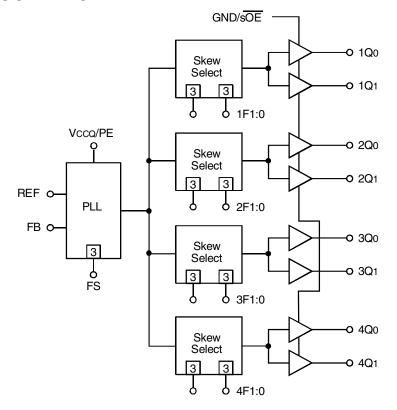

The IDT5V991A is a high fanout 3.3V PLL based clock driver intended for high performance computing and data-communications applications. A key feature of the programmable skew is the ability of outputs to lead or lag the REF input signal. The IDT5V991A has eight programmable skew outputs in four banks of 2. Skew is controlled by 3-level input signals that may be hard-wired to appropriate HIGH-MID-LOW levels.

When the GND/sOE pin is held low, all the outputs are synchronously enabled. However, if GND/sOE is held high, all the outputs except 3Q0 and 3Q1 are synchronously disabled.

Furthermore, when the VCCQ/PE is held high, all the outputs are synchronized with the positive edge of the REF clock input. When VCCQ/PE is held low, all the outputs are synchronized with the negative edge of REF. Both devices have LVTTL outputs with 12mA balanced drive outputs.

## **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

OCTOBER 2008

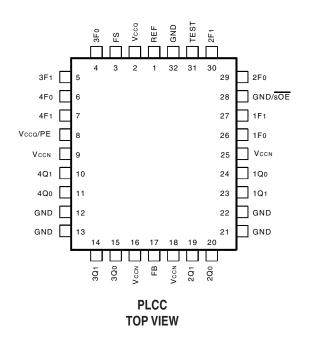

## **PIN CONFIGURATION**

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Description              | Max             | Unit |

|--------|--------------------------|-----------------|------|

|        | Supply Voltage to Ground | -0.5 to +7      | ٧    |

| Vı     | DC Input Voltage         | -0.5 to Vcc+0.5 | V    |

|        | REF Input Voltage        | -0.5 to +5.5    | ٧    |

| TJ     | Junction Temperature     | 150             | °C   |

| Tstg   | Storage Temperature      | -65 to +150     | °C   |

#### NOTE:

Stresses beyond those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

## **CAPACITANCE** (TA = $+25^{\circ}$ C, f = 1MHz, Vin = 0V)

| Parameter | Description       | Тур. | Max. | Unit |

|-----------|-------------------|------|------|------|

| CIN       | Input Capacitance | 5    | 7    | pF   |

#### NOTE:

1. Capacitance applies to all inputs except TEST, FS, and nF1:0.

#### PIN DESCRIPTION

| Pin Name            | Туре | Description                                                                                                                     |

|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| REF                 | IN   | Reference Clock Input                                                                                                           |

| FB                  | IN   | FeedbackInput                                                                                                                   |

| TEST <sup>(1)</sup> | IN   | When MID or HIGH, disables PLL (except for conditions of Note 1). REF goes to all outputs. Skew selections (see Control         |

|                     |      | Summary Table) remain in effect. Set LOW for normal operation.                                                                  |

| GND/ sOE (1)        | IN   | Synchronous Output Enable. When HIGH, it stops clock outputs (except 3Qo and 3Q1) in a LOW state - 3Qo and 3Q1 may be used      |

|                     |      | as the feedback signal to maintain phase lock. When TEST is held at MID level and GND/SOE is HIGH, the nF[1:0] pins act as      |

|                     |      | output disable controls for individual banks when $nF[1:0] = LL$ . Set GND/ $\overline{SOE}$ LOW for normal operation.          |

| Vccq/PE             | IN   | Selectable positive or negative edge control. When LOW/HIGH the outputs are synchronized with the negative/positive edge of the |

|                     |      | reference clock.                                                                                                                |

| nF[1:0]             | IN   | 3-level inputs for selecting 1 of 9 skew taps or frequency functions                                                            |

| FS                  | IN   | Selects appropriate oscillator circuit based on anticipated frequency range. (See PLL Programmable Skew Range.)                 |

| nQ[1:0]             | OUT  | Four banks of two outputs with programmable skew                                                                                |

| Vccn                | PWR  | Power supply for output buffers                                                                                                 |

| Vccq                | PWR  | Power supply for phase locked loop and other internal circuitry                                                                 |

| GND                 | PWR  | Ground                                                                                                                          |

#### NOTE:

1.When TEST = MID and  $GND/\overline{SOE}$  = HIGH, PLL remains active with nF[1:0] = LL functioning as an output disable control for individual output banks. Skew selections remain in effect unless nF[1:0] = LL.

### **PROGRAMMABLE SKEW**

Output skew with respect to the REF input is adjustable to compensate for PCB trace delays, backplane propagation delays or to accommodate requirements for special timing relationships between clocked components. Skew is selectable as a multiple of a time unit to which is of the order of a nanosecond (see PLL Programmable Skew Range and Resolution Table). There are nine skew configurations available for each output pair. These configurations are chosen by the nF1:0 control pins. In order

to minimize the number of control pins, 3-level inputs (HIGH-MID-LOW) are used, they are intended for but not restricted to hard-wiring. Undriven 3-level inputs default to the MID level. Where programmable skew is not a requirement, the control pins can be left open for the zero skew default setting. The Control Summary Table shows how to select specific skew taps by using the nF1:0 control pins.

## **EXTERNAL FEEDBACK**

By providing external feedback, the IDT5V991A gives users flexibility with regard to skew adjustment. The FB signal is compared with the input REF signal at the phase detector in order to drive the VCO. Phase differences cause the VCO of the PLL to adjust upwards or downwards accordingly.

An internal loop filter moderates the response of the VCO to the phase detector. The loop filter transfer function has been chosen to provide minimal jitter (or frequency variation) while still providing accurate responses to input frequency changes.

### PLL PROGRAMMABLE SKEW RANGE AND RESOLUTION TABLE

|                                             | FS = LOW      | FS = MID      | FS = HIGH     | Comments        |

|---------------------------------------------|---------------|---------------|---------------|-----------------|

| Timing Unit Calculation (tu)                | 1/(44 x FNOM) | 1/(26 x Fnom) | 1/(16 x FNOM) |                 |

| VCO Frequency Range (FNOM) <sup>(1,2)</sup> | 15 to 35MHz   | 25 to 60MHz   | 40 to 85 MHz  |                 |

| Skew Adjustment Range <sup>(3)</sup>        |               |               |               |                 |

| Max Adjustment:                             | ±9.09ns       | ±9.23ns       | ±9.38ns       | ns              |

|                                             | ±49º          | ±83º          | ±135º         | Phase Degrees   |

|                                             | ±14%          | ±23%          | ±37%          | % of Cycle Time |

| Example 1, FNOM = 15MHz                     | t∪ = 1.52ns   | _             | _             |                 |

| Example 2, FNOM = 25MHz                     | t∪=0.91ns     | tu = 1.54ns   | _             |                 |

| Example 3, FNOM = 30MHz                     | t∪=0.76ns     | tu = 1.28ns   | _             |                 |

| Example 4, FNOM = 40MHz                     | _             | tu = 0.96ns   | t∪=1.56ns     |                 |

| Example 5, FNOM = 50MHz                     | _             | tu = 0.77ns   | t∪=1.25ns     |                 |

| Example 6, FNOM = 80MHz                     | _             | _             | tu=0.78ns     |                 |

#### NOTES:

- The device may be operated outside recommended frequency ranges without damage, but functional operation is not guaranteed. Selecting the appropriate FS value based on input frequency range allows the PLL to operate in its 'sweet spot' where jitter is lowest.

- 2. The level to be set on FS is determined by the nominal operating frequency of the VCO and Time Unit Generator. The VCO frequency always appears at 1Q1:0, 2Q1:0, and the higher outputs when they are operated in their undivided modes. The frequency appearing at the REF and FB inputs will be the same as the VCO when the output connected to FB is undivided. The frequency of the REF and FB inputs will be 1/2 or 1/4 the VCO frequency when the part is configured for a frequency multiplication by using a divided output as the FB input.

- 3. Skew adjustment range assumes that a zero skew output is used for feedback. If a skewed Q output is used for feedback, then adjustment range will be greater. For example if a 4tu skewed output is used for feedback, all other outputs will be skewed -4tu in addition to whatever skew value is programmed for those outputs. 'Max adjustment' range applies to output pairs 3 and 4 where ± 6tu skew adjustment is possible and at the lowest FNOM value.

#### CONTROL SUMMARY TABLE FOR FEEDBACK SIGNALS

| nF1:0             | Skew (Pair #1, #2) | Skew (Pair #3) | Skew (Pair #4)          |

|-------------------|--------------------|----------------|-------------------------|

| LL <sup>(1)</sup> | -4tu               | Divide by 2    | Divide by 2             |

| LM                | LM –3tu            |                | –6tu                    |

| LH                | -2tu               | -4tu           | –4tu                    |

| ML                | –1t∪               | -2tu           | –2tu                    |

| MM                | Zero Skew          | Zero Skew      | Zero Skew               |

| MH                | 1tu                | 2t∪            | 2t∪                     |

| HL                | 2tu                | 4tu            | 4tu                     |

| HM                | 3tu                | 6tu            | 6tu                     |

| НН                | 4tu                | Divide by 4    | Inverted <sup>(2)</sup> |

#### NOTES:

- 1. LL disables outputs if TEST = MID and GND/sOE = HIGH.

- 2. When pair #4 is set to HH (inverted), GND/sOE disables pair #4 HIGH when Vcco/PE = HIGH, GND/sOE disables pair #4 LOW when Vcco/PE = LOW.

## RECOMMENDED OPERATING RANGE

|        |                               |      | A-2, -5, -7<br>strial) | IDT5V991A-2<br>(Commercial) |      |      |

|--------|-------------------------------|------|------------------------|-----------------------------|------|------|

| Symbol | Description                   | Min. | Max.                   | Min.                        | Max. | Unit |

| Vcc    | Power Supply Voltage          | 3    | 3.6                    | 3                           | 3.6  | V    |

| TA     | Ambient Operating Temperature | -40  | +85                    | 0                           | +70  | °C   |

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol | Parameter                                  | Conditions                  |                 | Min.      | Max. | Unit |

|--------|--------------------------------------------|-----------------------------|-----------------|-----------|------|------|

| VIH    | Input HIGH Voltage                         | Guaranteed Logic HIGH (REF, | FB Inputs Only) | 2         | _    | V    |

| VIL    | Input LOW Voltage                          | Guaranteed Logic LOW (REF,  | FB Inputs Only) | _         | 0.8  | V    |

| VIHH   | Input HIGH Voltage <sup>(1)</sup>          | 3-Level Inputs Only         | Vcc-0.6         | _         | V    |      |

| VIMM   | Input MID Voltage(1)                       | 3-Level Inputs Only         | Vcc/2-0.3       | Vcc/2+0.3 | V    |      |

| VILL   | Input LOW Voltage <sup>(1)</sup>           | 3-Level Inputs Only         | _               | 0.6       | V    |      |

| lin    | Input Leakage Current                      | VIN = Vcc or GND            | _               | ±5        | μA   |      |

|        | (REF, FB Inputs Only)                      | Vcc = Max.                  |                 |           |      |      |

|        |                                            | VIN = VCC                   | HIGH Level      | _         | ±200 |      |

| 13     | 3-Level Input DC Current (TEST, FS, nF1:0) | VIN = VCC/2                 | MID Level       | _         | ±50  | μΑ   |

|        |                                            | VIN = GND                   | LOW Level       | _         | ±200 |      |

| IPU    | Input Pull-Up Current (Vccq/PE)            | Vcc = Max., Vin = GND       |                 | _         | ±100 | μА   |

| IPD    | Input Pull-Down Current (GND/SOE)          | Vcc = Max., ViN = Vcc       | _               | ±100      | μА   |      |

| Vон    | Output HIGH Voltage                        | Vcc = Min., IoH = -12mA     |                 | 2.4       | _    | V    |

| Vol    | Output LOW Voltage                         | VCC = Min., IOL = 12mA      |                 | _         | 0.55 | V    |

#### NOTE:

## POWER SUPPLY CHARACTERISTICS

| Symbol | Parameter                               | Test Conditions <sup>(1)</sup>                      | Typ. <sup>(2)</sup> | Max. | Unit   |

|--------|-----------------------------------------|-----------------------------------------------------|---------------------|------|--------|

| Iccq   | Quiescent Power Supply Current          | Vcc = Max., TEST = MID, REF = LOW,                  | 8                   | 25   | mA     |

|        |                                         | Vcco/PE = LOW, GND/sOE = LOW All outputs unloaded   |                     |      |        |

|        |                                         | All outputs unloaded                                |                     |      |        |

| Δlcc   | Power Supply Current per Input HIGH     | Vcc = Max., Vin = 3V                                | 1                   | 30   | μΑ     |

| ICCD   | Dynamic Power Supply Current per Output | Vcc = Max., CL = 0pF                                | 55                  | 90   | μA/MHz |

| Ітот   | Total Power Supply Current              | $Vcc = 3.3V$ , $Fref = 20MHz$ , $CL = 160pF^{(1)}$  | 29                  | _    |        |

|        |                                         | Vcc = 3.3V, FREF = 33MHz, CL = 160pF <sup>(1)</sup> | 42                  | _    | mA     |

|        |                                         | Vcc = 3.3V, Fref = 66MHz, CL = 160pF <sup>(1)</sup> | 76                  | _    |        |

#### NOTE:

## INPUT TIMING REQUIREMENTS

| Symbol | Description <sup>(1)</sup>                    | Min. | Max. | Unit |

|--------|-----------------------------------------------|------|------|------|

| tR, tF | Maximum input rise and fall times, 0.8V to 2V | -    | 10   | ns/V |

| tpwc   | Input clock pulse, HIGH or LOW                | 3    | _    | ns   |

| DH     | Input duty cycle                              | 10   | 90   | %    |

| Ref    | Reference Clock Input                         | 3.75 | 85   | MHz  |

#### NOTE:

<sup>1.</sup> These inputs are normally wired to Vcc, GND, or unconnected. Internal termination resistors bias unconnected inputs to Vcc/2. If these inputs are switched, the function and timing of the outputs may be glitched, and the PLL may require an additional tLOCK time before all datasheet limits are achieved.

<sup>1.</sup> For eight outputs, each loaded with 20pF.

<sup>1.</sup> Where pulse width implied by DH is less than tPwc limit, tPwc limit applies.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE

|             |                                          |                               | l II                                                 | DT5V991A | -2   | 10   | DT5V991A   | -5       | ID.  | T5V991A | -7   |      |

|-------------|------------------------------------------|-------------------------------|------------------------------------------------------|----------|------|------|------------|----------|------|---------|------|------|

| Symbol      | Parameter                                |                               | Min.                                                 | Тур.     | Max. | Min. | Тур.       | Max.     | Min. | Тур.    | Max. | Unit |

| FNOM        | VCO Frequency Range                      |                               | See PLL Programmable Skew Range and Resolution Table |          |      |      |            |          |      |         |      |      |

| trpwh       | REF Pulse Width HIGH(11)                 |                               | 3                                                    | _        | _    | 3    | -          | _        | 3    | _       | _    | ns   |

| trpwl       | REF Pulse Width LOW(11)                  |                               | 3                                                    | _        | _    | 3    | _          | _        | 3    | _       | _    | ns   |

| tu          | Programmable Skew Time Unit              |                               |                                                      |          |      | See  | Control Su | mmary Ta | ble  | •       |      |      |

| tskewpr     | Zero Output Matched-Pair Skew            | (xQ0, xQ1) <sup>(1,2,3)</sup> | _                                                    | 0.05     | 0.2  | _    | 0.1        | 0.25     | _    | 0.1     | 0.25 | ns   |

| tskew0      | Zero Output Skew (All Outputs)(1         | 4,5)                          | _                                                    | 0.1      | 0.25 | _    | 0.25       | 0.5      | _    | 0.3     | 0.75 | ns   |

| tskew1      | Output Skew                              |                               | _                                                    | 0.25     | 0.5  | _    | 0.6        | 0.7      | _    | 0.6     | 1    | ns   |

|             | (Rise-Rise, Fall-Fall, Same Clas         | s Outputs)(1,6)               |                                                      |          |      |      |            |          |      |         |      |      |

| tskew2      | Output Skew                              |                               | _                                                    | 0.3      | 1.2  | _    | 0.5        | 1.2      | _    | 1       | 1.5  | ns   |

|             | (Rise-Fall, Nominal-Inverted, Div        | ided-Divided)(1,6)            |                                                      |          |      |      |            |          |      |         |      |      |

| tskew3      | Output Skew                              |                               | _                                                    | 0.25     | 0.5  | _    | 0.5        | 0.7      | _    | 0.7     | 1.2  | ns   |

|             | (Rise-Rise, Fall-Fall, Different Cla     | ass Outputs)(1,6)             |                                                      |          |      |      |            |          |      |         |      |      |

| tskew4      | Output Skew                              |                               | _                                                    | 0.5      | 0.9  | _    | 0.5        | 1        | _    | 1.2     | 1.7  | ns   |

|             | (Rise-Fall, Nominal-Divided, Divi        | ded-Inverted)(1,2)            |                                                      |          |      |      |            |          |      |         |      |      |

| tDEV        | Device-to-Device Skew <sup>(1,2,7)</sup> |                               | _                                                    | _        | 0.75 | _    | _          | 1.25     | _    | _       | 1.65 | ns   |

| <b>t</b> PD | REF Input to FB Propagation De           | lay <sup>(1,9)</sup>          | -0.25                                                | 0        | 0.25 | -0.5 | 0          | 0.5      | -0.7 | 0       | 0.7  | ns   |

| todcv       | Output Duty Cycle Variation from         | n 50% <sup>(1)</sup>          | -1.2                                                 | 0        | 1.2  | -1.2 | 0          | 1.2      | -1.2 | 0       | 1.2  | ns   |

| tpwH        | Output HIGH Time Deviation fro           | m 50% <sup>(1,10)</sup>       | _                                                    | _        | 2    | _    | _          | 2.5      | _    | _       | 3    | ns   |

| tPWL        | Output LOW Time Deviation from           | 1 50% <sup>(1,11)</sup>       | _                                                    | _        | 1.5  | _    | _          | 3        | _    | _       | 3.5  | ns   |

| torise      | Output Rise Time(1)                      |                               | 0.15                                                 | 1        | 1.2  | 0.15 | 1          | 1.5      | 0.15 | 1.5     | 2.5  | ns   |

| tofall      | Output Fall Time <sup>(1)</sup>          |                               | 0.15                                                 | 1        | 1.2  | 0.15 | 1          | 1.5      | 0.15 | 1.5     | 2.5  | ns   |

| tLOCK       | PLL Lock Time <sup>(1,8)</sup>           |                               | _                                                    | _        | 0.5  | _    | _          | 0.5      | _    | _       | 0.5  | ms   |

| ₩           | Cycle-to-Cycle Output Jitter(1)          | RMS                           | _                                                    | _        | 25   | _    | _          | 25       | _    | _       | 25   | ps   |

|             |                                          | Peak-to-Peak                  | _                                                    | _        | 200  | _    | _          | 200      | _    | _       | 200  |      |

#### NOTES:

- 1. All timing and jitter tolerances apply for FNOM  $\geq$  25MHz.

- 2. Skew is the time between the earliest and the latest output transition among all outputs for which the same to delay has been selected when all are loaded with the specified load.

- 3. tskewpr is the skew between a pair of outputs (xQo and xQ1) when all eight outputs are selected for 0tu.

- 4. tskewo is the skew between outputs when they are selected for tu.

- 5. For IDT5V991A-2 tskewo is measured with CL = 0pF; for CL = 30pF, tskewo = 0.35ns Max.

- 6. There are 3 classes of outputs: Nominal (multiple of tu delay), Inverted (4Qo and 4Q1 only with 4Fo = 4F1 = HIGH), and Divided (3Qx and 4Qx only in Divide-by-2 or Divide-by-4 mode).

- 7. IDEV is the output-to-output skew between any two devices operating under the same conditions (Vcc, ambient temperature, air flow, etc.)

- 8. tLOCK is the time that is required before synchronization is achieved. This specification is valid only after Vcc is stable and within normal operating limits. This parameter is measured from the application of a new signal or frequency at REF or FB until IPD is within specified limits.

- 9. tpD is measured with REF input rise and fall times (from 0.8V to 2V) of 1ns.

- 10. Measured at 2V.

- 11. Measured at 0.8V.

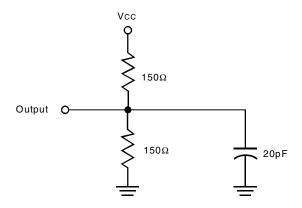

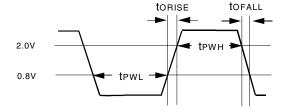

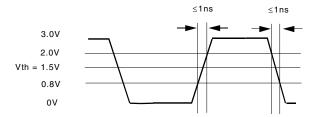

## **ACTEST LOADS AND WAVEFORMS**

Test Load

LVTTL Output Waveform

LVTTL Input Test Waveform

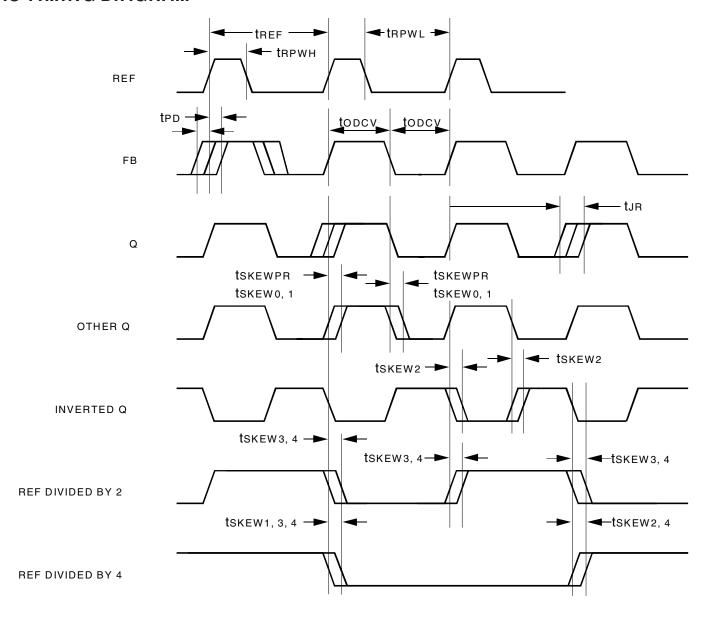

## AC TIMING DIAGRAM

#### NOTES:

Vcco/PE: The AC Timing Diagram applies to Vcco/PE=Vcc. For Vcco/PE=GND, the negative edge of FB aligns with the negative edge of REF, divided outputs change on the negative edge of REF, and the positive edges of the divide-by-2 and the divide-by-4 signals align.

Skew: The time between the earliest and the latest output transition among all outputs for which the same tu delay has been selected when all are loaded with 20pF and terminated with 75Ω to Vcc/2.

tskewpr: The skew between a pair of outputs (xQo and xQ1) when all eight outputs are selected for 0tu.

tskewo: The skew between outputs when they are selected for  $0 t v_{...}$

The output-to-output skew between any two devices operating under the same conditions (Vcc, ambient temperature, air flow, etc.)

todcv: The deviation of the output from a 50% duty cycle. Output pulse width variations are included in tskew2 and tskew4 specifications.

tPWH is measured at 2V.

tPWL is measured at 0.8V.

torise and torall are measured between 0.8V and 2V.

tLOCK: The time that is required before synchronization is achieved. This specification is valid only after Vcc is stable and within normal operating limits. This parameter is measured from the application of a new signal or frequency at REF or FB until tpd is within specified limits.

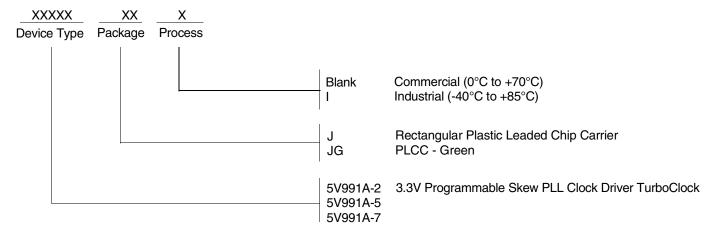

## **ORDERING INFORMATION**

6024 Silver Creek Valley Road San Jose, CA 95138 for SALES:

800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com

for Tech Support: clockhelp@idt.com