Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IFX1040

High Speed CAN-Transceiver with Stand-By Mode and Bus wake-up

# **Data Sheet**

Rev. 1.0, 2011-11-4

# Standard Power

#### **Table of Contents**

## **Table of Contents**

| 1 | <b>Overview</b> 3          |

|---|----------------------------|

| 2 | Pin Configuration          |

| 3 | Block Diagram              |

| 4 | Application Information    |

| 5 | Electrical Characteristics |

| 6 | <b>Diagrams</b>            |

| 7 | Application                |

| 8 | Package Outlines           |

| 9 | Revision History           |

# High Speed CAN-Transceiver with Stand-By Mode and Bus wake-up

IFX1040SJ

### 1 Overview

#### **Features**

- CAN data transmission rate up to 1 MBaud

- Compatible to ISO 11898-2 and ISO 11898-5

- Low power mode with remote wake-up via CAN bus

- Wake signaling by RxD toggle

- No BUS load in stand-by mode

- Wide common mode range for electromagnetic immunity (EMI)

- Digital inputs compatible to 3.3 and 5 V logic devices

- Split termination to stabilize the recessive level

- · TxD time-out function

- Overtemperature protection

- Green Product (RoHS compliant)

PG-DSO-8

#### **Description**

The CAN-transceiver IFX1040SJ is a monolithic integrated circuit in a PG-DSO-8 package for high speed differential mode data transmission (up to 1 Mbaud) and reception in industrial applications. It works as an interface between the CAN protocol controller and the physical bus lines compatible to ISO Standard 11898-2 and ISO Standard 11898-5.

The IFX1040SJ is designed to provide an excellent passive behavior when the transceiver is switched off and a remote wake-up capability via CAN bus in low power mode. This supports networks with partially un-powered nodes.

The IFX1040SJ has two operation modes, the normal and the stand-by mode. These modes can be chosen by the STB pin. If the IFX1040SJ is in stand-by mode and a message on the bus is detected, the IFX1040SJ changes the level at the RxD pin corresponding to the bus signal (wake-up flag).

The IFX1040SJ is designed to withstand the severe conditions of industrial applications.

| Туре      | Package  | Marking |

|-----------|----------|---------|

| IFX1040SJ | PG-DSO-8 | 1040SJ  |

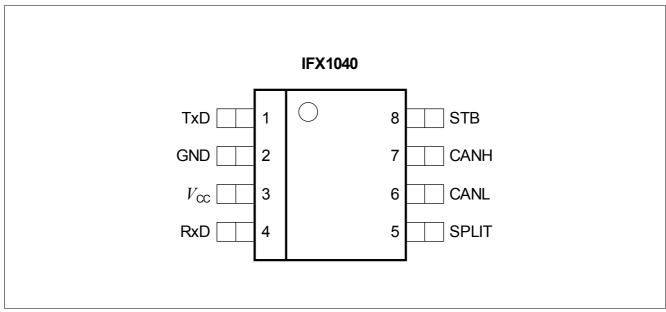

**Pin Configuration**

# 2 Pin Configuration

Figure 1 Pin Configuration IFX1040SJ (top view)

Table 1 Pin Definitions and Functions IFX1040SJ

| Pin No. | Symbol       | Function                                                                          |

|---------|--------------|-----------------------------------------------------------------------------------|

| 1       | TxD          | <b>CAN transmit data input</b> ; 20 kΩ pull-up, LOW in dominant state             |

| 2       | GND          | Ground                                                                            |

| 3       | $V_{\sf CC}$ | 5 V Supply input; 100 nF decoupling capacitor required                            |

| 4       | RxD          | CAN receive data output; LOW in dominant state,                                   |

| 5       | SPLIT        | Split termination output; to support the recessive voltage level of the bus lines |

| 6       | CANL         | Low line I/O; LOW in dominant state                                               |

| 7       | CANH         | High line I/O; HIGH in dominant state                                             |

| 8       | STB          | Mode Control Input; Internal pull-up, see Figure 3                                |

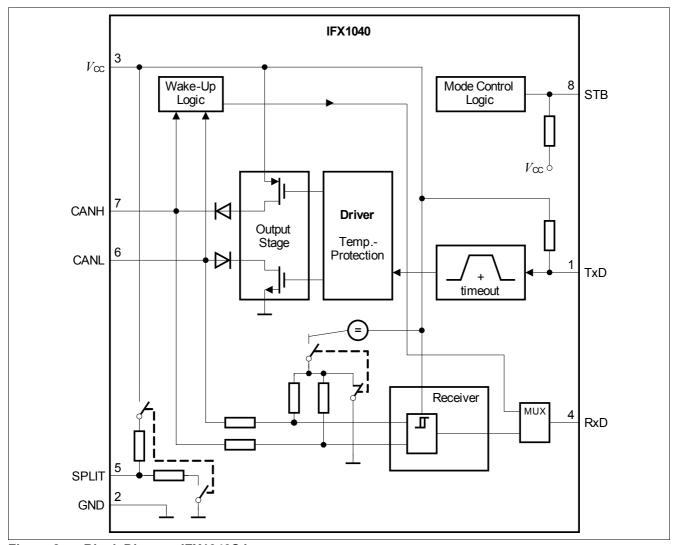

**Block Diagram**

# 3 Block Diagram

Figure 2 Block Diagram IFX1040SJ

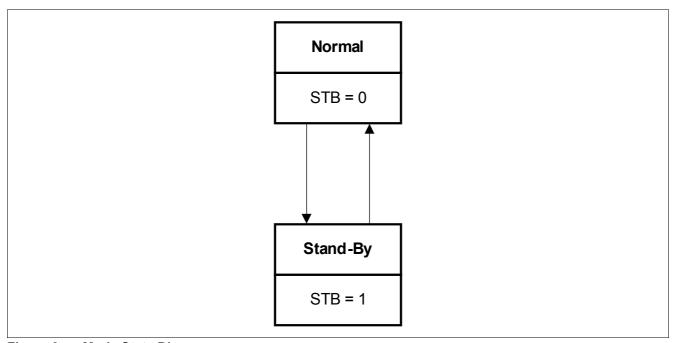

## 4 Application Information

The IFX1040SJ has two operation modes, the normal and the standby mode. These modes can be controlled with the STB pin (see **Figure 3**, **Table 2**). The STB pin has an implemented pull-up, so if there is no signal applied to STB or STB = HIGH, the standby mode is activated. To transfer the IFX1040SJ into the normal mode, STB has to be switched to LOW.

Figure 3 Mode State Diagram

Table 2 Truth Table

| Mode     | STB  | Event                        | RxD                    | <b>BUS Termination</b> |

|----------|------|------------------------------|------------------------|------------------------|

| Normal   | low  | bus dominant                 | low                    | V <sub>CC</sub> /2     |

|          |      | bus recessive                | high                   |                        |

| Stand by | high | wake-up via CAN bus detected | low/high <sup>1)</sup> | GND                    |

|          |      | no wake-up detected          | high                   |                        |

<sup>1)</sup> Signal at RxD changes corresponding to the bus signal during stand by mode. See Figure  $\bf 6$

#### **Normal Mode**

This mode is designed for the normal data transmission/reception within the HS-CAN network.

#### **Transmission**

The signal from the  $\mu$ C is applied to the TxD input of the IFX1040SJ. Now the bus driver switches the CANH/L output stages to transfer this input signal to the CAN bus lines.

#### **TxD Time-out Feature**

If the TxD signal is dominant for a time  $t > t_{TxD}$  the TxD time-out function deactivates the transmitter of the IFX1040. This is realized to prevent the bus from being blocked permanently dominant due to an error like in case of a malfunctioning microcontroller.

The transmission is released again, after a rising edge at TxD has been detected.

As a result of the TxD Time-Out function, the minimum bit rate is limited. The minimum achievable bit rate can be calculated by the maximum number of consecutive dominant bits allowed in the system. It is given by the maximum number of dominant bits allowed in the system divided by the TxD permanent dominant disable time t\_TxD.

#### **Reduced Electromagnetic Emission**

The bus driver has an implemented control to reduce the electromagnetic emission (EME). This is achieved by controlling the symmetry of the slope, resp. of CANH and CANL.

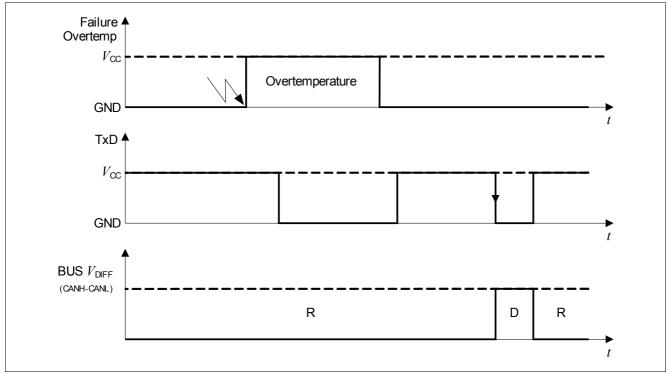

#### Overtemperature

The driver stages are protected against overtemperature. Exceeding the shutdown temperature results in deactivation of the driving stages at CANH/L. To avoid a bit failure after cooling down, the signals can be transmitted again only after a dominant to recessive edge at TxD.

**Figure 4** shows the way how the transmission stage is deactivated and activated again. First an over temperature condition causes the transmission stage to deactivate. After the over temperature condition is no longer present, the transmission is only possible after the TxD signal has changed to recessive level.

Figure 4 Release of the Transmission after Overtemperature

#### Reception

The analog CAN bus signals are converted into a digital signal at RxD via the differential input receiver. The RxD signal is switched to RxD output pin via the multiplexer (MUX), see **Figure 2**.

In normal mode the split pin is used to stabilize the recessive common mode signal.

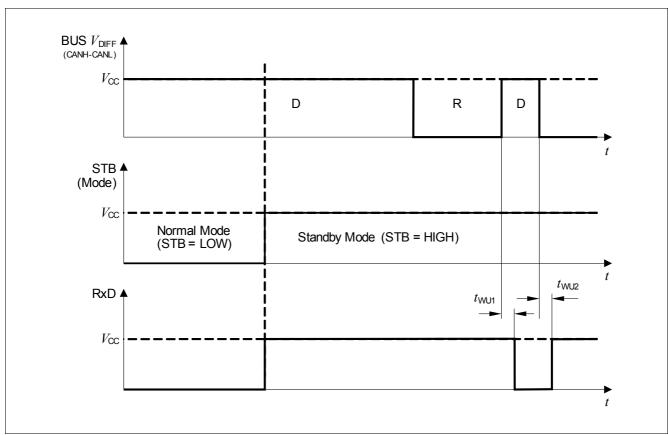

#### **Standby Mode**

The standby mode is designed to switch the IFX1040SJ into a low power mode with minimum current consumption. The driving stages and the receiver are deactivated. Only the relevant circuitry to guarantee a correct handling of the CAN bus wake-up is still active. This wake-up receiver is also designed to show an excellent immunity against electromagnetic noise (EMI).

#### Change into Standby Mode during CAN Bus Failure

It is possible to change from normal mode into the standby mode if the bus is dominant due to a bus failure without setting the RxD wake flag to LOW. The advantage is, that the IFX1040SJ can be kept in the standby mode even if a bus failure occurs.

**Figure 5** shows this mechanism in detail. During a bus network failure, the bus might be dominant. Normal communication is not possible until the failure is removed. To reduce the current consumption, it makes sense to switch over to standby mode. This is possible with the IFX1040SJ. If the dominant signal switches back to recessive level, e.g. failure removed, a wake-up via CAN bus (recessive to dominant signal detected) is possible.

Figure 5 Go-To Standby Mode during Bus Dominant Condition

#### Wake-up via CAN Message

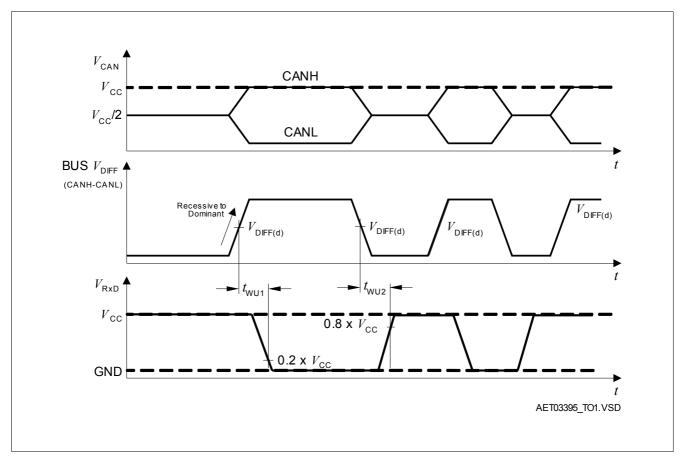

During standby mode, a dominant CAN message on the bus longer than the filtering time  $t > t_{WU1}$ , leads to the activation of the wake-up. The wake-up during standby mode is signaled with the RxD output pin. A dominant signal longer  $t > t_{WU1}$  on the CAN bus switches the RxD level to LOW, with a following recessive signal on the CAN bus longer  $t > t_{WU2}$  the RxD level is switched to high, see **Figure 6**.

The  $\mu C$  is able to detect this change at RxD and switch the transceiver into the normal mode.

Figure 6 Wake-up behavior

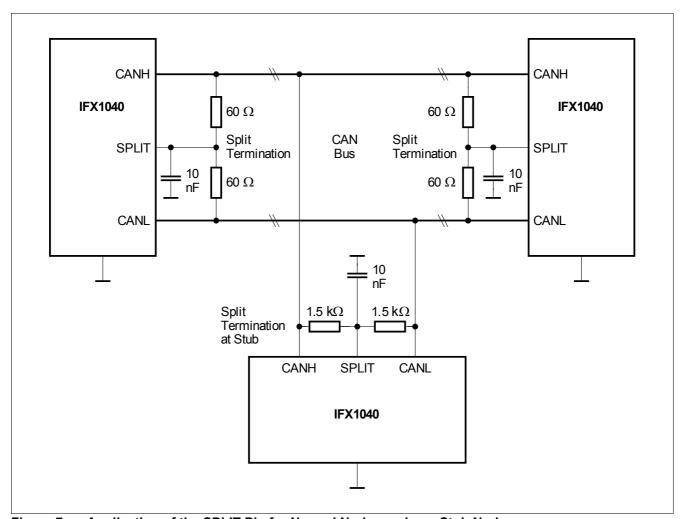

#### **Split Circuit**

The split circuitry is activated during normal mode and deactivated (SPLIT pin floating) during standby mode. The SPLIT pin is used to stabilize the recessive common mode signal in normal mode. This is realized with a stabilized voltage of  $0.5\ V_{CC}$  at SPLIT.

A correct application of the SPLIT pin is shown in **Figure 7**. The split termination for the left and right node is realized with two 60  $\Omega$  resistances and one 10 nF capacitor. The center node in this example is a stub node and the recommended value for the split resistances is 1.5 k $\Omega$ .

Figure 7 Application of the SPLIT Pin for Normal Nodes and one Stub Node

#### **Other Features**

#### Fail Safe

If the device is supplied but there is no signal at the digital inputs, the TxD and STB have an internal pull-up path, to prevent the transceiver to switch into the normal mode or send a dominant signal on the bus.

#### **Un-supplied Node**

The CANH/CANL pins remain high ohmic, if the transceiver is un-supplied.

## **5** Electrical Characteristics

Table 3 Absolute Maximum Ratings

| Parameter                                                    | Symbol          |           | it Values       | Unit | Remarks                                                               |  |

|--------------------------------------------------------------|-----------------|-----------|-----------------|------|-----------------------------------------------------------------------|--|

|                                                              |                 | Min. Max. |                 |      |                                                                       |  |

| Voltages                                                     | "               |           | 1               |      |                                                                       |  |

| Supply voltage                                               | $V_{\sf CC}$    | -0.3      | 5.5             | V    | _                                                                     |  |

| CAN bus voltage (CANH, CANL)                                 | $V_{CANH/L}$    | -32       | 40              | V    | _                                                                     |  |

| CAN bus differential voltage CANH, CANL, SPLIT               | $V_{CAN\;diff}$ | -40       | 40              | V    | CANH - CANL <  40 V <br>CANH - SPLIT <  40 V <br>CANL - SPLIT <  40 V |  |

| Input voltage at SPLIT                                       | $V_{SPLIT}$     | -27       | 40              | V    | _                                                                     |  |

| Logic voltages at STB, TxD, RxD                              | $V_{I}$         | -0.3      | V <sub>CC</sub> | V    | 0 V < V <sub>CC</sub> < 5.5 V                                         |  |

| Electrostatic discharge voltage at CANH, CANL, SPLIT vs. GND | $V_{ESD}$       | -6        | 6               | kV   | Human Body Model<br>(100 pF via 1.5 kW)                               |  |

| Electrostatic discharge voltage                              | $V_{ESD}$       | -2        | 2               | kV   | Human Body Model<br>(100 pF via 1.5 kW)                               |  |

| Temperatures                                                 |                 | 1         |                 |      |                                                                       |  |

| Junction Temperature                                         | $T_{\rm j}$     | -40       | 150             | °C   | _                                                                     |  |

| Storage Temperature                                          | $T_{\rm stg}$   | -50       | 150             | °C   | _                                                                     |  |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

### 5.1 Operating Range

Table 4 Operating Range

| Parameter                             | Symbol             | Lim  | it Values | Unit | Remarks |

|---------------------------------------|--------------------|------|-----------|------|---------|

|                                       |                    | Min. | Max.      |      |         |

| Supply voltage                        | $V_{\sf CC}$       | 4.75 | 5.25      | V    | _       |

| Junction temperature                  | $T_{i}$            | -40  | 125       | °C   | _       |

| Thermal Resistances                   |                    |      |           | '    |         |

| Junction ambient                      | $R_{\text{thi-a}}$ | _    | 185       | K/W  | 1)      |

| Thermal Shutdown (junction temperatur | re)                |      | +         |      |         |

| Thermal shutdown temperature          | $T_{jsD}$          | 150  | 190       | °C   | _       |

| Thermal shutdown hyst.                | $\Delta T$         | _    | 10        | K    | _       |

|                                       |                    |      |           |      |         |

<sup>1)</sup> Calculation of the junction temperature  $T_{\rm j} = T_{\rm amb} + P \times R_{\rm thj-a}$

#### Table 5 Electrical Characteristics

4.75 V <  $V_{\rm CC}$  < 5.25 V;  $R_{\rm L}$  = 60  $\Omega$ ; -40 °C <  $T_{\rm j}$  < 125 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                | Symbol                  | Limit Values                     |                       |                          | Unit | Remarks                                               |

|------------------------------------------|-------------------------|----------------------------------|-----------------------|--------------------------|------|-------------------------------------------------------|

|                                          |                         | Min.                             | Тур.                  | Max.                     |      |                                                       |

| Current Consumption                      |                         | •                                | •                     |                          | '    |                                                       |

| Current consumption                      | $I_{CC}$                | _                                | 6                     | 10                       | mA   | recessive state;<br>$V_{TXD} = V_{CC}$                |

| Current consumption                      | $I_{CC}$                | _                                | 45                    | 70                       | mA   | dominant state;<br>$V_{TxD} = 0 \; V$                 |

| Current consumption                      | $I_{\mathrm{CC,stb}}$   | -                                | 20                    | 30                       | μΑ   | stand-by mode;<br>TxD = high                          |

| Receiver Output RxD                      | l l                     |                                  |                       | "                        |      | 1                                                     |

| HIGH level output current                | $I_{\mathrm{RD,H}}$     | _                                | -4                    | -2                       | mA   | $V_{\rm RD}$ = 0.8 × $V_{\rm CC}$                     |

|                                          |                         | _                                | -100                  | _                        | μA   | stand-by mode                                         |

| LOW level output current                 | $I_{RD,L}$              | 2                                | 4                     | _                        | mA   | $V_{\rm RD}$ = 0.2 × $V_{\rm CC}$                     |

| Short circuit current                    | $I_{\rm SC,RxD}$        | _                                | 15                    | 20                       | mA   | _                                                     |

| Transmission Input TxD                   |                         | 1                                | ·                     |                          | "    |                                                       |

| HIGH level input voltage threshold       | $V_{TD,H}$              | 2.0                              | _                     | _                        | V    | recessive state                                       |

| LOW level input voltage threshold        | $V_{TD,L}$              | _                                | _                     | 8.0                      | V    | dominant state                                        |

| TxD pull-up resistance                   | $R_{TD}$                | 10                               | 20                    | 40                       | kΩ   | _                                                     |

| TxD input hysteresis                     | $V_{TD\;hys}$           | _                                | 200                   | _                        | mV   | _                                                     |

| Stand By Input (pin STB)                 |                         |                                  |                       |                          | '    |                                                       |

| HIGH level input voltage threshold       | $V_{STB,H}$             | 2.0                              | _                     | _                        | V    | normal mode                                           |

| LOW level input voltage threshold        | $V_{\mathrm{STB,L}}$    | _                                | _                     | 0.8                      | V    | receive-only mode                                     |

| STB pull-up resistance                   | $R_{STB}$               | 10                               | 20                    | 40                       | kΩ   | _                                                     |

| STB input hysteresis                     | $V_{\mathrm{STB\;hys}}$ | _                                | 200                   | _                        | mV   | -                                                     |

| Split Termination Output (pin SPLIT)     | •                       |                                  |                       |                          | •    |                                                       |

| Split output voltage                     | $V_{SPLIT}$             | $0.3 \times V_{\rm CC}$          | 0.5 × V <sub>CC</sub> | $V_{\rm CC}$             | V    | normal mode;<br>-500 μA < I <sub>SPLIT</sub> < 500 μΑ |

|                                          | $V_{SPLIT}$             | 0.45<br>× <i>V</i> <sub>CC</sub> | 0.5 ×                 | 0.55×<br>V <sub>CC</sub> | V    | normal mode;<br>no Load                               |

| Leakage current                          | $I_{SPLIT}$             | -5                               | 0                     | 5                        | μА   | standby mode;<br>-22 V < $V_{\rm SPLIT}$ < 35 V       |

| SPLIT output resistance                  | R <sub>SPLIT</sub>      | _                                | 600                   | _                        | Ω    | _                                                     |

| Bus Receiver                             | <br>                    | 1                                | 1                     |                          |      | 1                                                     |

| Differential receiver threshold voltage, | $V_{\rm diff,rdN}$      | _                                | 8.0                   | 0.9                      | V    | recessive to dominant                                 |

| normal mode                              | $V_{diff,drN}$          | 0.5                              | 0.6                   | _                        | V    | dominant to recessive                                 |

| Differential receiver threshold,         | $V_{diff,rdLP}$         |                                  | 0.9                   | 1.15                     | V    | recessive to dominant                                 |

| low power mode                           | $V_{diff,drLP}$         | 0.4                              | 8.0                   |                          | V    | dominant to recessive                                 |

| Common Mode Range                        | CMR                     | -12                              | _                     | 12                       | V    | V <sub>CC</sub> = 5 V                                 |

| Differential receiver hysteresis         | $V_{\mathrm{diff,hys}}$ | _                                | 200                   | _                        | mV   | _                                                     |

| CANH, CANL input resistance              | $R_{i}$                 | 10                               | 20                    | 30                       | kΩ   | recessive state                                       |

| Differential input resistance            | $R_{diff}$              | 20                               | 40                    | 60                       | kΩ   | recessive state                                       |

#### Table 5 Electrical Characteristics (cont'd)

4.75 V <  $V_{\rm CC}$  < 5.25 V;  $R_{\rm L}$  = 60  $\Omega$ ; -40 °C <  $T_{\rm j}$  < 125 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                   | Symbol                   | Limit Values |      |      | Unit | Remarks                                                                             |

|-------------------------------------------------------------|--------------------------|--------------|------|------|------|-------------------------------------------------------------------------------------|

|                                                             |                          | Min.         | Тур. | Max. |      |                                                                                     |

| Bus Transmitter                                             |                          |              |      |      |      | 1                                                                                   |

| CANL/CANH recessive output voltage                          | $V_{CANL/H}$             | 2.0          | 2.5  | 3.0  | V    | $V_{\text{TxD}} = V_{\text{CC}}$ , no load                                          |

| CANH, CANL recessive                                        | $V_{diff}$               | -500         | _    | 50   | mV   | $V_{TXD} = V_{CC};$                                                                 |

| output voltage difference                                   |                          |              |      |      |      | no load                                                                             |

| CANL dominant output voltage                                | $V_{CANL}$               | 0.5          | _    | 2.25 | V    | $V_{TxD}$ = 0 V;<br>$V_{CC}$ = 5 V                                                  |

| CANH dominant output voltage                                | $V_{CANH}$               | 2.75         | _    | 4.5  | V    | $V_{TXD} = 0 \; V;$<br>$V_{CC} = 5 \; V$                                            |

| CANH, CANL dominant output voltage                          | $V_{diff}$               | 1.5          | -    | 3.0  | V    | $V_{TxD} = 0 \; V;$                                                                 |

| difference                                                  |                          |              |      |      |      | $V_{\rm CC}$ = 5 V                                                                  |

| $V_{\text{diff}} = V_{\text{CANH}} - V_{\text{CANL}}$       |                          |              |      |      |      |                                                                                     |

| CANL short circuit current                                  | $I_{CANLsc}$             | 50           | 80   | 200  | mA   | V <sub>CANLshort</sub> = 18 V                                                       |

| CANH short circuit current                                  | $I_{CANHsc}$             | -200         | -80  | -50  | mA   | $V_{\text{CANHshort}} = 0 \text{ V}$                                                |

| Leakage current                                             | $I_{\mathrm{CANH,L,lk}}$ | -            | -    | -5   | μΑ   | $V_{\rm CC}$ = 0 V;                                                                 |

|                                                             |                          |              |      |      |      | $0 \text{ V} < V_{\text{CANH,L}} < 5 \text{ V}$                                     |

| Dynamic CAN-Transceiver Characteristics                     | S                        |              |      |      |      |                                                                                     |

| Propagation delay TxD-to-RxD LOW (recessive to dominant)    | $t_{\sf d(L),TR}$        | _            | 150  | 255  | ns   | $C_{L}$ = 47 pF;<br>$R_{L}$ = 60 $\Omega$ ;<br>$V_{CC}$ = 5 V;                      |

|                                                             |                          |              |      |      |      | $C_{RxD}$ = 15 pF                                                                   |

| Propagation delay TxD-to-RxD HIGH (dominant to recessive)   | $t_{\sf d(H),TR}$        | _            | 150  | 255  | ns   | $C_{L}$ = 47 pF;<br>$R_{L}$ = 60 $\Omega$ ;<br>$V_{CC}$ = 5 V;<br>$C_{RXD}$ = 15 pF |

| Propagation delay<br>TxD LOW to bus dominant                | $t_{d(L),T}$             | _            | 50   | 120  | ns   | $C_{L}$ = 47 pF;<br>$R_{L}$ = 60 $\Omega$ ;<br>$V_{CC}$ = 5 V                       |

| Propagation delay TxD HIGH to bus recessive                 | $t_{d(H),T}$             | _            | 50   | 120  | ns   | $C_{\rm L}$ = 47 pF;<br>$R_{\rm L}$ = 60 $\Omega$ ;<br>$V_{\rm CC}$ = 5 V           |

| Propagation delay bus dominant to RxD LOW                   | $t_{d(L),R}$             | _            | 100  | 135  | ns   | $C_{L}$ = 47 pF;<br>$R_{L}$ = 60 $\Omega$ ;<br>$V_{CC}$ = 5 V;<br>$C_{RXD}$ = 15 pF |

| Propagation delay<br>bus recessive to RxD HIGH              | t <sub>d(H),R</sub>      | -            | 100  | 135  | ns   | $C_{L}$ = 47 pF;<br>$R_{L}$ = 60 $\Omega$ ;<br>$V_{CC}$ = 5 V;<br>$C_{RXD}$ = 15 pF |

| Min. dominant time for bus wake-up signal (RxD high to low) | t <sub>WU1</sub>         | 0.75         | 3    | 5    | μS   | $t_{\text{WU1}} = t_{\text{d(L),R}} + t_{\text{WU}}$<br>see <b>Figure 6</b>         |

### Table 5 Electrical Characteristics (cont'd)

4.75 V <  $V_{\rm CC}$  < 5.25 V;  $R_{\rm L}$  = 60  $\Omega$ ; -40 °C <  $T_{\rm j}$  < 125 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter                                                    | Symbol           | l Limit Values |      |      | Unit | Remarks                                                |

|--------------------------------------------------------------|------------------|----------------|------|------|------|--------------------------------------------------------|

|                                                              |                  | Min.           | Тур. | Max. |      |                                                        |

| Min. recessive time for bus wake-up signal (RxD low to high) | t <sub>WU2</sub> | 0.75           | 3    | 5    | μS   | $t_{WU2} = t_{d(H),R} + t_{WU}$<br>see <b>Figure 6</b> |

| TxD permanent dominant disable time                          | $t_{TxD}$        | 0.3            | _    | 1.0  | ms   | _                                                      |

**Diagrams**

# 6 Diagrams

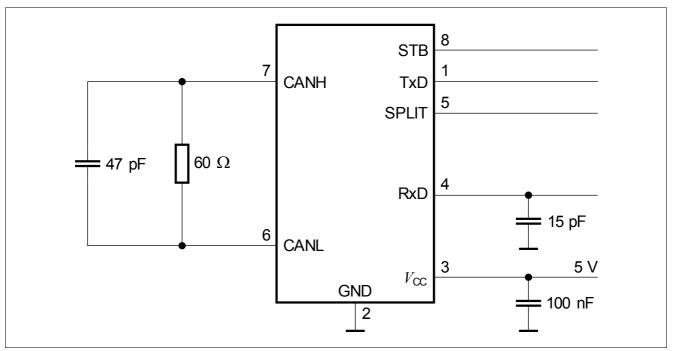

Figure 8 Test Circuit for Dynamic Characteristics

**Diagrams**

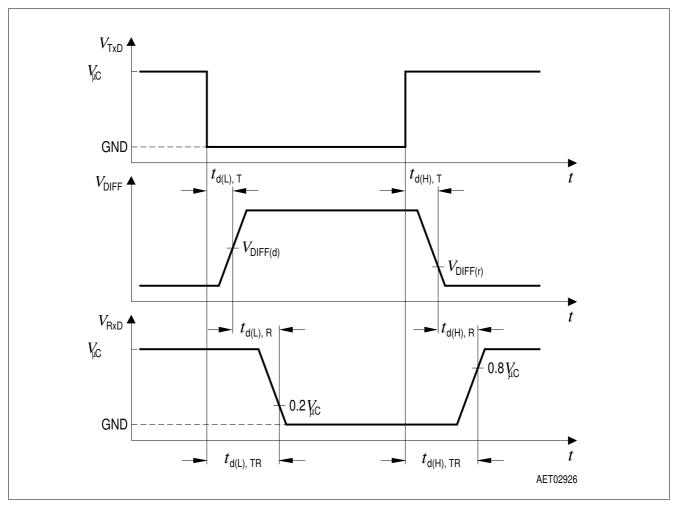

Figure 9 Timing Diagrams for Dynamic Characteristics

**Application**

## 7 Application

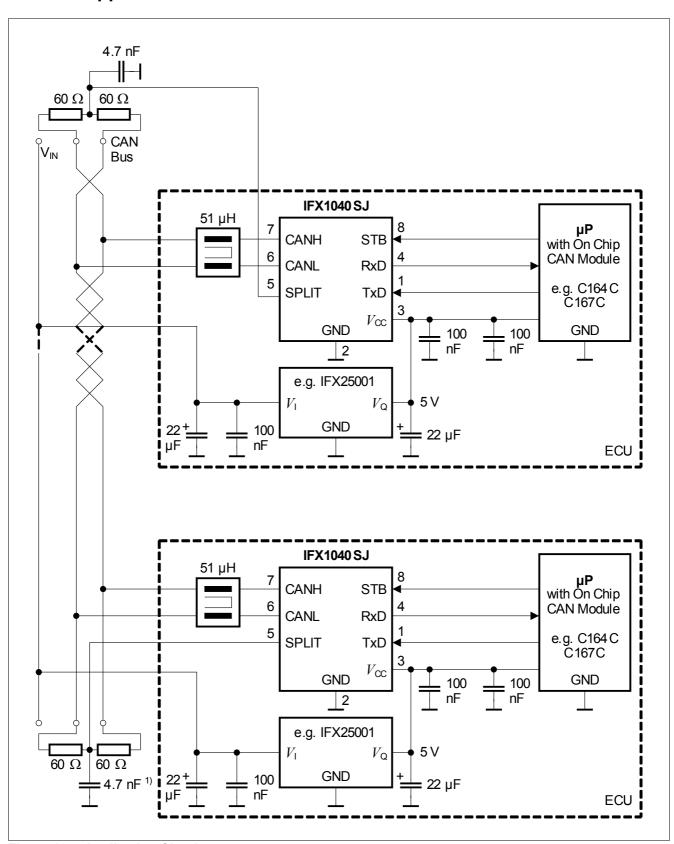

Figure 10 Application Circuit

**Package Outlines**

## 8 Package Outlines

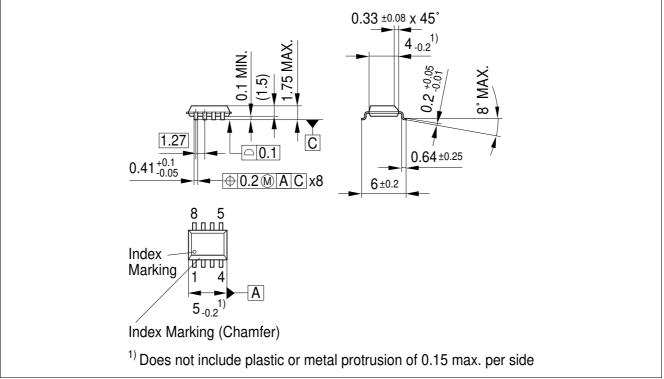

Figure 11 PG-DSO-8 (Plastic Dual Small Outline), lead free version

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

# 9 Revision History

| Revision | Date       | Changes    |

|----------|------------|------------|

| 1.0      | 2011-11-04 | Data Sheet |

Edition 2011-11-4

Published by Infineon Technologies AG 81726 Munich, Germany © 2011 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.