Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

SiC-JFET

Silicon Carbide- Junction Field Effect Transistor

CoolSiC TM

1200 V CoolSiC™ Power Transistor IJW120R100T1

Final Datasheet

Rev. 2.0, <2013-09-11>

### 1200 V Silicon Carbide JFET

### **Description**

CoolSiC™ is Infineon's new family of active power switches based on silicon carbide. Combining the excellent material properties of silicon carbide with our normally-on JFET concept allows the next steps towards higher performance paired with very high ruggedness. The extremely low switching and conduction losses make applications even more efficient, compact, lighter and cooler.

# IJW120R100T1

#### **Features**

- Ultra fast switching

- Internal fast body diode

- Low intrinsic capacitance

- Low gate charge

- 175 °C maximum operating temperature

#### **Benefits**

- Enabling higher system efficiency and/ or higher output power in same housing

- Enabling higher frequency / increased power density solutions

- System cost / space savings due to reduced cooling requirements

- Higher system reliability due to enlarged junction temperatures rates

- Reduced EMI

### **Applications**

- Solar Inverters

- High voltage DC/ DC or AC/ DC conversion

- Bidirectional Inverter

- Compliant for applications according to climate class IEC 60721-3-4 (4K4H)

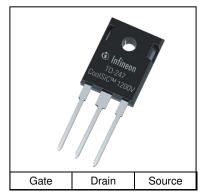

Gate

Pin 1

Drain

Pin 2

Source Pin 3

#### Table 1 Key Performance Parameters

| Parameter                | Value | Unit |

|--------------------------|-------|------|

| $V_{DS}$                 | 1200  | V    |

| R <sub>DS(on) max</sub>  | 100   | mΩ   |

| $Q_{G, typ}$             | 72    | nC   |

| I <sub>D, pulse</sub>    | 78    | Α    |

| E <sub>oss</sub> @ 800 V | 28    | μJ   |

#### Table 2 Pin Definition

| Pin 1 | Pin 2 | Pin 3  |

|-------|-------|--------|

| Gate  | Drain | Source |

| Type / ordering Code | Package    | Marking   | Related links            |  |  |

|----------------------|------------|-----------|--------------------------|--|--|

| IJW120R100T1 1)      | PG-TO247-3 | 120R100T1 | www.infineon.com/CoolSiC |  |  |

# Description

# **Table of Contents**

| Descrip | iption                              | 2  |

|---------|-------------------------------------|----|

| 1       | Application considerations          |    |

| 1.1     | Introduction                        | 4  |

| 1.2     | Driver circuit                      |    |

| 1.3     | Device characteristics              |    |

| 1.3.1   | Gate voltage window                 |    |

| 1.3.2   | Controllability                     | 5  |

| 1.3.3   | Reverse biased behavior             | 6  |

| 1.3.4   | Short circuit ruggedness            |    |

| 1.3.5   | Switching and conduction losses     | 6  |

| 1.4     | Environmental Conditions            |    |

| 2       | Maximum ratings                     | 7  |

| 3       | Thermal characteristics             | 8  |

| 4       | Electrical characteristics          | 8  |

| 5       | Electrical characteristics diagrams | 10 |

| 6       | Test circuits                       | 17 |

| 7       | Package outlines                    | 18 |

| 8       | Revision History                    | 19 |

**Application considerations**

# 1 Application considerations

#### 1.1 Introduction

Wide bandgap semiconductors are very attractive as a basematerial for power devices due to low losses, improved temperature capability and high thermal conductivity. Infineon's silicon carbide schottky diodes have been commercially available on the market for many years. The material and technology knowhow has been used to create new active switches based on silicon carbide providing significant improvement in the value proposition in comparison to known devices such as:

- Resistive forward characteristic in first and third quadrant

- Monolithic integrated body diode, in switching performance very close to SiC schottky barrier diodes

- Very fast and controllable switching transients

- Very low capacitances and gate charge

These benefits result in higher system efficiency, allow higher switching frequencies, increased power density and reduced cooling efforts. Due to the normally-on JFET concept any reliability-relevant issues from gate oxides on SiC are completely avoided. To allow the use of this normally-on concept in voltage-source-inverter configurations we propose the following driver circuit.

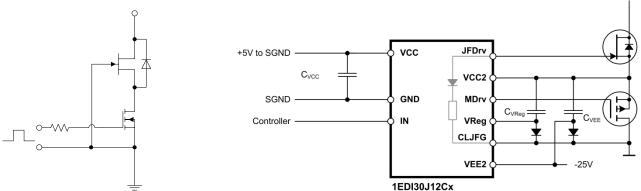

#### 1.2 Driver circuit

Being a normally-on device, the JFET is in its on-state at zero gate voltage and will go into the off-state at negative gate voltage. The normally off behavior can be easily realized by implementing a cascode configuration with a low voltage MOSFET as shown in Figure 1 (state of the art cascode). At e.g. startup, the LV MOSFET is in the off-state pushing the source of the JFET to positive potential relative to its gate and keeping the JFET hence in the off-state.

In this conventional cascode, the LV MOSFET will be switched on and off together with the JFET in each switching cycle. This approach has two major drawbacks: firstly, at turn-on additional switching losses will occur as the output capacitance of the LV MOSFET needs to be charged from the positive rail voltage, secondly the combination allows no direct control of the JFET due to the absence of a (JFET) - Drain- to- (LV MOS) - Gate capacitance. These drawbacks can be avoided with the proposed "direct drive" approach. Here, the JFET is directly switched on and off by applying a negative gate voltage and 0V respectively, whereas the series connected LV MOSFET is always in its on- state. The LV MOSFET is turned off only during start- up and e.g. emergency cases such as loss of auxiliary power supply. This solution represents the best match between performance and safety requirements. The driving scheme with a dedicated driver is shown in Fig. 2 (direct drive technology with 1EDI30J12Cx).

Figure 1: state of the art cascode

Figure 2: direct drive technology with 1EDI30J12Cx

Final Datasheet 4 Rev. 2.0, <2013-09-11>

**Application considerations**

#### 1.3 Device characteristics

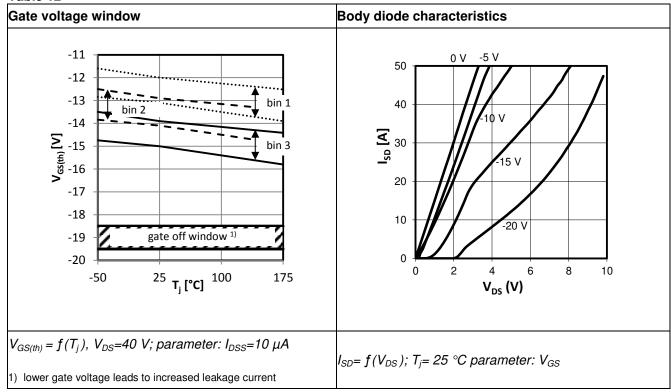

### 1.3.1 Gate voltage window

The gate electrode of the JFET shows, in contrary to isolated MOSFET concepts, a bipolar pn-junction like characteristic: it get's forward biased at around +2.5 V, hence a bipolar current will flow into the gate once the gate- to- source voltage exceeds 2.5 V. This is uncritical and may be used to turn-on the device faster than with the recommended 0 V turn-on. At 25 °C the threshold voltage of the channel can vary between -12 V and -15 V (Figure 3:  $V_{GS(th)}=f(T_j)$  parameter:  $I_{GSS}$ ). The products will be delivered within three groups (bin1, bin2, bin3) of 1 V range each. For paralleling, it is only allowed to parallel devices from the same bin. The use of devices from different bins for paralleling leads to different thermal device behavior. At a voltage of around -23 V the gate-to-source junction enters reverse breakdown, which leads to a temperature dependend bipolar current flow across the junction. In pure voltage driven turn-on and turn-off the lower gate voltage should stay within the window between the pinch-off (threshold) and the punch-through (increased leakage) voltage. For fast and safe turn-off it is strongly recommended to move the lower gate voltage level as close as possible to the punch-through threshold.

Figure 3:  $V_{GS(th)}=f(T_i)$  parameter:  $I_{DSS}=10 \mu A$

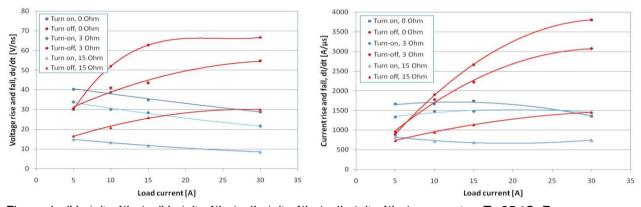

### 1.3.2 Controllability

The JFET can be well controlled through its miller plateau with an external gate resistor ( $Figure~4:~dV_{off}/~dt=f(I_{DS}),~dV_{orf}/~dt=f(I_{DS}),~dI_{off}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),~dI_{orf}/~dt=f(I_{DS}),$

Figure 4:  $dV_{off}/dt = f(I_{DS})$ ,  $dV_{on}/dt = f(I_{DS})$ ,  $dI_{off}/dt = f(I_{DS})$ ,  $dI_{on}/dt = f(I_{DS})$  parameter:  $T_j = 25$  °C,  $R_{G, external}$

Final Datasheet 5 Rev. 2.0, <2013-09-11>

Application considerations

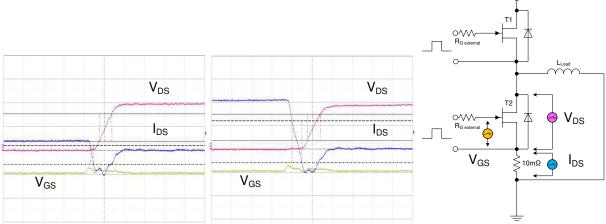

#### 1.3.3 Reverse biased behavior

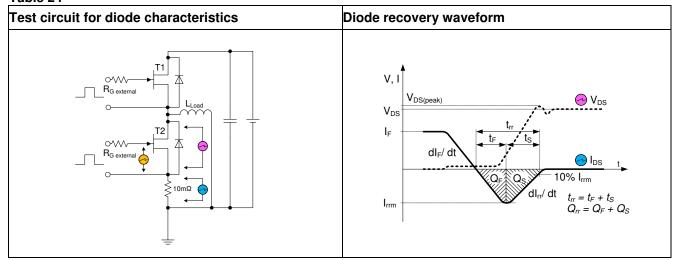

The monolithically integrated body diode shows a switching performance close to that of an external SiC schottky barrier diodes, renowned for their zero reverse recovery characteristic. Figure 5 (reverse recovery characteristic  $I_{SD}$ = 2 A left and  $I_{SD}$ = 10 A;  $T_j$ = 150 °C;  $V_{bulk}$ =400 V;  $R_{G, external}$  = (T1) 3.3  $\Omega$ , (T2) 10  $\Omega$ ) shows the reverse recovery characteristic of the monolithic integrated body diode of the JFET. The reverse recovery charge is load current independent. To avoid any additional losses during hard commutation of the body diode, it is recommended to couple the gate of the switch (acting as diode) with a very low external gate resistor to the gate driver.

Figure 5: reverse recovery characteristic  $I_{SD}$ = 2 A left and  $I_{SD}$ = 10 A;  $T_j$ = 150 °C;  $V_{bulk}$ =400 V;  $R_{G, external}$  = (T1) 3.3  $\Omega$  (T2) 10  $\Omega$

Due to the material properties of SiC the forward voltage drop  $V_f$  of the internal body diode is significantly higher compared to a SiC schottky barrier diode. Therefore, active turn-on of the channel of the JFET during reverse operation (synchronous rectification) is the preferred way of operation.

#### 1.3.4 Short circuit ruggedness

Due to excellent material properties and a very high temperature level for intrinsic carrier generation the device shows extremely good short circuit ruggedness.

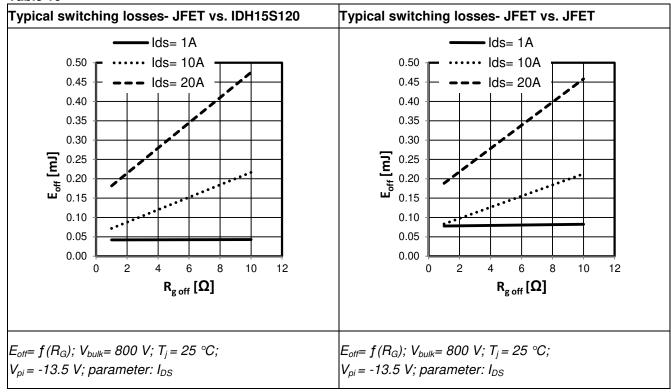

#### 1.3.5 Switching and conduction losses

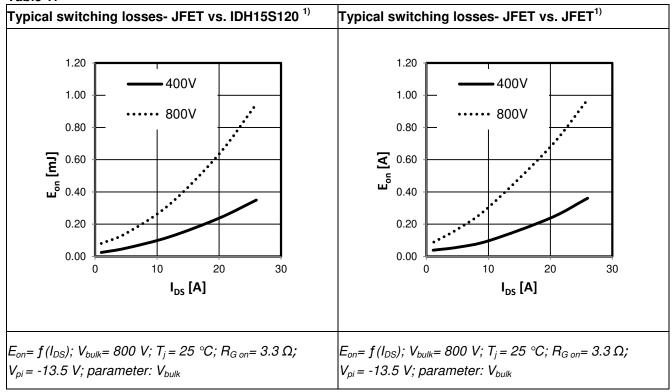

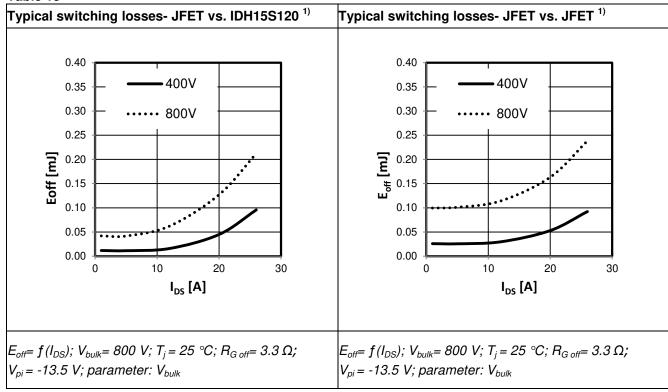

The switching energies are typically one order of magnitude lower than the losses of IGBTs. It is noteworthy to consider that the JFET, as pure majority carrier device, has no forward knee voltage and can be used on its ohmic characteristic both in forward and reverse direction.

Nevertheless, the JFET shows a strong dependency of the switching energies as function of the used gate resistor. A low resistive value of the gate resistor is recommended to operate the JFET at optimal conditions. The conduction losses in comparison to Super Junction MOSFET's are less temperature dependent. A factor of only 1.6 between 25 °C and 100 °C is measurable.

#### 1.4 Environmental Conditions

The parts are proofed according to IEC 60721-3-4 (4K4H). (Low air temperature -20 °C; High air temperature +55 °C; Low relative humitidy 4 %; High relative humitidy 100 %; Low absolute humitidy 0.9 g/  $m^3$ ; High absolute humitidy 36 g/  $m^3$ ...)

Final Datasheet 6 Rev. 2.0, <2013-09-11>

**Maximum ratings**

# 2 Maximum ratings

Table 3 Maximum ratings

| Parameter                           | Symbol                  |       | Values | Unit             | <b>Note/Test Condition</b> |                                                                                  |

|-------------------------------------|-------------------------|-------|--------|------------------|----------------------------|----------------------------------------------------------------------------------|

|                                     |                         | Min.  | Тур.   | Max.             |                            |                                                                                  |

|                                     |                         | _     | 1      | 26               |                            | $V_{GS} = 0 \text{ V}; T_C = 25 \text{ °C};$<br>$R_{thJC} = R_{thJC, max}$       |

| Continuous current, drain source 1) | I <sub>DS</sub>         | _     | _      | 18 <sup>5)</sup> |                            | $V_{GS} = 0 \text{ V}; T_C = 100 \text{ °C};$<br>$R_{thJC} = R_{thJC, max}$      |

|                                     |                         | _     | _      | 10 <sup>5)</sup> |                            | $V_{GS} = 0 \text{ V}; T_C = 150 \text{ °C};$<br>$R_{thJC} = R_{thJC, max}$      |

| Pulsed current, drain source 1)     |                         | _     | _      | 78               | A                          | $V_{GS} = 0 \text{ V; } T_C = 25 \text{ °C;}$ $R_{thJC} = R_{thJC, max}$         |

|                                     | I <sub>DS, pulse</sub>  | _     | _      | 68 <sup>5)</sup> |                            | $V_{GS} = 0 \text{ V}; T_C = 100 \text{ °C};$<br>$R_{thJC} = R_{thJC, max}$      |

|                                     |                         | _     | _      | 60 <sup>5)</sup> |                            | $V_{GS} = 0 \text{ V}; T_C = 150 \text{ °C};$<br>$R_{thJC} = R_{thJC, max}$      |

| Gate source voltage 2)              | $V_{GS}$                | -19.5 | _      | 2                | V                          |                                                                                  |

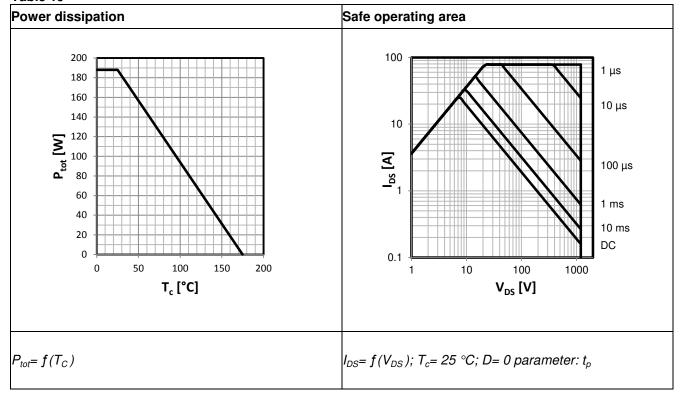

| Power dissipation                   | P <sub>tot</sub>        | _     | -      | 190              | W                          | T <sub>C</sub> = 25 °C                                                           |

| dV/ dt ruggedness, drain source     | dV <sub>DS</sub> ∕ dt   | -     | 1      | 80               | V/ ns                      | $I_{DS} \le I_{DS, pulse}$                                                       |

| D. Landan and Landan darie 1)       | ,                       | _     | 1      | 78               |                            | $V_{GS} = -19.5 \text{ V; } T_j = 25 \text{ °C;}$<br>$R_{thJC} = R_{thJC, max}$  |

| Pulsed current, source drain 1)     | I <sub>SD, pulsed</sub> | _     | ı      | 60 <sup>5)</sup> | A                          | $V_{GS} = -19.5 \text{ V}; T_j = 150 \text{ °C}; $<br>$R_{thJC} = R_{thJC, max}$ |

| dV/ dt ruggedness, source drain     | dV <sub>SD</sub> ∕ dt   | _     | _      | 80               | V/ ns                      | $I_{SD} \le I_{DS, pulse}$                                                       |

| Gate loop resistance, turn off 3)   | $R_{G, off}$            | _     | _      | 5.1              | Ω                          | • •                                                                              |

| Operating and storage temp. 4)      | $T_j;T_{stg}$           | -55   | _      | 175              | °C                         |                                                                                  |

| Mounting torque                     |                         | _     | _      | 60               | Ncm                        | M 2.5 screws                                                                     |

<sup>1)</sup> Limited by T<sub>i, max</sub>

<sup>2)</sup> The device is proofed against  $V_{GS}$  peaks. That allows to drive the parts shortly outside of the given maximum ratings  $(V_{GS, max} = 20 \text{ V}, V_{GS, min} = -50 \text{ V} \textcircled{0} t_{p, max} = 20 \text{ ns})$ . This will result in a temporary gate leakage peak only.

<sup>3)</sup> See application information

<sup>4)</sup> Prolonged storage at high temperatures reduces the lifetime of the product. Tested according to EIA/JESD22-A103D

<sup>5)</sup> Limits derived from product characterization, parameter not measured during production

Thermal characteristics

# 3 Thermal characteristics

Table 4 Thermal characteristics TO-247-3

| Parameter                                                  | Symbol        |      | Values |      | Values |                                       | Unit | Note/Test Condition |

|------------------------------------------------------------|---------------|------|--------|------|--------|---------------------------------------|------|---------------------|

|                                                            |               | Min. | Тур.   | Max. |        |                                       |      |                     |

| Thermal resistance, junction-case                          | $R_{ m thJC}$ | _    | _      | 0.78 |        |                                       |      |                     |

| Thermal resistance, junction-<br>ambient                   | $R_{thJA}$    | _    | _      | 62   | K/W    | leaded                                |      |                     |

| Soldering temperature, wavesoldering only allowed at leads | $T_{sold}$    | _    | _      | 260  | °C     | 1.6 mm (0.063 in.) from case for 10 s |      |                     |

### 4 Electrical characteristics

Table 5 Static characteristics

| Parameter                          | Symbol               |                       | Values |                       | Unit | Note/Test Condition                                        |

|------------------------------------|----------------------|-----------------------|--------|-----------------------|------|------------------------------------------------------------|

|                                    |                      | Min.                  | Тур.   | Max.                  |      |                                                            |

| Breakdown voltage, drain source    | V <sub>(BR)DSS</sub> | 1200                  | _      | _                     |      | $V_{GS}$ = -19.5 V; $I_{DS}$ = 1 mA;<br>$T_{C}$ = -50 °C   |

|                                    |                      | -13.1 <sup>bin1</sup> | _      | -12.0 <sup>bin1</sup> |      |                                                            |

|                                    |                      | -14.1 <sup>bin2</sup> |        | -12.9 <sup>bin2</sup> |      | $I_{DS}$ = 10 $\mu$ A; $V_{DS}$ = 40 V; $T_j$ = 25 °C      |

|                                    |                      | -15.0 <sup>bin3</sup> | ı      | -13.9 <sup>bin3</sup> |      | 1 <sub>j</sub> = 25 C                                      |

| 0)                                 |                      | -13.5 <sup>bin1</sup> | _      | -12.3 <sup>bin1</sup> |      | I <sub>DS</sub> = 10 μA; V <sub>DS</sub> = 40V;            |

| Gate threshold voltage 2)          | $V_{GS(th)}$         | -14.5 <sup>bin2</sup> | _      | -13.2 <sup>bin2</sup> |      | $T_{j=100} \circ C;^{1)}$                                  |

|                                    |                      | -15.4 <sup>bin3</sup> | _      | -14.2 <sup>bin3</sup> |      | 7,- 100 0,                                                 |

|                                    |                      | -13.8 <sup>bin1</sup> | _      | -12.4 <sup>bin1</sup> |      | Ina- 10 UA: Vna- 40 V:                                     |

|                                    |                      | -14.8 <sup>bin2</sup> | _      | -13.3 <sup>bin2</sup> |      | $I_{DS}$ = 10 $\mu$ A; $V_{DS}$ = 40 V; $T_j$ = 150 °C; 1) |

|                                    |                      | -15.7 <sup>bin3</sup> | _      | -14.3 <sup>bin3</sup> |      | 7,- 750 0,                                                 |

| Drain- source leakage current      |                      | _                     | 1.5    | 30                    |      | $V_{DS}$ = 1200 V; $V_{GS}$ = -19.5 V; $T_C$ = 25 °C       |

|                                    | $I_{DSS}$            | _                     | 3      | 60 <sup>1)</sup>      |      | $V_{DS}$ = 1200 V; $V_{GS}$ = -19.5 V; $T_C$ = 100 °C      |

|                                    |                      | _                     | 6      | 120 <sup>1)</sup>     |      | $V_{DS}$ = 1200 V; $V_{GS}$ = -19.5 V; $T_{i}$ = 150 °C    |

|                                    |                      | _                     | _      | 90                    | μΑ   | $V_{DS}$ = 0 V; $V_{GS}$ =-19.5 V; $T_C$ = 25 °C           |

| Gate- source leakage current       | $I_{GSS}$            | _                     | _      | 360 <sup>1)</sup>     |      | $V_{DS}$ = 0 V; $V_{GS}$ = -19.5 V; $T_C$ = 100 °C         |

|                                    |                      | _                     | _      | 720 <sup>1)</sup>     |      | $V_{DS}$ = 0 V; $V_{GS}$ = -19.5 V; $T_C$ = 150 °C         |

| Drain- source on- state resistance |                      | _                     | 0.080  | 0.100                 |      | $V_{GS} = 0 \ V; I_D = 9 \ A;$<br>$T_C = 25 \ ^{\circ}C$   |

|                                    | R <sub>DS(on)</sub>  | _                     | 0.130  | _                     |      | $V_{GS}$ = 0 V; $I_D$ =9 A;<br>$T_C$ = 100 °C              |

|                                    |                      | _                     | 0.175  | _                     | Ω    | $V_{GS}$ = 0 V; $I_D$ =9 A;<br>$T_C$ = 150 °C              |

| Gate resistance                    | $R_G$                | _                     | 1.4    | _                     |      | f=1 MHz, open drain;<br>$T_C=25$ °C                        |

<sup>1)</sup> Limits derived from product characterization, parameter not measured during production

<sup>2)</sup> For paralleling see application note

**Electrical characteristics**

Table 6 Dynamic characteristics

| Parameter                                                  | Symbol             | Symbol Values |      |      | Unit | Note/Test Condition                                                              |

|------------------------------------------------------------|--------------------|---------------|------|------|------|----------------------------------------------------------------------------------|

|                                                            |                    | Min.          | Тур. | Max. |      |                                                                                  |

| Innut considers                                            |                    | _             | 1550 | -    |      | $V_{GS}$ = -19.5 V; $V_{DS}$ = 0 V; $f$ = 1 MHz                                  |

| Input capacitance                                          | $C_{iss}$          | _             | 1200 | _    |      | $V_{GS}$ = -19.5 V; $V_{DS}$ = 800 V; $f$ = 1 MHz                                |

| Output capacitance                                         | 0                  | -             | 1070 | I    | _    | $V_{GS}$ = -19.5 V; $V_{DS}$ = 0 V; $f$ = 1 MHz                                  |

|                                                            | $C_{oss}$          | -             | 80   | -    | pF   | $V_{GS}$ = -19.5 V; $V_{DS}$ = 800 V; $f$ = 1 MHz                                |

| Effective output capacitance, energy related <sup>1)</sup> | $C_{o(er)}$        | -             | 89   | -    |      | $V_{GS}$ = -19.5 V; $V_{DS}$ = 0 V/800 V; $T_C$ =25 °C                           |

| Effective output capacitance, time related <sup>2)</sup>   | $C_{o(tr)}$        | _             | 112  | -    |      | $V_{GS}$ = -19.5 V; $V_{DS}$ = 0 V/800 V; $T_C$ =25 °C                           |

| Turn- on delay time                                        | t <sub>d(on)</sub> | -             | 49   | -    |      | 1/ 222.1/                                                                        |

| Turn- off delay time                                       | $t_{d(off)}$       | -             | 30   | ı    | ] "  | $V_{DS} = 800 \text{ V};$                                                        |

| Rise time                                                  | $t_r$              | _             | 26   | _    | ns   | $V_{GS}$ = -19.5 V/0 V; $I_D$ = 20 A;<br>$T_C$ = 25 °C; $R_{G,tot}$ = 2 $\Omega$ |

| Fall time                                                  | $t_f$              | _             | 19   | _    |      | $1C-20$ $O$ , $1G$ , $tot=2$ $\Omega$                                            |

- 1)  $C_{o(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{oss}$  while  $V_{DS}$  is rising from 0 V to 800 V

- 2)  $C_{o(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{oss}$  while  $V_{DS}$  is rising from 0 V to 800 V

Table 7 Gate charge characteristics

| Parameter                   | Symbol            |      |      |      | Unit | Note/Test Condition                       |

|-----------------------------|-------------------|------|------|------|------|-------------------------------------------|

|                             |                   | Min. | Тур. | Max. |      |                                           |

| Gate charge, gate to source | $Q_{GS}$          | _    | 16   | _    |      |                                           |

| Gate charge, gate to drain  | $Q_{GD}$          | _    | 32   | _    | nC   | $V_{DS}$ = 800 V to 0 V; $I_{DS}$ = 18 A; |

| Gate charge, total          | $Q_G$             | _    | 72   | _    |      | $V_{GS}$ = -19.5 V to 0 V                 |

| Gate plateau voltage        | $V_{\it plateau}$ | _    | -8   | _    | V    |                                           |

Table 8 Reverse diode characteristics

| Parameter                     | Symbol               |      | Values |      | Unit | Note/Test Condition                                                                             |

|-------------------------------|----------------------|------|--------|------|------|-------------------------------------------------------------------------------------------------|

|                               |                      | Min. | Тур.   | Max. |      |                                                                                                 |

|                               |                      | _    | 7.2    | _    |      | $I_{SD} = 18 \text{ A}; V_{GS} = -19.5 \text{ V};$<br>$T_C = 25 ^{\circ}\text{C}$               |

| Diode forward voltage         | $V_{SD}$             | -    | 7.5    | _    | V    | $I_{SD} = 18 \text{ A}; V_{GS} = -19.5 \text{ V};$<br>$T_C = 100 ^{\circ}\text{C}$              |

|                               |                      | -    | 7.6    | _    |      | $I_{SD} = 18 \text{ A}; V_{GS} = -19.5 \text{ V};$<br>$T_C = 150 ^{\circ}\text{C}$              |

| Reverse recovery time         | t <sub>rr</sub>      | _    | 15.6   | _    | ns   |                                                                                                 |

| Reverse recovery charge       | $Q_{rr}$             | =    | 118    |      | nC   |                                                                                                 |

| Peak reverse recovery current | I <sub>rrm</sub>     | _    | 11     | _    | Α    | $I_{SD} = 18 \text{ A}; V_{DS} = 800 \text{ V};$<br>$R_G = 0 \Omega; T_j = 25 ^{\circ}\text{C}$ |

| Current slope forward         | dI <sub>F</sub> ∕ dt | _    | 3      | _    | Λ/22 |                                                                                                 |

| Current slope reverse         | dI₁₁/ dt             | _    | 1.3    | _    | A/ns |                                                                                                 |

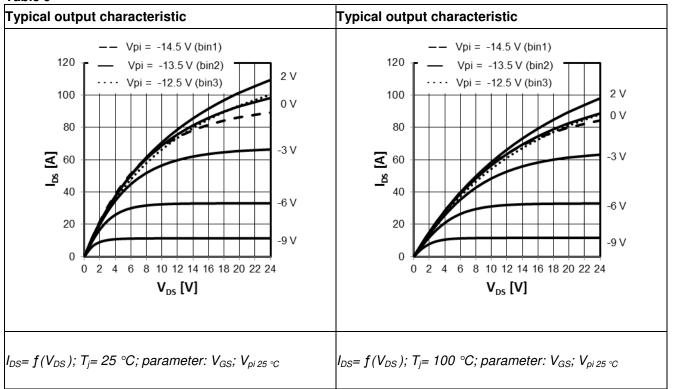

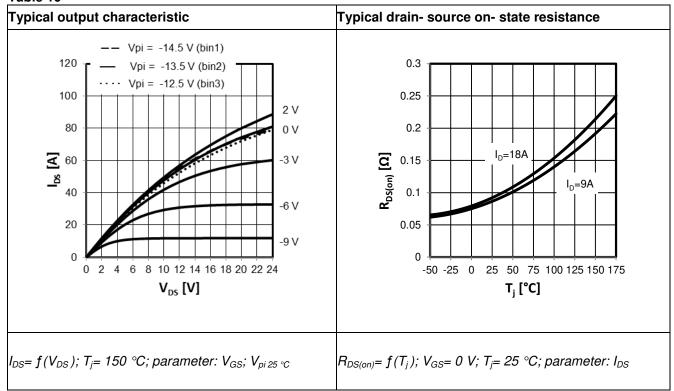

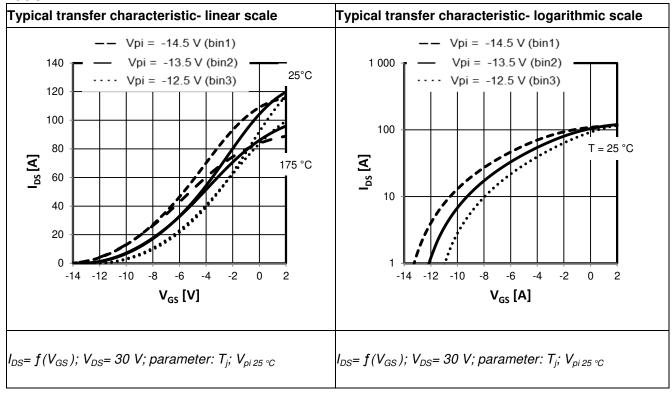

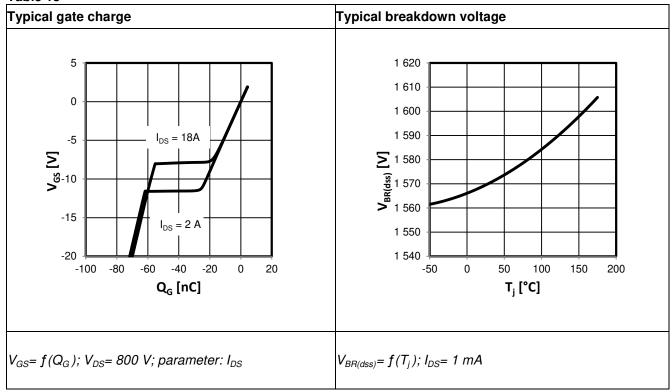

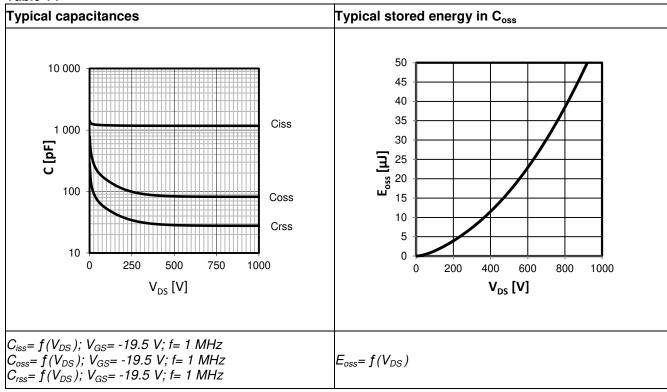

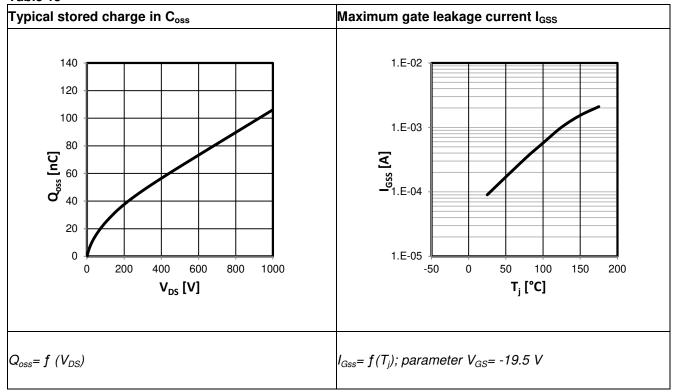

# 5 Electrical characteristics diagrams

Table 9

Table 10

Final Datasheet 10 Rev. 2.0, <2013-09-11>

Table 11

Table 12

Final Datasheet 11 Rev. 2.0, <2013-09-11>

Table 13

Table 14

Final Datasheet 12 Rev. 2.0, <2013-09-11>

Table 15

Table 16

Final Datasheet 13 Rev. 2.0, <2013-09-11>

Table 17

Table 18

<sup>1)</sup> Measured with Push Pull stage close to the gate; Rg =0  $\Omega$

Final Datasheet 14 Rev. 2.0, <2013-09-11>

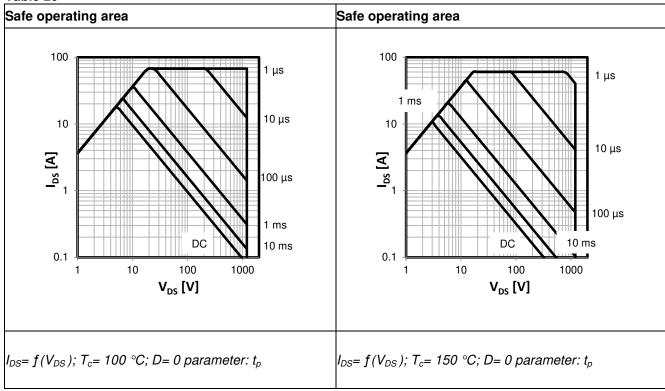

Table 19

Table 20

Final Datasheet 15 Rev. 2.0, <2013-09-11>

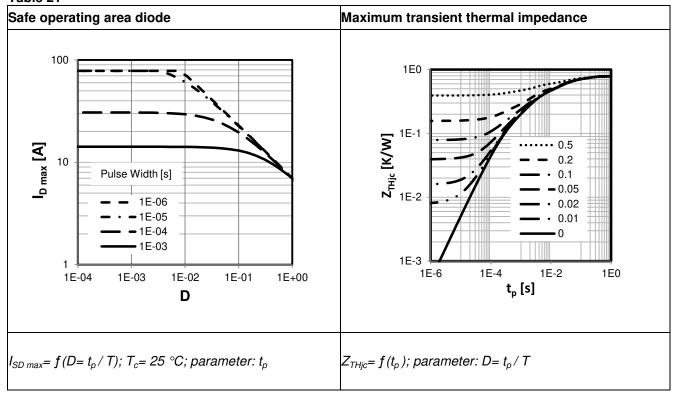

Table 21

**Test circuits**

### 6 Test circuits

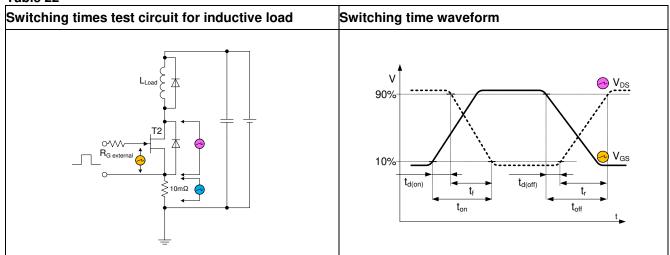

Table 22

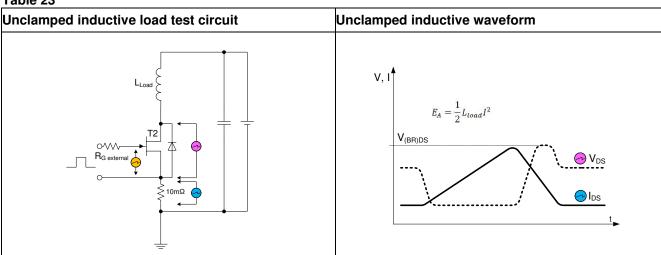

Table 23

Table 24

Package outlines

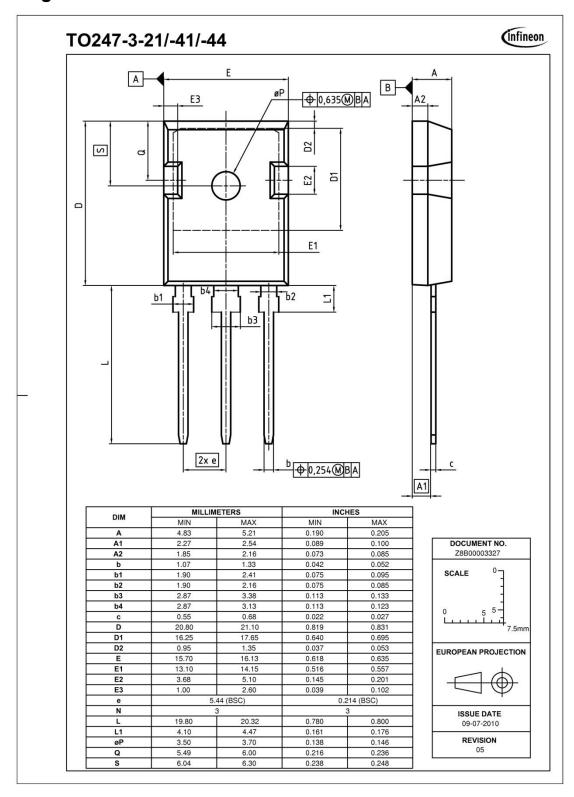

# 7 Package outlines

Figure 1 Outlines PG-TO247-3, dimensions in mm/inches

**Revision History**

## 8 Revision History

IJW120R100T1, 1200 V CoolSiC™ Power Transistor

Revision History: Rev. 2.0, <2013-09-11>

**Previous Revision:**

| Revision | Subjects (major changes since last version) |

|----------|---------------------------------------------|

| 0.9      | Target datasheet                            |

| 1.0      | Preliminary Datasheet                       |

| 2.0      | Final Datasheet                             |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: <a href="mailto:erratum@infineon.com">erratum@infineon.com</a> Edition 2011-12-09 Published by Infineon Technologies AG

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2011 Infineon Technologies AG

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support, automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

w w w .infineon.com