# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Intel<sup>®</sup> Arria<sup>®</sup> 10 Avalon<sup>®</sup>-ST Interface with SR-IOV PCIe\* Solutions User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **17.1**

## Contents

| 1. D  | atasheet                                                                                                             | . 6 |

|-------|----------------------------------------------------------------------------------------------------------------------|-----|

|       | 1.1. Intel <sup>®</sup> Intel <sup>®</sup> Arria <sup>®</sup> 10 Avalon-ST Interface with SR-IOV for PCIe* Datasheet | 6   |

|       | 1.1.1. SR-IOV Features                                                                                               | 7   |

|       | 1.2. Release Information                                                                                             | 9   |

|       | 1.3. Device Family Support                                                                                           | 9   |

|       | 1.4. Debug Features                                                                                                  | 10  |

|       | 1.5. IP Core Verification                                                                                            |     |

|       | 1.5.1. Compatibility Testing Environment                                                                             | .10 |

|       | 1.6. Performance and Resource Utilization                                                                            |     |

|       | 1.7. Recommended Speed Grades for SR-IOV Interface                                                                   |     |

| 2. G  | etting Started with the SR-IOV Design Example                                                                        | 12  |

|       | 2.1. Directory Structure for Intel Arria 10 SR-IOV Design Example                                                    |     |

|       | 2.2. Design Components for the SR-IOV Design Example                                                                 | 12  |

|       | 2.3. Generating the SR-IOV Design Example                                                                            |     |

|       | 2.4. Compiling and Simulating the Design for SR-IOV                                                                  |     |

|       |                                                                                                                      |     |

| 3. Pa | arameter Settings                                                                                                    |     |

|       | 3.1. Parameters                                                                                                      | 16  |

|       | 3.2. Intel Arria 10 Avalon-ST Settings                                                                               |     |

|       | 3.3. Intel Arria 10 SR-IOV System Settings                                                                           | 18  |

|       | 3.4. Base Address Register (BAR) Settings                                                                            |     |

|       | 3.5. SR-IOV Device Identification Registers                                                                          |     |

|       | 3.6. Intel Arria 10 Interrupt Capabilities                                                                           |     |

|       | 3.7. Physical Function TLP Processing Hints (TPH)                                                                    |     |

|       | 3.8. Address Translation Services (ATS)                                                                              |     |

|       | 3.9. PCI Express and PCI Capabilities Parameters                                                                     |     |

|       | 3.9.1. PCI Express and PCI Capabilities                                                                              |     |

|       | 3.9.2. Error Reporting                                                                                               |     |

|       | 3.9.3. Link Capabilities                                                                                             |     |

|       | 3.9.4. Slot Capabilities                                                                                             |     |

|       | 3.9.5. Power Management                                                                                              |     |

|       | 3.10. PHY Characteristics                                                                                            |     |

|       | 3.11. Example Designs                                                                                                | .27 |

| 4. P  | hysical Layout                                                                                                       | 28  |

|       | 4.1. Hard IP Block Placement In Intel Cyclone 10 GX Devices                                                          | 28  |

|       | 4.2. Hard IP Block Placement In Intel Arria 10 Devices                                                               |     |

|       | 4.3. Channel and Pin Placement for the Gen1, Gen2, and Gen3 Data Rates                                               | 32  |

|       | 4.4. Channel Placement and fPLL and ATX PLL Usage for the Gen3 Data Rate                                             |     |

|       | 4.5. PCI Express Gen3 Bank Usage Restrictions                                                                        |     |

| 5. I  | nterfaces and Signal Descriptions                                                                                    | 37  |

|       | 5.1. Avalon-ST TX Interface                                                                                          |     |

|       | 5.2. Component-Specific Avalon-ST Interface Signals                                                                  |     |

|       | 5.3. Avalon-ST RX Interface                                                                                          |     |

|       | 5.4. BAR Hit Signals                                                                                                 |     |

|       | 5.5. Configuration Status Interface                                                                                  |     |

| I<br>S | 5.6. Clock Signals                                                                   | .46 |

|--------|--------------------------------------------------------------------------------------|-----|

|        | 5.7. Function-Level Reset (FLR) Interface                                            |     |

|        | 5.8. SR-IOV Interrupt Interface                                                      |     |

|        | 5.9. Implementing MSI-X Interrupts                                                   |     |

|        | 5.10. Control Shadow Interface                                                       |     |

|        | 5.11. Local Management Interface (LMI) Signals                                       |     |

|        | 5.12. Reset, Status, and Link Training Signals                                       |     |

|        | 5.13. Hard IP Reconfiguration Interface                                              |     |

|        | 5.14. Serial Data Signals                                                            |     |

|        | 5.15. Test Signals                                                                   |     |

|        | 5.16. PIPE Interface Signals                                                         |     |

| 1      | 5.17. Intel Arria 10 Development Kit Conduit Interface                               | 66  |

| 6. Reg | isters                                                                               | 68  |

| 6      | 6.1. Addresses for Physical and Virtual Functions                                    | 68  |

| 6      | 6.2. Correspondence between Configuration Space Registers and the PCIe Specification | 72  |

|        | 6.3. PCI and PCI Express Configuration Space Registers                               |     |

|        | 6.3.1. Type 0 Configuration Space Registers                                          | 73  |

|        | 6.3.2. PCI and PCI Express Configuration Space Register Content                      | 74  |

|        | 6.3.3. Interrupt Line and Interrupt Pin Register                                     |     |

| 6      | 6.4. MSI Registers                                                                   | 75  |

| 6      | 6.5. MSI-X Capability Structure                                                      | 77  |

| 6      | 6.6. Power Management Capability Structure                                           | 78  |

| 6      | 6.7. PCI Express Capability Structure                                                | 79  |

| 6      | 6.8. Advanced Error Reporting (AER) Enhanced Capability Header Register              | 83  |

| 6      | 6.9. Uncorrectable Error Status Register                                             | 83  |

| 6      | 6.10. Uncorrectable Error Mask Register                                              | 84  |

| 6      | 6.11. Uncorrectable Error Severity Register                                          | .84 |

| 6      | 6.12. Correctable Error Status Register                                              | 85  |

| 6      | 6.13. Correctable Error Mask Register                                                | 85  |

|        | 6.14. Advanced Error Capabilities and Control Register                               |     |

| 6      | 6.15. Header Log Registers 0-3                                                       | 86  |

| 6      | 6.16. SR-IOV Virtualization Extended Capabilities Registers                          | 87  |

|        | 6.16.1. SR-IOV Virtualization Extended Capabilities Registers Address Map            |     |

|        | 6.16.2. ARI Enhanced Capability Header                                               | .89 |

|        | 6.16.3. SR-IOV Enhanced Capability Registers                                         | .90 |

|        | 6.16.4. Initial VFs and Total VFs Registers                                          |     |

|        | 6.16.5. VF Device ID Register                                                        |     |

|        | 6.16.6. Page Size Registers                                                          | 91  |

|        | 6.16.7. VF Base Address Registers (BARs) 0-5                                         | 92  |

|        | 6.16.8. Secondary PCI Express Extended Capability Header                             | 92  |

|        | 6.16.9. Lane Status Registers                                                        |     |

|        | 6.16.10. Transaction Processing Hints (TPH) Requester Enhanced Capability Header     | .93 |

|        | 6.16.11. TPH Requester Capability Register                                           | 94  |

|        | 6.16.12. TPH Requester Control Register                                              |     |

|        | 6.16.13. Address Translation Services ATS Enhanced Capability Header                 |     |

|        | 6.16.14. ATS Capability Register and ATS Control Register                            |     |

| e      | 6.17. Virtual Function Registers                                                     | 95  |

| 7. Res | et and Clocks                                                                        | 99  |

| 7      | 7.1. Reset Sequence for Hard IP for PCI Express IP Core and Application Layer        | 99  |

| <ul> <li>7.2. Function Level Reset (FLR)</li> <li>7.3. Clocks</li> <li>7.3.1. Clock Domains</li> <li>7.3.2. Clock Summary</li> </ul>                                                                                                                                                                                                                                                                                        | 101<br>101                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| <ul> <li>8. Programming and Testing SR-IOV Bridge MSI Interrupts</li></ul>                                                                                                                                                                                                                                                                                                                                                  | 104<br>.104                                                               |

| 9. Error Handling                                                                                                                                                                                                                                                                                                                                                                                                           | 107                                                                       |

| <ul> <li>9.1. Physical Layer Errors</li> <li>9.2. Data Link Layer Errors</li> <li>9.3. Transaction Layer Errors</li> <li>9.4. Error Reporting and Data Poisoning</li> <li>9.5. Uncorrectable and Correctable Error Status Bits</li> </ul>                                                                                                                                                                                   | 108<br>.108<br>109                                                        |

| 10. IP Core Architecture                                                                                                                                                                                                                                                                                                                                                                                                    | 112                                                                       |

| <ul> <li>10.1. PCI Express Protocol Stack</li> <li>10.2. PCI Express Protocol Stack</li> <li>10.3. Data Link Layer</li> <li>10.4. Physical Layer</li> <li>10.5. Top-Level Interfaces</li> <li>10.5.1. Avalon-ST Interface</li> <li>10.5.2. Clocks and Reset</li> <li>10.5.3. Interrupts</li> <li>10.5.4. PIPE</li> <li>10.6. Intel Arria 10 Hard IP for PCI Express with Single-Root I/O Virtualization (SR-IOV)</li> </ul> | 113<br>114<br>115<br>118<br>118<br>119<br>.120<br>120                     |

| 11. Design Implementation                                                                                                                                                                                                                                                                                                                                                                                                   | 123                                                                       |

| 11.1. Making Pin Assignments to Assign I/O Standard to Serial Data Pins<br>11.2. Recommended Reset Sequence to Avoid Link Training Issues<br>11.3. SDC Timing Constraints                                                                                                                                                                                                                                                   | .124                                                                      |

| 12. Debugging                                                                                                                                                                                                                                                                                                                                                                                                               | 125                                                                       |

| <ul> <li>12.1. Setting Up Simulation</li></ul>                                                                                                                                                                                                                                                                                                                                                                              | 125<br>126<br>126<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>128 |

| A. Transaction Layer Packet (TLP) Header Formats                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

| A.1. TLP Packet Formats without Data Payload<br>A.2. TLP Packet Formats with Data Payload                                                                                                                                                                                                                                                                                                                                   |                                                                           |

| B. Intel Arria 10 Avalon-ST with SR-IOV Interface for PCIe Solutions User Guide<br>Archive                         |     |  |

|--------------------------------------------------------------------------------------------------------------------|-----|--|

| C. Document Revision History                                                                                       | 135 |  |

| C.1. Document Revision History for the Intel Arria 10 Avalon-ST Interface with SR-IOV<br>PCIe Solutions User Guide | 135 |  |

## **1. Datasheet**

# **1.1.** Intel<sup>®</sup> Intel<sup>®</sup> Arria<sup>®</sup> **10** Avalon-ST Interface with SR-IOV for PCIe\* Datasheet

Intel<sup>®</sup> Intel Arria<sup>®</sup> 10 FPGAs include a configurable, hardened protocol stack for PCI Express\* that is compliant with *PCI Express Base Specification 2.1 or 3.0*. The Intel Arria 10 Hard IP for PCI Express with Single Root I/O Virtualization (SR-IOV) IP core consists of this hardened protocol stack and the SR-IOV soft logic. The SR-IOV soft logic uses the Configuration Space Bypass mode of the Hard IP to bypass the internal configuration block and BAR matching logic. These functions are implemented in external soft logic. Soft logic in the SR-IOV Bridge also implements interrupts and error reporting.

In 16.0, SR-IOV Bridge was redesigned to support up to 4 Physical Functions (PFs) and 2048 Virtual Functions (VFs). The SR-IOV bridge also supports the Address Translation Services (ATS) and TLP Processing Hints (TPH) capabilities.

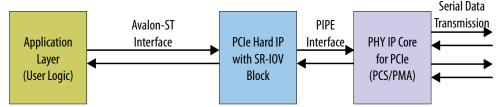

## Figure 1. Intel Arria 10 PCIe Variant with SR-IOV

The following figure shows the high-level modules and connecting interfaces for this variant.

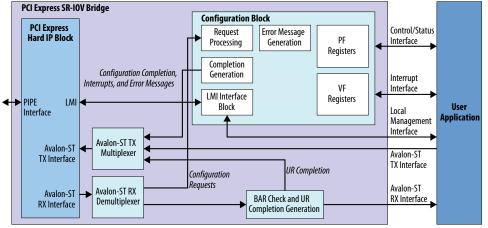

### Figure 2. Intel Arria 10 PCIe Variant with SR-IOV

The following figure provides the next level of detail for the modules that comprise the SR-IOV Bridge.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

## Table 2. PCI Express Data Throughput

The following table shows the aggregate bandwidth of a PCI Express link for Gen2 x4. The protocol specifies 2.5 giga-transfers per second for Gen1, 5.0 giga-transfers per second for Gen2. This table provides bandwidths for a single transmit (TX) or receive (RX) channel. The numbers double for duplex operation. Gen1 and Gen2 use 8B/10B encoding which introduces a 20% overhead.

|                                                 | Link Width |

|-------------------------------------------------|------------|

|                                                 | ×4         |

| PCI Express Gen2 (5.0 Gbps) - 256-bit interface | N/A        |

#### Table 3.PCI Express Data Throughput

The following table shows the aggregate bandwidth of a PCI Express link for Gen2 and Gen3 for supported link widths. The protocol specifies 2.5 giga-transfers per second for Gen1, 5.0 giga-transfers per second for Gen2, and 8.0 giga-transfers per second for Gen3. This table provides bandwidths for a single transmit (TX) or receive (RX) channel. The numbers double for duplex operation. Gen1 and Gen2 use 8B/10B encoding which introduces a 20% overhead. In contrast, Gen3 uses 128b/130b encoding which reduces the data throughput lost to encoding to about 1.5%.

|                                                 | Link Width |    |  |

|-------------------------------------------------|------------|----|--|

|                                                 | ×4         | ×8 |  |

| PCI Express Gen2 (5.0 Gbps) - 256-bit interface | N/A        | 32 |  |

| PCI Express Gen3 (8.0 Gbps) - 256-bit interface | 31.51      | 63 |  |

#### **Related Information**

- Introduction to Intel FPGA IP Cores

Provides general information about all Intel FPGA IP cores, including

parameterizing, generating, upgrading, and simulating IP cores.

- Creating Version-Independent IP and Platform Designer Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- Project Management Best Practices Guidelines for efficient management and portability of your project and IP files.

- Intel Arria 10 Avalon-ST with SR-IOV Interface for PCIe Solutions User Guide Archive on page 134

- Avalon Interface Specifications For information about the Avalon-ST interface protocol.

- Arria 10 Avalon-ST Interface for PCIe Solutions User Guide For the Avalon-ST interface to the application without SR-IOV.

- PCI Express Base Specification 3.0

## **1.1.1. SR-IOV Features**

New features in the Intel Quartus Prime 17.1 release:

• Added parameter to invert TX polarity.

The Intel Arria 10 Hard IP for PCI Express with SR-IOV supports the following features:

- Support for  $\times 4$ , and  $\times 8$  configurations with Gen2 or Gen3 lane rates for Endpoints

- Configuration Spaces for up to four PCIe Physical Functions (PFs) and a maximum of 2048 Virtual Functions (VFs) for the PFs

- Base address register (BAR) checking logic

- Dedicated 16 kilobyte (KB) receive buffer ٠

- Platform Designer example designs demonstrating parameterization, design modules, and connectivity

- Extended credit allocation settings to better optimize the RX buffer space based on application type

- Support for Advanced Error Reporting (AER) for PFs

- Support for Address Translation Services (ATS) and TLP Processing Hints (TPH) ٠ capabilities

- Support for a Control Shadow Interface to read the current settings for some of the VF Control Register fields in the PCI and PCI Express Configuration Spaces

- Support for Configuration Space Bypass Mode, allowing you to design a custom Configuration Space and support multiple functions

- Support for Function Level Reset (FLR) for PFs and VFs

- Support for Gen3 PIPE simulation

- Support for the following interrupt types:

- Message signaled interrupts (MSI) for PFs

- MSI-X for PFs and VFs

- Legacy interrupts for PFs

- Easy to use:

- Flexible configuration.

- Example designs to get started.

The Intel Arria 10 Avalon-ST Interface with SR-IOV PCIe Solutions User Guide explains how to use this IP core and not the PCI Express protocol. Although there is inevitable overlap between these two purposes, use this document only in conjunction with an understanding of the PCI Express Base Specification.

Note: This release provides separate user guides for the different variants.

#### **Related Information**

- Arria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide For the Avalon-MM interface and DMA functionality.

- Arria 10 Avalon-MM Interface for PCIe Solutions User Guide For the Avalon-MM interface with no DMA.

- Arria 10 Avalon-ST Interface for PCIe Solutions User Guide For the Avalon-ST interface.

## **1.2. Release Information**

#### Table 4. Hard IP for PCI Express Release Information

| Item           | Description                                       |  |

|----------------|---------------------------------------------------|--|

| Version        | 17.1                                              |  |

| Release Date   | November 2017                                     |  |

| Ordering Codes | Primary: IP-PCIE/SRIOV<br>Renewal: IPR-PCIE/SRIOV |  |

| Product IDs    | 00FB                                              |  |

| Vendor ID      | 6AF7                                              |  |

Intel verifies that the current version of the Quartus Prime software compiles the previous version of each IP core, if this IP core was included in the previous release. Intel reports any exceptions to this verification in the *Intel IP Release Notes* or clarifies them in the Quartus Prime IP Update tool. Intel does not verify compilation with IP core versions older than the previous release.

#### **Related Information**

- Intel FPGA IP Release Notes Provides release notes for the current and past versions Intel FPGA IP cores.

- Errata for the Intel Arria 10 Hard IP for PCI Express IP Core in the Knowledge Base

## **1.3. Device Family Support**

The following terms define device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- **Preliminary support**—the IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- **Final support**—the IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

#### Table 5.Device Family Support

| Device Family                                                                                                                  | Support Level |

|--------------------------------------------------------------------------------------------------------------------------------|---------------|

| Intel Arria 10                                                                                                                 | Final.        |

| Other device families Refer to the Intel's PCI Express IP Solutions web page for support information on other device families. |               |

## **Related Information**

PCI Express Solutions Web Page

## **1.4. Debug Features**

Debug features allow observation and control of the Hard IP for faster debugging of system-level problems.

## **Related Information**

Debugging on page 125

## 1.5. IP Core Verification

To ensure compliance with the PCI Express specification, Intel performs extensive verification. The simulation environment uses multiple testbenches that consist of industry-standard bus functional models (BFMs) driving the PCI Express link interface. Intel performs the following tests in the simulation environment:

- Directed and pseudorandom stimuli test the Application Layer interface, Configuration Space, and all types and sizes of TLPs

- Error injection tests inject errors in the link, TLPs, and Data Link Layer Packets (DLLPs), and check for the proper responses

- PCI-SIG<sup>®</sup> Compliance Checklist tests that specifically test the items in the checklist

- Random tests that test a wide range of traffic patterns

Intel provides example designs that you can leverage to test your PCBs and complete compliance base board testing (CBB testing) at PCI-SIG, upon request.

## 1.5.1. Compatibility Testing Environment

Intel has performed significant hardware testing to ensure a reliable solution. In addition, Intel internally tests every release with motherboards and PCI Express switches from a variety of manufacturers. All PCI-SIG compliance tests are run with each IP core release.

## 1.6. Performance and Resource Utilization

Because the PCIe protocol stack is implemented in hardened logic, it uses no core device resources (no ALMs and no embedded memory).

The SR-IOV Bridge is implemented is soft logic, requiring FPGA fabric resources. The following table shows the typical device resource utilization for selected configurations using the current version of the Quartus Prime software. With the exception of M20K memory blocks, the numbers of ALMs and logic registers are rounded up to the nearest 50.

| Number of PFs and VFs | ALMs       | M20K Memory Blocks | Logic Registers |

|-----------------------|------------|--------------------|-----------------|

| 1 PF, 4 VFs           | 2350       | 0                  | 5200            |

| 2 PFs, 4 VFs          | 3600       | 0                  | 6500            |

|                       | - <b>1</b> |                    | continued       |

| Number of PFs and VFs | ALMs  | M20K Memory Blocks | Logic Registers |

|-----------------------|-------|--------------------|-----------------|

| 4 PFs, 4 VFs          | 4650  | 0                  | 7700            |

| 1 PF, 2048 VFs        | 10350 | 0                  | 5700            |

| 2 PFs, 2048 VFs       | 11750 | 0                  | 7500            |

| 4 PFs 2048 VFs        | 14150 | 0                  | 10650           |

| 2 PFs                 | 2300  | 0                  | 5100            |

| 4 PFs                 | 3450  | 0                  | 6300            |

#### **Related Information**

Running the Fitter

For information on Fitter constraints.

## **1.7. Recommended Speed Grades for SR-IOV Interface**

### Table 7. Intel Arria 10 Recommended Speed Grades for All SR-IOV Configurations

Intel recommends setting the Quartus Prime Analysis & Synthesis Settings **Optimization Technique** to **Speed** when the Application Layer clock frequency is 250 MHz. For information about optimizing synthesis, refer to "Setting Up and Running Analysis and Synthesis in Quartus Prime Help. For more information about how to effect the **Optimization Technique** settings, refer to Area and Timing Optimization in volume 2 of the *Quartus Prime Handbook*. Refer to the *Related Links* below.

| Link Rate | Link Width | Interface<br>Width | Application Clock Frequency<br>(MHz) | Recommended Speed Grades |

|-----------|------------|--------------------|--------------------------------------|--------------------------|

| Gen2      | ×8         | 256 bits           | 125                                  | -1, -2, -3               |

| Gen3      | ×4         | 256 bits           | 125                                  | -1, -2, -3               |

| Gens      | ×8         | 256 bits           | 250                                  | -1, -2                   |

#### Table 8. Intel Arria 10 Recommended Speed Grades for All SR-IOV Configurations

Intel recommends setting the Quartus Prime Analysis & Synthesis Settings **Optimization Technique** to **Speed** when the Application Layer clock frequency is 250 MHz. For information about optimizing synthesis, refer to "Setting Up and Running Analysis and Synthesis in Quartus Prime Help. For more information about how to effect the **Optimization Technique** settings, refer to Area and Timing Optimization in volume 2 of the *Quartus Prime Handbook*. Refer to the *Related Links* below.

| Link Rate | Link Width | Interface<br>Width | Application Clock Frequency<br>(MHz) | Recommended Speed Grades |

|-----------|------------|--------------------|--------------------------------------|--------------------------|

| Gen2      | ×4         | 64 bits<br>128     | 125                                  | -1, -2, -3               |

#### **Related Information**

- Running Synthesis For settings that affect timing closure.

- Intel FPGA Software Installation and Licensing Manual For comprehensive information for installing and licensing Intel FPGA software.

## 2. Getting Started with the SR-IOV Design Example

The SR-IOV example design consists of a PCIe Endpoint that includes an SR-IOV bridge configured for one PF and four VFs. The example design also includes a basic application to facilitate host accesses to a target memory. This design example supports simulation. In simulation, the testbench issues downstream memory accesses to the virtual function BAR. The testbench then reads the data written and compares it to the expected result. The test passes if all the comparisons pass.

When you install the Intel Quartus Prime software you also install the IP Library. This installation includes design examples for Hard IP for PCI Express under the <install\_dir>/ip/altera/altera\_pcie/ directory. You can copy the design examples from the <install\_dir>/ip/altera/ altera\_pcie/ altera\_pcie/ altera\_pcie/altera\_pcie\_al0\_ed/example\_design/al0 directory. This walkthrough uses the sriov2\_target\_g3x8\_lpf\_4vf.qsys design example.

*Note:* Starting in the Quartus Prime 16.0 software release, you cannot simulate or compile SR-IOV designs without a license. Contact your local sales representative or email pcie@altera.com to obtain a license.

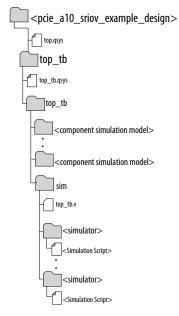

## **2.1. Directory Structure for Intel Arria 10 SR-IOV Design Example**

## Figure 3. Directory Structure for the Generated Example Design

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## **2.2. Design Components for the SR-IOV Design Example**

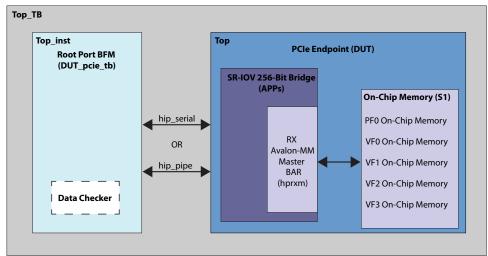

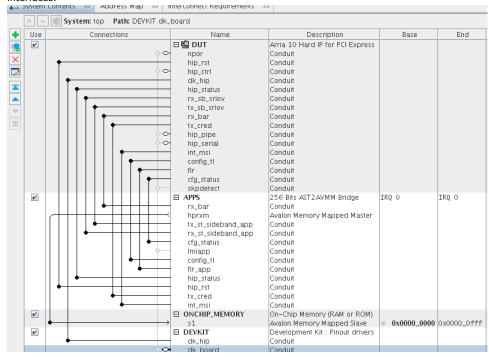

# Figure 4.Platform Designer Testbench for Intel Arria 10 Gen1 x8 128-bit SR-IOV<br/>Design Example

### Figure 5. Platform Designer Schematic for Top

This image of the Intel Arria 10 PCI Express DMA Design Example shows only the Avalon-ST, clock, and reset interfaces.

The testbench includes a PCIe Root Port BFM and a PCIe Gen3 x8 Endpoint implemented in hard logic. The SR-IOV bridge, implemented in soft logic, drives memory writes and reads to the four VFs. The simulation includes the following stages:

- Link Training

- Configuration ٠

- Memory writes to each VF

- Memory reads and compares to the expected data

## 2.3. Generating the SR-IOV Design Example

After installing the Quartus Prime software, copy the design examples from the <install\_dir>/ip/altera/ altera\_pcie/altera\_pcie\_a10\_ed/ example\_design/a10 directory. This walkthrough uses the sriov2\_top\_target\_gen3x8\_1pf\_4vf.qsys design example. To run the simulation, you must rename the design example top.gsys

- 1. Launch Platform Designer and open top.gsys.

- 2. On the Generate menu, select Generate Testbench System.

- 3. For Create testbench Platform Designer system, select Standard, BFMs for stand Platform Designer interfaces.

- 4. For Create testbench simulation model, select either Verilog or VHDL.

- 5. For **Output Directory** > **Testbench**, you can accept the default directory or modify it.

- 6. Click Generate.

- *Note:* Intel Arria 10 devices do not support the **Create timing and resource** estimates for third-party EDA synthesis tools option on the Generate Generate HDL menu. You can select this menu item, but generation fails.

## 2.4. Compiling and Simulating the Design for SR-IOV

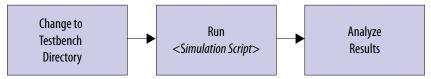

#### Figure 6. **Procedure**

Follow these steps to compile and simulate the design:

- 1. Change the simulation directory.

- 2. Run the simulation script for the simulator of your choice. Refer to the table below.

- 3. Analyze the results.

| Simulator           | Working Directory                                                     | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mentor<br>ModelSim* | <example_design>/top_tb/<br/>top_tb/sim/mentor/</example_design>      | <ul> <li>a. Invoke vsim</li> <li>b. do msim_setup.tcl</li> <li>c. ld_debug</li> <li>d. run -all</li> <li>e. A successful simulation ends with the following message,<br/>"Simulation stopped due to successful completion! Simulation passed."</li> </ul>                                                                                                                                                                                                                  |

| Mentor VCS*         | <example_design>/top_tb/<br/>top_tb/sim/synopsys/vcs</example_design> | <ul> <li>a. sh vcs_setup.sh USER_DEFINED_SIM_OPTIONS=""</li> <li>b. A successful simulation ends with the following message,<br/>"Simulation stopped due to successful completion! Simulation<br/>passed."</li> </ul>                                                                                                                                                                                                                                                      |

| Cadence<br>NCSim*   | <example_design>top_tb/<br/>top_tb/sim/cadence</example_design>       | <ul> <li>a. Create a shell script, my_setup.sh. This script allows you to add additional commands and override the defaults included in ncsim_setup.sh.</li> <li>b. Include the following command in my_setup.sh: source ncsim_setup.sh USER_DEFINED_SIM_OPTIONS=""</li> <li>c. chmod +x *.sh</li> <li>d/my_setup.sh</li> <li>e. A successful simulation ends with the following message, "Simulation stopped due to successful completion! Simulation passed."</li> </ul> |

#### Table 9. **Steps to Run Simulation**

Send Feedback

## **3. Parameter Settings**

## 3.1. Parameters

This chapter provides a reference for all the parameters of the Intel Arria 10 Hard IP for PCI Express IP core.

#### Table 10. Design Environment Parameter

Starting in Intel Quartus Prime 18.0, there is a new parameter **Design Environment** in the parameters editor window.

| Parameter             | Value                | Description                                                                                                                                                                                                                                                                                  |

|-----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design<br>Environment | Standalone<br>System | <ul> <li>Identifies the environment that the IP is in.</li> <li>The Standalone environment refers to the IP being in a standalone state where all its interfaces are exported.</li> <li>The System environment refers to the IP being instantiated in a Platform Designer system.</li> </ul> |

### Table 11.System Settings

| Parameter                     | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application<br>Interface Type | Avalon-ST<br>Avalon-MM<br>Avalon-MM with DMA<br>Avalon-ST with SR-IOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Selects the interface to the Application Layer.<br>Note: When the Design Environment parameter is<br>set to System, all four Application Interface<br>Types are available. However, when Design<br>Environment is set to Standalone, only<br>Avalon-ST and Avalon-ST with SR-IOV are<br>available.                                                                                           |

| Hard IP mode                  | Gen3x8, Interface: 256-bit, 250 MHz<br>Gen3x4, Interface: 256-bit, 125 MHz<br>Gen3x4, Interface: 128-bit, 250 MHz<br>Gen3x2, Interface: 128-bit, 125 MHz<br>Gen3x2, Interface: 64-bit, 125 MHz<br>Gen3x1, Interface: 64-bit, 125 MHz<br>Gen2x8, Interface: 256-bit, 125 MHz<br>Gen2x8, Interface: 128-bit, 250 MHz<br>Gen2x4, Interface: 128-bit, 125 MHz<br>Gen2x4, Interface: 64-bit, 125 MHz<br>Gen2x4, Interface: 64-bit, 125 MHz<br>Gen2x4, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x8, Interface: 64-bit, 125 MHz<br>Gen1x4, Interface: 64-bit, 125 MHz<br>Gen1x2, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 125 MHz<br>Gen1x1, Interface: 64-bit, 125 MHz | <ul> <li>Selects the following elements:</li> <li>The lane data rate. Gen1, Gen2, and Gen3 are supported</li> <li>The width of the data interface between the hard IP Transaction Layer and the Application Layer implemented in the FPGA fabric</li> <li>The Application Layer interface frequency Intel Cyclone<sup>®</sup> 10 GX devices support up to Gen2 x4 configurations.</li> </ul> |

| Port type                     | Native Endpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Specifies the port type.                                                                                                                                                                                                                                                                                                                                                                     |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

## 3. Parameter Settings UG-01161 | 2018.08.13

| Parameter                                                                | Value                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                          | Root Port                                     | The Endpoint stores parameters in the Type 0<br>Configuration Space. The Root Port stores parameter<br>in the Type 1 Configuration Space.<br>The <b>Avalon-ST with SR-IOV</b> interface supports onl<br><b>Native Endpoint</b> operation.<br>You can enable the Root Port in the current release.<br>Root Port mode only supports the Avalon <sup>®</sup> -MM<br>interface type, and it only supports basic simulation<br>and compilation. However, the Root Port mode is not<br>fully verified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RX Buffer credit<br>allocation -<br>performance for<br>received requests | Minimum<br>Low<br>Balanced<br>High<br>Maximum | <ul> <li>Determines the allocation of posted header credits, posted data credits, non-posted header credits, completion header credits, and completion data credits in the 16 KB RX buffer. The settings allow you to adjust the credit allocation to optimize your system. The credit allocation for the selected setting displays in the Message pane. The Message pane dynamically updates the number of credits for Posted Non-Posted Headers and Data, and Completion. Refer to the <i>Throughput Optimization</i> chapter for more information about optimizing your design.</li> <li>Refer to the <i>Throughput Optimization</i> chapter for more information about optimizing your design.</li> <li>Refer to the <i>RX Buffer Allocation Selections Available by Interface Type</i> below for the availability of these settings by interface type.</li> <li>Minimum—configures the minimum PCIe specification allowed for non-posted and posted request credits, leaving most of the RX Buffer space for received completion header and data. Select this option for variations where application logic generates many read requests from the PCIe link.</li> <li>Low—configures a slightly larger amount of RX Buffe space for non-posted and posted request credits, but still dedicates most of the space for received completion header and data. Select this option is recommended for typical endpoint applications where most of the PCIe link. This option is recommended for typical endpoint applications shere most of the PCIe traffic is generated by a DMA engin that is located in the endpoint application select this option for variations where most of the RX Buffer space for received completions. Select this option for variations where most of the PCIe link and the other half the RX Buffer space to received requests and allocates a slightly larger than minimum amount of space for received completions. Select this option where most of the PCIe link and the other and fit he PCIe link and the other and received completion space, leaving most of the RX Buffer space for</li></ul> |

| Parameter                          | Value                          | Description                                                                                                                                                                                               |

|------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                                | option is recommended for control and status<br>endpoint applications that do not generate any PCIe<br>requests of their own and only are the target of write<br>and read requests from the root complex. |

| RX Buffer<br>completion<br>credits | Header credits<br>Data credits | Displays the number of completion credits in the 16<br>KB RX buffer resulting from the credit allocation<br>parameter. Each header credit is 16 bytes. Each data<br>credit is 20 bytes.                   |

## **3.2. Intel Arria 10 Avalon-ST Settings**

## Table 12. System Settings for PCI Express

|                                                                      | _      | -                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                            | Value  | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

| Enable Avalon-ST<br>reset output port                                | On/Off | When <b>On</b> , the generated reset output port has the same functionality that the reset_status port included in the Reset and Link Status interface.                                                                                                                                                                                                                                                        |

| Enable byte parity<br>ports on Avalon-<br>ST interface               | On/Off | When <b>On</b> , the RX and TX datapaths are parity protected. Parity is odd. The Application Layer must provide valid byte parity in the Avalon-ST TX direction.<br>This parameter is only available for the Avalon-ST Intel Arria 10 Hard IP for PCI Express.                                                                                                                                                |

| Enable multiple<br>packets per cycle<br>for the 256-bit<br>interface | On/Off | When <b>On</b> , the 256-bit Avalon-ST interface supports the transmission of TLPs starting at any 128-bit address boundary, allowing support for multiple packets in a single cycle. To support multiple packets per cycle, the Avalon-ST interface includes 2 start of packet and end of packet signals for the 256-bit Avalon-ST interfaces. This is not supported for the Avalon-ST with SR-IOV interface. |

| Enable credit<br>consumed<br>selection port                          | On/Off | When you turn on this option, the core includes the tx_cons_cred_sel port. This parameter does not apply to the Avalon-MM interface.                                                                                                                                                                                                                                                                           |

| Enable<br>Configuration<br>bypass (CfgBP)                            | On/Off | When <b>On</b> , the Intel Arria 10 Hard IP for PCI Express bypasses the<br>Transaction Layer Configuration Space registers included as part of the Hard<br>IP, allowing you to substitute a custom Configuration Space implemented in<br>soft logic.<br>This parameter is not available for the Avalon-MM IP Cores.                                                                                           |

| Enable local<br>management<br>interface (LMI)                        | On/Off | When <b>On</b> , your variant includes the optional LMI interface. This interface is used to log error descriptor information in the TLP header log registers. The LMI interface provides the same access to Configuration Space registers as Configuration TLP requests.                                                                                                                                      |

## **Related Information**

PCI Express Base Specification 3.0

## 3.3. Intel Arria 10 SR-IOV System Settings

| Parameter                                                                                                                   | Value   | Description                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------|

| Total Physical Functions (PFs) :                                                                                            | 1-4     | This core supports 1-4 Physical Functions.                                               |

| Total Virtual Functions of<br>Physical Function0 (PF0 VFs) -<br>Total Virtual Functions of<br>Physical Function3 (PF3 VFs): | 0 -2048 | Total number of VFs assigned to a PF. You can assign VFs in the following granularities: |

|                                                                                                                             |         | continued                                                                                |

| Parameter                                                    | Value     | Description                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                              |           | <ul> <li>Granularity of 1 for 1-8 VFs</li> <li>Granularity of 4 for 8-256 VFs</li> <li>Granularity of 64 for 256-1024 VFs</li> <li>Granularity of 512 for 1024-2048 VFs</li> <li>The sum of VFs assigned to PF0, PF1, PF2 and PF3 cannot exceed the 2048 VF Total.</li> </ul> |

| System Supported Page Size:                                  | 4КВ - 4МВ | Specifies the pages sizes supported. Sets the Supported<br>Page Sizes register of the SR-IOV Capability structure.                                                                                                                                                            |

| Enable SR-IOV Support                                        | On/Off    | When <b>On</b> , the variant supports multiple PFs and VFs. When <b>Off</b> , .supports PFs only.                                                                                                                                                                             |

| Enable Alternative Routing-ID<br>(ARI) support               | On/Off    | When <b>On</b> , ARI supports up to 256 functions. Refer to <i>Section</i> 6.1.3 Alternative Routing-ID Interpretation (ARI) of the PCI Express Base Specification for more information about ARI.                                                                            |

| Enable Functional Level Reset<br>(FLR)                       | On/Off    | When <b>On</b> , each function has its own, individual reset.                                                                                                                                                                                                                 |

| Enable TLP Processing Hints<br>(TPH) support for PFs         | On/Off    | When <b>On</b> , the variant includes the TPH registers to help you                                                                                                                                                                                                           |

| Enable TLP Processing Hints<br>(TPH) support for VFs         |           | improve latency and traffic congestion.                                                                                                                                                                                                                                       |

| Enable Address Translation<br>Services (ATS) support for PFs | On/Off    | When <b>On</b> , the variant includes the ATS registers.                                                                                                                                                                                                                      |

| Enable Address Translation<br>Services (ATS) support for VFs | 01/01     | when <b>On</b> , the variant includes the ATS registers.                                                                                                                                                                                                                      |

### **Related Information**

PCI Express Base Specification 2.1 or 3.0

## 3.4. Base Address Register (BAR) Settings

Each function can implement up to six BARs. You can configure up to six 32-bit BARs or three 64-bit BARs for both PFs and VFs. The BAR settings are the same for all VFs associated with a PF.

| TADIE 15. DAK KEGISLEIS | Table 13. | BAR Registers |

|-------------------------|-----------|---------------|

|-------------------------|-----------|---------------|

| Parameter              | Value                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Present<br>(BAR0-BAR5) | Enabled/Disabled                 | Indicates whether or not this BAR is instantiated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Туре                   | 32-bit address<br>64-bit address | Specifies 32- or 64-bit addressing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Prefetchable           | Prefetchable<br>Non-prefetchable | <ul> <li>Defining memory as <b>Prefetchable</b> allows data in the region to be fetched ahead anticipating that the requestor may require more data from the same region than was originally requested. If you specify that a memory is prefetchable, it must have the following 2 attributes:</li> <li>Reads do not have side effects</li> <li>Write merging is allowed</li> <li>If you select <b>64-bit address</b>, 2 contiguous BARs are combined to form a 64-bit BAR. You must set the higher numbered BAR to <b>Disabled</b>.</li> </ul> |

| Parameter | Value         | Description                                                                                                                                                                                                     |

|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |               | If the BAR TYPE of any even BAR is set to 64-bit memory,<br>the next higher BAR supplies the upper address bits. The<br>supported combinations for 64-bit BARs are {BAR1, BAR0},<br>{BAR3, BAR2}, {BAR4, BAR5}. |

| Size      | 16 Bytes-2 GB | Specifies the memory size.                                                                                                                                                                                      |

## 3.5. SR-IOV Device Identification Registers

#### Table 14. **Device ID Registers**

The following table lists the default values of the read-only Device ID registers. You can use the parameter editor to change the values of these registers. At run time, you can change the values of these registers using the optional reconfiguration block signals. You can specify Device ID registers for each Physical Function.

| Register Name          | Default Value | Description                                                                                                                                                                                                                                                                 |

|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vendor ID              | 0x00001172    | Sets the read-only value of the Vendor ID register. This parameter can not be set to 0xFFFF per the PCI Express Specification.<br>Address offset: 0x000.                                                                                                                    |

| Device ID              | 0x0000000     | Sets the read-only value of the Device ID register.<br>Address offset: 0x000.                                                                                                                                                                                               |

| VF Device ID           | 0x0000000     | Sets the read-only value of the VF Device ID register.                                                                                                                                                                                                                      |

| Revision ID            | 0x0000000     | Sets the read-only value of the Revision ID register.<br>Address offset: 0x008.                                                                                                                                                                                             |

| Class code             | 0x0000000     | Sets the read-only value of the Class Code register.<br>Address offset: 0x008.                                                                                                                                                                                              |

| Subclass code          | 0×00000000    | Sets the read-only value of the Subclass Code register.<br>Address offset: 0x008.                                                                                                                                                                                           |

| Subsystem<br>Vendor ID | 0x00000000    | Sets the read-only value of the register in the PCI Type 0 Configuration<br>Space. This parameter cannot be set to 0xFFFF per the <i>PCI Express Base</i><br><i>Specification</i> . This value is assigned by PCI-SIG to the device manufacturer.<br>Address offset: 0x02C. |

| Subsystem Device<br>ID | 0x0000000     | Sets the read-only value of the Subsystem Device ID register in the PCI<br>Type O Configuration Space.<br>Address offset: 0x02C                                                                                                                                             |

## **Related Information**