# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Turbo IP Core**

**User Guide**

**UG-TURBO** 2015.11.11

# Contents

| About the Turbo IP Core                              |                                        |

|------------------------------------------------------|----------------------------------------|

| Altera DSP IP Core Features                          |                                        |

| Turbo IP Core Features                               |                                        |

| DSP IP Core Device Family Support                    |                                        |

| Turbo IP Core Release Information                    |                                        |

| DSP IP Core Verification                             |                                        |

| Turbo IP Core Performance and Resource Utilization   |                                        |

| Turbo Code Licensing Disclaimer                      |                                        |

| Turbo IP Core Getting Started                        | 2-1                                    |

| Licensing IP Cores                                   |                                        |

| OpenCore Plus IP Evaluation                          |                                        |

| Turbo IP Core OpenCore Plus Timeout Behavior         |                                        |

| IP Catalog and Parameter Editor                      |                                        |

| Generating IP Cores                                  |                                        |

| Files Generated for Altera IP Cores and Qsys Systems |                                        |

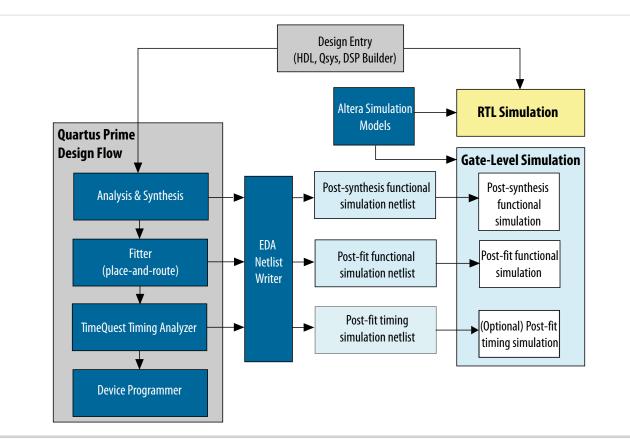

| Simulating Altera IP Cores in other EDA Tools        |                                        |

| DSP Builder Design Flow                              |                                        |

|                                                      |                                        |

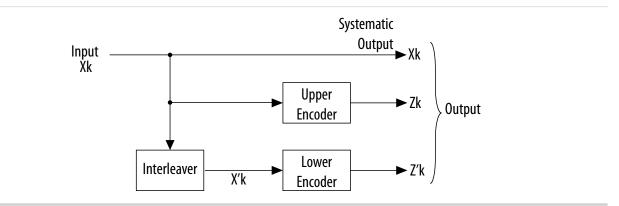

| Turbo IP Core Functional Description                 |                                        |

| Turbo Encoder                                        |                                        |

| Turbo Encoder Data Format                            |                                        |

| Turbo Encoder Latency Calculation                    |                                        |

| Turbo Decoder                                        |                                        |

| Turbo Decoder Data Format                            |                                        |

| CRC24A or CRC24B Early Termination                   |                                        |

| Decoder Latency Calculation                          |                                        |

| Turbo IP Core Parameters                             |                                        |

| Turbo IP Core Interfaces and Signals                 |                                        |

| Avalon-ST Interfaces in DSP IP Cores                 |                                        |

| Packet Format Errors                                 |                                        |

| Turbo Throughput                                     |                                        |

| Document Revision History                            | <i>A</i> 1                             |

| D'ocument revision mistor y                          | ······································ |

# About the Turbo IP Core

#### **Related Information**

- Introduction to Altera IP Cores Provides general information about all Altera IP cores, including parameterizing, generating, upgrading, and simulating IP.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- **Project Management Best Practices** Guidelines for efficient management and portability of your project and IP files.

## **Altera DSP IP Core Features**

- Avalon<sup>®</sup> Streaming (Avalon-ST) interfaces

- DSP Builder ready

- Testbenches to verify the IP core

- IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

## **Turbo IP Core Features**

- 3GPP LTE compliant.

- 3GPP UMTS compliant with support for block sizes from 40 to 5,114.

- C/MATLAB bit-accurate models for performance simulation or RTL test vector generation.

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

#### 1-2 DSP IP Core Device Family Support

## **Decoder Features**

- Successive interface cancellation (SIC) for the LTE-A channel coding enhancement over LTE.

- Run time parameters for interleaver size and number of iterations.

- Early termination with cyclical redundancy check (CRC).

- Compile time parameters for the number of parallel engines, choice of decoding algorithm, input precision, and output size.

- Double-buffering for reduced latency real-time applications, which allows the decoder to receive data while processing the previous data block.

- No external memory required.

## **Encoder Features**

- 3GPP LTE and LTE-A compliant.

- 3GPP UMTS compliant with support for block sizes from 40 to 5,114.

- Run-time selectable interleaver block sizes .

- Code rate 1/3 only.

- Use external rate matching for other code rates.

- Double-buffering allows the encoder to receive data while processing the previous data block.

# **DSP IP Core Device Family Support**

Altera<sup>®</sup> offers the following device support levels for Altera IP cores:

- Preliminary support—Altera verifies the IP core with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. You can use it in production designs with caution.

- Final support—Altera verifies the IP core with final timing models for this device family. The IP core meets all functional and timing requirements for the device family. You can use it in production designs.

## Table 1-1: DSP IP Core Device Family Support

| Device Family              | Support |

|----------------------------|---------|

| Arria <sup>®</sup> II GX   | Final   |

| Arria II GZ                | Final   |

| Arria V                    | Final   |

| Arria 10                   | Final   |

| Cyclone <sup>®</sup> IV    | Final   |

| Cyclone V                  | Final   |

| MAX <sup>®</sup> 10 FPGA   | Final   |

| Stratix <sup>®</sup> IV GT | Final   |

| Stratix IV GX/E            | Final   |

| Stratix V                  | Final   |

About the Turbo IP Core

| UG-TURBO<br>2015.11.11 | Turbo IP Core Release Information |  |

|------------------------|-----------------------------------|--|

| Device Family          | Support                           |  |

## Other device families

No support

## **Turbo IP Core Release Information**

Use the release information when licensing the IP core.

## Table 1-2: Release Information

| ltem          | Description          |

|---------------|----------------------|

| Version       | 15.1                 |

| Release Date  | November 2015        |

| Ordering Code | IP-TURBO (IPR-TURBO) |

| Product ID    | 00FC                 |

| Vendor ID     | 6AF7                 |

Altera verifies that the current version of the Quartus Prime software compiles the previous version of each IP core. Altera does not verify that the Quartus Prime software compiles IP core versions older than the previous version. The *Altera IP Release Notes* lists any exceptions.

#### **Related Information**

- Altera IP Release Notes

- Errata for Turbo IP core in the Knowledge Base

# **DSP IP Core Verification**

Before releasing a version of an IP core, Altera runs comprehensive regression tests to verify its quality and correctness. Altera generates custom variations of the IP core to exercise the various parameter options and thoroughly simulates the resulting simulation models with the results verified against master simulation models.

# **Turbo IP Core Performance and Resource Utilization**

## Table 1-3: Performance and Resource Utilization

Typical expected performance for a Turbo IP Core using the Quartus Prime software with the Arria V (5AGXFB3H4F35C5), Cyclone V (5CGXFC7C7F23C8), and Stratix V (5SGXEA7H3F35C3) devices.

|         |            | Paramet  | ers           | Memory  |     |      | fMAX |       |

|---------|------------|----------|---------------|---------|-----|------|------|-------|

| Device  | Codec Type | Standard | Input<br>Bits | Engines | ALM | M20K | M10K | (MHz) |

| Arria V | Encoder    | LTE      |               |         | 434 | -    | 2    | 237   |

#### 1-4 Turbo IP Core Performance and Resource Utilization

|           |            | Parameters Memory |               | Parameters |        | mory | fMAX |       |

|-----------|------------|-------------------|---------------|------------|--------|------|------|-------|

| Device    | Codec Type | Standard          | Input<br>Bits | Engines    | ALM    | M20K | M10K | (MHz) |

| Cyclone V | Encoder    | LTE               |               |            | 435    | -    | 2    | 175   |

| Stratix V | Encoder    | LTE               |               |            | 430    | 2    | -    | 344   |

| Arria V   | Encoder    | UMTS              |               |            | 959    | -    | 4    | 151   |

| Cyclone V | Encoder    | UMTS              |               |            | 961    | -    | 4    | 103   |

| Stratix V | Encoder    | UMTS              |               |            | 954    | 4    | -    | 245   |

| Arria V   | Decoder    | LTE               | 4             | 2          | 4,497  |      | 40   | 167   |

| Cyclone V | Decoder    | LTE               | 4             | 2          | 4,505  |      | 40   | 121   |

| Stratix V | Decoder    | LTE               | 4             | 2          | 4,138  | 27   | -    | 251   |

| Arria V   | Decoder    | LTE               | 4             | 4          | 6,194  |      | 37   | 175   |

| Cyclone V | Decoder    | LTE               | 4             | 4          | 6,221  |      | 37   | 132   |

| Stratix V | Decoder    | LTE               | 4             | 4          | 5,774  | 21   | -    | 273   |

| Arria V   | Decoder    | LTE               | 4             | 8          | 9,893  |      | 37   | 179   |

| Cyclone V | Decoder    | LTE               | 4             | 8          | 9,881  |      | 37   | 130   |

| Stratix V | Decoder    | LTE               | 4             | 8          | 9,049  | 21   | -    | 253   |

| Arria V   | Decoder    | LTE               | 8             | 2          | 5,998  |      | 58   | 156   |

| Cyclone V | Decoder    | LTE               | 8             | 2          | 6,001  |      | 58   | 122   |

| Stratix V | Decoder    | LTE               | 8             | 2          | 5,370  | 39   | -    | 251   |

| Arria V   | Decoder    | LTE               | 8             | 4          | 8,482  |      | 55   | 168   |

| Cyclone V | Decoder    | LTE               | 8             | 4          | 8,520  |      | 55   | 124   |

| Stratix V | Decoder    | LTE               | 8             | 4          | 7,658  | 30   |      | 256   |

| Arria V   | Decoder    | LTE               | 8             | 8          | 13,672 |      | 54   | 161   |

| Cyclone V | Decoder    | LTE               | 8             | 8          | 13,690 |      |      | 117   |

| Stratix V | Decoder    | LTE               | 8             | 8          | 12,246 | 30   |      | 250   |

| Arria V   | Decoder    | UMTS              | 4             | 2          | 3,935  |      | 81   | 133   |

| Stratix V | Decoder    | UMTS              | 4             | 2          | 3,622  | 71   |      | 217   |

| Arria V   | Decoder    | UMTS              | 4             | 4          | 6,161  |      | 83   | 137   |

| Cyclone V | Decoder    | UMTS              | 4             | 4          | 6,141  |      | 83   | 100   |

| Stratix V | Decoder    | UMTS              | 4             | 4          | 5,661  | 73   |      | 215   |

| Arria V   | Decoder    | UMTS              | 8             | 2          | 5,394  |      | 91   | 124   |

| Cyclone V | Decoder    | UMTS              | 8             | 2          | 5,390  |      | 91   | 93    |

| Stratix V | Decoder    | UMTS              | 8             | 2          | 4,646  | 81   |      | 194   |

| Arria V   | Decoder    | UMTS              | 8             | 4          | 8,189  |      | 93   | 125   |

**Altera Corporation**

About the Turbo IP Core

| Parameters |            |          |               | Memory  |       | fMAX |      |       |

|------------|------------|----------|---------------|---------|-------|------|------|-------|

| Device     | Codec Type | Standard | Input<br>Bits | Engines | ALM   | M20K | M10K | (MHz) |

| Cyclone V  | Decoder    | UMTS     | 8             | 4       | 8,190 |      | 93   | 92    |

| Stratix V  | Decoder    | UMTS     | 8             | 4       | 7,381 | 78   |      | 188   |

# **Turbo Code Licensing Disclaimer**

France Telecom, for itself and certain other parties, claims certain intellectual property rights covering Turbo Codes technology, and has decided to license these rights under a licensing program called the Turbo Codes Licensing Program. Supply of this IP core does not convey a license nor imply any right to use any Turbo Codes patents owned by France Telecom, TDF or GET. For information about the Turbo Codes Licensing Program, contact France Telecom at the following address:

France Telecom R&D

VAT/TURBOCODES

38, rue du Général Leclerc

92794 Issy Moulineaux

Cedex 9

France

About the Turbo IP Core

# Turbo IP Core Getting Started

# 2015.11.11 UG-TURBO Subscribe Send Feedback

# **Licensing IP Cores**

The Altera IP Library provides many useful IP core functions for your production use without purchasing an additional license. Some Altera MegaCore<sup>®</sup> IP functions require that you purchase a separate license for production use. However, the OpenCore<sup>®</sup> feature allows evaluation of any Altera IP core in simulation and compilation in the software. After you are satisfied with functionality and performance, visit the Self Service Licensing Center to obtain a license number for any Altera product.

## Figure 2-1: IP Core Installation Path

## 📄 acds

**quartus** - Contains the Quartus Prime software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

</p

**Note:** The default IP installation directory on Windows is *<drive>:\altera\<version number>*; on Linux it is *<home directory>/altera/ <version number>*.

## **OpenCore Plus IP Evaluation**

Altera's free OpenCore Plus feature allows you to evaluate licensed MegaCore IP cores in simulation and hardware before purchase. You need only purchase a license for MegaCore IP cores if you decide to take your design to production. OpenCore Plus supports the following evaluations:

- Simulate the behavior of a licensed IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

OpenCore Plus evaluation supports the following two operation modes:

- Untethered—run the design containing the licensed IP for a limited time.

- Tethered—run the design containing the licensed IP for a longer time or indefinitely. This requires a connection between your board and the host computer.

ISO 9001:2008 Registered

<sup>© 2015</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### 2-2 Turbo IP Core OpenCore Plus Timeout Behavior

Note: All IP cores that use OpenCore Plus time out simultaneously when any IP core in the design times out.

#### **Related Information**

- Altera Licensing Site

- Altera Software Installation and Licensing Manual

## **Turbo IP Core OpenCore Plus Timeout Behavior**

All IP cores in a device time out simultaneously when the most restrictive evaluation time is reached. If a design has more than one IP core, the time-out behavior of the other IP cores may mask the time-out behavior of a specific IP core .

For IP cores, the untethered time-out is 1 hour; the tethered time-out value is indefinite. Your design stops working after the hardware evaluation time expires. The Quartus Prime software uses OpenCore Plus Files (.ocp) in your project directory to identify your use of the OpenCore Plus evaluation program. After you activate the feature, do not delete these files..When the evaluation time expires, the data output port reset\_n goes low, which keeps the IP core permanently in its reset state.

#### **Related Information**

• AN 320: OpenCore Plus Evaluation of Megafunctions

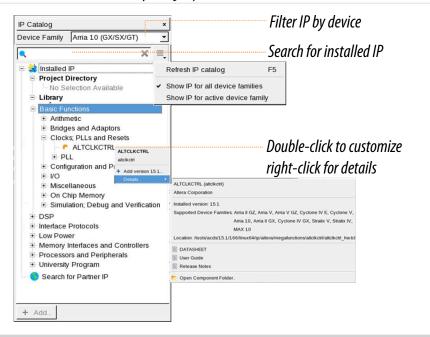

## **IP Catalog and Parameter Editor**

The IP Catalog (**Tools** > **IP Catalog**) and parameter editor help you easily customize and integrate IP cores into your project. Use the IP Catalog and parameter editor to select, customize, and generate files representing the custom IP variation in your project.

The IP Catalog displays the installed IP cores available for your design. Double-click any IP core to launch the parameter editor and generate files representing your IP variation. Use the following features to help you quickly locate and select an IP core:

- Filter IP Catalog to Show IP for active device family or Show IP for all device families. If you have no project open, select the Device Family in IP Catalog.

- Type in the Search field to locate any full or partial IP core name in IP Catalog.

- Right-click an IP core name in IP Catalog to display details about supported devices, open the IP core's installation folder, and click links to IP documentation.

- Click Search for Partner IP, to access partner IP information on the Altera website.

The parameter editor prompts you to specify an IP variation name, optional ports, and output file generation options. The parameter editor generates a top-level Qsys system file (**.qsys**) or IP file (**.qip**) representing the IP core in your project. You can also parameterize an IP variation without an open project.

The IP Catalog is also available in Qsys (**View** > **IP Catalog**). The Qsys IP Catalog includes exclusive system interconnect, video and image processing, and other system-level IP that are not available in the IP Catalog. For more information about using the Qsys IP Catalog, refer to *Creating a System with Qsys* in the *Handbook*.

Note: The IP Catalog (Tools > IP Catalog) and parameter editor replace the MegaWizard<sup>™</sup> Plug-In Manager for IP selection and parameterization, beginning in Quartus II software version 14.0. Use the IP Catalog and parameter editor to locate and parameterize Altera IP cores.

## **Generating IP Cores**

You can quickly configure a custom IP variation in the parameter editor. Use the following steps to specify IP core options and parameters in the parameter editor.

#### Figure 2-2: IP Parameter Editor

and target device

| Parameters 83                                                                                                                                    | _ 🗗 🗖 🗖 Details 🚳 Block Symbol 😂 🛛 _ 🗗 🛃 🛛 and                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| stem: unsaved Path: xcvr_fpll_a10_0                                                                                                              | deta                                                                                                                                                                                           |

| rria 10 fPLL<br>era_xcvr_fpll_a10                                                                                                                | Petails Arria 10 fPLL                                                                                                                                                                          |

| Dynamic Reconfiguration Generation Options Advanced Parameters PLL Master Clock Generation Block                                                 | Name altera_xcvr_fpil_a10     Version 15.1     Author Altera Corporation                                                                                                                       |

| General     FPLL Mode:     Transceiver     Protocol mode:     Basic     Basic     Enable fractional mode     Enable manual counter configuration | Description         Arria 10 FPLL.           Group         Interface Protocols/Tran           Data Sheet         http://www.altera.com/li           User Guide         https://documentation.a |

| Enable ATX to FPLL cascade clock input port                                                                                                      | Release Notes https://documentation.av                                                                                                                                                         |

| Actual reference clock frequency: 100.0 MHz Actual reference clock frequency: 100.0 MHz                                                          | Versets 🛛 – 🗗 🛱                                                                                                                                                                                |

| Number of PL                                                                                                                                     | S for xcvr_fpll_a10_0                                                                                                                                                                          |

| Selected refer Your IP settings will be saved in a .qsys file. Create IP Variation                                                               | t<br>t. New to create a preset.                                                                                                                                                                |

| Bandwidth: Entity name: unnamed .                                                                                                                |                                                                                                                                                                                                |

| Save in folder: //users/jbrossar/150_migrate_upgrade_test                                                                                        | GX 2500Mbps Bonded<br>GX 2500Mbps Single Channel<br>GX 2500Mbps xN Non-Bonded                                                                                                                  |

| Type Family. Arria 10                                                                                                                            | PCIe Gen1 and Gen2 Multi Lane 100Mhz  PCIe Gen1 and Gen2 Single Lane 100Mhz                                                                                                                    |

| 1 In     Device: 10AS016C3U19E2LG                                                                                                                |                                                                                                                                                                                                |

| Info: Your IP will be saved in /users/jbrossar/150_migrate_upgra                                                                                 | ide_test/unnamed.qsys                                                                                                                                                                          |

|                                                                                                                                                  | Update Delete New                                                                                                                                                                              |

| Errors, O Warn                                                                                                                                   | OK Generate HDL Finish                                                                                                                                                                         |

In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize. The parameter editor appears.

specific applications

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <*your\_ip*>.qsys. Click OK. Do not include spaces in IP variation names or paths.

- **3.** Specify the parameters and options for your IP variation in the parameter editor, including one or more of the following. Refer to your IP core user guide for information about specific IP core parameters.

**Turbo IP Core Getting Started**

- Optionally select preset parameter values if provided for your IP core. Presets specify initial parameter values for specific applications.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

- 4. Click Generate HDL. The Generation dialog box appears.

- **5.** Specify output file generation options, and then click **Generate**. The IP variation files generate according to your specifications.

- 6. To generate a simulation testbench, click Generate > Generate Testbench System.

- 7. To generate an HDL instantiation template that you can copy and paste into your text editor, click **Generate** > **HDL Example**.

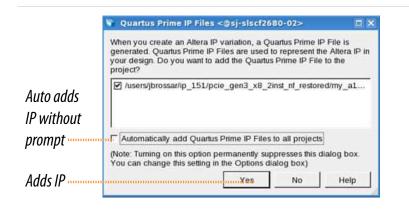

- 8. Click Finish. Click Yes if prompted to add files representing the IP variation to your project. Optionally turn on the option to Automatically add Quartus Prime IP Files to All Projects. Click Project > Add/Remove Files in Project to add IP files at any time.

## Figure 2-3: Adding IP Files to Project

For Arria 10 devices and newer, the generated **.qsys** file must be added to your project to represent IP and Qsys systems. For devices released prior to Arria 10 devices, the generated **.qip** and **.sip** files must be added to your project for IP and Qsys systems.

The generated .qsys file must be added to your project to represent IP and Qsys systems.

**9.** After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

#### **Related Information**

- IP User Guide Documentation

- Altera IP Release Notes

## Files Generated for Altera IP Cores and Qsys Systems

The software generates the following output file structure for IP cores and Qsys systems. For Arria 10 devices and newer, the generated **.qsys** file must be added to your project to represent IP and Qsys systems. For devices released prior to Arria 10 devices, the generated **.qip** and **.sip** files must be added to your project to represent IP and Qsys systems. The software generates the following output file structure for IP cores and Qsys systems. The generated **.qsys** file must be added to your project to represent IP and Qsys systems. The software generates the following output file structure for IP cores and Qsys systems. The generated **.qsys** file must be added to your project to represent IP and Qsys systems.

**Turbo IP Core Getting Started**

**Altera Corporation**

## Figure 2-4: Files generated for IP cores and Qsys Systems

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre> <your_ip>.qip or .qsys - System or IP integration file</your_ip></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <pre> <your_ip>.sopcinfo - Software tool-chain integration file</your_ip></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre> <your_ip> - IP core variation files</your_ip></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <pre></pre> /// <pre>- VHDL component declaration</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre></pre> debuginfo - Post-generation debug data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre></pre> _ppf - XML I/O pin information file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre></pre> qip - Lists files for IP core synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <pre></pre> /// <pre>// &lt;</pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre> |

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |