Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Synchronous Buck Multiphase Optimized LGA Power Block

**Integrated Power Semiconductors, Drivers & Passives**

#### Features:

- Full function multiphase building block

- Output current 40A continuous with no derating up to T<sub>PCR</sub> = 100°C and T<sub>CASF</sub> = 100°C

- Operating frequency up to 1.0 MHz

- · Efficient dual sided cooling

- Small footprint low profile (11mm x 11mm x 2.2mm) package

- · Optimized for very low power losses

- LGA interface

- · Ease of design

- Proprietary packaging enables ultra low Rth<sub>j-case top</sub>

# CR

iP2003 Power Block

#### Description

The iP2003 is a fully optimized solution for high current synchronous buck multiphase applications. Board space and design time are greatly reduced because most of the components required for each phase of a typical discrete-based multiphase circuit are integrated into a single 11mm x 11mm x 2.2mm power block. The only additional components required for a complete multiphase converter are a PWM IC, the external inductors, and the input and output capacitors.

iPOWIR technology offers designers an innovative board space saving solution for applications requiring high power densities. iPOWIR technology eases design for applications where component integration offers benefits in performance and functionality. iPOWIR technology solutions are also optimized internally for layout, heat transfer and component selection.

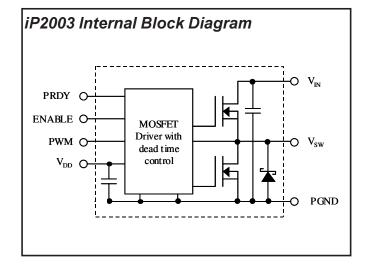

| Pin# | Pin Name        | Pin Function                                                                                                                                                                                                                                                                                                                              |

|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | $V_{DD}$        | Supply voltage for the internal circuitry.                                                                                                                                                                                                                                                                                                |

| 2    | ENABLE          | When set to logic level high, internal circuitry of the device is enabled. When set to logic level low, the PRDY pin is forced low, the Control and Sychronous switches are turned off, and the supply current is less than $10\mu A$ .                                                                                                   |

| 3    | PWM             | TTL-level input signal to MOSFET drivers.                                                                                                                                                                                                                                                                                                 |

| 4    | PRDY            | Power Ready - This pin indicates the status of ENABLE or $V_{\rm DD}$ . This output will be driven low when ENABLE is logic low or when $V_{\rm DD}$ is less than 4.4V (typ.). When ENABLE is logic high and $V_{\rm DD}$ is greater than 4.4V (typ.), this output is driven high. This output has a 10mA source and 1mA sink capability. |

| 5, 7 | PGND            | Power Ground - connection to the ground of bulk and filter capacitors.                                                                                                                                                                                                                                                                    |

| 6    | V <sub>SW</sub> | Switching Node - connection to the output inductor.                                                                                                                                                                                                                                                                                       |

| 8    | $V_{IN}$        | Input voltage for the DC-DC converter.                                                                                                                                                                                                                                                                                                    |

## iP2003

#### All specifications @25°C (unless otherwise specified)

#### **Absolute Maximum Ratings:**

| Parameter               | Symbol           | Min  | Тур | Max            | Units | Conditions                                      |

|-------------------------|------------------|------|-----|----------------|-------|-------------------------------------------------|

| V <sub>IN</sub> to PGND | $V_{IN}$         | -    | -   | 16             | V     |                                                 |

| V <sub>DD</sub> to PGND | $V_{DD}$         | -    | -   | 6.0            | V     |                                                 |

| PWM to PGND             | PWM              | -0.3 | -   | $V_{DD} + 0.3$ | V     | Not to exceed 6.0V                              |

| Enable to PGND          | ENABLE           | -0.3 | -   | $V_{DD} + 0.3$ | V     | Not to exceed 6.0V                              |

| Output RMS Current      | I <sub>OUT</sub> | -    | -   | 40             | Α     | Measured at V <sub>SW</sub>                     |

| Block Temperature       | T <sub>BLK</sub> | -40  | -   | 125            | °C    | Capable of start up over full temperature range |

|                         |                  |      |     |                |       | remperature range                               |

**Recommended Operating Conditions:**

| Parameter            | Symbol           | Min | Тур | Max  | Units | Conditions |

|----------------------|------------------|-----|-----|------|-------|------------|

| Supply Voltage       | $V_{DD}$         | 4.6 | 5.0 | 5.5  | V     |            |

| Input Voltage        | V <sub>IN</sub>  | 3.0 | -   | 13.2 | V     |            |

| Output Voltage       | $V_{OUT}$        | 0.8 | -   | 3.3  | V     |            |

| Output Current       | I <sub>OUT</sub> | -   | -   | 40   | Α     |            |

| Operating Frequency  | fsw              | 300 | -   | 1000 | kHz   |            |

| Operating Duty Cycle | D                | -   | -   | 85   | %     |            |

#### Electrical Specifications @ $V_{DD} = 5V$ (unless otherwise specified):

| Parameter                         | Symbol                | Min | Тур | Max  | Units | Conditions                                                  |

|-----------------------------------|-----------------------|-----|-----|------|-------|-------------------------------------------------------------|

| Block Power Loss ①                | P <sub>LOSS</sub>     | -   | 9.4 | 11.7 | W     | V <sub>IN</sub> =12V, V <sub>OUT</sub> =1.3V                |

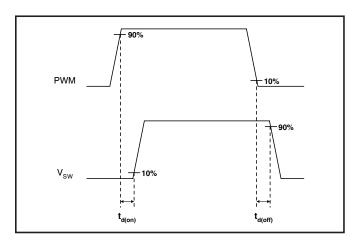

| Turn On Delay ②                   | t <sub>d(on)</sub>    | -   | 63  | -    | no    | I <sub>OUT</sub> =40A, f <sub>SW</sub> =1MHz                |

| Turn Off Delay ②                  | t <sub>d(off)</sub>   | -   | 26  | -    | ns    | L = 0.3µH                                                   |

| V <sub>IN</sub> Quiescent Current | I <sub>Q-VIN</sub>    | -   | -   | 1.0  | mA    | Enable = 0V, V <sub>IN</sub> =12V                           |

| V <sub>DD</sub> Quiescent Current | I <sub>Q-VDD</sub>    | -   | 10  | -    | μΑ    | Enable = 0V, V <sub>DD</sub> =5V                            |

| Under-Voltage Lockout             | UVLO                  |     |     |      |       |                                                             |

| Start Threshold                   | $V_{START}$           | 4.2 | 4.4 | 4.5  | V     |                                                             |

| Hysteresis                        | V <sub>Hvs-UVLO</sub> | -   | 150 | -    | mV    |                                                             |

| Enable                            | ENABLE                |     |     |      |       |                                                             |

| Input Voltage High                | $V_{IH}$              | 2.0 | -   | -    | V     |                                                             |

| Input Voltage Low                 | $V_{IL}$              | -   | -   | 0.8  |       |                                                             |

| Power Ready                       | PRDY                  |     |     |      |       |                                                             |

| Logic Level High                  | $V_{OH}$              | 4.5 | 4.6 | -    | V     | V <sub>DD</sub> =4.6V, I <sub>Load</sub> =10mA              |

| Logic Level Low                   | V <sub>OL</sub>       | -   | 0.1 | 0.2  |       | $V_{DD}$ <uvlo <math="" threshold,="">I_{Load} = 1mA</uvlo> |

| PWM Input                         | PWM                   |     |     |      |       |                                                             |

| Logic Level High                  | $V_{OH}$              | 2.0 | -   |      | V     |                                                             |

| Logic Level Low                   | V <sub>OL</sub>       | -   | -   | 0.8  |       |                                                             |

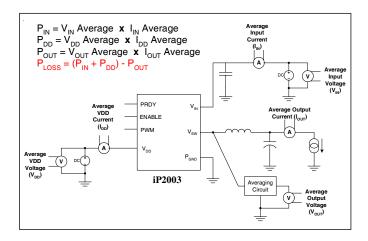

① Measurement were made using four 10uF (TDK C3225X5R1C106KT or equiv.) capacitors across the input (see Fig. 8).

② Not associated with the rise and fall times. Does not affect Power Loss (see Fig. 9).

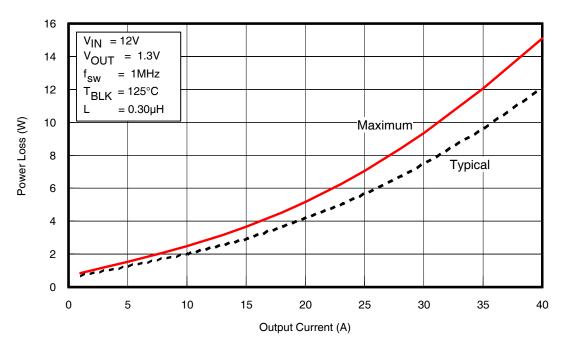

Fig. 1: Power Loss vs. Current

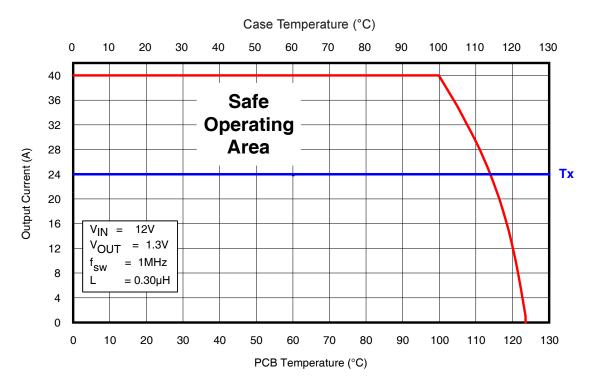

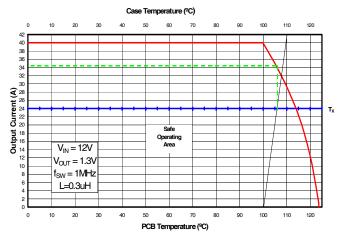

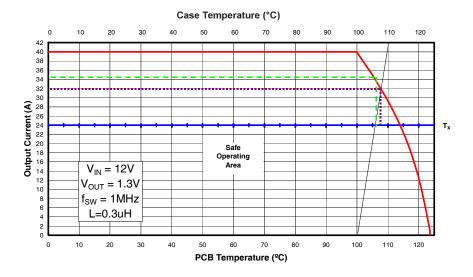

Fig. 2: Safe Operating Area (SOA) vs.  $T_{PCB} \& T_{CASE}$

#### **Typical Performance Curves**

1.16 4.0 SOA Temp Adjustment (°C) 1.12 3.0 Power Loss (Normalized) 1.08  $V_{IN} = \overline{12V}$ 1.04  $I_{OUT} = 40A$ = 1MHz 1.00  $= 0.30 \mu H$  $^{\mathsf{T}}\mathsf{BLK} = 125^{\circ}\mathsf{C}$ 0.96 -1.0 0.8 1.2 1.6 2.0 2.4 2.8 3.2 3.6 Output Voltage (V)

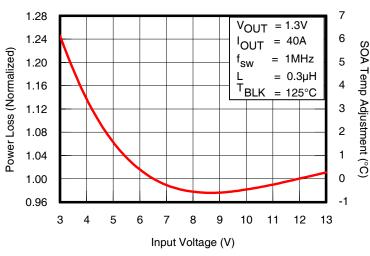

Fig. 3: Normalized Power Loss vs.  $V_{IN}$

Fig. 4: Normalized Power Loss vs. V<sub>OUT</sub>

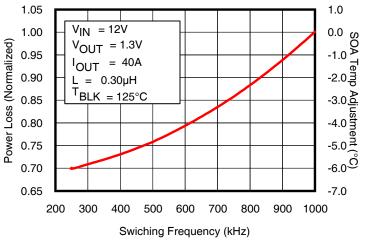

Fig. 5: Normalized Power Loss vs. Frequency

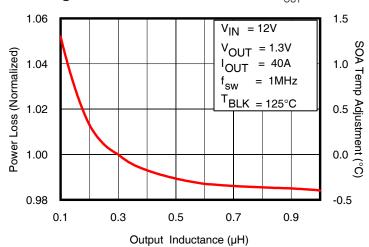

Fig. 6: Normalized Power Loss vs. Inductance

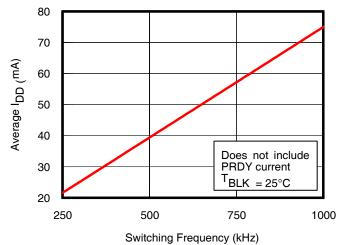

**Fig. 7:**  $I_{DD}$  ( $V_{DD}$  current) vs. Frequency

#### **Applying the Safe Operating Area (SOA) Curve**

The SOA graph incorporates power loss and thermal resistance information in a way that allows one to solve for maximum current capability in a simplified graphical manner. It incorporates the ability to solve thermal problems where heat is drawn out through the printed circuit board and the top of the case.

#### **Procedure**

- 1) Draw a line from Case Temp axis at  $T_{CASE}$  to the PCB Temp axis at  $T_{PCB}$ .

- 2) Draw a vertical line from the  $T_{\chi}$  axis intercept to the SOA curve.

- 3) Draw a horizontal line from the intersection of the vertical line with the SOA curve to the Y-axis. The point at which the horizontal line meets the Y-axis is the SOA current.

#### Calculating Power Loss and SOA for Different Operating Conditions

To calculate power loss for a given set of operating conditions, the following procedure should be followed: Determine the maximum current for each iP2003 and obtain the maximum power loss from Fig 1. Use the curves in Figs. 3, 4, 5 and 6 to obtain normalized power loss values that match the operating conditions in the application. The maximum power loss under the operating conditions is then the product of the power loss from Fig. 1 and the normalized values.

To calculate the SOA for a given set of operating conditions, the following procedure should be followed: Determine the maximum PCB temperature and Case temperature at the maximum operating current of each iP2003. Obtain the SOA temperature adjustments that match the operating conditions in the application from Figs. 3, 4, 5 and 6. Then, add the sum of the SOA temperature adjustments to the Tx axis intercept in Fig 2.

The example below explains how to calculate maximum power loss and SOA.

#### **Example:**

#### **Operating Conditions**

Output Current = 40A Input Voltage = 10V Output Voltage = 3.3V Sw Freq= 900kHz Inductor =  $0.2\mu H$   $T_{PCB} = 100^{\circ}C$ ,  $T_{CASE} = 110^{\circ}C$

#### **Calculating Maximum Power Loss:**

(Fig. 1) Maximum power loss = 15W

(Fig. 3) Normalized power loss for input voltage  $\approx 0.98$

(Fig. 4) Normalized power loss for output voltage  $\approx 1.14$

(Fig. 5) Normalized power loss for frequency  $\approx 0.94$

(Fig. 6) Normalized power loss for inductor value  $\approx 1.013$

Calculated Maximum Power Loss for given conditions = 15W x 0.98 x 1.14 x 0.94 x 1.013 ≈ 15.96W

#### **Calculating SOA Temperature:**

(Fig. 3) SOA Temperature Adjustment for input voltage  $\approx$  -0.5°C

(Fig. 4) SOA Temperature Adjustment for output voltage  $\approx 3.3^{\circ}\text{C}$

(Fig. 5) SOA Temperature Adjustment for frequency ≈ -1.2°C

(Fig. 6) SOA Temperature Adjustment for inductor value ≈ 0.25°C

$T_X$  axis intercept temp adjustment = - 0.5°C + 3.3°C - 1.2°C + 0.25°C  $\approx$  1.85°C

Assuming  $T_{CASE} = 110^{\circ}C \& T_{PCB} = 100^{\circ}C$ :

The following example shows how the SOA current is adjusted for a  $T_{\chi}$  increase of 1.85°C.

Fig. 9: Timing Diagram

#### **PCB Layout Guidelines**

The PCB layout and bypassing issues have been addressed with the internal design of the iP2003. One of the most critical elements of proper PCB layout with iP2003 is the placement of the external input bypass capacitors and the routing of the connecting power tracks. The iPOWIR Block will function normally without any additional external input bypass capacitors. However, the addition of the external capacitors will improve the long term reliable operation of the block.

It is recommended that the designer uses the following guidelines:

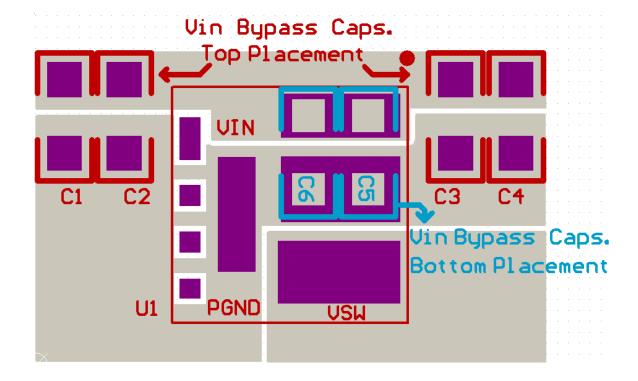

- 1. The diagram below suggests the addition of the input bypass capacitors either on the top side of the PCB (capacitors C1-C4) or top and bottom side (C5, C6), if placement on the bottom side is feasible. Although there is a certain degree of bypassing inside the iP2003, these external capacitors must be placed as close to the iPOWIR device as possible.

- 2. In the diagram below, observe the routing of the power tracks that connect the external bypass capacitors.

- 3. Provide a mid-layer solid ground plane with connections to the top through vias.

- 4. Refer to IR application note AN-1029 to determine the size of the vias and the copper weight and thickness when designing the PCB.

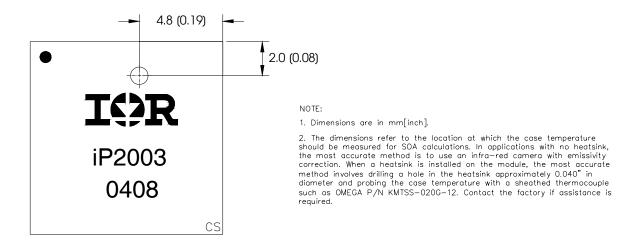

Fig 10: Maximum  $T_{\text{CASE}}$  measurement location

#### NOTES

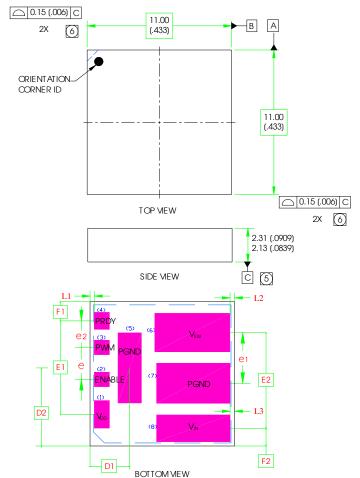

- 1. DIMENSIONING & TOLERANCING PER ASME Y14.5M-1994.

- 2. DIMENSIONS ARE SHOWN IN MILLIMETERS (INCHES).

- 3. CONTROLLING DIMENSION: MILLIMETER

- 4. LAND DESIGNATION PER JESD MO 222, SPP-010.

- 5 PRIMARY DATUM C IS SEATING PLANE.

- (6) BILATERAL TOLERANCE ZONE IS APPLIED TO EACH SIDE OF THE PACKAGE BODY.

#### LAYOUT NOTES:

- LAND PATTERN ON USERS PCB SHOULD BE AN IDENTICAL MIRROR IMAGE OF THE PATTERN SHOWN IN THE BOTTOM VIEW.

- 2. LANDS SHOULD BE SOLDER MASK DEFINED.

| DIMENSION   |   | NOMINAL | DIMENSION | NOMINAL    |

|-------------|---|---------|-----------|------------|

| (1)         | Х | 1.1430  | е         | 2.4384     |

|             | Υ | 2.1016  | el        | 3.8610     |

| (2),(3)     | Х | 1.1430  | e2        | 2.0193     |

| (2),(0)     | Υ | 1.1016  | D1        | 3.023 BSC  |

| (4)         | Х | 1.1430  | D2        | 5.945 BSC  |

| (4)         | Υ | 1.2827  | E1        | 7.1167 BSC |

| (5)         | Х | 1.778   | E2        | 7.289 BSC  |

| (0)         | Υ | 5.334   | F1        | 1.4732 BSC |

| (6)         | Х | 5.715   | F2        | 1.348 BSC  |

| (6)         | Υ | 2.921   | L1        | 0.3556     |

| <i>(</i> 7) | Х | 5.588   | L2        | 0.345      |

| (7)         | Υ | 3.048   | L3        | 0.332      |

| (8)         | Х | 5.588   |           |            |

| (0)         | Υ | 2.032   |           |            |

| REF         |   | JEDEO   | : MO-222  | )          |

Fig 11: Mechanical Drawing

Refer to the following application notes for detailed guidelines and suggestions when implementing iPOWIR Technology products:

#### AN-1030: Applying iPOWIR Products in Your Thermal Environment

This paper explains how to use the Power Loss and SOA curves in the data sheet to validate if the operating conditions and thermal environment are within the Safe Operating Area of the iPOWIR product.

AN-1047: Graphical solution for two branch heatsinking Safe Operating Area Detailed explanation of the dual axis SOA graph and how it is derived.

# AN-1028: Recommended Design, Integration and Rework Guidelines for International Rectifier's iPowlR Technology BGA and LGA Packages

This paper discusses optimization of the layout design for mounting iPowIR BGA and LGA packages on printed circuit boards, accounting for thermal and electrical performance and assembly considerations. Topics discussed includes PCB layout placement, routing, and via interconnect suggestions, as well as soldering, pick and place, reflow, cleaning and reworking recommendations.

IRDCiP2003 : Reference design for iP2003

Data and specifications subject to change without notice.

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information.11/04