Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <a href="http://www.nxp.com">http://www.nxp.com</a>, <a href="http://www.semiconductors.philips.com/">http://www.nxp.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>)

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use salesaddresses@nexperia.com (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

# IP4786CZ32

DVI and HDMI interface ESD and overcurrent protection, DDC/CEC buffering, hot plug detect and backdrive protection

Rev. 5 — 24 June 2014

Product data sheet

### 1. Product profile

#### 1.1 General description

The IP4786CZ32 is designed to protect High-Definition Multimedia Interface (HDMI) transmitter host interfaces. It includes HDMI 5 V overcurrent / overvoltage protection, Display Data Channel (DDC) buffering and decoupling, hot plug detect, backdrive protection, Consumer Electronic Control (CEC) buffering and decoupling, and ±12 kV contact ElectroStatic Discharge (ESD) protection for all I/Os, exceeding the IEC 61000-4-2 level 4 standard.

The IP4786CZ32 incorporates Transmission Line Clamping (TLC) technology on the high-speed Transition Minimized Differential Signaling (TMDS) lines to simplify routing and help reduce impedance discontinuities. All TMDS lines are protected by an impedance-matched diode configuration that minimizes impedance discontinuities caused by typical shunt diodes.

The enhanced 60 mA overcurrent / overvoltage linear regulator guarantees HDMI-compliant 5 V output voltage levels with up to 6.5 V inputs.

The DDC lines use a new buffering concept which decouples the internal capacitive load from the external capacitive load for use with standard Complementary Metal Oxide Semiconductor (CMOS) or Low Voltage Transistor-Transistor Logic (LVTTL) I/O cells down to 1.8 V. This buffering also redrives the DDC and CEC signals, allowing the use of longer or cheaper HDMI cables with a higher capacitance. The internal hot plug detect module simplifies the application of the HDMI transmitter to control the hot plug signal.

All lines provide appropriate integrated pull-ups and pull-downs for HDMI compliance and backdrive protection to guarantee that HDMI interface signals are not pulled down if the system is powered down or enters Standby mode. Only a single external capacitor is required for operation.

#### 1.2 Features and benefits

- HDMI 2.0 and all backward compatible standards are supported

- 6.0 Gbps TMDS Bit Rate (600 Mcsc TMDS Character Rate) compatible

- Supports UHD 4k (2160p) 60 Hz display modes

- Impedance matched 100  $\Omega$  differential transmission line ESD protection for TMDS lines ( $\pm 10~\Omega$ ). No Printed-Circuit Board (PCB) pre-compensation required

- Simplified flow-through routing utilizing less overall PCB space

- DDC capacitive decoupling between system side and HDMI connector side and buffering to drive cable with high capacitive load (> 700 pF/25 m)

# All external I/O lines with ESD protection of at least ±12 kV, exceeding the

DVI and HDMI interface ESD and overcurrent protection

Hot plug detect module

IEC 61000-4-2, level 4 standard

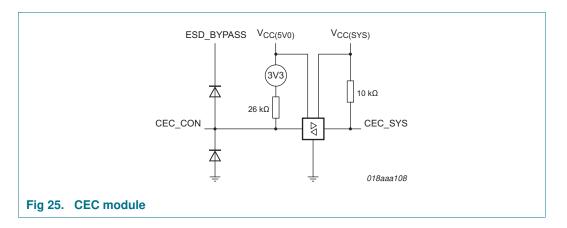

- CEC buffering and isolation, with integrated backdrive-protected 26 kΩ pull-up

- Robust ESD protection without degradation after repeated ESD strikes

- Highest integration in a small footprint, PCB level, optimized RF routing,

32-pin HVQFN leadless package

### 1.3 Applications

- The IP4786CZ32 can be used for a wide range of HDMI source devices, consumer and computing electronics:

- ◆ Standard-Definition (SD) and High-Definition (HD) DVD player

- Set-top box

- PC graphic card

- Game console

- ◆ HDMI picture performance quality enhancer module

- Digital Visual Interface (DVI)

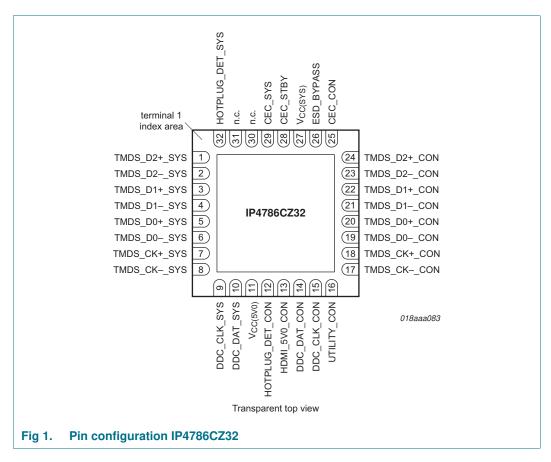

## 2. Pinning information

### 2.1 Pinning

IP4786CZ32

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2014. All rights reserved

### **DVI and HDMI interface ESD and overcurrent protection**

# 2.2 Pin description

Table 1. Pin description

| Pin        | Name                 | Description                                                    |

|------------|----------------------|----------------------------------------------------------------|

| 1          | TMDS_D2+_SYS         | TMDS to ASIC inside system                                     |

| 2          | TMDS_D2SYS           | TMDS to ASIC inside system                                     |

| 3          | TMDS_D1+_SYS         | TMDS to ASIC inside system                                     |

| 4          | TMDS_D1SYS           | TMDS to ASIC inside system                                     |

| 5          | TMDS_D0+_SYS         | TMDS to ASIC inside system                                     |

| 6          | TMDS_D0SYS           | TMDS to ASIC inside system                                     |

| 7          | TMDS_CK+_SYS         | TMDS to ASIC inside system                                     |

| 8          | TMDS_CKSYS           | TMDS to ASIC inside system                                     |

| 9          | DDC_CLK_SYS          | DDC clock system side                                          |

| 10         | DDC_DAT_SYS          | DDC data system side                                           |

| 11         | V <sub>CC(5V0)</sub> | 5 V supply input                                               |

| 12         | HOTPLUG_DET_CON      | hot plug detect connector side                                 |

| 13         | HDMI_5V0_CON         | 5 V overcurrent out to connector                               |

| 14         | DDC_DAT_CON          | DDC data connector side                                        |

| 15         | DDC_CLK_CON          | DDC clock connector side                                       |

| 16         | UTILITY_CON          | utility line ESD protection                                    |

| 17         | TMDS_CKCON           | TMDS ESD protection to connector                               |

| 18         | TMDS_CK+_CON         | TMDS ESD protection to connector                               |

| 19         | TMDS_D0CON           | TMDS ESD protection to connector                               |

| 20         | TMDS_D0+_CON         | TMDS ESD protection to connector                               |

| 21         | TMDS_D1CON           | TMDS ESD protection to connector                               |

| 22         | TMDS_D1+_CON         | TMDS ESD protection to connector                               |

| 23         | TMDS_D2CON           | TMDS ESD protection to connector                               |

| 24         | TMDS_D2+_CON         | TMDS ESD protection to connector                               |

| 25         | CEC_CON              | CEC signal connector side                                      |

| 26         | ESD_BYPASS           | ESD bias voltage                                               |

| 27         | V <sub>CC(SYS)</sub> | supply voltage for level shifting                              |

| 28         | CEC_STBY             | CEC Standby mode control (LOW for lowest power, CEC-only mode) |

| 29         | CEC_SYS              | CEC I/O signal system side                                     |

| 30         | n.c.                 | not connected                                                  |

| 31         | n.c.                 | not connected                                                  |

| 32         | HOTPLUG_DET_SYS      | hot plug detect system side                                    |

| ground pad | GND                  | ground                                                         |

## DVI and HDMI interface ESD and overcurrent protection

# 3. Ordering information

Table 2. Ordering information

| Type number | Package |                                                                                                            |          |  |  |  |  |

|-------------|---------|------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|             | Name    | Description V                                                                                              |          |  |  |  |  |

| IP4786CZ32  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85$ mm | SOT617-3 |  |  |  |  |

#### **DVI and HDMI interface ESD and overcurrent protection**

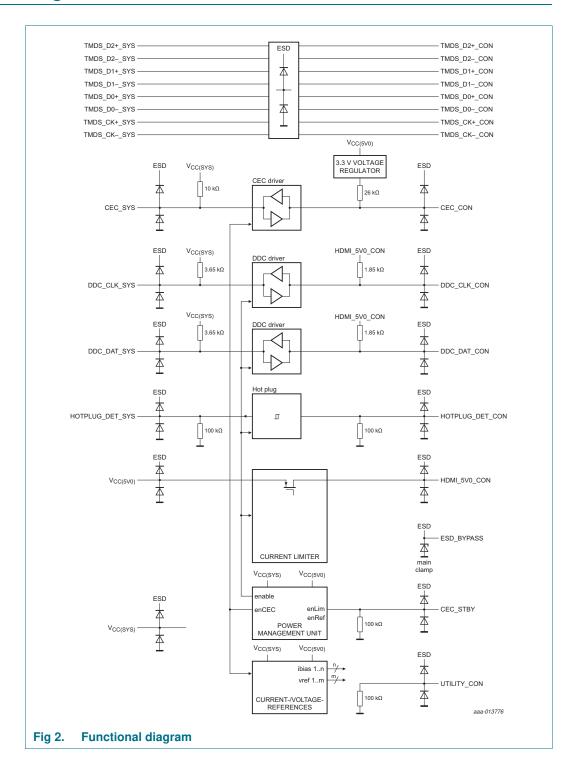

# 4. Functional diagram

## DVI and HDMI interface ESD and overcurrent protection

# 5. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                                                                 | Parameter               | Conditions                                                                                                              | Min       | Max  | Unit |

|------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|------|------|

| V <sub>CC(5V0)</sub>                                                   | supply voltage (5.0 V)  |                                                                                                                         | GND - 0.5 | 6.5  | V    |

| VI                                                                     | input voltage           | I/O pins                                                                                                                | GND - 0.5 | 5.5  | V    |

| V <sub>ESD</sub>                                                       | electrostatic discharge | IEC 61000-4-2, level 4 (contact) [1]                                                                                    | -         | ±12  | kV   |

| V <sub>CC(5V0)</sub> sup<br>V <sub>I</sub> inp<br>V <sub>ESD</sub> ele | voltage                 | IEC 61000-4-2, level 1 (contact) [2]                                                                                    | -         | ±2   | kV   |

| P <sub>tot</sub>                                                       | total power dissipation | DDC operating at 100 kHz;<br>CEC operating at 1 kHz;<br>50 % duty cycle; CEC_STBY = HIGH;<br>no current at HDMI_5V0_CON | -         | 50   | mW   |

|                                                                        |                         | DDC and CEC bus in idle mode;<br>CEC_STBY = HIGH;<br>no current at HDMI_5V0_CON                                         | -         | 3.0  | mW   |

|                                                                        |                         | DDC and CEC bus in idle mode;<br>CEC_STBY = LOW                                                                         | -         | 1.0  | mW   |

| T <sub>amb</sub>                                                       | ambient temperature     |                                                                                                                         | -25       | +85  | °C   |

| T <sub>stg</sub>                                                       | storage temperature     |                                                                                                                         | -55       | +125 | °C   |

<sup>[1]</sup> Connector-side pins (typically denoted with "\_CON" suffix) to ground.

<sup>[2]</sup> System-side pins: CEC\_SYS, DDC\_DAT\_SYS, DDC\_CLK\_SYS, HOTPLUG\_DET\_SYS, CEC\_STBY, V<sub>CC(SYS)</sub> and V<sub>CC(5V0)</sub>.

#### DVI and HDMI interface ESD and overcurrent protection

#### 6. Static characteristics

Table 4. Supplies

$T_{amb} = -25$  °C to +85 °C unless otherwise specified.

| Symbol               | Parameter              | Conditions | Min  | Тур | Max | Unit |

|----------------------|------------------------|------------|------|-----|-----|------|

| V <sub>CC(5V0)</sub> | supply voltage (5.0 V) | [1]        | 4.5  | 5.0 | 6.5 | V    |

| V <sub>CC(SYS)</sub> | system supply voltage  |            | 1.62 | 3.3 | 5.5 | V    |

<sup>[1]</sup> The IP4786CZ32 contains a 5 V voltage regulator function for higher input voltages. Any input voltage of 4.925 V < V<sub>CC(5V0)</sub> < 6.50 V will provide HDMI-compliant output levels of 4.8 V to 5.3 V on HDMI\_5V0\_CON.

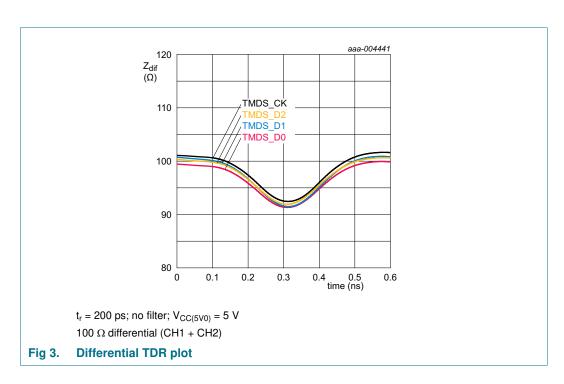

Table 5. TMDS protection circuit

$T_{amb} = -25$  °C to +85 °C unless otherwise specified.

| Symbol                      | Parameter                                   | Conditions                                                           |        | Min | Тур | Max | Unit |

|-----------------------------|---------------------------------------------|----------------------------------------------------------------------|--------|-----|-----|-----|------|

| TMDS chan                   | nel                                         |                                                                      |        |     |     |     |      |

| $Z_{i(dif)}$                | differential input impedance                | TDR measured;<br>t <sub>r</sub> = 200 ps                             |        | 90  | 100 | 110 | Ω    |

| C <sub>eff</sub>            | effective capacitance                       | equivalent shunt capacitance for TDR minimum; $t_r = 200 \text{ ps}$ |        | -   | 0.6 | -   | pF   |

| Protection of               | diode                                       |                                                                      |        |     | '   |     |      |

| $V_{BRzd}$                  | Zener diode breakdown voltage               | I = 1.0 mA                                                           |        | 6.0 | -   | 9.0 | V    |

| r <sub>dyn</sub>            | dynamic resistance                          | surge; I = 1.0 A;<br>IEC 61000-4-5/9                                 |        |     |     |     |      |

|                             |                                             | positive transient                                                   |        | -   | 1.0 | -   | Ω    |

|                             |                                             | negative transient                                                   |        | -   | 1.0 | -   | Ω    |

|                             |                                             | TLP                                                                  |        |     |     |     |      |

|                             |                                             | positive transient                                                   | [3]    | -   | 1.0 | -   | Ω    |

|                             |                                             | negative transient                                                   | [3]    | -   | 1.0 | -   | Ω    |

| I <sub>bck</sub>            | back current                                | $V_{CC(5V0)} < V_{ch(TMDS)}$                                         | [4][5] | -   | 0.1 | 1.0 | μА   |

| I <sub>LR</sub>             | reverse leakage current                     | $V_1 = 3.0 \text{ V}$                                                |        | -   | 1.0 | -   | μΑ   |

| V <sub>F</sub>              | forward voltage                             |                                                                      |        | -   | 0.7 | -   | V    |

| V <sub>CL(ch)trt(pos)</sub> | positive transient channel clamping voltage | 100 ns TLP; 50 $\Omega$ pulser at 50 ns                              |        | -   | 8.0 | -   | V    |

- [1] This parameter is guaranteed by design.

- [2] Capacitive dip at HDMI Time Domain Reflectometer (TDR) measurement conditions.

- [3] ANSI-ESDSP5.5.1-2004, ESD sensitivity testing Transmission Line Pulse (TLP) component level method 50 TDR.

- [4] Signal pins:

- TMDS\_D0+\_CON, TMDS\_D0-\_CON, TMDS\_D1+\_CON, TMDS\_D1-\_CON, TMDS\_D2+\_CON, TMDS\_D2-\_CON, TMDS\_CK+\_CON, TMDS\_CK-\_CON, TMDS\_D0+\_SYS, TMDS\_D0-\_SYS, TMDS\_D1+\_SYS, TMDS\_D1-\_SYS, TMDS\_D2+\_SYS, TMDS\_D2-\_SYS, TMDS\_CK+\_SYS and TMDS\_CK-\_SYS.

- [5] Backdrive current from TMDS\_x\_SYS and TMDS\_x\_CON pins to local V<sub>CC(5V0)</sub> bias rail at power-down. Device does not block backdrive current leakage through the device to/from ASIC I/O pins connected to TMDS\_x\_SYS pins.

#### **DVI and HDMI interface ESD and overcurrent protection**

Table 6. HDMI\_5V0\_CON

$T_{amb}$  = -25 °C to +85 °C unless otherwise specified.

| Symbol              | Parameter                    | Conditions                                                          |            | Min | Тур  | Max | Unit |

|---------------------|------------------------------|---------------------------------------------------------------------|------------|-----|------|-----|------|

| r <sub>dyn</sub>    | dynamic resistance           | TLP                                                                 |            |     |      |     |      |

|                     |                              | positive transient                                                  | <u>[1]</u> | -   | 1.0  | -   | Ω    |

|                     |                              | negative transient                                                  | <u>[1]</u> | -   | 1.0  | -   | Ω    |

| V <sub>CL</sub>     | clamping voltage             | 100 ns TLP;<br>50 Ω pulser at 50 ns                                 |            | -   | 8    | -   | V    |

| I <sub>O(max)</sub> | maximum output current       | V <sub>(HDMI_5V0_CON)</sub> = 4.8 V                                 |            | 55  | -    | -   | mA   |

| I <sub>bck</sub>    | back current                 | $V_{CC(5V0)} < V_{(HDMI\_5V0\_CON)}$                                |            | -   | -    | 10  | μА   |

| I <sub>O(sc)</sub>  | short-circuit output current | $V_{(HDMI\_5V0\_CON)} = 0 V$                                        |            | -   | 125  | 175 | mA   |

| $V_{do}$            | dropout voltage              | 4.5 V < V <sub>CC(5V0)</sub> < 4.925 V;<br>DDC = LOW                | [2]        |     |      |     |      |

|                     |                              | I <sub>O</sub> = 10 mA                                              |            | -   | 70   | -   | mV   |

|                     |                              | I <sub>O</sub> = 55 mA                                              |            | -   | -    | 125 | mV   |

| V <sub>O(LDO)</sub> | LDO output voltage           | $I_{O} \le 55$ mA;<br>4.925 V < $V_{CC(5V0)} < 6.5$ V;<br>DDC = LOW | [2]        | 4.8 | 5.05 | 5.3 | V    |

<sup>[1]</sup> ANSI-ESDSP5.5.1-2004, ESD sensitivity testing TLP component level method 50 TDR.

Table 7. UTILITY\_CON

$T_{amb} = -25$  °C to +85 °C unless otherwise specified.

| Symbol           | Parameter                                          | Conditions                                                                                                                                                                                      |     | Min | Тур | Max | Unit |

|------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|

| Supplies:        | pins V <sub>CC(5V0)</sub> and V <sub>CC(SYS)</sub> |                                                                                                                                                                                                 |     |     |     |     |      |

| r <sub>dyn</sub> | dynamic resistance                                 | TLP                                                                                                                                                                                             |     |     |     |     |      |

|                  |                                                    | positive transient                                                                                                                                                                              | [1] | -   | 1.0 | -   | Ω    |

|                  |                                                    | negative transient                                                                                                                                                                              | [1] | -   | 1.0 | -   | Ω    |

| V <sub>CL</sub>  | clamping voltage                                   | 100 ns TLP;<br>50 Ω pulser at 50 ns                                                                                                                                                             |     | -   | 8.0 | -   | V    |

| C <sub>i</sub>   | input capacitance                                  | $\begin{split} &V_{CC(5V0)} = 0 \text{ V;} \\ &V_{CC(SYS)} = 0 \text{ V; } V_{bias} = 2.5 \text{ V;} \\ &AC \text{ input } = 3.5 \text{ V}_{(p\text{-}p)}; \\ &f = 100 \text{ kHz} \end{split}$ |     | -   | 8.0 | 10  | pF   |

| R <sub>pd</sub>  | pull-down resistance                               |                                                                                                                                                                                                 |     | 60  | 100 | 140 | kΩ   |

<sup>[1]</sup> ANSI-ESDSP5.5.1-2004, ESD sensitivity testing TLP component level method 50 TDR.

<sup>[2]</sup> The IP4786CZ32 contains a 5 V voltage regulator function for higher input voltages. Any input voltage of 4.925 V < V<sub>CC(5V0)</sub> < 6.50 V will provide HDMI-compliant output levels of 4.8 V to 5.3 V on HDMI\_5V0\_CON.

### **DVI and HDMI interface ESD and overcurrent protection**

Table 8. Static characteristics

$T_{amb}$  = -25 °C to +85 °C unless otherwise specified.

| Symbol            | Parameter                 | Conditions                                                                                                                                                                                 | Min                                                              | Тур  | Max                                                               | Unit |

|-------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|-------------------------------------------------------------------|------|

| DDC buff          | er on connector side[1]   |                                                                                                                                                                                            |                                                                  |      |                                                                   |      |

| V <sub>IH</sub>   | HIGH-level input voltage  |                                                                                                                                                                                            | $\begin{matrix} 0.5 \times \\ V_{(HDMI\_5V0\_CON)} \end{matrix}$ | -    | 6.5                                                               | V    |

| V <sub>IL</sub>   | LOW-level input voltage   |                                                                                                                                                                                            | -0.5                                                             | -    | $\begin{array}{c} 0.3 \times \\ V_{(HDMI\_5V0\_CON)} \end{array}$ | V    |

| V <sub>OH</sub>   | HIGH-level output voltage | [2]                                                                                                                                                                                        | V <sub>(HDMI_5V0_CON)</sub><br>- 0.02                            | -    | V <sub>(HDMI_5V0_CON)</sub><br>+ 0.02                             | V    |

| V <sub>OL</sub>   | LOW-level output voltage  | internal pull-up and external sink                                                                                                                                                         | -                                                                | 100  | 200                                                               | mV   |

| V <sub>IK</sub>   | input clamping voltage    | $I_I = -18 \text{ mA}$                                                                                                                                                                     | -                                                                | -    | -1.0                                                              | ٧    |

| C <sub>IO</sub>   | input/output capacitance  | $V_{CC(5V0)} = 5.0 \text{ V};$ [2]3] $V_{CC(5YS)} = 3.3 \text{ V};$ CEC_STBY = HIGH                                                                                                        | -                                                                | 8.0  | 10                                                                | pF   |

| R <sub>pu</sub>   | pull-up resistance        |                                                                                                                                                                                            | 1.6                                                              | 1.8  | 2.0                                                               | kΩ   |

| DDC buff          | er on system side[1][4]   |                                                                                                                                                                                            |                                                                  |      |                                                                   |      |

| V <sub>IH</sub> I | HIGH-level input voltage  | $V_{CC(SYS)} = 1.8 \text{ V}$                                                                                                                                                              | 450                                                              | -    | -                                                                 | mV   |

|                   |                           | V <sub>CC(SYS)</sub> = 2.5 V                                                                                                                                                               | 620                                                              | -    | -                                                                 | mV   |

|                   |                           | $V_{CC(SYS)} = 3.3 \text{ V}$                                                                                                                                                              | 760                                                              | -    | -                                                                 | mV   |

|                   |                           | $V_{CC(SYS)} = 5.0 \text{ V}$                                                                                                                                                              | 800                                                              | -    | -                                                                 | mV   |

| $V_{IL}$          | LOW-level input voltage   | $V_{CC(SYS)} = 1.8 \text{ V}$                                                                                                                                                              | -                                                                | -    | 330                                                               | mV   |

|                   |                           | V <sub>CC(SYS)</sub> = 2.5 V                                                                                                                                                               | -                                                                | -    | 380                                                               | mV   |

|                   |                           | $V_{CC(SYS)} = 3.3 \text{ V}$                                                                                                                                                              | -                                                                | -    | 400                                                               | mV   |

|                   |                           | $V_{CC(SYS)} = 5.0 \text{ V}$                                                                                                                                                              | -                                                                | -    | 420                                                               | mV   |

| V <sub>OH</sub>   | HIGH-level output voltage | [2]                                                                                                                                                                                        | $V_{\text{CC(SYS)}} - 0.02$                                      | -    | V <sub>CC(SYS)</sub> + 0.02                                       | V    |

| V <sub>OL</sub>   | LOW-level output voltage  | $V_{CC(SYS)} = 1.8 \text{ V}$ [5]                                                                                                                                                          | -                                                                | 490  | 500                                                               | mV   |

|                   |                           | $V_{CC(SYS)} = 2.5 \text{ V}$ [5]                                                                                                                                                          | -                                                                | 640  | 690                                                               | mV   |

|                   |                           | $V_{CC(SYS)} = 3.3 \text{ V}$ [5]                                                                                                                                                          | -                                                                | 685  | 790                                                               | mV   |

|                   |                           | $V_{CC(SYS)} = 5.0 \text{ V}$ [5]                                                                                                                                                          | -                                                                | 720  | 820                                                               | mV   |

| $V_{IK}$          | input clamping voltage    | $I_I = -18 \text{ mA}$                                                                                                                                                                     | -                                                                | -    | -1.0                                                              | ٧    |

| C <sub>IO</sub>   | input/output capacitance  | $\begin{split} &V_{CC(5V0)} = 0 \text{ V;} \\ &V_{CC(SYS)} = 0 \text{ V;} \\ &V_{bias} = 2.5 \text{ V;} \\ &AC \text{ input} = 3.5 \text{ V}_{(p-p)}; \\ &f = 100 \text{ kHz} \end{split}$ | -                                                                | 6.0  | 8.0                                                               | pF   |

| R <sub>pu</sub>   | pull-up resistance        |                                                                                                                                                                                            | 3.2                                                              | 3.65 | 4.1                                                               | kΩ   |

### **DVI and HDMI interface ESD and overcurrent protection**

**Table 8.** Static characteristics ... continued  $T_{amb} = -25$  °C to +85 °C unless otherwise specified.

| Symbol                 | Parameter                 | Conditions                                                                                                                                                                                  |     | Min                  | Тур  | Max                  | Unit |

|------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|------|----------------------|------|

| CEC_CO                 | V[1]                      |                                                                                                                                                                                             |     |                      |      |                      |      |

| V <sub>IH</sub>        | HIGH-level input voltage  |                                                                                                                                                                                             |     | 2.0                  | -    | -                    | V    |

| V <sub>IL</sub>        | LOW-level input voltage   |                                                                                                                                                                                             |     | -                    | -    | 0.80                 | V    |

| V <sub>OH</sub>        | HIGH-level output voltage |                                                                                                                                                                                             |     | 2.88                 | 3.3  | 3.63                 | V    |

| V <sub>OL</sub>        | LOW-level output voltage  | I <sub>OL</sub> = 1.5 mA                                                                                                                                                                    |     | -                    | 100  | 200                  | mV   |

| C <sub>IO</sub>        | input/output capacitance  | $\begin{split} &V_{CC(5V0)} = 0 \text{ V;} \\ &V_{CC(SYS)} = 0 \text{ V;} \\ &V_{bias} = 1.65 \text{ V;} \\ &AC \text{ input} = 2.5 \text{ V}_{(p-p)}; \\ &f = 100 \text{ kHz} \end{split}$ | [2] | -                    | 8.0  | 10                   | pF   |

| R <sub>pu</sub>        | pull-up resistance        |                                                                                                                                                                                             |     | 23.4                 | 26.0 | 28.6                 | kΩ   |

| I <sub>leak(CEC)</sub> | CEC leakage current       | $V_{CC(5V0)} = 0 \text{ V};$<br>$V_{CC(SYS)} = 0 \text{ V};$<br>CEC_CON connected<br>to 3.63 V via 27 k $\Omega$                                                                            |     | -                    | -    | 0.1                  | μА   |

| CEC_SYS                | <u>[1][4]</u>             |                                                                                                                                                                                             |     |                      | •    | *                    | -    |

| V <sub>IH</sub>        | HIGH-level input voltage  | $V_{CC(SYS)} = 1.8 \text{ V}$                                                                                                                                                               |     | 450                  | -    | -                    | mV   |

|                        |                           | V <sub>CC(SYS)</sub> = 2.5 V                                                                                                                                                                |     | 620                  | -    | -                    | mV   |

|                        |                           | $V_{CC(SYS)} = 3.3 \text{ V}$                                                                                                                                                               |     | 760                  | -    | -                    | mV   |

|                        |                           | $V_{CC(SYS)} = 5.0 \text{ V}$                                                                                                                                                               |     | 800                  | -    | -                    | mV   |

| $V_{IL}$               | LOW-level input voltage   | V <sub>CC(SYS)</sub> = 1.8 V                                                                                                                                                                |     | -                    | -    | 330                  | mV   |

|                        |                           | V <sub>CC(SYS)</sub> = 2.5 V                                                                                                                                                                |     | -                    | -    | 380                  | mV   |

|                        |                           | $V_{CC(SYS)} = 3.3 \text{ V}$                                                                                                                                                               |     | -                    | -    | 400                  | mV   |

|                        |                           | $V_{CC(SYS)} = 5.0 \text{ V}$                                                                                                                                                               |     | -                    | -    | 420                  | mV   |

| V <sub>OH</sub>        | HIGH-level output voltage |                                                                                                                                                                                             | [2] | $V_{CC(SYS)} - 0.02$ | -    | $V_{CC(SYS)} + 0.02$ | V    |

| $V_{OL}$               | LOW-level output voltage  | $V_{CC(SYS)} = 1.8 \text{ V}$                                                                                                                                                               | [5] | -                    | 490  | 500                  | mV   |

|                        |                           | $V_{CC(SYS)} = 2.5 \text{ V}$                                                                                                                                                               | [5] | -                    | 640  | 690                  | mV   |

|                        |                           | $V_{CC(SYS)} = 3.3 \text{ V}$                                                                                                                                                               | [5] | -                    | 675  | 770                  | mV   |

|                        |                           | $V_{CC(SYS)} = 5.0 \text{ V}$                                                                                                                                                               | [5] | -                    | 710  | 800                  | mV   |

| C <sub>IO</sub>        | input/output capacitance  | $\begin{split} &V_{CC(5V0)} = 0 \text{ V;} \\ &V_{CC(SYS)} = 0 \text{ V;} \\ &V_{bias} = 1.65 \text{ V;} \\ &AC \text{ input} = 2.5 \text{ V}_{(p-p)}; \\ &f = 100 \text{ kHz} \end{split}$ | [2] | -                    | 6.0  | 7.0                  | pF   |

| R <sub>pu</sub>        | pull-up resistance        |                                                                                                                                                                                             |     | 8.5                  | 10   | 11.5                 | kΩ   |

| HOTPLU                 | G_DET_CON[1]              |                                                                                                                                                                                             |     |                      | •    |                      | •    |

| V <sub>IH</sub>        | HIGH-level input voltage  |                                                                                                                                                                                             |     | 2.0                  | -    | -                    | V    |

| V <sub>IL</sub>        | LOW-level input voltage   |                                                                                                                                                                                             |     | -                    | -    | 0.8                  | V    |

| R <sub>pd</sub>        | pull-down resistance      |                                                                                                                                                                                             |     | 60                   | 100  | 140                  | kΩ   |

| C <sub>i</sub>         | input capacitance         | $\begin{split} &V_{CC(5V0)} = 0 \text{ V;} \\ &V_{CC(SYS)} = 0 \text{ V;} \\ &V_{bias} = 2.5 \text{ V;} \\ &AC \text{ input} = 3.5 \text{ V}_{(p-p)}; \\ &f = 100 \text{ kHz} \end{split}$  | [2] | -                    | 8.0  | 10                   | pF   |

#### **DVI and HDMI interface ESD and overcurrent protection**

Table 8.

Static characteristics ...continued

$T_{amb}$  = -25 °C to +85 °C unless otherwise specified.

| Symbol          | Parameter                 | Conditions               | Min                      | Тур | Max | Unit |

|-----------------|---------------------------|--------------------------|--------------------------|-----|-----|------|

| HOTPLUG         | DET_SYS[1]                |                          |                          |     |     |      |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OL</sub> = 1 mA   | $0.7 \times V_{CC(SYS)}$ | -   | -   | ٧    |

| V <sub>OL</sub> | LOW-level output voltage  | $I_{OL} = -1 \text{ mA}$ | -                        | 200 | 300 | mV   |

| R <sub>pd</sub> | pull-down resistance      |                          | 60                       | 100 | 140 | kΩ   |

- [1] The device is active if the input voltage at pin CEC\_STBY is above the HIGH level.

- [2] This parameter is guaranteed by design.

- [3] Capacitive load measured at power-on.

- [4] No external pull-up resistor attached.

- [5] Typical value at  $T_{amb} = +25$  °C.

#### Table 9. CEC\_STBY power management circuit

$V_{CC(SYS)} = 1.62 \text{ V}$  to 5.5 V;  $V_{CC(5V0)} = 4.5 \text{ V}$  to 6.5 V; GND = 0 V;  $T_{amb} = -25 \text{ °C}$  to +85 °C unless otherwise specified.

| Symbol          | Parameter                | Conditions                  |     | Min  | Тур | Max | Unit |

|-----------------|--------------------------|-----------------------------|-----|------|-----|-----|------|

| Board side:     | input pin CEC_STBY[1]    |                             |     |      |     | ·   | ·    |

| V <sub>IH</sub> | HIGH-level input voltage | HIGH = active               | [2] | 1.2  | -   | 6.5 | V    |

| V <sub>IL</sub> | LOW-level input voltage  | LOW = standby               | [3] | -0.5 | -   | 0.8 | V    |

| R <sub>pd</sub> | pull-down resistance     |                             |     | 60   | 100 | 140 | kΩ   |

| C <sub>i</sub>  | input capacitance        | $V_I = 3 V \text{ or } 0 V$ |     | -    | 6   | 7   | рF   |

- [1] The CEC\_STBY pin should be connected permanently to V<sub>CC(5V0)</sub> or V<sub>CC(SYS)</sub> if no enable control is needed.

- [2] DDC buffers, Hot Plug Detect (HPD) buffer, and HDMI\_5V0\_CON out enabled; CEC buffer enabled.

- [3] DDC buffers, HPD buffer, and HDMI\_5V0\_CON out disabled; CEC buffer enabled.

#### **DVI and HDMI interface ESD and overcurrent protection**

# 7. Dynamic characteristics

Table 10. Dynamic characteristics

$V_{CC(5V0)} = 5.0 \text{ V}$ ;  $V_{CC(SYS)} = 1.8 \text{ V}$ ; GND = 0 V;  $T_{amb} = -25 \text{ °C to } +85 \text{ °C unless otherwise specified}$ .

| Symbol           | Parameter                     | Conditions                              | Min | Тур | Max | Unit |

|------------------|-------------------------------|-----------------------------------------|-----|-----|-----|------|

| DDC_DAT_         | SYS, DDC_CLK_SYS, DDC_DAT_C   | CON, DDC_CLK_CON[1]                     |     |     |     |      |

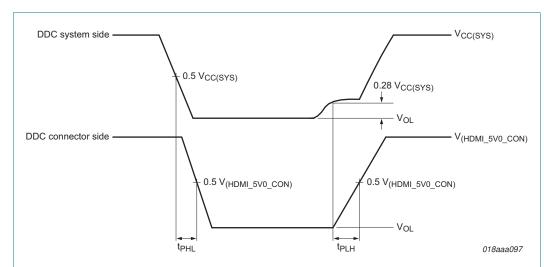

| t <sub>PLH</sub> | LOW to HIGH propagation delay | system side to connector side Figure 16 | -   | 80  | -   | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | system side to connector side Figure 16 | -   | 60  | -   | ns   |

| t <sub>PLH</sub> | LOW to HIGH propagation delay | connector side to system side Figure 17 | -   | 120 | -   | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay | connector side to system side Figure 17 | -   | 80  | -   | ns   |

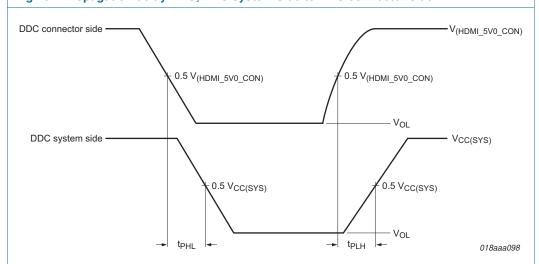

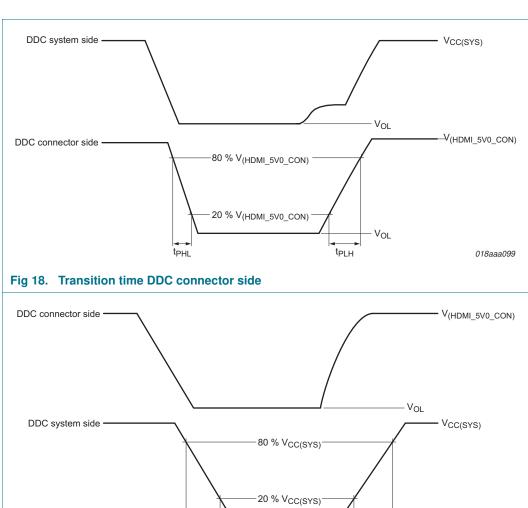

| t <sub>TLH</sub> | LOW to HIGH transition time   | connector side Figure 18                | -   | 150 | -   | ns   |

| t <sub>THL</sub> | HIGH to LOW transition time   | connector side Figure 18                | -   | 100 | -   | ns   |

| t <sub>TLH</sub> | LOW to HIGH transition time   | system side Figure 19                   | -   | 250 | -   | ns   |

| t <sub>THL</sub> | HIGH to LOW transition time   | system side Figure 19                   | -   | 80  | -   | ns   |

[1] All dynamic measurements are done with a 75 pF load. Rise times are determined by internal pull-up resistors.

#### **DVI and HDMI interface ESD and overcurrent protection**

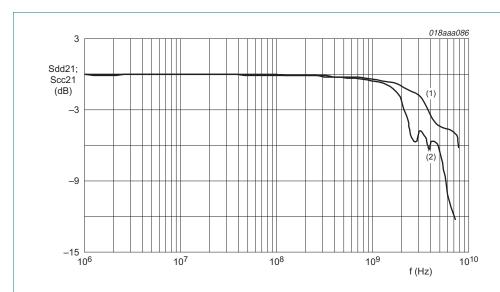

- (1) Sdd21

- (2) Scc21

Normalized to 100  $\Omega$ ; differential pairs at signal pins.

Fig 4. Mixed-mode differential and common-mode insertion loss; typical values

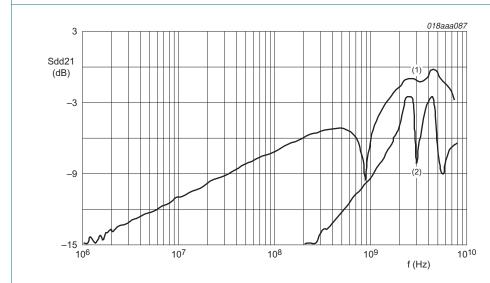

- (1) Sdd21; Near End Crosstalk (NEXT)

- (2) Sdd21; Far End Crosstalk (FEXT) normalized to 100  $\Omega$ ; differential pairs CH1/CH2 versus CH3/CH4

Fig 5. Mixed-mode differential and common-mode NEXT / FEXT; typical values

## DVI and HDMI interface ESD and overcurrent protection

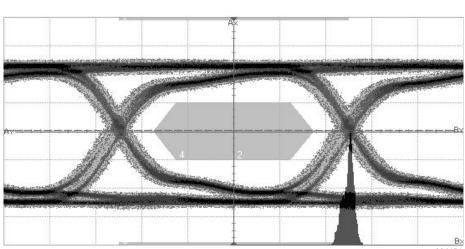

aaa-004451

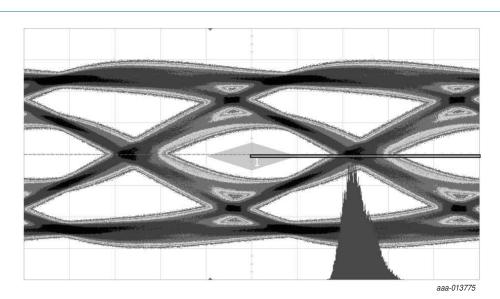

227 MHz pixel clock Horizontal scale: 90 ps/div Vertical scale: 200 mV/div

Offset: 42.6 mV

#### Fig 6. Eye diagram using IP4786CZ32 (1080p, 12 bit)

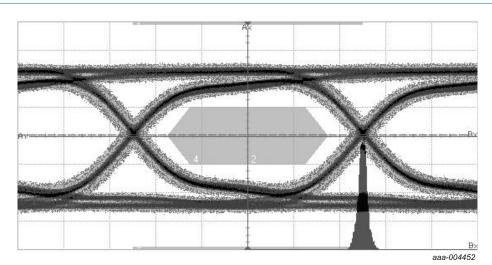

297 MHz pixel clock

Horizontal scale: 67.5 ps/div Vertical scale: 200 mV/div

Offset: 42.6 mV

Fig 7. Eye diagram using IP4786CZ32 (1080p, 16 bit)

#### **DVI and HDMI interface ESD and overcurrent protection**

148.5 MHz test frequency Horizontal scale: 53.8 ps/div

Vertical scale: 200 mV/div

Measured at TP2 with worst cable emulator, reference cable equalizer and

worst case negative skew

Fig 8. Eye diagram using IP4786CZ32 (2160p, 60 Hz)

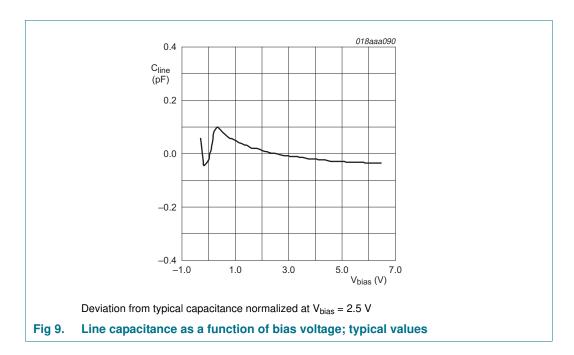

#### **DVI and HDMI interface ESD and overcurrent protection**

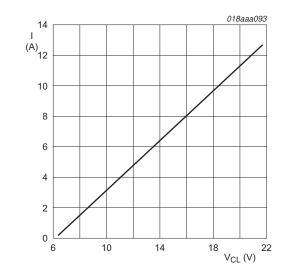

IEC 61000-4-5;  $t_p$  = 8/20  $\mu$ s; positive pulse

Fig 10. Dynamic resistance with positive clamping

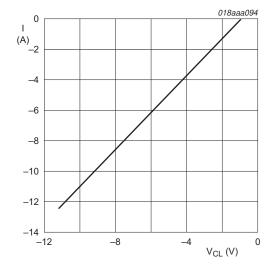

IEC 61000-4-5;  $t_p = 8/20 \mu s$ ; negative pulse

Fig 11. Dynamic resistance with negative clamping

t<sub>p</sub> = 100 ns; TLP; signal pins; typical values

Fig 12. Dynamic resistance with positive clamping

$t_p = 100 \text{ ns}$ ; TLP; signal pins; typical values

Fig 13. Dynamic resistance with negative clamping

#### **DVI and HDMI interface ESD and overcurrent protection**

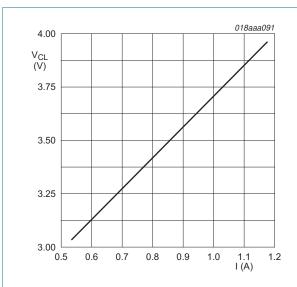

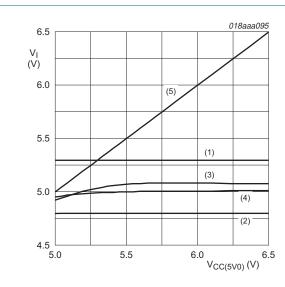

- (1) 5.3 V; maximum values; HDMI CTS TID 7-11

- (2) 4.8 V; minimum values; HDMI CTS TID 7-11

- (3) I = 0 mA

- (4) I = 55 mA

- (5)  $V_{CC(5V0)}$  supply input; 4.925 V to 6.5 V

Fig 14. Overvoltage limiter function (HDMI\_5V0\_CON)

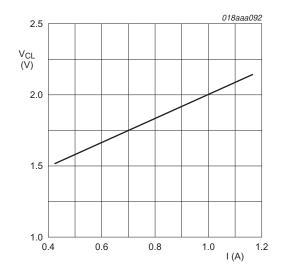

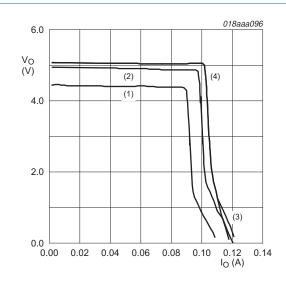

- (1)  $V_{CC(5V0)} = 4.5 \text{ V}$

- (2)  $V_{CC(5V0)} = 5.0 \text{ V}$

- (3)  $V_{CC(5V0)} = 5.5 \text{ V}$

- (4)  $V_{CC(5V0)} = 6.5 \text{ V}$

Fig 15. Overcurrent limiter function (HDMI\_5V0\_CON)

#### **DVI and HDMI interface ESD and overcurrent protection**

## 8. AC waveforms

### 8.1 DDC propagation delay

Fig 16. Propagation delay DDC, DDC system side to DDC connector side

Fig 17. Propagation delay DDC, DDC connector side to DDC system side

#### **DVI and HDMI interface ESD and overcurrent protection**

$t_{\mathsf{PLH}}$

### 8.2 DDC transition time

Fig 19. Transition time DDC system side

t<sub>PHL</sub>

018aaa100

#### DVI and HDMI interface ESD and overcurrent protection

# 9. Application information

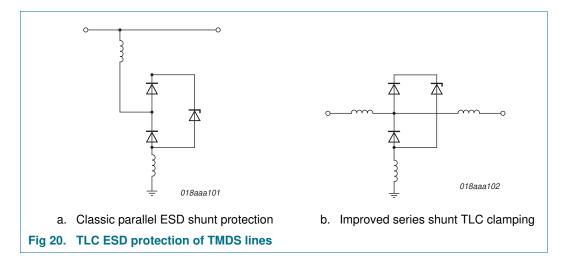

#### 9.1 TMDS ESD

To protect the TMDS lines and also to comply with the impedance requirements of the HDMI specification, the IP4786CZ32 provides ESD protection with matched TLC ESD structures. Typical Dual Rail Clamp (DRC) or rail-to-rail shunt structures are common for low-capacitance ESD protection (as shown on the left side of Figure 20) where the dominant factor for the TMDS line impedance dip is determined by the capacitive load to ground. Parasitic lead inductances of the packaging in this case works against the ESD clamping performance by including the  $\Delta I/\Delta t$  reactance of the inductance into the path of the ESD shunt.

The IP4786CZ32 utilizes these inherent inductances in series with the transmission line in order to present an effective capacitive load of roughly only 0.7 pF. This TLC structure minimizes the capacitive dip, for ideal signal integrity (Figure 20; right side) without complicated PCB pre-compensation. As a beneficial side effect, this enhances the ESD performance of the device as well, since the reactance of the series inductance attenuates the fast initial peak of the ESD pulse, for a lower residual pulse delivered to the Application Specific Integrated Circuit (ASIC).

#### **DVI and HDMI interface ESD and overcurrent protection**

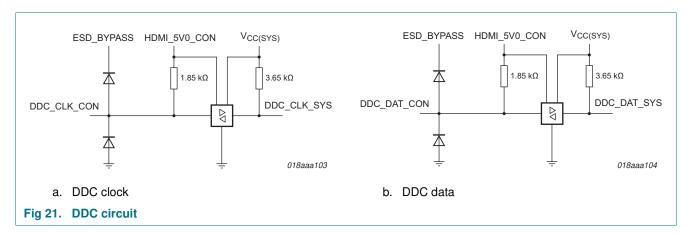

#### 9.2 DDC circuit

The DDC bus circuit integrates all required pull-ups, and provides full capacitive decoupling between the HDMI connector and the DDC bus lines on the PCB. The capacitive decoupling ensures that the maximum capacitive load is well within the 50 pF maximum of the HDMI specification. No external pull-ups or pull-downs are required.

The bidirectional buffers support high-capacitive load on the HDMI cable-side. Various non-compliant but prevalent low-cost cables have been observed with a capacitive load of up to 6 nF on the DDC lines, far exceeding the 700 pF HDMI limit. The IP4786CZ32 can easily decouple this from the weaker ASIC I/O buffers, and drive the rogue cable successfully.

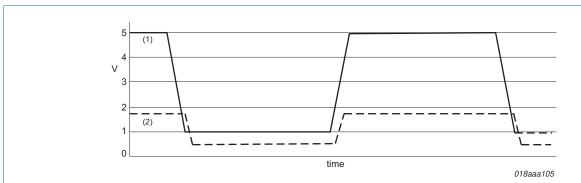

- (1) Valid  $I^2C$  signaling example on the cable (connector side) from 5 V (HIGH) to approximately 1 V (LOW).

- (2) Valid logic-level signaling example to the ASIC (system side) from 1.8 V (HIGH) to approximately 0.5 V (LOW).

Fig 22. DDC level shifting waveform example

#### **DVI and HDMI interface ESD and overcurrent protection**

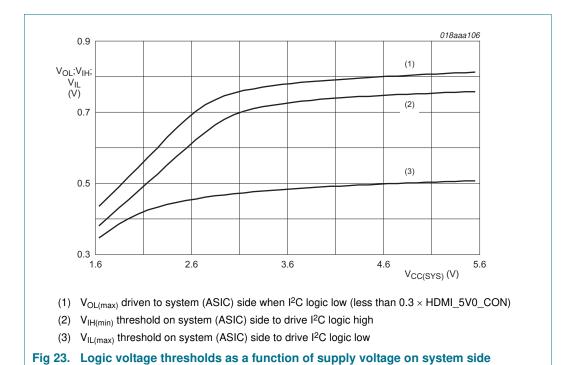

## 9.3 Logic low I<sup>2</sup>C voltage shifter

The DDC buffers provide an additional feature commonly required for high-integration HDMI ASICs which are limited to CMOS or LVTTL LOW-level input voltage ( $V_{IL}$ ) on their available I/O buffer cells. These I/Os are not strictly compliant with the 0.3  $V_{DD}$  threshold voltage levels of I<sup>2</sup>C and may miss intended logic low levels on the cable between 0.8 V and 1.5 V (typical values).

This feature is also included in the CEC buffer, and thus allows standard I/O buffer cells to be used in ASICs and microcontrollers.

#### DVI and HDMI interface ESD and overcurrent protection

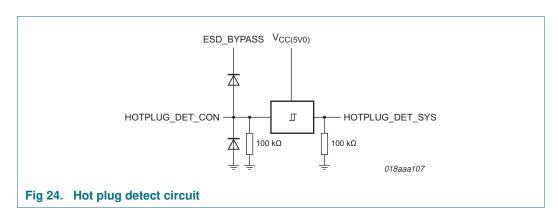

### 9.4 Hot plug detect circuit and HEAC support

The IP4786CZ32 includes a hot plug detect circuit that simplifies the hot plug application. The circuit generates a standard logic level from the hot plug signal.

The hot plug detect circuit is pulling down the signal to avoid any floating signal. The comparator guarantees a save detection of the 2 V hot plug signal without any glitches or oscillation at the hot plug output.

The IP4786CZ32 also provides an additional ESD pin to protect the reserved / HEAC pin along with hot plug detect to 12 kV, exceeding IEC 61000-4-2 level 4.

#### 9.5 CEC

The logical multidrop topology of the CEC bus can include complex physical stubs, loading cables, and interconnects that may deteriorate signal quality. The IP4786CZ32 includes a full bidirectional buffer to drive the CEC bus and isolate the CEC microcontroller or ASIC General-Purpose Input/Output (GPIO).

The CEC buffer derives power from an on-board 3.3 V regulator from the  $V_{CC(5V0)}$  domain (see <u>Figure 25</u>). This allows extensive system power management configurations and guarantees an HDMI-compliant  $V_{(CEC\_CON)}$  on the connector, as well as the backdrive-protected 125  $\mu$ A nominal CEC pull-up which does not degrade the bus when powered down.

By placing the CEC microcontroller and  $V_{CC(5V0)}$  input on a 5 V rail as shown in <u>Figure 28</u>, the CEC microcontroller can communicate over CEC for power commands, and then enable the HDMI port via the CEC\_STBY pin, as well as the rest of the system as needed.

If IP4786CZ32 Standby modes are not required, or if the Power-down modes are not desired, the CEC\_STBY pin can be pulled HIGH to  $V_{\text{CC}(5V0)}$  or  $V_{\text{CC}(SYS)}$  for continuous HDMI and CEC operation.

Strapping the CEC\_STBY =  $V_{CC(SYS)} = V_{DD}$  of ASIC guarantees that all interface signals ending with the suffix "\_SYS" on the system side will be disabled when  $V_{CC(SYS)}$  goes low, protecting the ASIC I/O signals from exceeding its local  $V_{DD}$ . In this mode, even if  $V_{CC(5V0)}$  is powered, HDMI\_5V0\_CON go active and hot plug events can be detected only when the ASIC power supply rail is on.

Strapping CEC\_STBY =  $V_{CC(5V0)}$  is the most basic configuration where the buffers are enabled whenever the local  $V_{CC(5V0)}$  and  $V_{CC(SYS)}$  supplies reach minimum operating levels.

### **DVI and HDMI interface ESD and overcurrent protection**

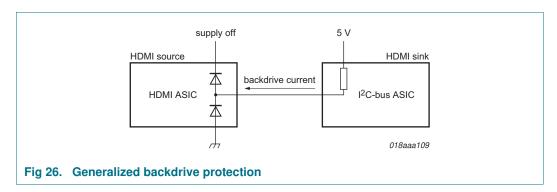

#### 9.6 Backdrive protection

The HDMI connector contains various signals which can partly supply current into an HDMI device that is powered down.

Typically, the DDC lines and the CEC signals can force significant current back into the powered-down rails as shown in <u>Figure 26</u>, causing power-on reset problems with the system, and possible damage. The IP4786CZ32 prevents this backdrive condition whenever the I/O voltage is greater than the local supply.