# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

SD 3.0-compliant memory card integrated voltage level translator with EMI filter and ESD protection

Rev. 2 — 24 May 2013

**Product data sheet**

### 1. General description

The device is an SD 3.0-compliant 6-bit bidirectional dual voltage level translator. It is designed to interface between a memory card operating at 1.8 V or 2.9 V signal levels and a host with a fixed nominal supply voltage of 1.2 V to 3.3 V. The device supports SD 3.0 SDR50, DDR50, SDR25, SDR12 and SD 2.0 High-Speed (50 MHz) and Default-Speed (25 MHz) modes. The device has an integrated switchable voltage regulator to supply the card-side I/Os, built-in EMI filters and robust ESD protections (IEC 61000-4-2, level 4).

### 2. Features and benefits

- Supports up to 100 MHz clock rate

- Feedback channel for clock synchronization

- SD 3.0 specification-compliant voltage translation to support SDR50, DDR50, SDR25, SDR12, High-Speed and Default-Speed modes

- Low dropout voltage regulator to supply the card-side I/Os

- Low-power consumption by push-pull output stage with break-before-make architecture

- Integrated pull-up and pull-down resistors: no external resistors required

- Integrated EMI filters suppress higher harmonics of digital I/Os

- Integrated 8 kV ESD protection according to IEC 61000-4-2, level 4 on card side

- Level shifting buffers keep ESD stress away from the host (zero-clamping concept)

- Pb-free, RoHS compliant and free of halogen and antimony (Dark Green compliant)

- 25-ball WLCSP; pitch 0.4 mm

## 3. Applications

- SD, MMC, microSD memory card interfaces

- Mobile phones, smartphones and tablet PCs

- Card readers in computer

- Digital cameras

## 4. Ordering information

#### Table 1.Ordering information

| Type number  | Package | age                                                                                        |            |  |  |  |  |

|--------------|---------|--------------------------------------------------------------------------------------------|------------|--|--|--|--|

|              | Name    | Description                                                                                | Version    |  |  |  |  |

| IP4855CX25/P | WLCSP25 | wafer level chip-size package; 25 bumps (5 $\times$ 5); 2.04 $\times$ 2.04 $\times$ 0.5 mm | IP4855CX25 |  |  |  |  |

SD 3.0-compliant memory card integrated dual voltage level translator

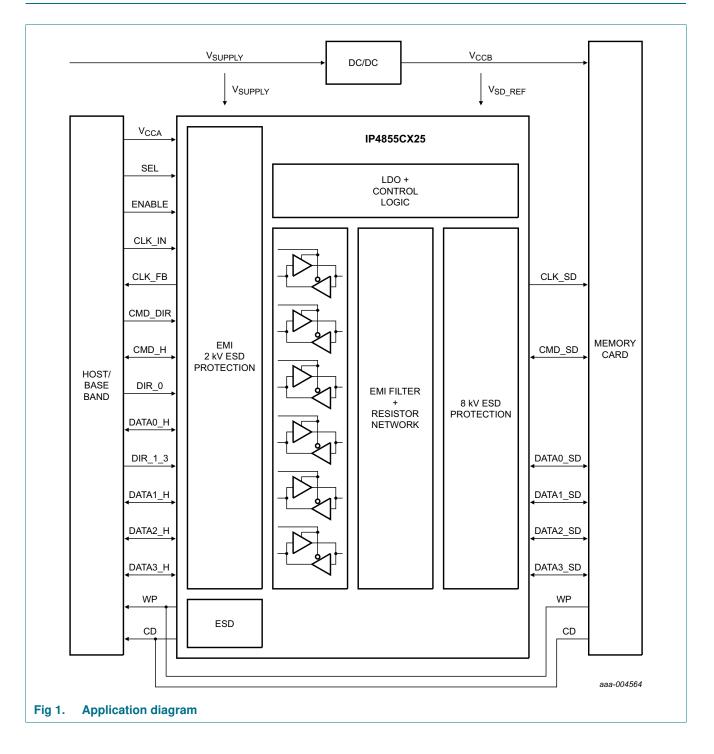

## 5. Block diagram

#### SD 3.0-compliant memory card integrated dual voltage level translator

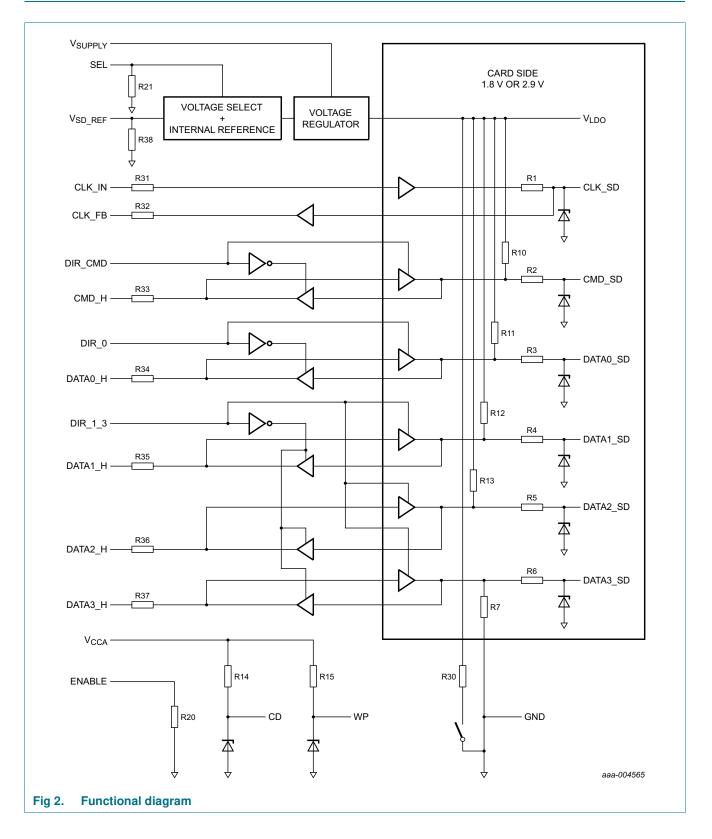

## 6. Functional diagram

P4855CX25 Product data sheet

## 7. Pinning information

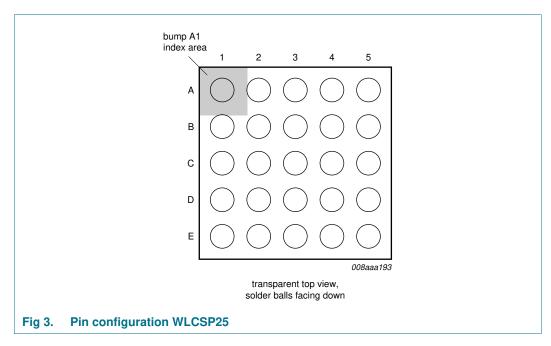

### 7.1 Pinning

#### Table 2.Pin allocation table

| Pin | Symbol  | Pin | Symbol  | Pin | Symbol           | Pin | Symbol              | Pin | Symbol   |

|-----|---------|-----|---------|-----|------------------|-----|---------------------|-----|----------|

| A1  | DATA2_H | A2  | DIR_CMD | A3  | DIR_0            | A4  | V <sub>SUPPLY</sub> | A5  | DATA2_SD |

| B1  | DATA3_H | B2  | SEL     | B3  | V <sub>CCA</sub> | B4  | $V_{LDO}$           | B5  | DATA3_SD |

| C1  | CLK_IN  | C2  | ENABLE  | C3  | GND              | C4  | $V_{SD\_REF}$       | C5  | CLK_SD   |

| D1  | DATA0_H | D2  | CMD_H   | D3  | CD               | D4  | CMD_SD              | D5  | DATA0_SD |

| E1  | DATA1_H | E2  | CLK_FB  | E3  | DIR_1_3          | E4  | WP                  | E5  | DATA1_SD |

### 7.2 Pin description

#### Table 3. Pin description

| Symbol [1]          | Pin | Type <sup>[2]</sup> | Description                                |  |  |  |

|---------------------|-----|---------------------|--------------------------------------------|--|--|--|

| DATA2_H             | A1  | I/O                 | data 2 input or output on host side        |  |  |  |

| DIR_CMD             | A2  | I                   | direction control input for command        |  |  |  |

| DIR_0               | A3  | I                   | direction control input for data 0         |  |  |  |

| V <sub>SUPPLY</sub> | A4  | S                   | supply voltage (from battery or regulator) |  |  |  |

| DATA2_SD            | A5  | I/O                 | data 2 input or output on memory card side |  |  |  |

| DATA3_H             | B1  | I/O                 | data 3 input or output on host side        |  |  |  |

| SEL                 | B2  | I                   | card side I/O voltage level select         |  |  |  |

| V <sub>CCA</sub>    | B3  | S                   | supply voltage from host side              |  |  |  |

| V <sub>LDO</sub>    | B4  | 0                   | internal supply decoupling                 |  |  |  |

| DATA3_SD            | B5  | I/O                 | data 3 input or output on memory card side |  |  |  |

|                     |     |                     |                                            |  |  |  |

P4855CX25 Product data sheet

#### **NXP Semiconductors**

#### SD 3.0-compliant memory card integrated dual voltage level translator

| Table 3.      | Pin descripti | i <b>on</b> continue | ed                                                   |

|---------------|---------------|----------------------|------------------------------------------------------|

| Symbol [1]    | Pin           | Type <sup>[2]</sup>  | Description                                          |

| CLK_IN        | C1            | I                    | clock signal input on host side                      |

| ENABLE        | C2            | l                    | device enable input                                  |

| GND           | C3            | S                    | supply ground                                        |

| $V_{SD\_REF}$ | C4            | l                    | reference voltage for the internal voltage regulator |

| CLK_SD        | C5            | 0                    | clock signal output on memory card side              |

| DATA0_H       | D1            | I/O                  | data 0 input or output on host side                  |

| CMD_H         | D2            | I/O                  | command input or output on host side                 |

| CD            | D3            | 0                    | card detect switch biasing output                    |

| CMD_SD        | D4            | I/O                  | command input or output on memory card side          |

| DATA0_SE      | D D5          | I/O                  | data 0 input or output on memory card side           |

| DATA1_H       | E1            | I/O                  | data 1 input or output on host side                  |

| CLK_FB        | E2            | 0                    | clock feedback output on host side                   |

| DIR_1_3       | E3            | I                    | direction control input for data 1, data 2, data 3   |

| WP            | E4            | 0                    | write protect switch biasing output                  |

| DATA1_SE      | ) E5          | I/O                  | data 1 input or output on memory card side           |

[1] The pin names relate particularly to SD memory cards, but also apply to microSD and MMC memory cards.

[2] I = input, O = output, I/O = input and output, S = power supply

### 8. Functional description

#### 8.1 Level translator

The bidirectional level translator shifts the data between the I/O supply levels of the host and the memory card. Dedicated direction control signals determine if a command and data signals are transferred from the memory card to the host (card read mode) or from the host to the memory card (card write mode). The voltage translator has to support several clock and data transfer rates at the signaling levels specified in the SD 3.0 standard specification.

| Signal level (V) | Clock rate (MHz)                  | Data rate (MB/s)                                                                |

|------------------|-----------------------------------|---------------------------------------------------------------------------------|

| • • •            |                                   | Data fate (MD/S)                                                                |

| 3.3              | 25                                | 12.5                                                                            |

| 3.3              | 50                                | 25                                                                              |

| 1.8              | 25                                | 12.5                                                                            |

| 1.8              | 50                                | 25                                                                              |

| 1.8              | 100                               | 50                                                                              |

| 1.8              | 50                                | 50                                                                              |

|                  | 1.8       1.8       1.8       1.8 | 3.3     25       3.3     50       1.8     25       1.8     50       1.8     100 |

#### Table 4. Supported modes

Product data sheet

IP4855CX25

5 of 30

#### 8.2 Enable and direction control

The pin ENABLE enables/disables the Low DropOut (LDO) and is used to put the host-side, card-side I/O drivers into high-ohmic 3-state mode.

| Table 5. I/O | function cont             | rol signal truth              | table      |                                  |            |  |

|--------------|---------------------------|-------------------------------|------------|----------------------------------|------------|--|

| Control      |                           | Host-side                     |            | Memory card-side                 |            |  |

| Pin          | Level <sup>[1]</sup>      | Pin                           | Function   | Pin                              | Function   |  |

| Pin ENABLE   | = HIGH and V <sub>C</sub> | <sub>CA</sub> ≥ 1.62 V        |            | '                                | "          |  |

| DIR_CMD      | Н                         | CMD_H                         | input      | CMD_SD                           | output     |  |

|              | L                         | CMD_H                         | output     | CMD_SD                           | input      |  |

| DIR_0        | Н                         | DATA0_H                       | input      | DATA0_SD                         | output     |  |

|              | L                         | DATA0_H                       | output     | DATA0_SD                         | input      |  |

| DIR_1_3      | Η                         | DATA1_H<br>DATA2_H<br>DATA3_H | input      | DATA1_SD<br>DATA2_SD<br>DATA3_SD | output     |  |

|              | L                         | DATA1_H<br>DATA2_H<br>DATA3_H | output     | DATA1_SD<br>DATA2_SD<br>DATA3_SD | input      |  |

| -            | -                         | CLK_IN                        | input      | CLK_SD                           | output     |  |

| -            | -                         | CLK_FB                        | output     | -                                | -          |  |

| Pin ENABLE   | = LOW or V <sub>CC</sub>  | ₄ ≤ 0.8 V                     |            |                                  |            |  |

| DIR_CMD      | Х                         | CMD_H                         | high-ohmic | CMD_SD                           | high-ohmic |  |

| DIR_0        | Х                         | DATA0_H                       | high-ohmic | DATA0_SD                         | high-ohmic |  |

| DIR_1_3      | Х                         | DATA1_H<br>DATA2_H<br>DATA3_H | high-ohmic | DATA1_SD<br>DATA2_SD<br>DATA3_SD | high-ohmic |  |

| -            | -                         | CLK_IN                        | input      | CLK_SD                           | high-ohmic |  |

| -            | -                         | CLK_IN                        | high-ohmic | -                                | -          |  |

[1] H = HIGH; L = LOW and X = don't care.

#### 8.3 Integrated voltage regulator

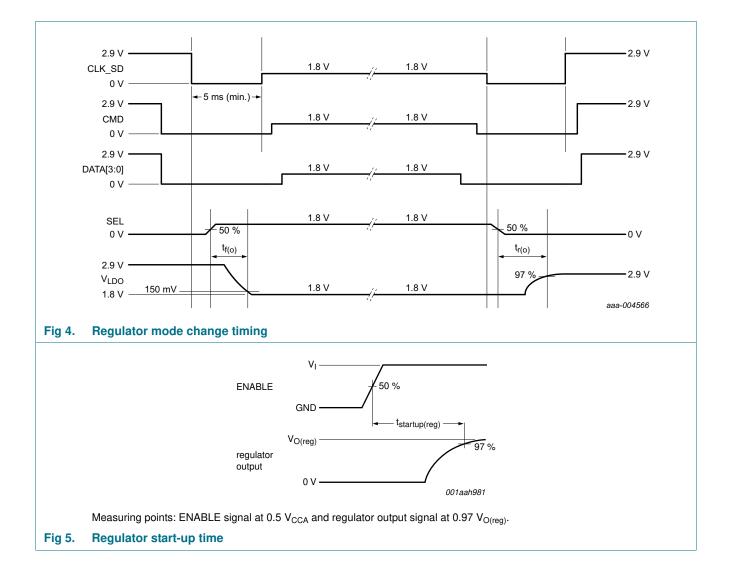

The low dropout voltage regulator delivers supply voltage for the voltage translators and the card-side input/output stages. It has to support 1.8 V and 3 V signaling modes as stipulated in the SD 3.0 specification. The switching time between the two output voltage modes is compliant with SD 3.0 specification. Depending on the signaling level at pin SEL, the regulator delivers 1.8 V (SEL = HIGH) or 2.9 V (SEL = LOW,  $V_{SD_REF} < 1 V$ ). For card supply voltage, see <u>Section 8.4</u>.

| Table 0.           | SD card Sit   | ie voltage i     | ever control signal truth table |                                             |

|--------------------|---------------|------------------|---------------------------------|---------------------------------------------|

| Input              |               | Output           |                                 |                                             |

| SEL <sup>[1]</sup> | $V_{SD\_REF}$ | V <sub>LDO</sub> | Pin <sup>[2]</sup>              | Function                                    |

| Н                  | irrelevant    | 1.8 V            | DATA0_SD to DATA3_SD, CLK_SD    | low supply voltage level (1.8 $V_{typ}$ )   |

| L                  | < 1 V         | 2.9 V            | DATA0_SD to DATA3_SD, CLK_SD    | high supply voltage level (2.9 $V_{typ}$ )  |

|                    | > 1.5 V       | $V_{SD REF}$     | DATA0_SD to DATA3_SD, CLK_SD    | supply voltage level based on $V_{SD\ REF}$ |

#### Table 6. SD card side voltage level control signal truth table

$[1] \quad H=HIGH \ and \ L=LOW.$

[2] Host-side pins are not influenced by SEL.

#### 8.4 Memory card voltage tracking (reference select)

The device can track the memory card supply via pin  $V_{SD\_REF}$ . This allows achieving optimum interoperability by perfectly matching input/output levels between voltage translator and memory card in the 3 V signaling mode. Therefore, the voltage regulator aims to follow the reference voltage provided at input  $V_{SD\_REF}$  directly. If tracking of the memory card supply is not desired, connect pin  $V_{SD\_REF}$  to ground so the voltage regulator refers to an integrated voltage reference. For 1.8 V (SEL = HIGH) signaling, the voltage regulator is referred to the internal reference which is independent of the voltage at  $V_{SD\_REF}$ .

#### 8.5 Feedback clock channel

The clock is transmitted from the host to the memory card side. The voltage translator and the Printed-Circuit Board (PCB) tracks introduce some amount of delay. It reduces timing margin for data read back from memory card, especially at higher data rates. Therefore, a feedback path is provided to compensate the delay. The reasoning behind this approach is the fact that the clock is always delivered by the host, while the data in the timing critical read mode comes from the card.

#### 8.6 EMI filter

All input/output driver stages are equipped with EMI filters to reduce interferences towards sensitive mobile communication.

#### 8.7 ESD protection

The device has robust ESD protections on all memory card pins as well as on the  $V_{SD\_REF}$  and  $V_{SUPPLY}$  pins. The architecture prevents any stress for the host: the voltage translator discharges any stress to supply ground.

Pins Write Protect (WP) and Card Detection (CD) might be pulled down by the memory card which has to be detected by the host. Both signals must be HIGH if no card is inserted. Therefore the pins are equipped with International Electrotechnical Commission (IEC) system-level ESD protections and pull-up resistors connected to the host supply  $V_{CCA}$ .

IP4855CX25

7 of 30

#### **Limiting values** 9.

#### **Limiting values** Table 7.

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                          | Conditions                                                                                      | Min              | Max   | Unit |

|---------------------|------------------------------------|-------------------------------------------------------------------------------------------------|------------------|-------|------|

| V <sub>CC</sub>     | supply voltage                     | 4 ms transient                                                                                  |                  |       |      |

|                     |                                    | on pin V <sub>SUPPLY</sub>                                                                      | -0.5             | +6.0  | V    |

|                     |                                    | on pin V <sub>CCA</sub>                                                                         | -0.5             | +4.6  | V    |

| VI                  | input voltage                      | 4 ms transient at I/O pins                                                                      | -0.5             | +4.6  | V    |

| P <sub>tot</sub>    | total power dissipation            | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$                                              | -                | 1000  | mW   |

| T <sub>stg</sub>    | storage temperature                |                                                                                                 | -55              | +150  | °C   |

| T <sub>amb</sub>    | ambient temperature                |                                                                                                 | -40              | +85   | °C   |

| V <sub>ESD</sub>    | electrostatic discharge<br>voltage | IEC 61000-4-2, level 4, all memory card-side pins, $V_{SUPPLY},V_{SD\_REF},WP$ and CD to ground | <u>[1]</u> –8000 | +8000 | V    |

|                     |                                    | Human Body Model (HBM)<br>JEDEC JESD22-A114F; all pins                                          | -2000            | +2000 | V    |

|                     |                                    | Machine Model (MM) JEDEC JESD22-A115;<br>all pins                                               | -200             | +200  | V    |

| I <sub>lu(IO)</sub> | input/output latch-up current      | JESD 78B: -0.5 $V_{CC}$ < $V_{I}$ < 1.5 $V_{CC}$ ; $T_{j}$ < 125 °C                             | -100             | +100  | mA   |

[1] All system level tests are performed with the application-specific capacitors connected to the supply pins V<sub>SUPPLY</sub>, V<sub>LDO</sub> and V<sub>CCA</sub>.

## 10. Recommended operating conditions

| Table 8.         | Operating cond               | itions                                           |     |      |     |                    |      |

|------------------|------------------------------|--------------------------------------------------|-----|------|-----|--------------------|------|

| Symbol           | Parameter                    | Conditions                                       |     | Min  | Тур | Max                | Unit |

| V <sub>CC</sub>  | supply voltage               | on pin V <sub>SUPPLY</sub>                       | [1] | 2.5  | -   | 5.5                | V    |

|                  |                              | on pin V <sub>CCA</sub>                          |     | 1.1  | -   | 3.6                | V    |

| VI               | input voltage                | host side                                        | [2] | -0.3 | -   | $V_{CCA} + 0.3$    | V    |

|                  |                              | memory card side                                 |     | -0.3 | -   | $V_{O(reg)} + 0.3$ | V    |

| C <sub>ext</sub> | external capacitance         | recommended capacitor at pin $V_{\text{LDO}}$    |     | -    | 1.0 | -                  | μF   |

| ESR              | equivalent series resistance | at pin V <sub>LDO</sub>                          |     | 0    | -   | 50                 | mW   |

| C <sub>ext</sub> | external                     | recommended capacitor at pin $V_{\mbox{SUPPLY}}$ |     | -    | 0.1 | -                  | μF   |

|                  | capacitance                  | recommended capacitor at pin $V_{CCA}$           |     | -    | 0.1 | -                  | μF   |

[1] By minimum value the device is still fully functional, but the voltage on pin V<sub>LDO</sub> might drop below the recommended memory card supply voltage.

[2] The voltage must not exceed 3.6 V.

IP4855CX25 **Product data sheet**

SD 3.0-compliant memory card integrated dual voltage level translator

#### Table 9. Integrated resistors

$T_{amb} = 25 \ ^{\circ}C$ ; unless otherwise specified.

| Symbol          | Parameter            | Conditions                                  | Min            | Тур  | Max  | Unit |

|-----------------|----------------------|---------------------------------------------|----------------|------|------|------|

| R <sub>pd</sub> | pull-down resistance | R7; tolerance ±30 %                         | 329            | 470  | 611  | kΩ   |

|                 |                      | R30; tolerance ±30 %                        | 70             | 100  | 130  | Ω    |

|                 |                      | R38; tolerance ±30 %                        | 200            | 350  | 500  | kΩ   |

|                 |                      | R20, R21; tolerance ±30 %                   | 200            | 350  | 500  | kΩ   |

| R <sub>pu</sub> | pull-up resistance   | R10; tolerance ±30 %                        | 10.5           | 5 15 | 19.5 | kΩ   |

|                 |                      | R11 to R13; tolerance ±30 %                 | 49             | 70   | 91   | kΩ   |

|                 |                      | R14 and R15; tolerance $\pm 30$ %           | 70             | 100  | 130  | kΩ   |

| Rs              | series resistance    | card side; R1 to R6; tolerance $\pm 20~\%$  | [1] 32         | 40   | 48   | Ω    |

|                 |                      | host side; R31 to R37; tolerance $\pm 20$ % | [ <u>1]</u> 26 | 33   | 40   | Ω    |

[1] Guaranteed by design and characterization.

### **11. Static characteristics**

#### Table 10. Static characteristics

At recommended operating conditions;  $T_{amb} = -40$  °C to +85 °C; voltages are referenced to GND (ground = 0 V);  $C_{ext} = 1 \ \mu F$  at pin  $V_{LDO}$ ; unless otherwise specified.

| Symbol              | Parameter                    | Conditions                                                                                                         | Min                           | Typ <mark>[1]</mark> | Max                           | Unit |

|---------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|-------------------------------|------|

| Supply              | voltage regulator for ca     | ard-side I/O pin: V <sub>LDO</sub>                                                                                 |                               |                      |                               |      |

| V <sub>O(reg)</sub> | regulator output             | SEL = LOW; V <sub>SD_REF</sub> < 1 V; V <sub>SUPPLY</sub> $\ge$ 2.9 V                                              | 2.75                          | 2.9                  | 3.0                           | V    |

|                     | voltage                      | $\begin{array}{l} \text{SEL = LOW; V_{SD\_REF} > 1.5 V;} \\ \text{V}_{SUPPLY} \geq \text{V}_{SD\_REF} \end{array}$ | V <sub>SD_REF</sub><br>- 0.15 | $V_{SD\_REF}$        | V <sub>SD_REF</sub><br>+ 0.05 | V    |

|                     |                              | SEL = HIGH; $V_{SUPPLY} \ge 2.5 V$                                                                                 | 1.7                           | 1.8                  | 1.95                          | V    |

| $V_{do(reg)}$       | regulator dropout<br>voltage | SEL = LOW; V <sub>SUPPLY</sub> $\leq$ 2.9 V; I <sub>O</sub> = 50 mA                                                | -                             | -                    | 150                           | mV   |

| Host-sid            | le input signals: CMD_       | H and DATA0_H to DATA3_H, CLK_IN                                                                                   |                               |                      |                               |      |

| V <sub>IH</sub>     | HIGH-level input voltage     |                                                                                                                    | $0.625 \times V_{CCA}$        | -                    | V <sub>CCA</sub> + 0.3        | V    |

| V <sub>IL</sub>     | LOW-level input voltage      |                                                                                                                    | -0.3                          | -                    | $0.25 \times V_{CCA}$         | V    |

| ILI                 | input leakage current        | V <sub>CCA</sub> = 1.8 V; ENABLE = LOW                                                                             | -                             | -                    | 1.0                           | nA   |

| Host-sid            | le control signals           |                                                                                                                    |                               |                      |                               |      |

| SEL, EN             | ABLE                         |                                                                                                                    |                               |                      |                               |      |

| V <sub>IH</sub>     | HIGH-level input voltage     |                                                                                                                    | 0.75                          | -                    | V <sub>CCA</sub> + 0.3        | V    |

| V <sub>IL</sub>     | LOW-level input voltage      |                                                                                                                    | -0.3                          | -                    | 0.15                          | V    |

| DIR_0, [            | DIR_1_3, DIR_CMD             |                                                                                                                    |                               |                      |                               |      |

| V <sub>IH</sub>     | HIGH-level input<br>voltage  |                                                                                                                    | $0.65 \times V_{CCA}$         | -                    | V <sub>CCA</sub> + 0.3        | V    |

| V <sub>IL</sub>     | LOW-level input voltage      |                                                                                                                    | -0.3                          | -                    | $0.35 \times V_{CCA}$         | V    |

#### Table 10. Static characteristics ...continued

At recommended operating conditions;  $T_{amb} = -40$  °C to +85 °C; voltages are referenced to GND (ground = 0 V);  $C_{ext} = 1 \ \mu F$  at pin  $V_{LDO}$ ; unless otherwise specified.

| -                   | Parameter                       | Conditions                                                                                                                                                                                  | Min                                                       | Typ[1] | Max                       | Unit |

|---------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------|---------------------------|------|

| V <sub>SD_REF</sub> |                                 |                                                                                                                                                                                             |                                                           |        |                           |      |

| V <sub>IH</sub>     | HIGH-level input voltage        |                                                                                                                                                                                             | 1.5                                                       | -      | 3.63                      | V    |

| VIL                 | LOW-level input voltage         |                                                                                                                                                                                             | -0.3                                                      | -      | 1.0                       | V    |

| Host-sid            | le output signals: CLK          | FB, CMD_H and DATA0_H to DATA3_H                                                                                                                                                            |                                                           |        |                           |      |

| V <sub>OH</sub>     | HIGH-level output<br>voltage    | $I_{O}$ = 2 mA; $V_{I}$ = $V_{IH}$ (card side)                                                                                                                                              | $0.75 	imes V_{CCA}$                                      |        | -                         | V    |

| V <sub>OL</sub>     | LOW-level output voltage        | $I_{O}$ = $-2$ mA; $V_{I}$ = $V_{IL}$ (card side)                                                                                                                                           | -                                                         | -      | $0.125 \times V_{CCA}$    | V    |

| Card-sid            | le input signals: CMD           | SD and DATA0_SD to DATA3_SD                                                                                                                                                                 |                                                           |        |                           |      |

| V <sub>IH</sub>     | HIGH-level input voltage        | SEL = LOW (2.9 V interface)                                                                                                                                                                 | $0.625 \times V_{O(reg)}$                                 | -      | V <sub>O(reg)</sub> + 0.3 | V    |

|                     |                                 | SEL = HIGH (1.8 V interface)                                                                                                                                                                | $\begin{array}{c} 0.625 \times \\ V_{O(reg)} \end{array}$ | -      | V <sub>O(reg)</sub> + 0.3 | V    |

| V <sub>IL</sub>     | LOW-level input voltage         | SEL = LOW (2.9 V interface)                                                                                                                                                                 | -0.3                                                      | -      | $0.25 \times V_{O(reg)}$  | V    |

|                     |                                 | SEL = HIGH (1.8 V interface)                                                                                                                                                                | -0.3                                                      | -      | $0.25 	imes V_{O(reg)}$   | V    |

| Card-sic            | le output signal                |                                                                                                                                                                                             |                                                           |        |                           |      |

| CMD_SE              | D and DATA0_SD to DA            | TA3_SD, CLK_SD                                                                                                                                                                              |                                                           |        |                           |      |

| V <sub>OH</sub>     | HIGH-level output voltage       | $I_O = -4 \text{ mA}; V_I = V_{IH} \text{ (host side)}; \text{SEL} = LOW $ (2.9 V interface)                                                                                                | $0.75 \times V_{O(reg)}$                                  | -      | V <sub>O(reg)</sub> + 0.3 | V    |

|                     |                                 | $I_O = -2 \text{ mA}; V_I = V_{IH} \text{ (host side)}; \text{SEL} = \text{HIGH} $ (1.8 V interface)                                                                                        | $0.75 \times V_{O(reg)}$                                  | -      | V <sub>O(reg)</sub> + 0.3 | V    |

| V <sub>OL</sub>     | LOW-level output voltage        | $I_O = 4 \text{ mA}; V_I = V_{IL} \text{ (host side)}; \text{SEL} = LOW (2.9 V interface)$                                                                                                  | -0.3                                                      | -      | $0.125 \times V_{O(reg)}$ | V    |

|                     |                                 | $I_O = 2 \text{ mA}; V_I = V_{IL} \text{ (host side)}; \text{SEL} = \text{HIGH}$<br>(1.8 V interface)                                                                                       | -0.3                                                      | -      | $0.125 \times V_{O(reg)}$ | V    |

| I <sub>O(sc)</sub>  | short-circuit output<br>current | card-side pins connected to ground;<br>host-side input signals = HIGH;<br>$V_{SD_REF} = 3.6 V$ ; $V_{SUPPLY} = 5.5 V$ ;<br>$V_{CCA} = 3.6 V$ ; SEL = LOW;<br>DIR_1_3, DIR_CMD, DIR_0 = HIGH | -                                                         | -      | 100                       | mA   |

| Bus sign            | al equivalent capacitand        | ce                                                                                                                                                                                          |                                                           |        |                           |      |

| C <sub>ch</sub>     | channel capacitance             | $\label{eq:VI} \begin{array}{l} V_{I} = 0 \; V; \; f_{i} = 1 \; MHz; \; V_{SUPPLY} = 3.5 \; V; \\ V_{CCA} = 1.8 \; V \end{array}$                                                           | [2]                                                       |        |                           |      |

|                     |                                 | host side                                                                                                                                                                                   | -                                                         | 3.5    | 5                         | pF   |

|                     |                                 | card side                                                                                                                                                                                   | -                                                         | 5      | 10                        | pF   |

#### Table 10. Static characteristics ...continued

At recommended operating conditions;  $T_{amb} = -40$  °C to +85 °C; voltages are referenced to GND (ground = 0 V);  $C_{ext} = 1 \ \mu F$  at pin  $V_{LDO}$ ; unless otherwise specified.

| Symbol                | Parameter                 | Conditions                                                   | Min | Typ <mark>[1]</mark> | Max | Unit |

|-----------------------|---------------------------|--------------------------------------------------------------|-----|----------------------|-----|------|

| Current               | consumption               |                                                              |     |                      |     |      |

| I <sub>CC(stat)</sub> | static supply current     | ENABLE = HIGH (active mode);<br>all inputs = HIGH; DIR = LOW |     |                      |     |      |

|                       |                           | SEL = LOW (2.9 V interface)                                  | -   | -                    | 100 | μA   |

|                       |                           | SEL = HIGH (1.8 V interface)                                 | -   | -                    | 100 | μA   |

| I <sub>CC(stb)</sub>  | standby supply<br>current | ENABLE = LOW (inactive mode)                                 | -   | -                    | 1   | μA   |

[1] Typical values are measured at  $T_{amb} = 25 \ ^{\circ}C$ .

[2] EMI filter line capacitance per data channel from I/O driver to pin; C<sub>ch</sub> is guaranteed by design.

### **12. Dynamic characteristics**

#### 12.1 Voltage regulator

#### Table 11. Voltage regulator

$T_{amb} = 25 \ ^{\circ}C$ ; unless otherwise specified.

| Symbol                    | Parameter                           | Conditions                                                                             | Min | Тур | Мах | Unit |

|---------------------------|-------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|------|

| Voltage reg               | ulator output pin: V <sub>LDO</sub> |                                                                                        |     |     |     |      |

| t <sub>startup(reg)</sub> | regulator start-up time             | $V_{CCA}$ = 1.8 V; $V_{SUPPLY}$ = 3.5 V;<br>$C_{ext}$ = 1 $\mu$ F; see <u>Figure 5</u> | -   | -   | 100 | μS   |

| t <sub>f(0)</sub>         | output fall time                    | V <sub>O(reg)</sub> = 2.9 V to 1.8 V;<br>SEL = LOW to HIGH; see <u>Figure 4</u>        | -   | -   | 1   | ms   |

| t <sub>r(o)</sub>         | output rise time                    | V <sub>O(reg)</sub> = 1.8 V to 2.9 V;<br>SEL = HIGH to LOW; see <u>Figure 4</u>        | -   | -   | 100 | μS   |

#### **NXP Semiconductors**

## IP4855CX25

#### SD 3.0-compliant memory card integrated dual voltage level translator

IP4855CX25

12 of 30

#### 12.2 ESD characteristic of pin write protect and card detect

#### Table 12. ESD characteristic of write protect and card detect

At recommended operating conditions;  $T_{amb} = +25 \ ^{\circ}C$ ; voltages are referenced to GND (ground = 0 V); unless otherwise specified

| Symbol           | Parameter             | Conditions         | Min          | Тур | Max | Unit |

|------------------|-----------------------|--------------------|--------------|-----|-----|------|

| ESD prot         | ection pins: WP and C | D                  |              |     |     |      |

| $V_{BR}$         | breakdown voltage     | TLP; I = 1 mA      | -            | 8   | -   | V    |

| r <sub>dyn</sub> | dynamic resistance    | positive transient | <u>[1]</u> - | 0.5 | -   | Ω    |

|                  |                       | negative transient | [1] -        | 0.5 | -   | Ω    |

[1] TLP according to ANSI-ESD STM5.5.1/IEC 62615  $Z_0 = 50 \Omega$ ; pulse width = 100 ns; rise time = 200 ps; averaging window = 50 ns to 80 ns

### **13. Application information**

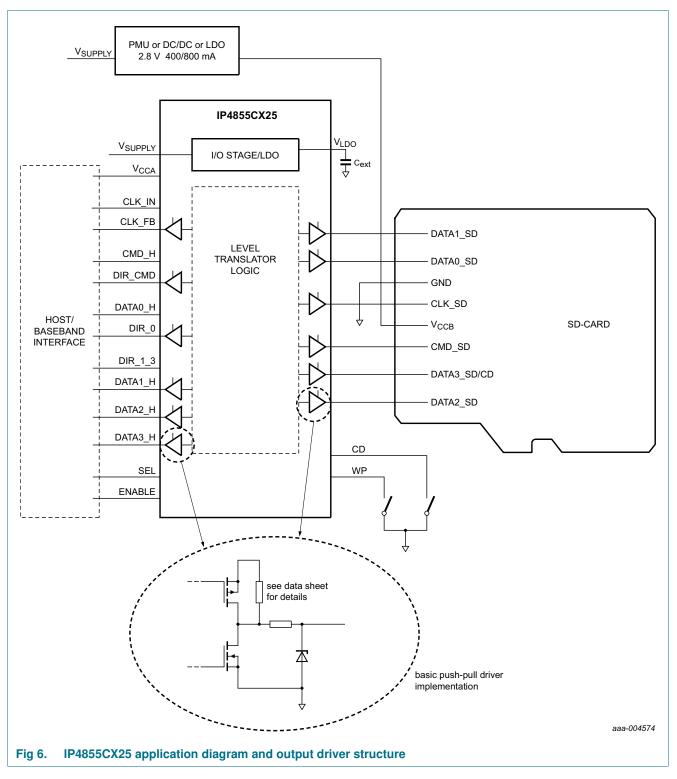

The IP4855CX25 is optimized to connect SD 3.0 and SD 2.0 compatible memory cards to 1.8 V base band/host interfaces. While the internal I/O interface towards the memory card is supplied by the IP4855CX25 integrated voltage regulator, any connected memory card has to be supplied from an external source. Using for example DDR50 or SDR50 modes requires a power supply with up to 400 mA DC current capabilities.

Place IP4855CX25 as close as possible to the card holder to minimize the influence of trace length on the timing values. The trace length between IP4855CX25 and the card has a much bigger influence on the timing than the identical length between the host interface and the IP4855CX25.

IP4855CX25

13 of 30

#### **NXP Semiconductors**

## IP4855CX25

SD 3.0-compliant memory card integrated dual voltage level translator

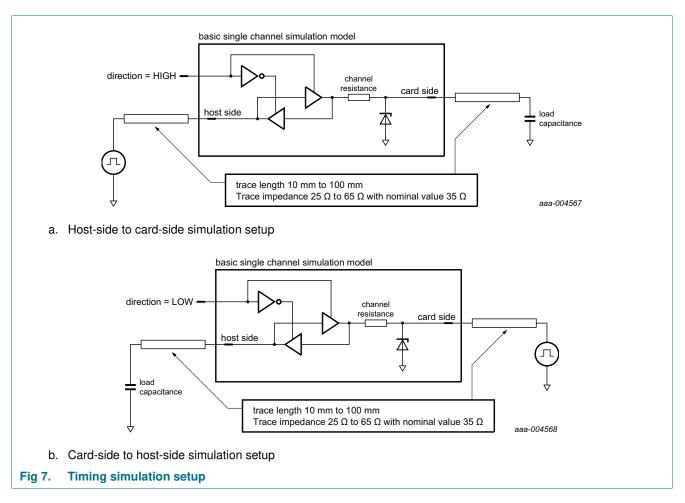

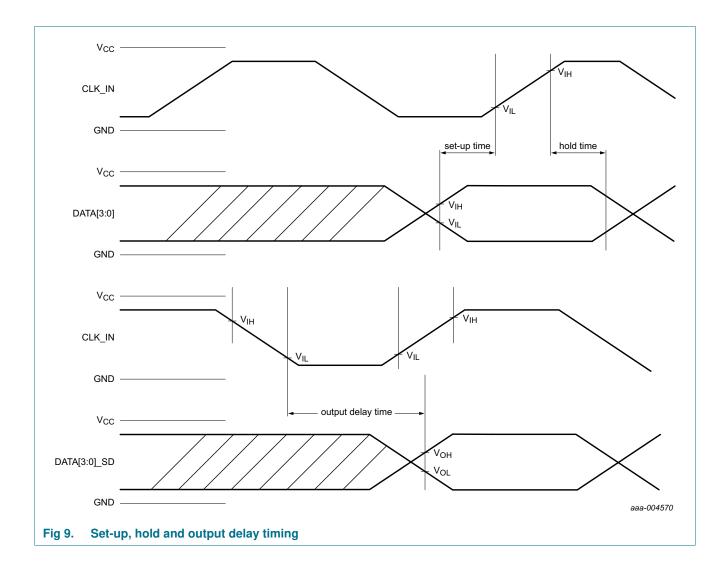

One main task of the level translator is to shift the signal within the SD 3.0 specification. Therefore, the following simulation results show the low impact of the device. Use the clock feedback channel for a compensation of delay introduced by PCB traces and IP4855CX25.

Product data sheet

## 13.1 Simulation setup for transition time, propagation delay and set-up/hold times

### **NXP Semiconductors**

## IP4855CX25

#### SD 3.0-compliant memory card integrated dual voltage level translator

IP4855CX25

16 of 30

#### **NXP Semiconductors**

#### SD 3.0-compliant memory card integrated dual voltage level translator

### 13.2 Interface voltage timing data

#### Table 13. Output rise and fall times card side

$V_{SUPPLY} = 4 V$ ; unless otherwise specified; track impedance 35  $\Omega$ , track length (to and from IP4855CX25) 15 mm;  $R_{source} = 50 \Omega$ ; see <u>Figure 7</u> for set-up circuit and <u>Figure 8</u> for timing diagram;  $V_{CCA} = 1.8 V$ ; transition time is the same as output rise time and output fall time

| Symbol                                       | Parameter                                                         | Conditions                                                                                                                                                                    | Min.          | Тур        | Мах        | Unit     |  |

|----------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|------------|----------|--|

| Memory                                       | card-side output pir                                              | ns: CLK_SD, CMD_SD and DATA0_SD to DATA3_                                                                                                                                     | _SD; 2.9 V mo | ode (SEL   | = LOW)     |          |  |

| Referenc                                     | e points at 20 % and                                              | 70 %                                                                                                                                                                          |               |            |            |          |  |

| t <sub>t</sub>                               | transition time                                                   | C <sub>L</sub> = 10 pF                                                                                                                                                        |               |            |            |          |  |

|                                              |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 2.9 V                                                                                                                           | 0.8           | 1.1        | 1.3        | ns       |  |

|                                              |                                                                   | best case; $T_{amb} = -40 ^{\circ}\text{C}$ ; $V_{LDO} = 3.6 \text{ V}$                                                                                                       | 0.8           | 1.0        | 1.2        | ns       |  |

|                                              |                                                                   | worst case; $T_{amb}$ = +85 °C; $V_{LDO}$ = 2.7 V                                                                                                                             | 0.8           | 1.1        | 1.3        | ns       |  |

|                                              |                                                                   | C <sub>L</sub> = 20 pF                                                                                                                                                        | [1]           |            |            |          |  |

|                                              |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 2.9 V                                                                                                                           | 1.4           | 1.6        | 1.9        | ns       |  |

|                                              |                                                                   | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 3.6 \text{ V}$                                                                                                             | 1.3           | 1.6        | 1.8        | ns       |  |

|                                              |                                                                   | worst case; $T_{amb}$ = +85 °C; $V_{LDO}$ = 2.7 V                                                                                                                             | 1.4           | 1.6        | 1.9        | ns       |  |

| Referenc                                     | e points at 10 % and                                              | 90 % [2]                                                                                                                                                                      |               |            |            |          |  |

| t                                            | transition time                                                   | C <sub>L</sub> = 10 pF                                                                                                                                                        |               |            |            |          |  |

|                                              |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 2.9 V                                                                                                                           | 1.9           | 2.1        | 2.4        | ns       |  |

|                                              |                                                                   | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 3.6 \text{ V}$                                                                                                             | 1.9           | 2.0        | 2.2        | ns       |  |

|                                              |                                                                   | worst case; $T_{amb}$ = +85 °C; $V_{LDO}$ = 2.7 V                                                                                                                             | 2.0           | 2.2        | 2.4        | ns       |  |

|                                              |                                                                   | C <sub>L</sub> = 20 pF                                                                                                                                                        | [1]           |            |            |          |  |

|                                              |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 2.9 V                                                                                                                           | 2.9           | 3.1        | 3.4        | ns       |  |

|                                              | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 3.6 \text{ V}$ | 2.9                                                                                                                                                                           | 3.0           | 3.2        | ns         |          |  |

|                                              |                                                                   | worst case; $T_{amb}$ = +85 °C; $V_{LDO}$ = 2.7 V                                                                                                                             | 2.9           | 3.2        | 3.5        | ns       |  |

| Memory                                       | card-side output pir                                              | ns: CLK_SD, CMD_SD and DATA0_SD to DATA3_                                                                                                                                     | SD; 1.8 V mo  | ode (SEL   | = HIGH)    |          |  |

| Referenc                                     | e points at 20 % and                                              | 70 %                                                                                                                                                                          |               |            |            |          |  |

| t                                            | transition time                                                   | C <sub>L</sub> = 10 pF                                                                                                                                                        |               |            |            |          |  |

|                                              |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 1.8 V                                                                                                                           | 0.8           | 1.1        | 1.3        | ns       |  |

|                                              |                                                                   | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 1.95 \text{ V}$                                                                                                            | 0.8           | 1.0        | 1.2        | ns       |  |

|                                              |                                                                   | worst case; $T_{amb}$ = +85 °C; $V_{LDO}$ = 1.7 V                                                                                                                             | 0.8           | 1.1        | 1.3        | ns       |  |

|                                              | transition time                                                   | transition time $C_L = 20 \text{ pF}$ [1]                                                                                                                                     |               |            |            |          |  |

| t <sub>t</sub>                               |                                                                   |                                                                                                                                                                               |               |            |            |          |  |

| ł                                            |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 1.8 V                                                                                                                           | 1.4           | 1.6        | 1.9        | ns       |  |

| t                                            |                                                                   | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 1.8 V<br>best case; $T_{amb}$ = -40 °C; $V_{LDO}$ = 1.95 V                                                                      | 1.4<br>1.3    | 1.6<br>1.6 | 1.9<br>1.8 | ns<br>ns |  |

| t <sub>t</sub>                               |                                                                   |                                                                                                                                                                               |               |            |            |          |  |

|                                              | e points at 10 % and                                              | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 1.95 \text{ V}$<br>worst case; $T_{amb} = +85 \text{ °C}$ ; $V_{LDO} = 1.7 \text{ V}$                                      | 1.3           | 1.6        | 1.8        | ns       |  |

| Referenc                                     |                                                                   | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 1.95 \text{ V}$<br>worst case; $T_{amb} = +85 \text{ °C}$ ; $V_{LDO} = 1.7 \text{ V}$                                      | 1.3           | 1.6        | 1.8        | ns       |  |

| t <sub>t</sub><br>Referenc<br>t <sub>t</sub> | e points at 10 % and                                              | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 1.95 \text{ V}$<br>worst case; $T_{amb} = +85 \text{ °C}$ ; $V_{LDO} = 1.7 \text{ V}$<br>90 % [2]                          | 1.3           | 1.6        | 1.8        | ns       |  |

| Referenc                                     | e points at 10 % and                                              | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 1.95 \text{ V}$<br>worst case; $T_{amb} = +85 \text{ °C}$ ; $V_{LDO} = 1.7 \text{ V}$<br>90 % [2]<br>$C_L = 10 \text{ pF}$ | 1.3<br>1.4    | 1.6<br>1.6 | 1.8<br>1.9 | ns<br>ns |  |

#### Table 13. Output rise and fall times card side ...continued

$V_{SUPPLY} = 4 V$ ; unless otherwise specified; track impedance 35  $\Omega$ , track length (to and from IP4855CX25) 15 mm;  $R_{source} = 50 \Omega$ ; see Figure 7 for set-up circuit and Figure 8 for timing diagram;  $V_{CCA} = 1.8 V$ ; transition time is the same as output rise time and output fall time

| Symbol | Parameter       | Conditions                                                         | Min. | Тур | Max | Unit |

|--------|-----------------|--------------------------------------------------------------------|------|-----|-----|------|

| tt     | transition time | C <sub>L</sub> = 20 pF                                             | [1]  |     |     |      |

|        |                 | nominal case; $T_{amb}$ = +25 °C; $V_{LDO}$ = 1.8 V                | 2.9  | 3.1 | 3.4 | ns   |

|        |                 | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{LDO} = 1.95 \text{ V}$ | 2.9  | 3.0 | 3.2 | ns   |

|        |                 | worst case; $T_{amb}$ = +85 °C; $V_{LDO}$ = 1.7 V                  | 2.9  | 3.2 | 3.5 | ns   |

[1] A capacitive load of  $C_L = 20 \text{ pF}$  is out of the range of allowed SD-card interface parasitic capacitance.

[2] Reference points 90 % and 10 % are not required according to the SD 3.0 specification.

#### Table 14. Output rise and fall times host side

$V_{SUPPLY} = 4.0 V$ ; SEL = LOW;  $V_{O(reg)} = 2.9 V$ ; unless otherwise specified; track impedance 35  $\Omega$ , track length (to and from IP4855CX25) 15 mm;  $R_{source} = 50 \Omega$ ; see <u>Figure 7</u> for set-up circuit and <u>Figure 8</u> timing diagram; transition time is the same as output rise time and output fall time

| Symbol         | Parameter              | Conditions                                                                                                                                | Min        | Тур        | Max        | Unit     |

|----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|----------|

| Host-sid       | e output pins: CLK_F   | B, CMD_H and DATA0_H to DATA3_H (3.3 V host)                                                                                              |            |            |            |          |

| Referenc       | e points at 20 % and 7 | 0 %                                                                                                                                       |            |            |            |          |

| tt             | transition time        | $C_L = 5 \text{ pF}$                                                                                                                      |            |            |            |          |

|                |                        | nominal case; $T_{amb}$ = +25 °C; $V_{CCA}$ = 3.3 V                                                                                       | 0.5        | 0.6        | 0.7        | ns       |

|                |                        | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{CCA} = 3.6 \text{ V}$                                                                         | 0.5        | 0.6        | 0.7        | ns       |

|                |                        | worst case; $T_{amb}$ = +85 °C; $V_{CCA}$ = 2.7 V                                                                                         | 0.5        | 0.6        | 0.7        | ns       |

| Referenc       | e points at 10 % and 9 | 0 % [1]                                                                                                                                   |            |            |            |          |

| t <sub>t</sub> | transition time        | $C_L = 5 \text{ pF}$                                                                                                                      |            |            |            |          |

|                |                        | nominal case; $T_{amb}$ = +25 °C; $V_{CCA}$ = 3.3 V                                                                                       | 1.0        | 1.3        | 1.5        | ns       |

|                |                        | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{CCA} = 3.6 \text{ V}$                                                                         | 1.0        | 1.2        | 1.4        | ns       |

|                |                        | worst case; $T_{amb}$ = +85 °C; $V_{CCA}$ = 2.7 V                                                                                         | 1.3        | 1.4        | 1.6        | ns       |

| Host-sid       | e output pins: CLK_F   | B, CMD_H and DATA0_H to DATA3_H (1.8 V host)                                                                                              |            |            |            |          |

| Referenc       | e points at 20 % and 7 | 0 %                                                                                                                                       |            |            |            |          |

| t <sub>t</sub> | transition time        | $C_L = 5 \text{ pF}$                                                                                                                      |            |            |            |          |

|                |                        | nominal case; $T_{amb}$ = +25 °C; $V_{CCA}$ = 1.8 V                                                                                       | 0.5        | 0.6        | 0.7        | ns       |

|                |                        | best case; $T_{amb} = -40 \text{ °C}$ ; $V_{CCA} = 1.9 \text{ V}$                                                                         | 0.5        | 0.6        | 0.7        | ns       |

|                |                        | worst case; $T_{amb}$ = +85 °C; $V_{CCA}$ = 1.62 V                                                                                        | 0.5        | 0.6        | 0.7        | ns       |

| Referenc       | e points at 10 % and 9 | 0 % [1]                                                                                                                                   |            |            |            |          |

|                | transition time        | C <sub>L</sub> = 5 pF                                                                                                                     |            |            |            |          |

| t <sub>t</sub> |                        |                                                                                                                                           |            |            |            |          |

| tt             |                        | nominal case; T <sub>amb</sub> = +25 °C; V <sub>CCA</sub> = 1.8 V                                                                         | 1.0        | 1.3        | 1.5        | ns       |

| tt             |                        | nominal case; $T_{amb} = +25 \text{ °C}$ ; $V_{CCA} = 1.8 \text{ V}$<br>best case; $T_{amb} = -40 \text{ °C}$ ; $V_{CCA} = 1.9 \text{ V}$ | 1.0<br>1.0 | 1.3<br>1.2 | 1.5<br>1.4 | ns<br>ns |

[1] Reference points 90 % and 10 % are not required according to the SD 3.0 specification.

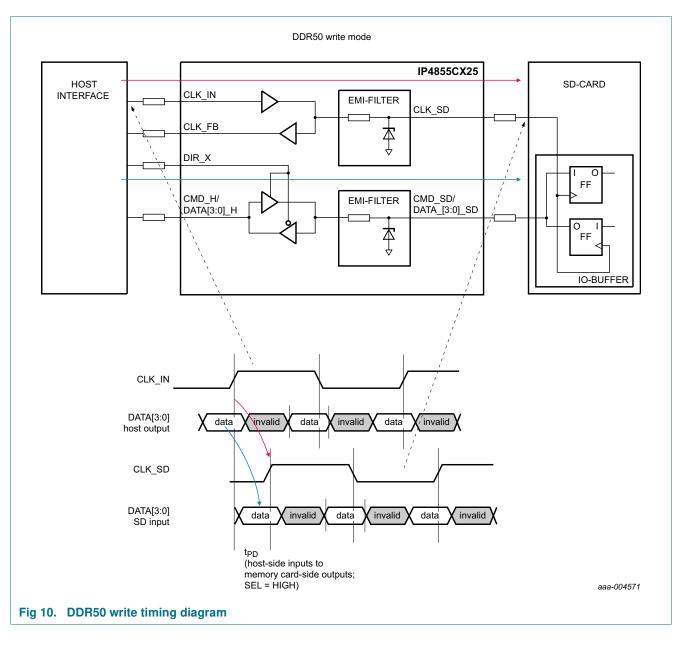

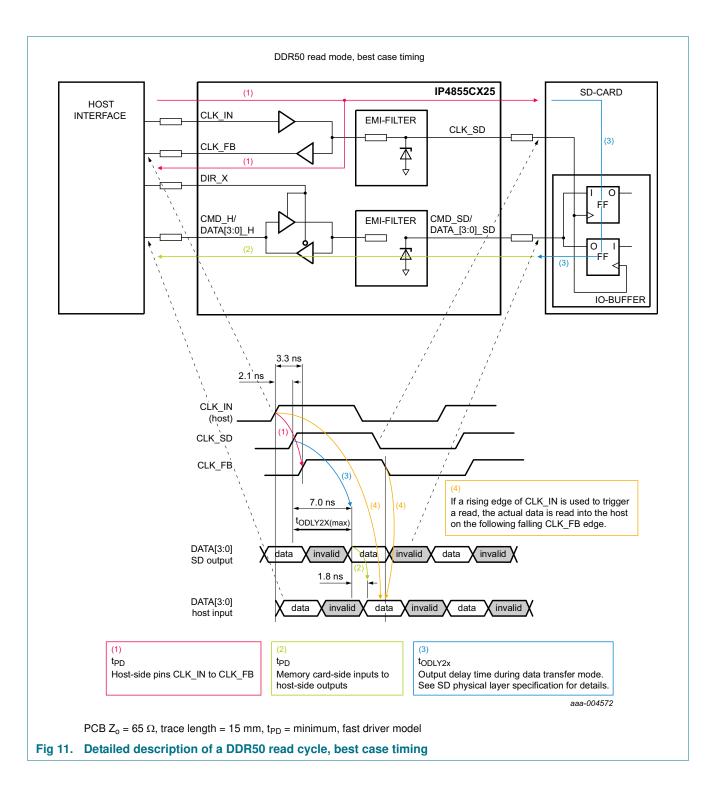

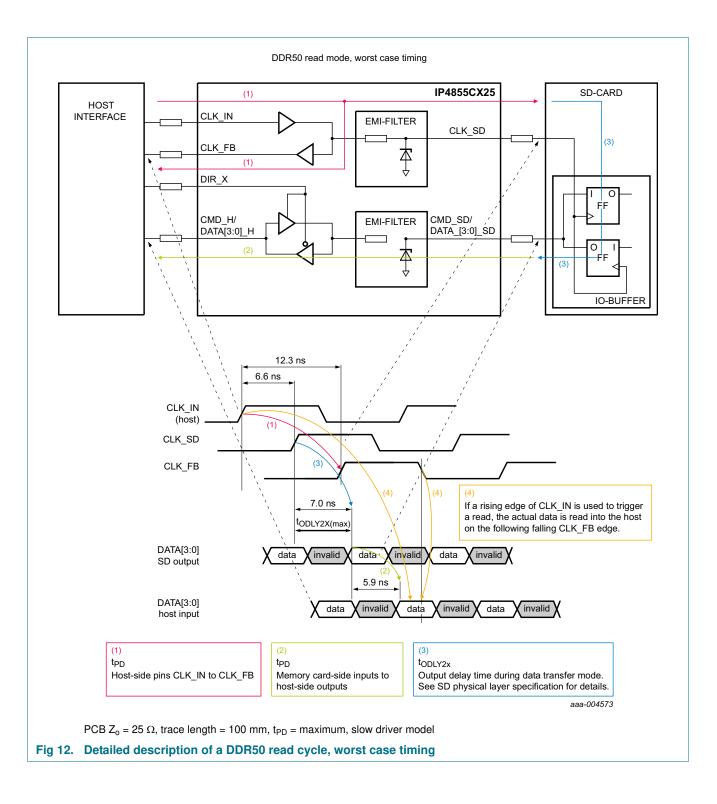

#### 13.3 DDR50 mode timing details

The Default-Speed (DS) and High-Speed (HS) modes use 3.3 V signaling and offer a maximum of 25 MB/s. Besides these modes, IP4855CX25 also supports the SDR12, SDR25 and DDR50 modes using 1.8 V signaling and up to 50 MB/s.

Especially the DDR50 mode introduces a basic change in the timing behavior of the SD card interface. The SDR12 and SDR50 modes are similar to the DS and HS modes.

Any delay on all relevant signal lines (as shown in the timing diagram in <u>Figure 10</u>) is uncritical for SD card write operations as long as the skew between the different signals is small enough.

In contrast to the write cycle, the read cycle is more complex to analyze and depends on the IP4855CX25 delay, the maximum delay added by the PCB and the additional setup time of the SD card.

| Table 15. | DDR50 read mode: | parameters for b | pest case and worst | case timings |

|-----------|------------------|------------------|---------------------|--------------|

|-----------|------------------|------------------|---------------------|--------------|

| Parameter                  | Best case timing (Figure 11) | Worst case timing (Figure 12) |

|----------------------------|------------------------------|-------------------------------|

| PCB output impedance $Z_o$ | 65 Ω                         | 25 Ω                          |

| Symmetrical trace length   | 15 mm per side               | 100 mm per side               |

| t <sub>PD</sub>            | minimum                      | maximum                       |

| Driver model               | fast                         | slow                          |

The same mechanism is triggered on each falling clock edge too, as the DDR50 mode uses both edges of the clock signal for data transfer.

According to the SD 3.01 physical layer specification, the maximum delay between CLK\_IN (CLK\_SD signal) at the SD card and data out from the SD card (DATA[3:0]\_SD out) is 7.0 ns. This value is specified for a load of  $C_L \le 25$  pF.

#### SD 3.0-compliant memory card integrated dual voltage level translator

#### SD 3.0-compliant memory card integrated dual voltage level translator

#### SD 3.0-compliant memory card integrated dual voltage level translator

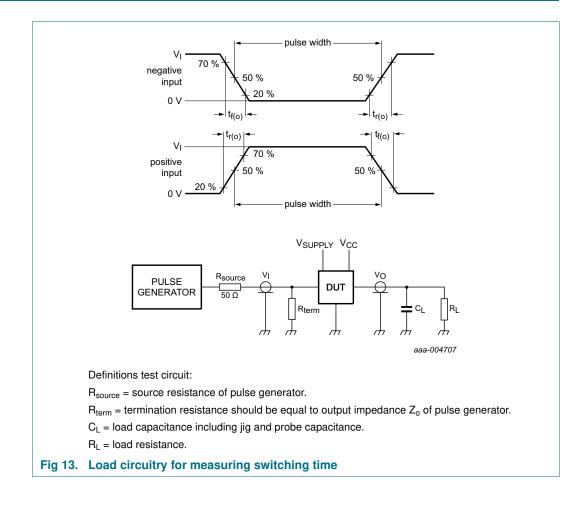

## 14. Test information

#### **NXP Semiconductors**

## IP4855CX25

SD 3.0-compliant memory card integrated dual voltage level translator

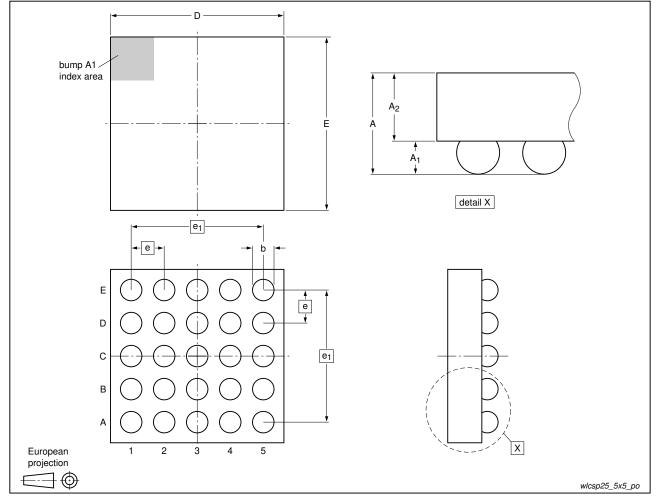

## 15. Package outline

WLCSP25: wafer level chip-size package; 25 bumps (5 x 5)

#### Fig 14. Package outline IP4855CX25 (WLCSP25)

| Table 16. | Dimensions | of IP4855CX25 | for Figure 14 |

|-----------|------------|---------------|---------------|

|-----------|------------|---------------|---------------|

| Symbol         | Min  | Тур  | Мах  | Unit |

|----------------|------|------|------|------|

| A              | 0.44 | 0.47 | 0.50 | mm   |

| A <sub>1</sub> | 0.18 | 0.20 | 0.22 | mm   |

| A <sub>2</sub> | 0.25 | 0.27 | 0.29 | mm   |

| b              | 0.21 | 0.26 | 0.31 | mm   |

| D              | 1.99 | 2.04 | 2.09 | mm   |

| E              | 1.99 | 2.04 | 2.09 | mm   |

| е              | -    | 0.4  | -    | mm   |

P4855CX25 Product data sheet

### 16. Design and assembly recommendations

#### 16.1 PCB design guidelines

For optimum performance, use a Non-Solder Mask PCB Design (NSMD), also known as a copper-defined design, incorporating laser-drilled micro-vias connecting the ground pads to a buried ground-plane layer. This results in the lowest possible ground inductance and provides the best high frequency and ESD performance. For this case, refer to <u>Table 17</u> for the recommended PCB design parameters.

#### Table 17. Recommended PCB design parameters

| Parameter                     | Value or Specification [1] |

|-------------------------------|----------------------------|

| PCB pad diameter              | 250 μm                     |

| Micro-via diameter            | 100 μm (0.004 inch)        |

| Solder mask aperture diameter | 325 μm                     |

| Copper thickness              | 20 μm to 40 μm             |

| Copper finish                 | AuNi or OSP                |

| PCB material                  | FR4                        |

[1] OSP: Organic Solderability Preservation FR4: Flame Retard 4

#### 16.2 PCB assembly guidelines for Pb-free soldering

#### Table 18. Assembly recommendations

| Parameter                       | Value or Specification                |

|---------------------------------|---------------------------------------|

| Solder screen aperture diameter | 290 μm                                |

| Solder screen thickness         | 100 μm (0.004 inch)                   |

| Solder paste: Pb-free           | SnAg (3 % to 4 %) Cu (0.5 % to 0.9 %) |

| Solder/flux ratio               | 50/50                                 |

| Solder reflow profile           | see Figure 15                         |