Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IR2308(S) & (PbF)

### HALF-BRIDGE DRIVER

#### **Features**

- Floating channel designed for bootstrap operation Fully operational to +600V Tolerant to negative transient voltage dV/dt immune

- Gate drive supply range from 10 to 20V

- Undervoltage lockout for both channels

- 3.3V, 5V and 15V input logic compatible

- Cross-conduction prevention logic

- Matched propagation delay for both channels

- Outputs in phase with inputs

- Logic and power ground +/- 5V offset.

- Internal 540ns dead-time

- Lower di/dt gate driver for better noise immunity

- Also available LEAD\_FREE

### **Description**

The IR2308(S) are high voltage, high speed power MOSFET and IGBT drivers with dependent high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is

### **Packages**

#### 2106//2108//2109/2304/2308 Feature Comparison

| Part  | Input<br>logic | Cross-<br>conduction<br>prevention<br>logic | Dead-Time                     | Ground Pins |  |

|-------|----------------|---------------------------------------------|-------------------------------|-------------|--|

| 2106  | HIN/LIN        | no                                          | none COM                      |             |  |

| 21064 | HIIN/LIIN      | 110                                         | none                          | VSS/COM     |  |

| 2108  | HIN/LIN        | yes                                         | Internal 540ns                | COM         |  |

| 21084 | TIIIN/LIIN     | yes                                         | Programmable 0.54~5 μs        | VSS/COM     |  |

| 2109  | IN/SD          | VOC                                         | Internal 540ns                | COM         |  |

| 21094 | IIV/SD         | yes                                         | yes Programmable 0.54~5 μs VS |             |  |

| 2304  | HIN/LIN        | yes                                         | Internal 100ns                | СОМ         |  |

| 2308  | HIN/LIN        | yes                                         | Internal 540ns                | COM         |  |

compatible with standard CMOS or LSTTL output, down to 3.3V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side configuration which operates up to 600 volts.

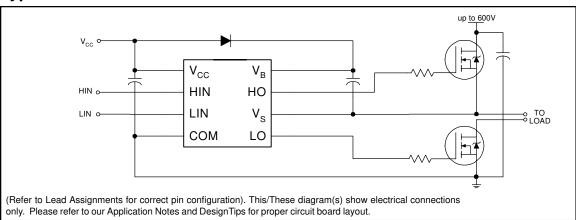

# **Typical Connection**

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                         |               | Min.                  | Max.                  | Units   |

|---------------------|----------------------------------------------------|---------------|-----------------------|-----------------------|---------|

| V <sub>B</sub>      | High side floating absolute voltage                |               | -0.3                  | 625                   |         |

| Vs                  | High side floating supply offset voltage           |               | V <sub>B</sub> - 25   | V <sub>B</sub> + 0.3  |         |

| V <sub>HO</sub>     | High side floating output voltage                  |               | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3  | v       |

| V <sub>CC</sub>     | Low side and logic fixed supply voltage            |               | -0.3                  | 25                    |         |

| V <sub>LO</sub>     | Low side output voltage                            |               | -0.3                  | V <sub>CC</sub> + 0.3 |         |

| V <sub>IN</sub>     | Logic input voltage (HIN & LIN )                   |               | V <sub>SS</sub> - 0.3 | V <sub>CC</sub> + 0.3 |         |

| dV <sub>S</sub> /dt | Allowable offset supply voltage transient          |               | _                     | 50                    | V/ns    |

| PD                  | Package power dissipation @ T <sub>A</sub> ≤ +25°C | (8 lead PDIP) | _                     | 1.0                   | 147     |

|                     |                                                    | (8 lead SOIC) | _                     | 0.625                 | W       |

| Rth <sub>JA</sub>   | Thermal resistance, junction to ambient            | (8 lead PDIP) | _                     | 125                   | °C/W    |

|                     | -                                                  | (8 lead SOIC) | _                     | 200                   | . 0, ** |

| TJ                  | Junction temperature                               |               | _                     | 150                   |         |

| T <sub>S</sub>      | Storage temperature                                |               | -50                   | 150                   | °C      |

| TL                  | Lead temperature (soldering, 10 seconds)           |               | _                     | 300                   |         |

# **Recommended Operating Conditions**

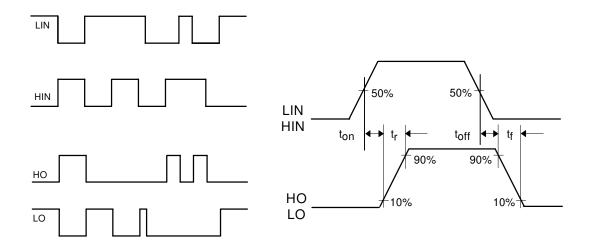

The Input/Output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions. The  $V_S$  and  $V_{SS}$  offset rating are tested with all supplies biased at 15V differential.

| Symbol          | Definition                                 | Min.                | Max.                | Units |

|-----------------|--------------------------------------------|---------------------|---------------------|-------|

| VB              | High side floating supply absolute voltage | V <sub>S</sub> + 10 | V <sub>S</sub> + 20 |       |

| Vs              | High side floating supply offset voltage   | Note 1              | 600                 |       |

| V <sub>HO</sub> | High side floating output voltage          | Vs                  | V <sub>B</sub>      | v     |

| V <sub>CC</sub> | Low side and logic fixed supply voltage    | 10                  | 20                  |       |

| V <sub>LO</sub> | Low side output voltage                    | 0                   | Vcc                 |       |

| V <sub>IN</sub> | Logic input voltage                        | COM                 | V <sub>CC</sub>     |       |

| T <sub>A</sub>  | Ambient temperature                        | -40                 | 125                 | °C    |

Note 1: Logic operational for  $V_S$  of -5 to +600V. Logic state held for  $V_S$  of -5V to -V<sub>BS</sub>. (Please refer to the Design Tin DT97-3 for more details).

## **Dynamic Electrical Characteristics**

$V_{BIAS}$  (V<sub>CC</sub>, V<sub>BS</sub>) = 15V, V<sub>SS</sub> = COM, C<sub>L</sub> = 1000 pF, T<sub>A</sub> = 25°C, DT = VSS unless otherwise specified.

| Symbol         | Definition                                     | Min. | Тур. | Max. | Units | <b>Test Conditions</b>      |

|----------------|------------------------------------------------|------|------|------|-------|-----------------------------|

| ton            | Turn-on propagation delay                      | _    | 220  | 300  |       | Vs = 0V                     |

| toff           | Turn-off propagation delay                     | _    | 200  | 280  |       | V <sub>S</sub> = 0V or 600V |

| MT             | Delay matching   ton - toff                    | _    | 0    | 46   |       |                             |

| t <sub>r</sub> | Turn-on rise time                              | _    | 150  | 220  |       | V <sub>S</sub> = 0V         |

| tf             | Turn-off fall time                             | _    | 50   | 80   | nsec  | V <sub>S</sub> = 0V         |

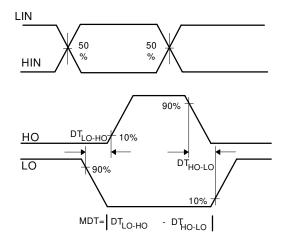

| DT             | Deadtime: LO turn-off to HO turn-on(DTLO-HO) & | 400  | 540  | 680  |       |                             |

|                | HO turn-off to LO turn-on (DTHO-LO)            |      |      |      |       |                             |

| MDT            | Deadtime matching = DTLO-HO - DTHO-LO          | _    | 0    | 60   |       |                             |

### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15V,  $V_{SS}$  = COM, DT=  $V_{SS}$  and  $V_{AB}$  and  $V_{AB}$  = 25°C unless otherwise specified. The  $V_{IL}$ ,  $V_{IH}$  and  $V_{IL}$  and  $V_{$

| Symbol              | Definition                                                             | Min. | Тур. | Max. | Units                   | <b>Test Conditions</b>                 |

|---------------------|------------------------------------------------------------------------|------|------|------|-------------------------|----------------------------------------|

| V <sub>IH</sub>     | Logic "1" input voltage for HIN & LIN                                  | 2.9  | _    | _    |                         | V <sub>CC</sub> = 10V to 20V           |

| V <sub>IL</sub>     | Logic "0" input voltage for HIN & LIN                                  | _    | _    | 0.8  | V                       | V <sub>CC</sub> = 10V to 20V           |

| V <sub>OH</sub>     | High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub>          | -    | 0.8  | 1.4  | ·                       | I <sub>O</sub> = 20 mA                 |

| V <sub>OL</sub>     | Low level output voltage, VO                                           | -    | 0.3  | 0.6  |                         | I <sub>O</sub> = 20 mA                 |

| I <sub>LK</sub>     | Offset supply leakage current                                          | _    | _    | 50   |                         | V <sub>B</sub> = V <sub>S</sub> = 600V |

| I <sub>QBS</sub>    | Quiescent V <sub>BS</sub> supply current                               | 20   | 60   | 150  | μΑ                      | V <sub>IN</sub> = 0V or 5V             |

| IQCC                | Quiescent V <sub>CC</sub> supply current                               | 0.4  | 1.0  | 1.6  | mA                      | V <sub>IN</sub> = 0V or 5V             |

| I <sub>IN+</sub>    | Logic "1" input bias current                                           | _    | 5    | 20   |                         | HIN = 5V, LIN = 5V                     |

| I <sub>IN-</sub>    | Logic "0" input bias current                                           | _    | 1    | 2    | <del>-</del> μ <b>A</b> | HIN = 0V, LIN = 0V                     |

| V <sub>CCUV+</sub>  | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage positive going | 8.0  | 8.9  | 10   |                         |                                        |

| V <sub>BSUV+</sub>  | threshold                                                              |      |      |      |                         |                                        |

| V <sub>CCUV</sub> - | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage negative going | 7.4  | 8.2  | 9.0  | V                       |                                        |

| V <sub>BSUV</sub> - | threshold                                                              |      |      |      |                         |                                        |

| V <sub>CCUVH</sub>  | Hysteresis                                                             | 0.3  | 0.7  | _    |                         |                                        |

| V <sub>BSUVH</sub>  |                                                                        |      |      |      |                         |                                        |

| I <sub>O+</sub>     | Output high short circuit pulsed current                               | 97   | 200  | _    |                         | $V_O = 0V$ ,                           |

|                     |                                                                        |      |      |      | mA                      | PW ≤ 10 μs                             |

| I <sub>O</sub> -    | Output low short circuit pulsed current                                | 250  | 350  | -    | 11174                   | $V_0 = 15V$ ,                          |

|                     |                                                                        |      |      |      |                         | PW ≤ 10 μs                             |

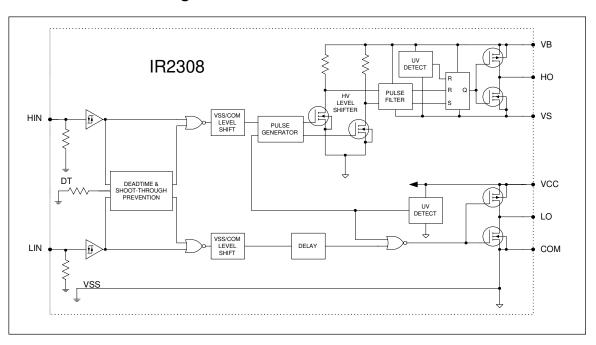

# **Functional Block Diagram**

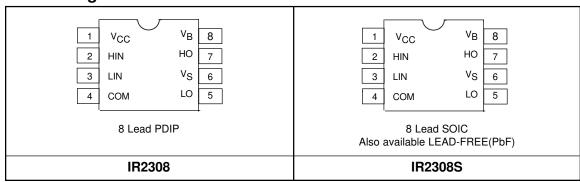

### **Lead Definitions**

| Symbol           | Description                                                 |

|------------------|-------------------------------------------------------------|

| HIN              | Logic input for high side gate driver output (HO), in phase |

| LIN              | Logic input for low side gate driver output (LO), in phase  |

| V <sub>B</sub>   | High side floating supply                                   |

| НО               | High side gate driver output                                |

| VS               | High side floating supply return                            |

| V <sub>C</sub> C | Low side and logic fixed supply                             |

| LO               | Low side gate driver output                                 |

| COM              | Low side return                                             |

# **Lead Assignments**

Figure 1. Input/Output Timing Diagram

Figure 2. Switching Time Waveform Definitions

Figure 3. Deadtime Waveform Definitions

International

IOR Rectifier

IR WORLD HEADQUARTERS: 233 Kansas Street, El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 3/19/2003

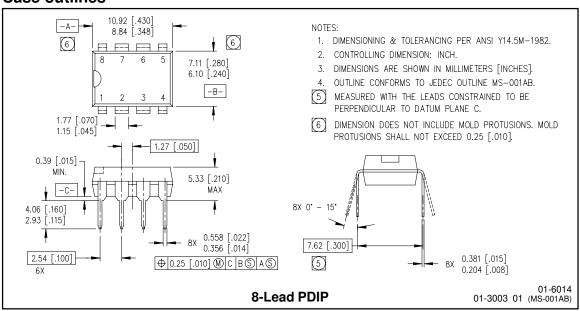

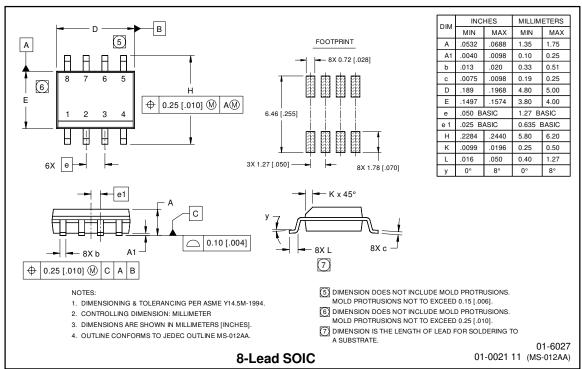

# IR2308(S) & (PbF)

### **Case outlines**

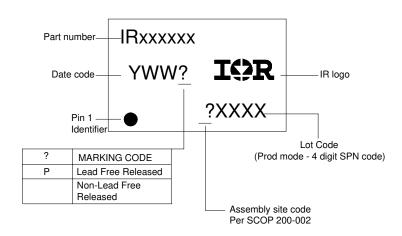

### LEADFREE PART MARKING INFORMATION

### **ORDER INFORMATION**

### **Basic Part (Non-Lead Free)**

8-Lead PDIP IR2308 order IR2308 8-Lead SOIC IR2308S order IR2308S

#### **Leadfree Part**

8-Lead PDIP R2308 not available 8-Lead SOIC IR2308S order IR2308SPbF

# International TOR Rectifier

Thisproduct has been designed and qualified for the industrial market.

Qualification Standards can be found on IR's Web Site http://www.irf.com

Data and specifications subject to change without notice.

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

6/15/2004