# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IRAUDAMP7D

# 25W-500W Scalable Output Power Class D Audio Power Amplifier Reference Design Using the IRS2092 Protected Digital Audio Driver

By

Jun Honda, Manuel Rodríguez, Wenduo Liu

### CAUTION:

International Rectifier suggests the following guidelines for safe operation and handling of IRAUDAMP7D Demo Board:

- Always wear safety glasses whenever operating Demo Board

- Avoid personal contact with exposed metal surfaces when operating Demo Board

- Turn off Demo Board when placing or removing measurement probes

# REFERENCE DESIGN

| Item | Table of Contents                       | Page  |

|------|-----------------------------------------|-------|

| 1    | Introduction of scalable design         | 3     |

| 2    | Power table values for each power model | 4     |

| 3    | Specifications                          | 4-5   |

| 4    | Connection setup                        | 6     |

| 5    | Test procedure                          | 7     |

| 6    | Performance and test graphs             | 8-13  |

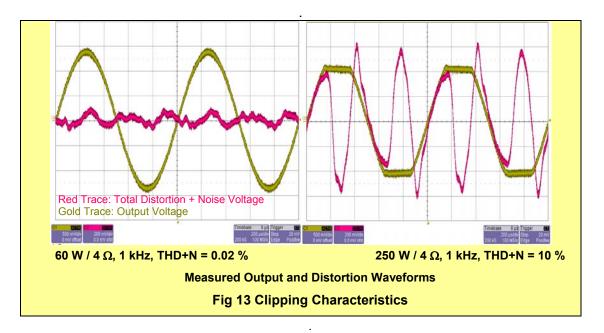

| 7    | Clipping characteristics                | 14    |

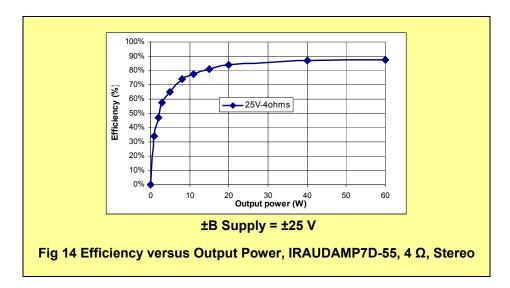

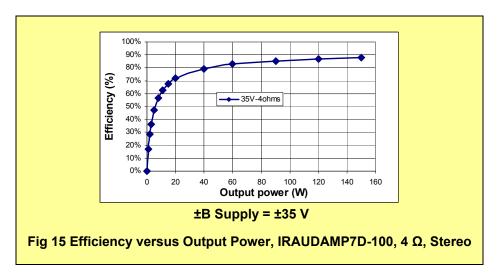

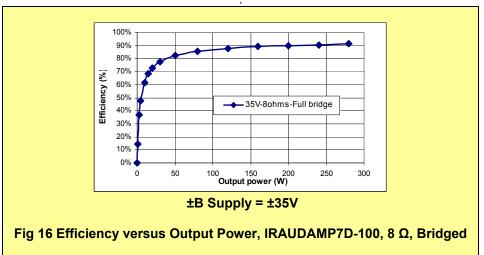

| 8    | Efficiency                              | 14-16 |

| 9    | Thermal considerations                  | 16    |

| 10   | PSRR, half bridge, full bridge          | 16    |

| 11   | Short circuit response                  | 17-18 |

| 12   | IRAUDAMP7D Overview                     | 18-19 |

| 13   | Functions Descriptions                  | 20-22 |

| 14   | Selectable dead Time                    | 22    |

| 15   | Protection Features                     | 22-25 |

| 16   | Click and pop noise control             | 25    |

| 17   | Bus pumping                             | 26    |

| 18   | Bridged configuration                   | 27    |

| 19   | Input signal and Gain                   | 28    |

| 20   | Gain settings                           | 29    |

| 21   | Schematics                              | 30-32 |

| 22   | Bill of Materials                       | 33-36 |

| 23   | IRAUDAMP7D models differential table    | 36    |

| 24   | Hardware                                | 37-38 |

| 25   | PCB specifications                      | 39    |

| 26   | Assembly Drawings                       | 40    |

| 27   | Revision changes descriptions           | 41    |

# Introduction

The IRAUDAMP7D reference design is a two-channel Class D audio power amplifier that features output power scalability. The IRAUDAMP7D offers selectable half-bridge (stereo) and full-bridge (bridged) modes.

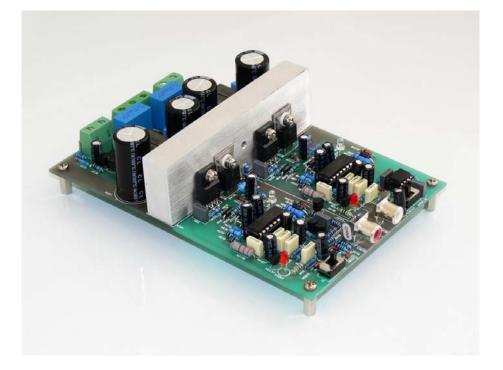

This reference design demonstrates how to use the IRS2092 Class D audio driver IC, along with IR's digital audio dual MOSFETs, such as IRFI4024H-117P, IRFI4019H-117P, IRFI4212H-117P and IRFI4020H-117P, on a single layer PCB. The design shows how to implement peripheral circuits on an optimum PCB layout using a single sided board.

The resulting design requires a small heatsink for normal operation (one-eighth of continuous rated power). The reference design provides all the required housekeeping power supplies and protections.

#### Unless otherwise noted, this user's manual is based on 150V model, IRAUDAMP7D-150,.

Other output power versions can be configured by replacing components given in the component selection of Table 5 on page 36

#### Applications

- AV receivers

- Home theater systems

- Mini component stereos

- Powered speakers

- Sub-woofers

- Musical Instrument amplifiers

- Automotive after market amplifiers

#### Features

| Output Power:                 | Scalable output power from 25W- 500W (see Table 1)                     |

|-------------------------------|------------------------------------------------------------------------|

| Residual Noise:               | 200 μV, IHF-A weighted, AES-17 filter                                  |

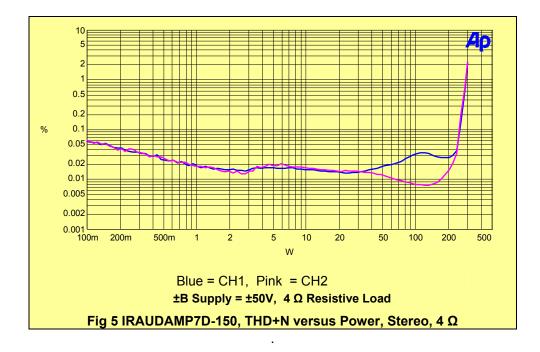

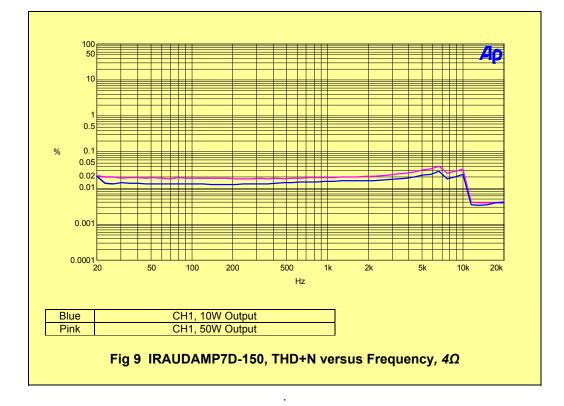

| Distortion:                   | 0.05 % THD+N @ 60W, 4 Ω                                                |

| Efficiency:                   | 90 % @ 500W, 8 Ω, Class D stage                                        |

| Multiple Protection Features: | Over-current protection (OCP), high side and low side MOSFET           |

|                               | Over-voltage protection (OVP),                                         |

|                               | Under-voltage protection (UVP), high side and low side MOSFET          |

|                               | DC-protection (DCP),                                                   |

|                               | Over-temperature protection (OTP)                                      |

| PWM topology:                 | Self-oscillating PWM, half-bridge or full-bridge topologies selectable |

|                              |                 | Model Name     |                |                |                |  |

|------------------------------|-----------------|----------------|----------------|----------------|----------------|--|

| ltem                         |                 | AMP7D-55       | AMP7D-100      | AMP7D-150      | AMP7D-200      |  |

| IR Power<br>MOSFET           | FET1A,<br>FET1B | IRFI4024H-117P | IRFI4212H-117P | IRFI4019H-117P | IRFI4020H-117P |  |

| Half Bridge                  | 8 Ω             | 25W x 2        | 60W x 2        | 125W x 2       | 250W x 2       |  |

| Than Bridge                  | Half Bridge 4 Ω |                | 120W x 2       | 250W x 2       | Not Supported  |  |

| Full Bridge                  | 8 Ω             | 100W x 1       | 240W x 1       | 500W x 1       | Not Supported  |  |

| Nominal<br>Supply<br>Voltage | +B, -B          | ±25V           | ±35V           | ±50V           | ±70V           |  |

| Min/Max<br>Supply<br>Voltage | +B, -B          | ±20V ~ ±28V    | ±28V ~ ±45V    | ±45V ~ ±60V    | ±60V ~ ±80V    |  |

| Voltage<br>Gain              | Gv              | 20             | 30             | 36             | 40             |  |

## Table 1 IRAUDAMP7D Specification Table Series

#### Notes:

- All the power ratings are at clipping power (THD+N = 1 %). To estimate power ratings at THD+N=10%, multiply them by 1.33

- See Table 5 on page 36 for the complete listing of components table.

## **Specifications**

#### General Test Conditions for IRAUDAMP7D-150 (unless otherwise noted) Notes / Conditions

| Power Supply Voltages      | ± 50V  |

|----------------------------|--------|

| Load Impedance             | 4 Ω    |

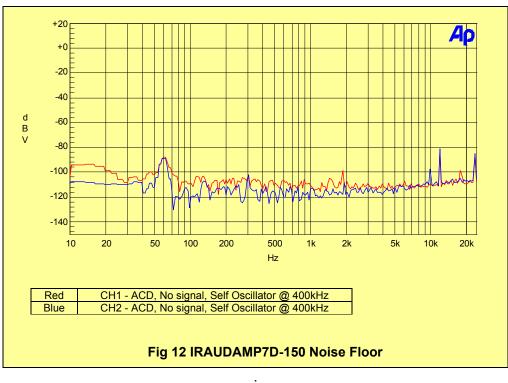

| Self-Oscillating Frequency | 400kHz |

| Voltage Gain               | 36     |

| Electrical Data                  | Typical                     | Notes / Conditions                |

|----------------------------------|-----------------------------|-----------------------------------|

| IR Devices Used IRS209           | 2, Protected digital audic  | o driver                          |

| IRFI402                          | 24H-117P, IRFI4019H-1       | 17P, IRFI4212H-117P, IRFI4020H-   |

| 117P D                           | igital audio MOSFETs        |                                   |

| PWM Modulator Self-ose           | cillating, second order sig | ma-delta modulation, analog input |

| Power Supply Range               | ± 45V to ± 60V              | Or see table 1 above              |

| Output Power CH1-2: (1 % THD+N)  | 300W                        | 1kHz                              |

| Output Power CH1-2: (10 % THD+N) | 400W                        | 1kHz                              |

| Rated Load Impedance             | 8 - 4 Ω                     | Resistive load                    |

| Standby Supply Current           | +50 mA/-80 mA               | No input signal                   |

| Total Idle Power Consumption     | 7W                          | No input signal                   |

| Channel Efficiency               | 90 %                        | Single-channel driven, 120W       |

## **Audio Performance**

|                                      | Before<br>Demodulator | Class D<br>Output | Notes / Conditions                                                  |

|--------------------------------------|-----------------------|-------------------|---------------------------------------------------------------------|

| THD+N, 1W                            | 0.09 %                | 0.1 %             |                                                                     |

| THD+N, 10W                           | 0.03 %                | 0.04 %            | 1kHz, Single-channel driven                                         |

| THD+N, 60W                           | 0.03 %                | 0.05 %            | _                                                                   |

| THD+N, 100W                          | 0.08 %                | 0.10 %            |                                                                     |

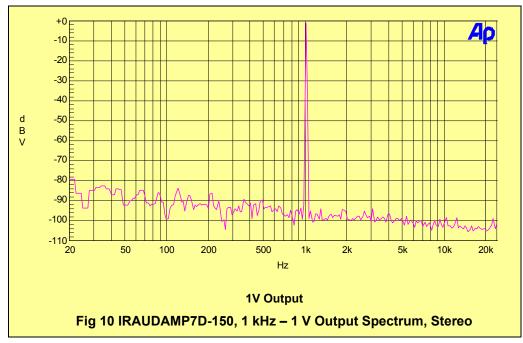

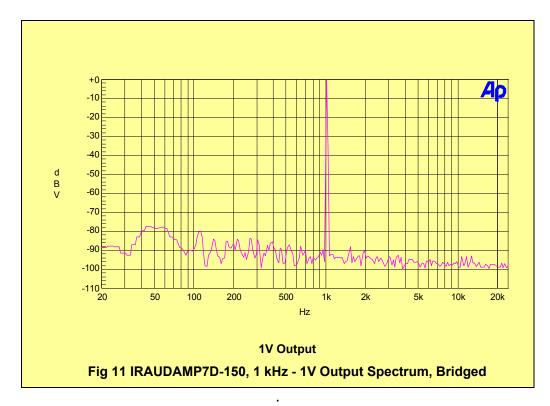

| Dynamic Range                        | 100 dB                | 100 dB            | A-weighted, AES-17 filter,<br>Single-channel operation              |

| Residual Noise                       | 200 μV                | 200 μV            | 22 Hz – 20kHz, AES17 filter<br>Self-oscillating frequency<br>400kHz |

| Damping Factor                       | 2000                  | 170               | 1kHz, relative to 4 $\Omega$ load                                   |

|                                      | 95 dB                 | 90 dB             | 100Hz                                                               |

| Channel Separation                   | 85 dB                 | 80 dB             | 1kHz                                                                |

|                                      | 75 dB                 | 65 dB             | 10kHz                                                               |

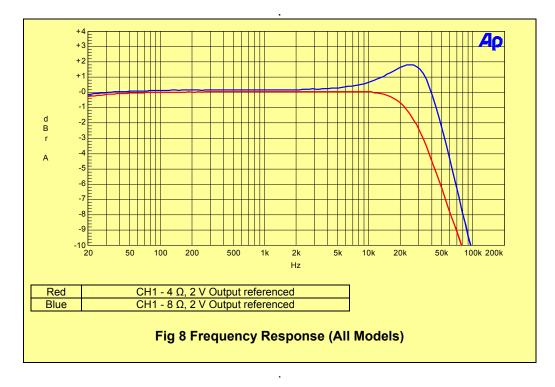

| Frequency Response : 20 Hz-<br>20kHz | 20 Hz-35kHz           | ±3 dB             | 1W, 4 Ω – 8 Ω Load                                                  |

# Thermal Performance (T<sub>A</sub>=25 °C)

| Condition                    | Typical                                           | Notes / Conditions       |

|------------------------------|---------------------------------------------------|--------------------------|

| Idling                       | T <sub>C</sub> =30 °C<br>T <sub>PCB</sub> =37 °C  | No signal input          |

| 2 ch x 15W (1/8 rated power) | T <sub>C</sub> =54 °C<br>T <sub>PCB</sub> =67 °C  |                          |

| 2 ch x 120W (Rated power)    | T <sub>C</sub> =80 °C<br>T <sub>PCB</sub> =106 °C | OTP shutdown after 150 s |

# **Physical Specifications**

| Dimensions | 6"(L) x 4"(W) x 1.25"(H)           |

|------------|------------------------------------|

|            | 150 mm (L) x 100 mm (W) x 35 mm(H) |

| Weight     | 0.330kgm                           |

# **Test Setup**

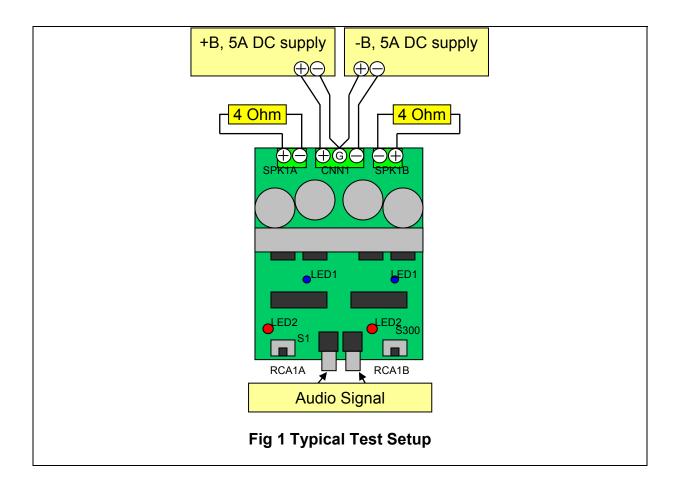

# **Connector Description**

| CH1 IN  | RCA1A | Analog input for CH1                   |

|---------|-------|----------------------------------------|

| CH2 IN  | RCA1B | Analog input for CH2                   |

| SUPPLY  | CNN1  | Positive and negative supply (+B / -B) |

| CH1 OUT | SPK1A | Output for CH1                         |

| CH2 OUT | SPK1B | Output for CH2                         |

# **Switches Descriptions**

| S1   | Shutdown PWM                     |

|------|----------------------------------|

| S300 | Half bridge / Full bridge select |

## **Indicator Description**

| LED1A, B | PWM (presence of low side gate signal) |

|----------|----------------------------------------|

| LED2A,B  | Protection                             |

# **Test Procedures**

## **Test Setup:**

- 1. On the unit under test (UUT), set switch S1 to OFF and S300 to Stereo positions.

- 2. Connect 4  $\Omega$ -200 W dummy loads to output connectors, SPKR1A and SPKR1B, as shown on Fig 1.

- 3. Set up a dual power supply ±50V with 5A current limit

- 4. Turn OFF the dual power supply before connecting to UUT.

- 5. Connect the dual power supply to CNN1, as shown in Fig 1.

### Power up:

- 6. Turn ON the dual power supply. The ±B supplies must be applied and removed at the same time.

- 7. The red LEDs (Protections) turn ON immediately and stay on as long as S1 is in OFF position. Blue LEDs stay OFF.

- 8. Quiescent current for the positive and negative supplies must be less than 50mA, while S1 is in OFF position. Under this condition, IRS2092 is in shutdown mode.

- 9. Slide S1 to ON position; after one second delay, the two blue LEDs turn ON and the red LEDs turns off. The two blue LEDs indicate that PWM oscillation is present. This transition delay time is controlled by CSD pin of IRS2092, capacitor CP3

- 10. Under the normal operating condition with no input signal applied, quiescent current for the positive supply must be less than 50 mA; the negative supply current must be less than 100 mA.

# Switching Frequency Test:

With an oscilloscope, monitor switching waveform at test points VS1 of VS2 and L1B of CH2. Self oscillating frequency must be 400kHz ± 25kHz. Note: The self-oscillating switching frequency is pre-calibrated to 400kHz by the value of R11. To change switching frequency, change the resistances of R11A and R11B for CH1 and CH2 respectively.

# Audio Functionality Tests:

- 12. Set the signal generator to 1kHz, 20 mV<sub>RMS</sub> output.

- 13. Connect audio signal generators to RCA1A and RCA1B.

- 14. Sweep the audio signal voltage from 15 mV<sub>RMS</sub> to 1 V<sub>RMS</sub>.

- 15. Monitor the output signals at SPK1A/B with an oscilloscope. Waveform must be a non distorted sinusoidal signal.

- 16. Observe 1  $V_{RMS}$  input generates output voltage of 36  $V_{RMS}$ . The ratio, R8/(R7+R2), determines the voltage gain of IRAUDAMP7D.

- 17. Set switch S300 to Bridged position.

- 18. Observe that voltage gain doubles.

# Test Setup using Audio Precision (Ap):

- 19. Use unbalance-floating signal generator outputs.

- 20. Use balanced inputs taken across output terminals, SPKR1A and SPKR1B.

- 21. Connect Ap frame ground to GND in terminal CNN1.

- 22. Place AES-17 filter for all the testing except frequency response.

- 23. Use signal voltage sweep range from 15 mV<sub>RMS</sub> to 1 V<sub>RMS</sub>.

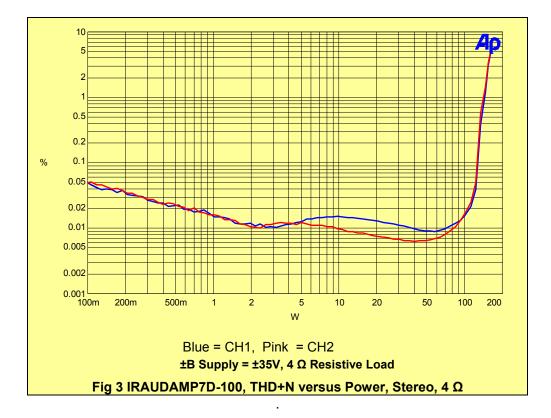

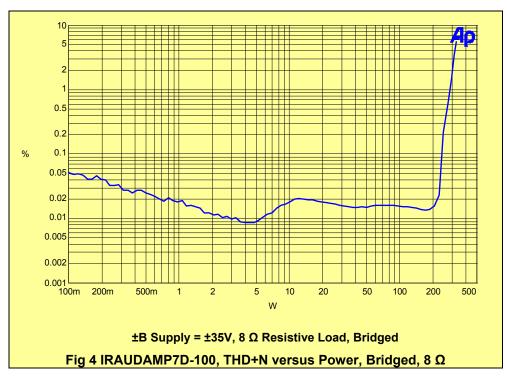

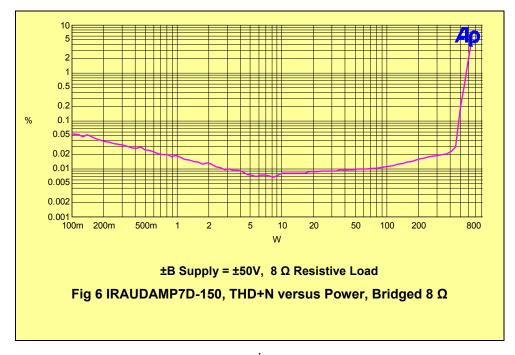

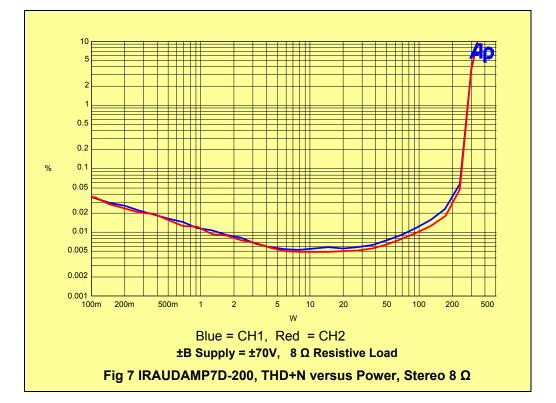

- 24. Run Ap test programs for all subsequent tests as shown in Fig 2- Fig 13 below.

# **Test Results**

# **REFERENCE DESIGN**

.

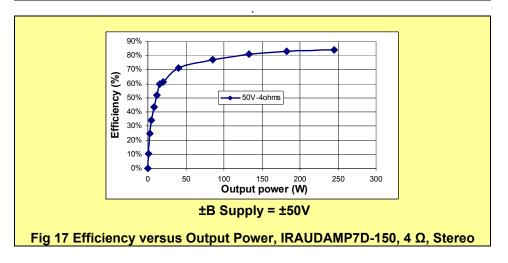

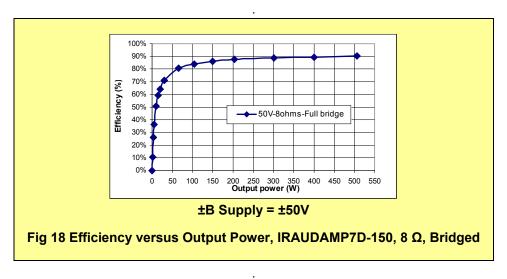

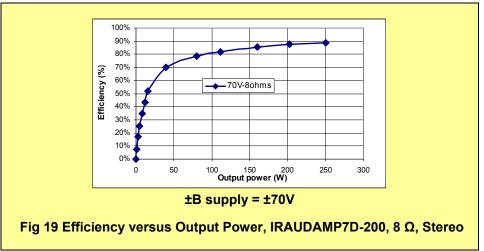

# Efficiency

Figs 14-19 show efficiency characteristics of the IRAUDAMP7D. The high efficiency is achieved by following major factors:

- 1) Low conduction loss due to the dual FETs offering low  $R_{DS(ON)}$

- Low switching loss due to the dual FETs offering low input capacitance for fast rise and fall times

- 3) Secure dead-time provided by the IRS2092, avoiding cross-conduction

### **Thermal Considerations**

With this high efficiency, the IRAUDAMP7D design can handle one-eighth of the continuous rated power, which is generally considered to be a normal operating condition for safety standards, without additional heatsink or forced air-cooling.

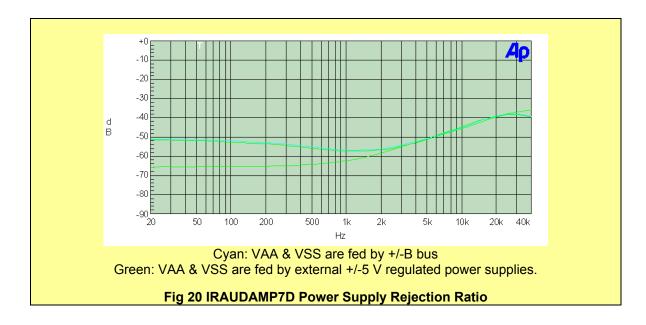

# Power Supply Rejection Ratio (PSRR)

The IRAUDAMP7D obtains good power supply rejection ratio of -65 dB at 1kHz shown in Fig 20. With this high PSRR, IRAUDAMP7D accepts any power supply topology as far as the supply voltages fit in the min and max range.

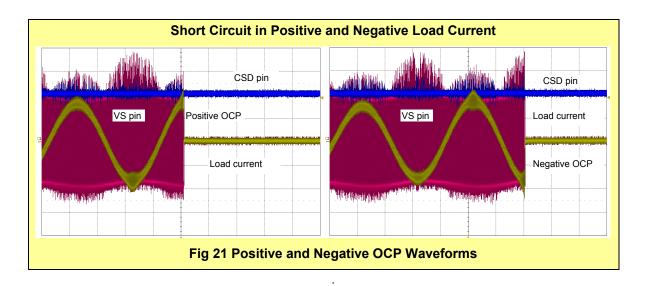

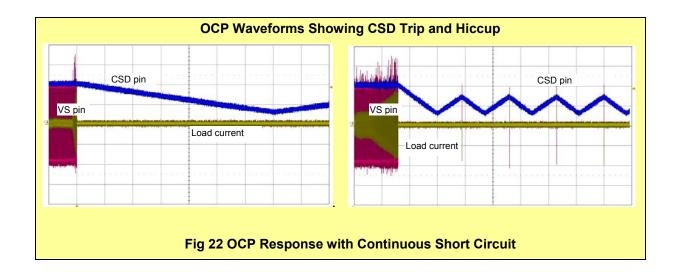

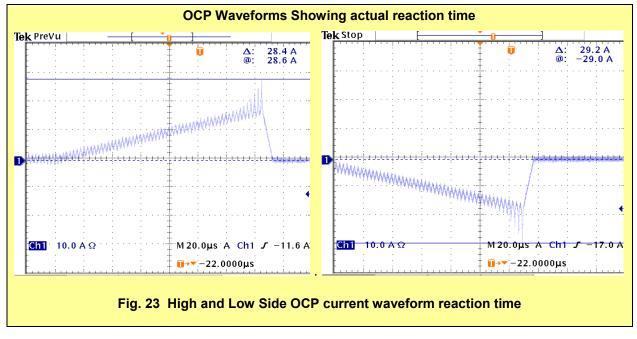

# **Short Circuit Protection Response**

Figs 21-23 show over current protection reaction time of the IRAUDAMP7D in a short circuit event. As soon as the IRS2092 detects over current condition, it shuts down PWM. After one second, the IRS2092 tries to resume the PWM. If the short circuit persists, the IRS2092 repeats try and fail sequences until the short circuit is removed.

# **Actual Reaction Time**

# IRAUDAMP7D Overview

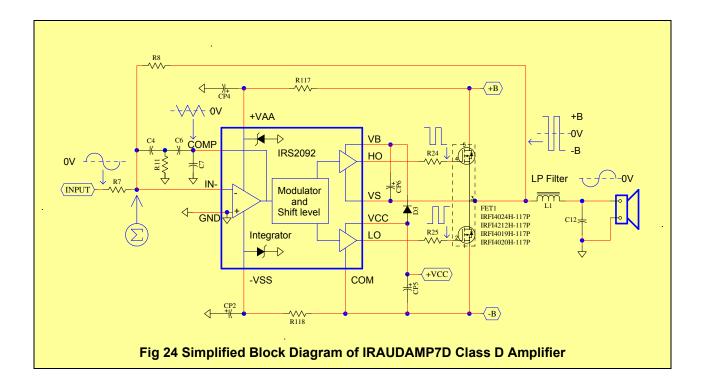

The IRAUDAMP7D features a self-oscillating type PWM modulator for the lowest component count, highest performance and robust design. This topology represents an analog version of a second-order sigma-delta modulation having a Class D switching stage inside the loop. The

benefit of the sigma-delta modulation, in comparison to the carrier-signal based modulation, is that all the error in the audible frequency range is shifted to the inaudible upper-frequency range by nature of its operation. Also, sigma-delta modulation allows a designer to apply a sufficient amount of error correction.

The IRAUDAMP7D self-oscillating topology consists of following essential functional blocks.

- Front-end integrator

- PWM comparator

- Level shifters

- Gate drivers and MOSFETs

- Output LPF

## Integrator

Referring to Fig 24 below, the input operational amplifier of the IRS2092 forms a front-end secondorder integrator with R7, C4, C6, and R11. The integrator that receives a rectangular feedback signal from the PWM output via R8 and audio input signal via R7 generates quadratic carrier signal in COMP pin. The analog input signal shifts the average value of the quadratic waveform such that the duty cycle varies according to the instantaneous voltage of the analog input signal.

#### **PWM Comparator**

The carrier signal in COMP pin is converted to PWM signal by an internal comparator that has threshold at middle point between VAA and VSS. The comparator has no hysteresis in its input threshold.

### Level Shifters

The internal input level-shifter transfers the PWM signal down to the low-side gate driver section. The gate driver section has another level-shifter that level shifts up the high-side gate signal to the high-side gate driver section.

### Gate Drivers and MOSFETs

The received PWM signal is sent to the dead-time generation block where a programmable amount of dead time is added into the PWM signal between the two gate output signals of LO and HO to prevent potential cross conduction across the output power MOSFETs. The high-side level-shifter shifts up the high-side gate drive signal out of the dead-time block.

The IRS2092 drives two MOSFETs, high- and low-sides, in the power stage providing the amplified PWM waveform.

### Output LPF

## **REFERENCE DESIGN**

The amplified PWM output is reconstructed back to analog signal by the output LC LPF. Demodulation LC low-pass filter (LPF) formed by L1 and C12, filters out the Class D switching carrier signal leaving the audio output at the speaker load. A single stage output filter can be used with switching frequencies of 400 kHz and greater; a design with a lower switching frequency may require an additional stage of LPF.

# **Functional Descriptions**

# **IRS2092 Gate Driver IC**

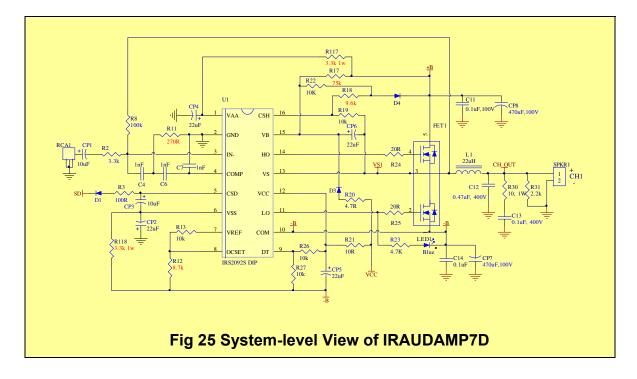

The IRAUDAMP7D uses IRS2092, a high-voltage (up to 200 V), high-speed power MOSFET driver with internal dead-time and protection functions specifically designed for Class D audio amplifier applications. These functions include OCP and UVP. The IRS2092 integrates bidirectional over current protection for both high-side and low-side MOSFETs. The dead-time can be selected for optimized performance according to the size of the MOSFET, minimizing dead-time while preventing shoot-through. As a result, there is no gate-timing adjustment required externally. Selectable dead-time through the DT pin voltage is an easy and reliable function which requires only two external resistors, R26 and R27 as shown on Fig 25 below.

The IRS2092 offers the following functions.

• PWM modulator

- Dead-time insertion

- Over current protection

- Under voltage protection

- Level shifters

Refer to IRS2092 datasheet and AN-1138 for more details.

### Self-Oscillating Frequency

Self-oscillating frequency is determined by the total delay time along the control loop of the system; the propagation delay of the IRS2092, the MOSFETs switching speed, the time-constant of front-end integrator (R7, R8, R11, C4, C6, C7). Variations in +B and –B supply voltages also affect the self-oscillating frequency.

The self-oscillating frequency changes with the duty ratio. The frequency is highest at idling. It drops as duty cycle varies away from 50%.

### Adjustments of Self-Oscillating Frequency

Use R11 to set different self-oscillating frequencies. The PWM switching frequency in this type of self-oscillating switching scheme greatly impacts the audio performance, both in absolute

frequency and frequency relative to the other channels. In the absolute terms, at higher frequencies distortion due to switching-time becomes significant, while at lower frequencies, the bandwidth of the amplifier suffers. In relative terms, interference between channels is most significant if the relative frequency difference is within the audible range.

Normally, when adjusting the self-oscillating frequency of the different channels, it is suggested to either match the frequencies accurately, or have them separated by at least 25kHz. Under the normal operating condition with no audio input signal, the switching-frequency is set around 400kHz in the IRAUDAMP7D.

#### Selectable Dead-time

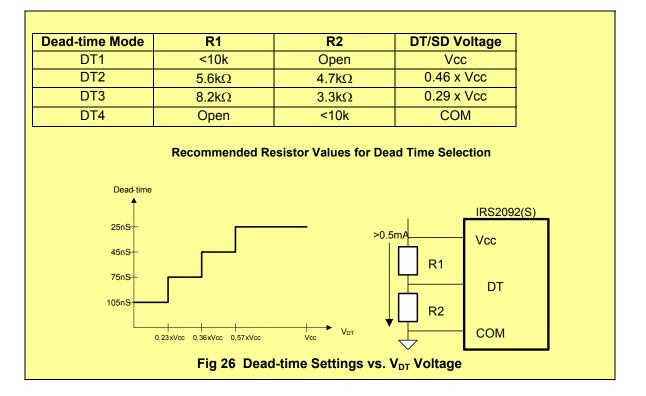

The dead-time of the IRS2092 is set based on the voltage applied to the DT pin. Fig 26 lists the suggested component value for each programmable dead-time between 25 and 105 ns. All the IRAUDAMP7D models use DT2 (45ns) dead-time.

### **Protection System Overview**

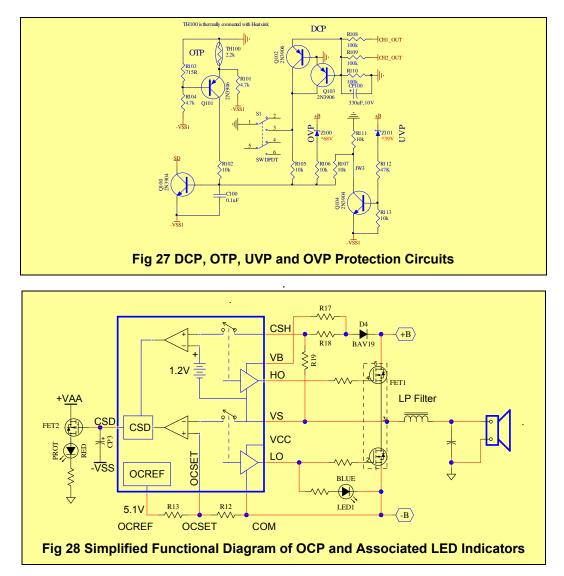

The IRS2092 integrates over current protection (OCP) inside the IC. The rest of the protections, such as over-voltage protection (OVP), under-voltage protection (UVP), speaker DC offset

protection (DCP) and over temperature protection (OTP), are realized externally to the IRS2092 (Fig 27).

In the event that any of these external fault conditions are detected, the external shutdown circuit will disable the output by pulling down CSD pins, turning on red LEDs, and turning off blue LEDs (Fig 28). If the fault condition persists, the protection circuit stays in shutdown until the fault is removed. Once the fault is cleared, the blue LEDs turn on and red LEDs turn off.

# Over-Current Protection (OCP) Low-Side Current Sensing

The low-side current sensing feature protects the low side MOSFET from an overload condition in negative load current by measuring drain-to-source voltage across  $R_{DS(ON)}$  during its on state. OCP shuts down the switching operation if the drain-to-source voltage exceeds a preset trip level.

The voltage setting on the OCSET pin programs the threshold for low-side over-current sensing. When the VS voltage during low-side conduction gets higher than the OCSET voltage, the IRS2092 turns off outputs and pulls CSD down to -VSS.

## High-Side Current Sensing

The high-side current sensing protects the high side MOSFET from an overload condition in positive load current by measuring drain-to-source voltage across  $R_{DS(ON)}$  during its on state. OCP shuts down the switching operation if the drain-to-source voltage exceeds a preset trip level.

High-side over-current sensing monitors drain-to-source voltage of the high-side MOSFET while it is in the on state through the CSH and VS pins. The CSH pin detects the drain voltage with reference to the VS pin, which is the source of the high-side MOSFET. In contrast to the low-side current sensing, the threshold of CSH pin to trigger OC protection is internally fixed at 1.2V. An external resistive divider R19, R18 and R17 are used to program a threshold as shown in Fig 26. An external reverse blocking diode D4 is required to block high voltage feeding into the CSH pin during low-side conduction. By subtracting a forward voltage drop of 0.6V at D4, the minimum threshold which can be set for the high-side is 0.6V across the drain-to-source.

| Function                            | Device       | Amp7-55 | Amp7-100 | Amp7-150 | Amp7-200 |

|-------------------------------------|--------------|---------|----------|----------|----------|

| OCSET                               | R12A<br>R12B | 1.3K    | 3.9K     | 7.5K     | 5.2K     |

| Tested OCP current 25°C             |              |         | 23A      | 30A      | 23A      |

| CSH                                 | R18A<br>R18B | 0.0     | 4.7K     | 9.6K     | 8.2K     |

| Tested OCP current 25°C             |              |         | 23A      | 29A      | 23A      |

| Peak load current<br>at rated power |              | 6.0A    | 8.7A     | 12.2A    | 8.9A     |

### Table 2 Actual OCP table setting thresholds

### **Over-Voltage Protection (OVP)**

OVP is provided externally to the IRS2092. OVP shuts down the amplifier if the bus voltage between GND and +B exceeds 75V. The threshold is determined by a Zener diode Z100. OVP

protects the board from harmful excessive supply voltages, such as due to bus pumping at very low frequency continuous output in stereo mode.

### Under-Voltage Protection (UVP)

UVP is provided externally to the IRS2092. UVP prevents unwanted audible noise output from unstable PWM operation during power up and down. UVP shuts down the amplifier if the bus voltage between GND and +B falls below a voltage set by Zener diode Z101.

## Speaker DC-Voltage Protection (DCP)

DCP protects speakers against DC output current feeding to its voice coil. DC offset detection detects abnormal DC offset and shuts down PWM. If this abnormal condition is caused by a MOSFET failure because one of the high-side or low-side MOSFETs short circuited and remained in the on state, the power supply needs to be cut off in order to protect the speakers. Output DC offset greater than ±4V triggers DCP.

## Offset Null (DC Offset) Adjustment

The IRAUDAMP7D requires no output-offset adjustment. DC offsets are tested to be less than ±20 mV.

### **Over-Temperature Protection (OTP)**

A NTC resistor, TH100 in Fig 25, is placed in close proximity to two dual MOSFETs on a heatsink to monitor heatsink temperature. If the heatsink temperature rises above 100 °C, the OTP shuts down both channels by pulling down CSD pins of the IRS2092. OTP recovers once the temperature has cooled down.

### **ON-OFF Switch**

OFF position of S1 forces the IRAUDAMP7D to stay in shutdown mode by pulling down the CSD pin. During the shutdown mode the output MOSFETs are kept off.

#### Click and POP Noise Reduction

Thanks to the click and pop elimination function built into the IRS2092, IRAUDAMP7D does not use any additional components for this function.