Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Data Sheet**

#### iMOTION™ Motion Controller Module for PM AC Fan

### **Quality Requirement Category: Industry**

#### **Features**

- Complete 250V 500V 3-phase inverter system in one chip

- Permanent Magnet Sinusoidal Motors Control by Hall sensors

Only two low cost Hall elements required

- High efficiency control by quadratic phase advance curve

- Internal clock based on external RC

- 15V single power supply3.3V Integrated Voltage Regulator

- Integrated protection features:

Dynamic overcurrent, Overtemperature,

Overspeed, Rotor lock, Undervoltage lockout

- Full Three Phase Gate Driver

- Integrated Bootstrap Diodes

- No heatsink required

- 12x12 mm<sup>2</sup> PQFN package

### **Applications**

• PM fan motor control

# Description

Other than the IRDM982 the IRDM983 only requires two hall sensors.

The integrated digital controller does not require any programming.

Instead there are 16 load curves stored in the internal ROM that can be selected via two resistor pairs.

The IRDM983 is packaged in the 12 x 12 PQFN package and designed to dissipate the power loss through a PCB without the use of an external heatsink.

There are two products available depending on the power rating of the internal high voltage MOSFETs:

- 1) IRDM983-025MB employs six MOSFETs 500V 2A and 600V high voltage IC

- 2) IRDM983-035MB employs six MOSFETs 500V 3A and 600V high voltage IC

#### PD19082016

# IRDM983-025MB, IRDM983-035MB Complete Motion Controller Module for PM AC fan

#### **Features**

- Complete 500V 3-phase inverter system in one chip

- No heat-sink required

- Permanent Magnet Sinusoidal Motors Control by two Hall sensors

- Selectable 4 or 12 pulse output per revolution<sup>1)</sup>

- High efficiency control by quadratic phase advance curve

- Internal clock based on external RC

- 15V single power supply

- 3.3V Integrated Voltage Regulator

- Dynamic overcurrent limit per temperature

- Over-temperature control

- Over-speed protection

- Rotor lock detection/protection

- Full Three Phase Gate Driver

- Integrated Bootstrap Diodes

- Under-voltage lockout

Typical ApplicationsFan motor control

# Product Summary

| Topology            | 3 Phase AC                                   |

|---------------------|----------------------------------------------|

| V <sub>OFFSET</sub> | ≤ 500 V for IRDM983-<br>025MB, IRDM983-035MB |

| Control             | Phase Advancement control                    |

| Feedback            | DC Bus shunt, 2 Hall sensor                  |

| Temperature sensor  | Integrated                                   |

#### **Package**

1) When used with 8 poles motor. In general it is 1 pulse / 3 pulses per electrical revolution.

# **Revision History**

- Created new DS (April, 2015)

Fixed part numbers typo (5 May 2015)

- Updated ESD level (19 August 2016)

# International **TOR** Rectifier

# IRDM983-025MB, IRDM983-035MB

| Table of Contents                                         |

|-----------------------------------------------------------|

| INTRODUCTION4                                             |

| QUALIFICATION INFORMATION†6                               |

| IRDM983-025MB / IRDM983-035MB ELECTRICAL CHARACTERISTICS9 |

| LEAD DEFINITIONS21                                        |

| PACKAGE OUTLINE23                                         |

| PACKAGE MARKING25                                         |

| SOLDERING TEMPERATURE PROFILE26                           |

|                                                           |

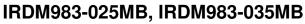

### Introduction

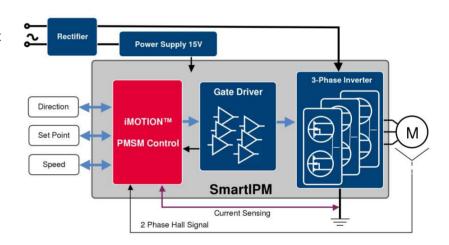

IRDM983-025MB, IRDM983-035MB are the complete PM motor controller including six power MOSFET, high voltage integrated circuit, high precision analog circuit and digital control algorithm. There are two products depending on power rating of internal high voltage MOSFET listed below:

- 1) IRDM983-025MB employs six MOSFET 500V 2A and 600V high voltage IC

- 2) IRDM983-035MB employs six MOSFET 500V 3A and 600V high voltage IC

All two products are packaged in the 12 x 12 PQFN package and designed to dissipate the power loss through a mating PCB without an external heatsink. All two products contain exactly same control algorithm and analog functions. The controller implements a two Hall sensors based control algorithm for 3-phase sinusoidal permanent magnet motor fan applications. The control also employs high efficiency PM motor control algorithm based on a quadratic load curve stored in internal ROM. 16 possible curves are selectable.

All devices have an on-chip voltage regulator to derive the 3.3V, required by the digital logic, from the 15V (VCC) supply. The 3.3VDC regulated voltage pin is available externally for connection to Hall-effect sensors. The IC provides low power standby (less than 7mW) mode of operation that 3.3V power is cut off when VSP (Voltage Input) becomes less than 1.15V to provide further power efficient operation.

An integrated A/D Converter is used to acquire EFF load curve selection, temperature (internal temp sensing), and the VSP input that sets the voltage applied to the motor. An internal temperature sensor is interfaced to the ADC and resulting digital conversion data is used to control the dynamic overcurrent setpoints as well as max overtemperature limit.

The protection functions include a supply under-voltage lockout (3.3V and 15VDC), over-speed protection, over-temperature limit and Over-current limitation protections. The reset circuitry includes a Power-On reset block and a reset input.

All devices do not require any programming. Default coefficients and system parameters are stored in internal ROM. The EFF input pin, used to adapt to specific motor and load to improve efficiency, can be used by means of two resistor pairs to choose one of 16 pre-stored load curves in ROM. DIR is a digital input pins which specify the motor direction command (CW or CCW).

All devices have an on-chip PLL to generate internal clocks. The PLL requires an external low frequency reference clock (32,768 Hz). The clock can be provided through an RC network connected to CLKIN and XTAL pins.

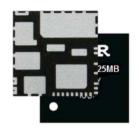

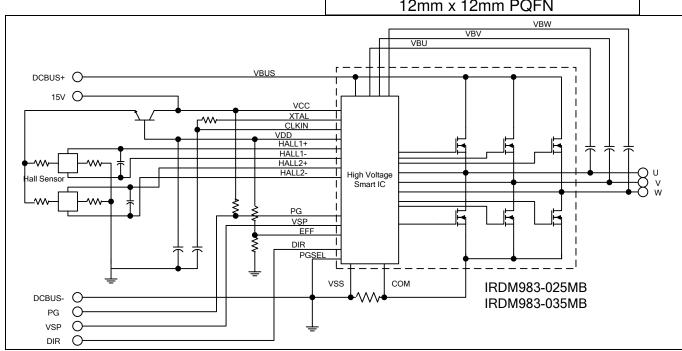

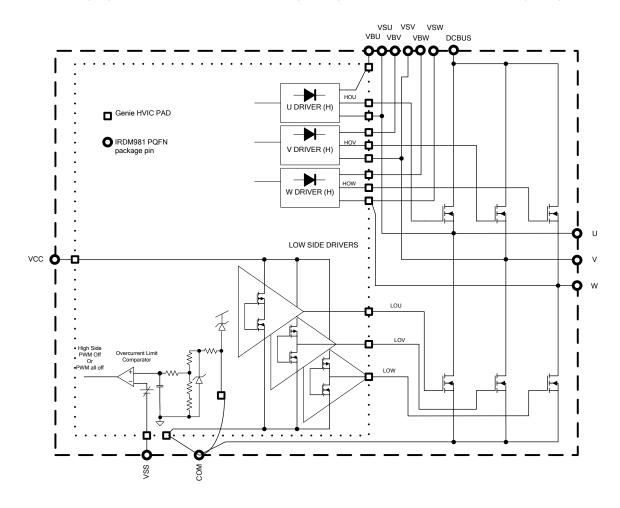

The IRDM983-025MB, IRDM983-035MB integrate high and low side gate drivers for applications up to 500V, it includes integrated Bootstrap FET that emulate bootstrap diode function and six power MOSFETs. The simplified block diagram is shown in Figure 1 in terms of hardware elements.

### Simplified Block Diagram

Figure 1 Simplified Block Diagram

# **Qualification Information**†

| Qualifi                    | ication Level    | Industrial <sup>††</sup> (per JEDEC JESD 47)<br>Stress Test; Preconditioning, Temp Cycle, Autoclave, THB, HTSL, LTSL, IOL,                                                                                             |                                                                                                                                                                                                |  |  |

|----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Moisture Sensitivity Level |                  | PQFN                                                                                                                                                                                                                   | MSL3 <sup>†††</sup> (per IPC/JEDEC J-STD-020) Floor Life Time; 168 hours Conditions; <30°C/60% RH Bake conditions; 125 +5/-0°C, 24 hours minimum                                               |  |  |

| ECD                        | Machine Model    | R1=0Ω, C1=200pF+/-10%                                                                                                                                                                                                  | Class B (per JEDEC Standard JESD22-A115) R1=0\(\Omega\), C1=200pF+/-10\(\omega\) Any part that passes after exposure to an ESD pulse of 100V, but fails after exposure to an ESD pulse of 150V |  |  |

| ESD                        | Human Body Model | Class 2 (per EIA/JEDEC standard EIA/JESD22-A114) R1=1500\(\text{Q+}/-1\)\%, C1=100\(\text{F+}/-10\)\% Any part that passes after exposure to an ESD pulse of 1500V, but fails after exposure to an ESD pulse of 2000V. |                                                                                                                                                                                                |  |  |

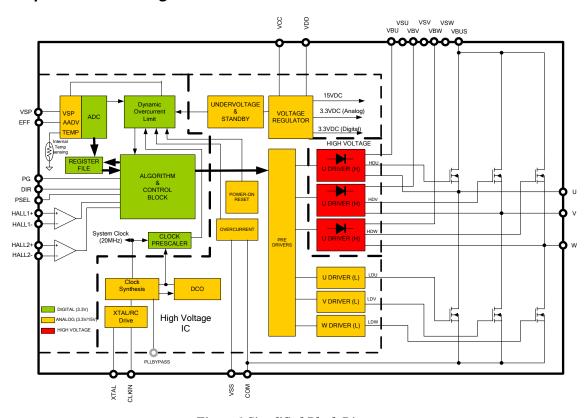

| IC Lat                     | ch-Up Test       | Class I, Level A (per JESD78) Testing performed at room temperature ambient. The failure criteria as defined in table 1.                                                                                               |                                                                                                                                                                                                |  |  |

| RoHS                       | Compliant        | Yes                                                                                                                                                                                                                    |                                                                                                                                                                                                |  |  |

<sup>†</sup> Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

<sup>††</sup> Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

<sup>†††</sup> Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

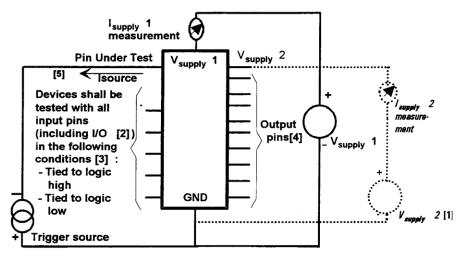

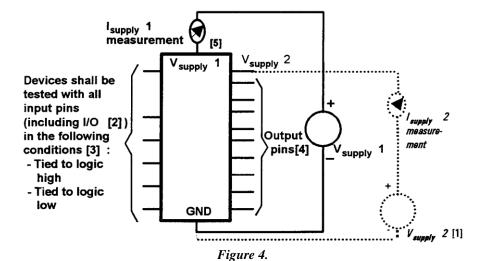

| CLASS | TEST<br>TYPE                                         | TRICCER<br>POLARITY       | CONDITION<br>OF<br>UNITESTED<br>INPUT PINS      | TEST TEMPERATURE (±2°C)            | V <sub>supply</sub><br>CONDITION                                  | TRIGGER TEST<br>CONDITIONS<br>[6]                                 | FAILURE<br>CRITERIA               |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

|-------|------------------------------------------------------|---------------------------|-------------------------------------------------|------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---------|-------------|-------------|-------------|-------------|-------------|-------------|-----------------------------------------------------------------|-----------|--|

|       |                                                      | POSITIVE<br>see<br>FIGURE | Max. Logic<br>High [1]<br>Min. Logic<br>Low [1] |                                    |                                                                   | +(Inom+100 mA)<br>or 1.5X Inom,<br>whichever is<br>greater [3]    |                                   |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

| l     | NEGATIVE Max. Logic High [1] see FIGURE Min. Logic   |                           | Room                                            | Maximum operating voltage for each | -100 mA or5X<br>Inom, whichever<br>is greater in<br>magnitude [4] |                                                                   |                                   |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

|       | V <sub>supply</sub><br>OVER-<br>VOLT-                | see                       | Max. Logic<br>High [1]                          | temperature                        | temperature                                                       | temperature                                                       | temperature                       | temperature | temperature | temperature | temperature | temperature | temperature | temperature | pin gro | temperature | temperature | temperature | temperature | temperature | temperature | V <sub>supply</sub><br>pin group<br>per device<br>specification | 1.5 X max |  |

|       | AGE<br>TEST                                          | FIGURE                    | Min. Logic<br>Low [1]                           |                                    |                                                                   | V <sub>supply</sub> [2]                                           | 1.4X<br>Inom<br>or Inom<br>+10 mA |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

|       | 1 TEST                                               | POSITIVE<br>see<br>FIGURE | Max. Logic<br>High [1]<br>Min. Logic<br>Low [1] |                                    |                                                                   | +(Inom+100 mA)<br>or 1.5X Inom,<br>whichever is<br>greater [3]    | whichever<br>is greater<br>[5]    |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

| 11    | 1-TEST                                               | NEGATIVE<br>see<br>FIGURE | Max. Logic<br>High [1]<br>Min. Logic<br>Low [1] | Maximum<br>ambient                 | Maximum operating voltage for each                                | -100 mA or5X<br>Inom, whichever<br>is greater in<br>magnitude [4] |                                   |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

|       | V <sub>supply</sub><br>OVER-<br>VOLT-<br>ACE<br>TEST | OMER-                     | see                                             | Max. Logic<br>High [1]             | operating<br>temperature                                          | V <sub>supply</sub><br>pin group<br>per device<br>specification   | 1.5 X max.                        |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

|       |                                                      | FIGURE                    | Min. Logic<br>Low[1]                            |                                    |                                                                   | V <sub>supply</sub> [2]                                           |                                   |             |             |             |             |             |             |             |         |             |             |             |             |             |             |                                                                 |           |  |

Table 1.

Figure 2.

Figure 3.

### IRDM983-025MB/-035MB Electrical Characteristics

### Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to **VSS** unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

Ta=25C, unless otherwise stated.

| Symbol                | Definition                                             | Min.              | Max.      | Units  | Condition                                                                    |

|-----------------------|--------------------------------------------------------|-------------------|-----------|--------|------------------------------------------------------------------------------|

| $V_{ISO}$             | Isolation voltage                                      |                   | -         | Vrms   | AC 1 minute                                                                  |

| VISO                  | Isolation voltage                                      | 1800              | -         | VIIIIS | AC 1 second                                                                  |

| DCBUS                 | DC bus voltage                                         | bus voltage _ 500 |           |        | IRDM983-025MB<br>IRDM983-035MB                                               |

| DCBUS <sub>STAT</sub> | DC bus voltage for PWM off                             | -                 | 600 V     |        | IRDM983-025MB<br>IRDM983-035MB<br>VSP=0V, 1 minute,<br>CO1=CO2 <sup>2)</sup> |

| VBU, VBV,<br>VBW      | High-side floating absolute voltage                    | -0.3              | 525       |        |                                                                              |

| VSU, VSV,<br>VSW      | High-side floating supply offset voltage               | VB - 25           | VB + 0.3  |        |                                                                              |

| VCC                   | Low side power supply absolute voltage                 | -0.3              | 24        |        |                                                                              |

|                       | Drain current, IRDM983-035MB                           | -                 | 3.9       |        | Tc=25°C, Rth=2C/W                                                            |

| ID                    | Drain current, IRDM983-025MB                           | -                 | 2.6       | А      | Tc=25°C, Rth=3C/W                                                            |

| I <sub>VDD</sub>      | VDD current capability                                 | -                 | 2         | 0      | TW=1ms                                                                       |

| I <sub>VSP</sub>      | VSP input current                                      | -                 | 5         | mA     |                                                                              |

| COM                   | Power Ground                                           | VCC - 24          | VCC + 0.3 |        |                                                                              |

| $V_{HCOM}$            | Hall Sensor input common mode voltage                  | -0.3              | VDD       |        |                                                                              |

| $V_{PG}$              | Open drain output motor evolution pulse                | -0.3              | VCC+0.3   |        |                                                                              |

| $V_{VSP}$             | Analog input voltage VSP                               | -0.3              | 10.0      | V      |                                                                              |

| $V_{DIR}$ $V_{EFF}$   | Direction, Efficiency curve pins input voltage         | -0.3              | VDD+0.3   |        |                                                                              |

| VDD                   | VDD 3.3V voltage regulator output                      |                   | 3.6       |        | No short to ground                                                           |

| PD                    | Package power dissipation @ Tc ≤ +100 °C <sup>1)</sup> | -                 | 5         | W      |                                                                              |

| TJ                    | Junction temperature <sup>1)</sup>                     | -                 | 150       |        |                                                                              |

| TS                    | Storage temperature <sup>1)</sup>                      | -55               | 150       | °C     |                                                                              |

| TL                    | Lead temperature (soldering, 10 seconds) <sup>1)</sup> | -                 | 260       |        |                                                                              |

|                       |                                                        |                   |           |        |                                                                              |

<sup>1)</sup> Guarantee by design, not tested at manufacturing

<sup>2)</sup> Output capacitance between VB-VS and VS-COM are same within  $\pm -1\%$

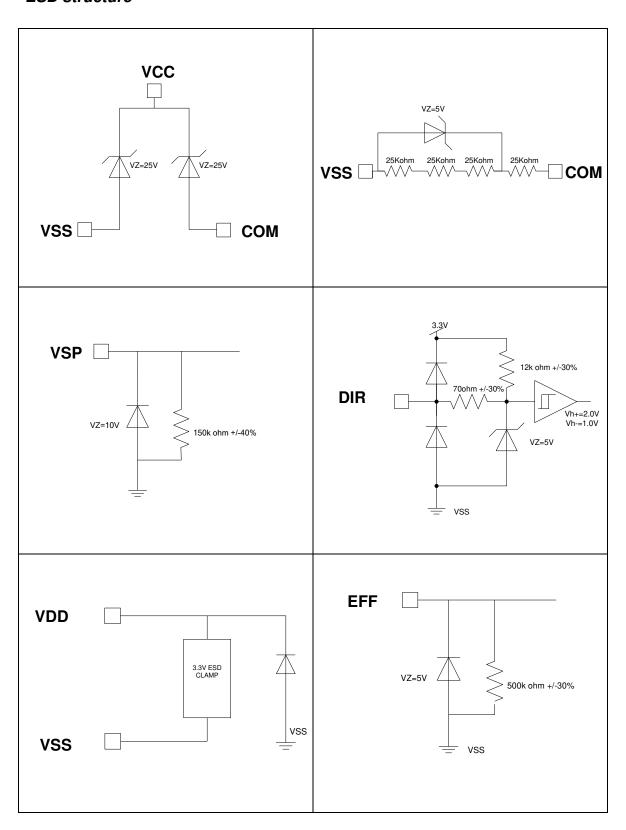

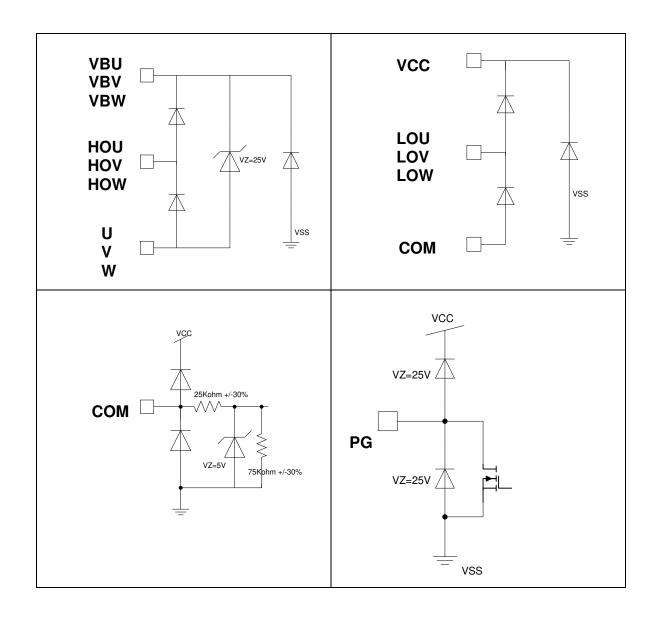

#### ESD structure

#### Recommended Operating Conditions

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to **VSS** unless otherwise stated in the table.

The input/output logic timing diagram is shown in Fig. 1.

The VS and VSS offset rating are tested with all supplies biased at a 15 V (VCC) differential / 3.3V (VDD).

Power up and down sequences are not dependent on the order of VCC, DCBUS, and VSP for proper operation to start or

| Symbol                           | Definition                                              | Min.               | Тур          | Max.               | Units | Condition                                                                                                    |

|----------------------------------|---------------------------------------------------------|--------------------|--------------|--------------------|-------|--------------------------------------------------------------------------------------------------------------|

| $V_U,V_V,V_W$                    | PWM output motor voltage <sup>1)</sup>                  | 100                | 320          | 450                | V     | IRDM983-025MB<br>IRDM983-035MB                                                                               |

| V <sub>PWMTR</sub>               | Transient PWM output motor voltage †1)                  | -50                | 0            | 500                |       | 50ns transient period                                                                                        |

|                                  |                                                         | -                  | 50           | -                  |       | Fc=20kHz, DCBUS=300V,<br>IO=140mArms, no heatsink,<br>Ta=40C, IRDM983-025MB                                  |

| Po                               | Output power <sup>1)</sup>                              | -                  | 60           | -                  | W     | Fc=20kHz, DCBUS=300V, IO=200mArms, no heatsink, Ta=40C, IRDM983-035MB                                        |

| VCC                              | Low side supply voltage                                 | 13.5 <sup>1)</sup> | 15           | 16.5 <sup>1)</sup> |       |                                                                                                              |

| V <sub>COM</sub>                 | COM-VSS voltage                                         | -5                 | 0            | 5                  |       |                                                                                                              |

| V <sub>HCOM</sub>                | Hall sensor input voltage<br>COMMON MODE                | 0.6                | -            | 2.9                |       |                                                                                                              |

| $V_{\text{DIR}}, V_{\text{EFF}}$ | Direction, Efficiency curve selection input pin voltage | 0                  | -            | VDD                | V     |                                                                                                              |

| $V_{PG}$                         | Open drain output motor evolution pulse                 | 0                  | -            | VCC                | V     |                                                                                                              |

| $V_{VSP}$                        | VSP input voltage                                       | 0                  | -            | 9.8                |       |                                                                                                              |

| VDD                              | 3.3V voltage regulator output                           | 3.0                | -            | 3.6                |       | lo=2mA                                                                                                       |

| VDDstby                          | 3.3V voltage regulator output when in stand by 1)       | 0                  | -            | 0.8                |       | VSP<1,15V for more than 5 s,<br>Cout=20pF                                                                    |

| I <sub>VDD</sub>                 | VDD current capability                                  | -                  | -            | 2                  | mA    | TW=1ms                                                                                                       |

| $C_{VDD}$                        | Capacitor at VDD                                        | 2.2                | -            | 22                 | uF    |                                                                                                              |

| FCRmax                           | Carrier frequency                                       | 23.3k              | 23.9k        | 24.5k              |       | $R_{CLKIN}$ =57.6K $\Omega$ , $C_{CLKIN}$ =270pF<br>$F_{CLKIN}$ =38.99kHz                                    |

| FCRtyp                           | Carrier frequency                                       | 18.1k              | 18.5k        | 18.9k              | Hz    | $R_{CLKIN}=75K\Omega$ , $C_{CLKIN}=270pF$<br>$F_{CLKIN}=30.31kHz$                                            |

| FCRmin                           | Carrier frequency                                       | 14.5k              | 14.7k        | 15.0k              |       | $R_{\text{CLKIN}}$ =95.3K $\Omega$ , $C_{\text{CLKIN}}$ =270pF<br>$F_{\text{CLKIN}}$ =24.07kHz               |

| R <sub>CLKIN</sub>               | Resistor for RC oscillator <sup>2)</sup>                | -                  | 75K<br>39.2K | -                  | Ω     | R=75kohm with C=270pF,<br>$C_{PCB}$ =0pF Fc=18.83kHz<br>R=75kohm with C=270pF,<br>$C_{PCB}$ =5pF Fc=18.50kHz |

| C <sub>CLKIN</sub>               | Capacitor for RC oscillator <sup>2)</sup>               | -                  | 270<br>470   | -                  | pF    | R=39.2kohm with C=470pF, $C_{PCB}$ =0pF Fc=20.75kHz R=39.2kohm with C=470pF, $C_{PCB}$ =5pF Fc=20.54kHz      |

| TA                               | Ambient temperature <sup>1)</sup>                       | -40                |              | 125                | °C    |                                                                                                              |

<sup>†</sup>Operational for transient negative VS of - 50 V with a 50 ns pulse width is guaranteed by design. Refer to the Application Information section of this datasheet for more details.

C<sub>PCB</sub>: Board layout capacitance

<sup>1)</sup> Guarantee by design, not tested at manufacturing

<sup>2)</sup> Carrier Frequency is calculated by the following. FC=1/(((R+50)  $\times$  (C+5 $\times$ 10<sup>-12</sup>+C<sub>PCB</sub>)+900 $\times$ 10<sup>-9</sup>) $\times$ 2.466)

#### Static Electrical Characteristics

$(V_{\text{CC}}\text{-COM}) = (V_{\text{B}}\text{-V}_{\text{S}}) = 15 \text{ V}$ . TA = 25°C unless otherwise specified. The VSP and IIN parameters are referenced to  $V_{\text{SS}}$  and are applicable to all six channels. The VO and IO parameters are referenced to respective  $V_{\text{S}}$  and COM and are applicable to the respective output leads HO or LO. The  $V_{\text{CCUV}}$  parameters are referenced to  $V_{\text{SS}}$ . The  $V_{\text{BSUV}}$  parameters are referenced to  $V_{\text{S}}$ .

| Symbol                                                                             | Definition                                                                                  | Min  | Тур  | Max               | Units | Test Conditions                     |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|-------------------|-------|-------------------------------------|

| IDSS                                                                               | DC bus to COM leakage current, IRDM983-035MB                                                | -    | 70   | 200               | uA    | DCBUS=500V,<br>Tj=25C,per device    |

|                                                                                    | DC bus to COM leakage current, IRDM983-025MB                                                | -    | 50   | 100               |       |                                     |

|                                                                                    | MOSFET body diode voltage, IRDM983-025MB                                                    | -    |      | 1.0 <sup>2)</sup> |       |                                     |

| VF                                                                                 | MOSFET body diode voltage, IRDM983-035MB                                                    | -    |      | 1.02)             |       | IF=1A                               |

| VDD                                                                                | VDD voltage                                                                                 | 3.0  | 3.3  | 3.6               |       | lo=2mA                              |

| VIH                                                                                | Logic "1" input voltage                                                                     | 2.5  | -    | -                 |       |                                     |

| VIL                                                                                | Logic "0" input voltage                                                                     | -    | -    | 0.8               |       |                                     |

| VSPstbylow                                                                         | Active to Standby mode VSP input negative going thresholds                                  | 1.05 | 1.15 | 1.25              |       |                                     |

| VSPstbyhigh                                                                        | Standby to Active mode VSP input positive going thresholds                                  | 1.3  | 1.4  | 1.5               | V     |                                     |

| VSPstbyhys                                                                         | Standby mode VSP hysteresis                                                                 | 0.1  | 0.25 | 0.4               |       |                                     |

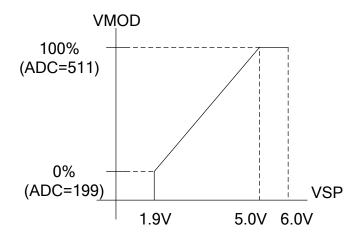

| VSPmin                                                                             | VSP 0%duty                                                                                  | 1.7  | 1.9  | 2.1               |       |                                     |

| VSPmax                                                                             | VSP 100%duty                                                                                | 4.8  | 5.0  | 5.2               |       |                                     |

| VSP6step<br>enter                                                                  | VSP voltage that ensures enter in 6 step mode                                               | 8.0  | 8.8  | 9.68              |       | 500 ms continuously above threshold |

| VSP6step exit                                                                      | VSP voltage that ensures exit from 6 step mode                                              | 8.0  | 8.8  | 9.68              |       | 200 ms continuously below threshold |

| $V_{HCOM}$                                                                         | Hall sensor input voltage COMMON MODE                                                       | 0.6  | 2    | 2.9               |       |                                     |

| $V_{HDIF}$                                                                         | Hall sensor input voltage DIFFERENTIAL MODE                                                 | 0.03 | 0.5  | 2.5               |       |                                     |

| $V_{NOG}$                                                                          | Hall sensor input OP amp open loop gain 1)                                                  | 60   | -    | 80                | dB    | Ta=-40 – 125C                       |

| $V_{HOO}$                                                                          | Hall sensor input OP amp offset1)                                                           | -    | 1    | -                 | mV    |                                     |

| V <sub>IHSTH</sub>                                                                 | Hall sensor input Schmitt Trigger input buffer hysteresis <sup>1)</sup>                     | -    | 1    | -                 |       |                                     |

| $V_{HST+}$                                                                         | Hall sensor input Digital Schmitt Trigger input buffer positive going voltage <sup>1)</sup> | -    | 2    | -                 |       |                                     |

| V <sub>HST-</sub>                                                                  | Hall sensor input Digital Schmitt Trigger input buffer negative going voltage <sup>1)</sup> | -    | 1    | -                 |       |                                     |

| V <sub>CLKIN,TH+</sub>                                                             | CLKIN positive going threshold                                                              | 2.5  | -    | -                 |       |                                     |

| $V_{\text{CLKIN,TH-}}$                                                             | CLKIN negative going threshold                                                              | -    | -    | 0.8               | V     |                                     |

| $V_{\text{CC,UVTH+}}$ $V_{\text{CC}}$ supply undervoltage positive going Threshold |                                                                                             | 8    | 8.9  | 9.8               |       |                                     |

| $V_{\text{CC,UVTH-}}$ $V_{\text{CC}}$ supply undervoltage negative going Threshold |                                                                                             | 7.4  | 8.2  | 9                 |       |                                     |

| V <sub>CC,UVHYS</sub> V <sub>CC</sub> supply undervoltage hysteresis               |                                                                                             | 0.3  | 0.7  | -                 |       |                                     |

| $V_{BS,UVTH+}$                                                                     | 11110011010                                                                                 |      | 8.9  | 9.8               |       |                                     |

| V <sub>BS, UVTH-</sub>                                                             | V <sub>BS</sub> supply undervoltage negative going<br>Threshold                             | 7.4  | 8.2  | 9                 | V     |                                     |

| $V_{BS,UVHYS}$                                                                     | V <sub>BS</sub> supply undervoltage hysteresis                                              | 0.3  | 0.7  | -                 |       |                                     |

## IRDM983-025MB, IRDM983-035MB

|                       |                                                           |      |      |      |        | ·                                    |

|-----------------------|-----------------------------------------------------------|------|------|------|--------|--------------------------------------|

| V <sub>ILIM1</sub>    | Current Limit Input voltage 1 3)                          | 450  | 520  | 590  |        | Tc<92C (+/-12C)                      |

| V <sub>ILIM2</sub>    | Current Limit Input voltage 2 3)                          | 300  | 375  | 450  | mV     | Tc=92<96C (+/-12C)                   |

| V <sub>ILIM3</sub>    | Current Limit Input voltage 3 3)                          | 200  | 250  | 300  |        | Tc=96<100C(+/-12C)                   |

| V <sub>ROCKILIM</sub> | Current Limit input voltage at Rotor Lock                 | 200  | 250  | 300  |        |                                      |

| V <sub>ILIMHYS</sub>  | Current Limit Input voltage hysteresis                    | -    | 60   | -    |        |                                      |

| T <sub>OT+</sub>      | Positive going over-temperature limit                     | 88   | 100  | 112  | °C     |                                      |

| T <sub>OT-</sub>      | Negative going over-temperature limit                     | 68   | 80   | 92   |        |                                      |

| TAC                   | Temp sensor absolute accuracy                             | 0    | -    | 12   |        |                                      |

| TES                   | Temp sensor resolution <sup>1)</sup>                      | 0    | -    | 3.25 |        |                                      |

| ICC                   | Vcc current                                               | -    | 13   | 24   | mA     |                                      |

| ICC <sub>STDBY</sub>  | Vcc current at standby                                    | -    | 0.10 | 0.20 |        |                                      |

| I <sub>VDD</sub>      | 3.3V output current                                       | -    | -    | 2    |        |                                      |

| $C_{VDD}$             | External capacitor for VDD <sup>1)</sup>                  | 2.2  | -    | 22   | uF     |                                      |

| PWM <sub>RES</sub>    | PWM pulse width resolution                                | -    | 500  | -    | Counts | 100ns resolution                     |

| MOD <sub>RESINT</sub> | Internal modulator amplitude resolution <sup>1)</sup>     | -    | 1686 | -    |        |                                      |

| Fc                    | PWM carrier frequency                                     | 19.6 | 20   | 20.4 | kHz    | CLKIN=32.768kHz                      |

| FXTAL                 | XTAL pin frequency <sup>1)</sup>                          | 29.6 | 30.3 | 30.9 |        | R=75kohm, C=270pF                    |

|                       |                                                           | 32.2 | 32.8 | 33.5 |        | R=40.2kohm,<br>C=470pF               |

| RBS                   | Ron internal bootstrap diode                              | -    | 220  | -    | Ω      | ·                                    |

| PD <sub>STBY</sub>    | Standby power dissipation                                 | -    | 1.5  | 3.0  | mW     | VSP<1.15V,<br>DCBUS=0V               |

| I <sub>DRV+</sub>     | Internal driver gate drive sourcing current <sup>1)</sup> |      | 6    |      |        | V <sub>DRV</sub> =0 V,PW ≤10 μs      |

| I <sub>DRV-</sub>     | Internal driver gate drive sinking current <sup>1)</sup>  | -    | 160  | -    | mA     | V <sub>DRV</sub> =15 V,<br>PW ≤10 μs |

| RON <sub>SPDFBK</sub> | Ron of SPDFBK pin                                         | -    | 50   | 100  | Ω      |                                      |

|                       |                                                           | -    | 3    | -    |        | IRDM983-025MB                        |

| Rthj-c                | Thermal resistance, junction to case <sup>1)</sup>        | -    | 2    | -    | °C /W  | IRDM983-035MB                        |

<sup>1)</sup> Guaranteed by design, not tested at manufacturing

<sup>2)</sup> Tested at wafer probe

<sup>3)</sup> V<sub>ILIM1,2,3</sub> thresholds are tested at 25 degC. Temperature range is based on characterization only.

### **Dynamic Electrical Characteristics**

$V_{CC}$ =  $V_B$  = 15 V,  $V_S$  =  $V_{SS}$  = COM,  $T_A$  = 25°C, and  $C_L$  = 1000 pF unless otherwise specified.

| Symbol                   | Definition                                               | Min   | Тур   | Max  | Units | Test Conditions                                                                        |

|--------------------------|----------------------------------------------------------|-------|-------|------|-------|----------------------------------------------------------------------------------------|

|                          |                                                          | -     | 3     | -    | Α     | RDM983-025MB, $T_J$ =25°C,<br>$t_{SC}$ <20 $\mu$ s<br>$V^+$ = 320V, $V_{CC}$ =15V      |

| Icsc                     | Short Circuit Drain Current <sup>1)</sup>                | -     | 5     | -    |       | RDM983-035MB, $T_J$ =25°C, $t_{SC}$ <20 $\mu$ s   V <sup>+</sup> = 320V, $V_{CC}$ =15V |

| SCSOA                    | Short Circuit duration period <sup>1)</sup>              | 20000 | -     | -    | ns    | $V^+$ = 300V(IRDM983-025MB,-35MB), $V_{CC}$ =+15V to 0V, line to line short            |

| $t_{RR}$                 | Reverse recovery time 1)                                 | -     | 80    | -    | ns    | ID=1A, di/dt=100A/us                                                                   |

| t <sub>ILIM</sub>        | ILIM to PWM current limit propagation delay              | -     | 3000  | -    | ns    | C <sub>LOAD</sub> = 1nF, F <sub>CLKIN</sub> =32.768kHz                                 |

|                          |                                                          | 500   | 1000  | 1700 |       | VILIM=2V, Ta=25C                                                                       |

| t <sub>ILIMFIL</sub>     | ILIM filter time <sup>1)</sup>                           | 400   | 800   | 1400 |       | VILIM=2V, Ta=125C                                                                      |

|                          |                                                          | 600   | 1200  | 2000 | ns    | VILIM=2V, Ta=-40C                                                                      |

| t <sub>HFILA</sub>       | Hall differential input analog filter1)                  | -     | 1500  | -    | 110   |                                                                                        |

| t <sub>HFILD</sub>       | Hall input digital filter delay <sup>1)</sup>            | -     | 2500  | -    |       | F <sub>CLKIN</sub> =32.768kHz                                                          |

| t <sub>HALLSAT</sub>     | HALL input response time from saturation <sup>1)</sup>   | -     | 5000  | -    |       |                                                                                        |

| t <sub>HALLPG</sub>      | HALL input to PG output propagation delay                | -     | 5000  | -    |       | F <sub>CLKIN</sub> =32.768kHz                                                          |

| tvspact                  | VSP standby to PWM active time                           | 14.0  | 17.5  | 22.0 | ms    | CVDD=2.2uF, VSP=0→5.4V, F <sub>CLKIN</sub> =32.768kHz                                  |

| T <sub>VSPONDELAY</sub>  | VSP active to PWM duty active                            | 2.0   | 3.5   | 5.0  |       | VSP from 1.8V to 2.6V,<br>F <sub>CLKIN</sub> =32.768kHz                                |

| t <sub>VDDHOLD</sub>     | VDD hold time at standby <sup>1)</sup>                   | 4.9   | 5.0   | 5.1  | S     | CVDD=2.2uF, VSP=2→0V,<br>F <sub>CLKIN</sub> =32.768kHz                                 |

| t <sub>RLOCKDETECT</sub> | Rotor Lock detect time <sup>1)</sup>                     | 4.9   | 5     | 5.1  | 3     | VSP>2.1V,  Elec freq <3Hz,  F <sub>CLKIN</sub> =32.768kHz                              |

| DT                       | Deadtime                                                 | -     | 1000  | -    |       | F <sub>CLKIN</sub> =32.768kHz                                                          |

| $PW_{HIN}$               | Internal high side minimum pulse width                   | -     | 400   | -    | ns    | Not a final output of a part , F <sub>CLKIN</sub> =32.768kHz                           |

| $PW_{LIN}$               | Internal low side minimum pulse width                    | -     | 100   | -    |       | Not a final output of a part , F <sub>CLKIN</sub> =32.768kHz                           |

| SPD <sub>OVER</sub>      | Over speed <sup>1)</sup>                                 | -     | 200   | -    |       | F <sub>CLKIN</sub> =32.768kHz                                                          |

| SPD <sub>PWMCHG</sub>    | Block commutation to sine PWM change speed <sup>1)</sup> | -     | 3     | -    | Hz    | 1 consecutive electrical angle update period, F <sub>CLKIN</sub> =32.768kHz            |

| SPD <sub>EFF1</sub>      | EFF bending point 1 speed <sup>1)</sup>                  | -     | 33.33 | -    |       | F <sub>CLKIN</sub> =32.768kHz                                                          |

| SPD <sub>EFF2</sub>      | EFF bending point 2 speed <sup>1)</sup>                  | -     | 83.33 | -    |       | F <sub>CLKIN</sub> =32.768kHz                                                          |

<sup>1)</sup> Guaranteed by design, not tested at manufacturing

### Figures of Input Circuit and Table

The following Figure shows the interconnect bonding among the HVIC and MOSFETs within a package.

Figure 11 Connection diagram of VSS/COM and power pins/pads

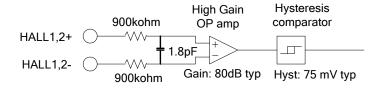

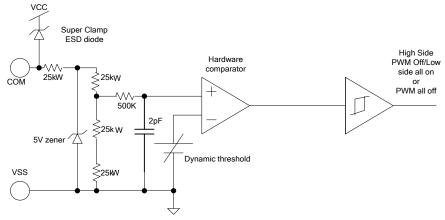

The following Figures show the VSP input mapping, the Hall sensor input circuit, and the ISENSE pin input filter circuit.

Figure 12 VSP Range and Thresholds

Figure 13 Hall sensor input circuit

Figure 14 COM pin current limit comparator and analog filter

### **Load Curves**

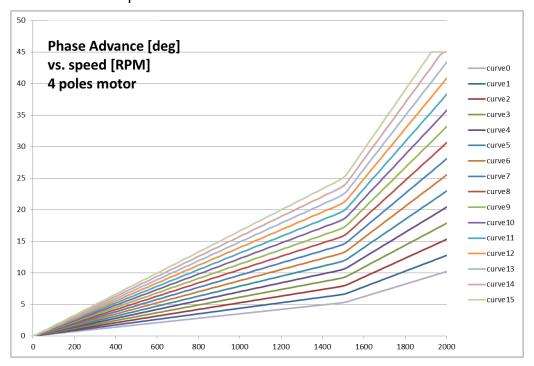

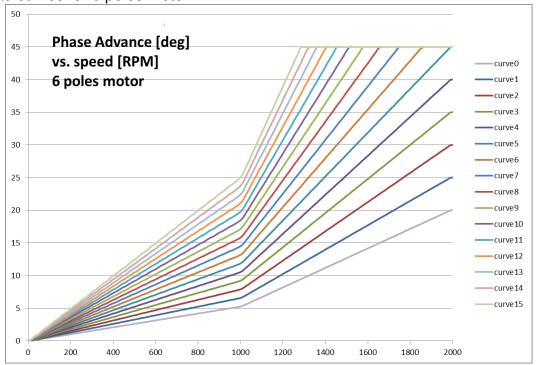

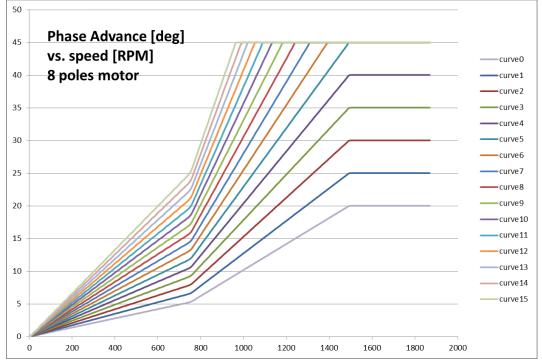

The following Table shows EFF pin mapping between input voltage and the advanced angle in degree per 50Hz of fundamental electrical frequency. Phase advance is by design clamped to be lower than 45 degrees at every frequency. At frequencies above 100 Hz the advancement is constant and it is kept to the same value at 100Hz.

| Select      | Degree/50Hz | Frequency [Hz] @ advance=45deg | EFF input       | EFF digital input |

|-------------|-------------|--------------------------------|-----------------|-------------------|

| 15          | 25.49       | 64.22                          | 3.094V - 3.300V | 152               |

| 14          | 24.15       | 65.75                          | 2.888V - 3.087V | 144               |

| 13          | 22.81       | 68.04                          | 2.681V - 2.881V | 136               |

| 12          | 21.47       | 70.34                          | 2.475V - 2.675V | 128               |

| 11          | 20.12       | 72.63                          | 2.269V - 2.469V | 120               |

| 10          | 18.78       | 75.69                          | 2.063V - 2.262V | 112               |

| 9           | 17.44       | 78.75                          | 1.856V - 2.056V | 104               |

| 8           | 16.10       | 81.80                          | 1.650V - 1.850V | 96                |

| 7           | 14.76       | 87.16                          | 1.444V - 1.644V | 88                |

| 6           | 13.42       | 92.51                          | 1.238V - 1.437V | 80                |

| 5           | 12.07       | 99.39                          | 1.031V - 1.231V | 72                |

| 4           | 10.73       | Advance=40deg<br>above 100Hz   | 0.825V – 1.025V | 64                |

| 3           | 9.39        | Advance=35deg<br>above 100Hz   | 0.619V - 0.819V | 56                |

| 2           | 8.05        | Advance=30deg<br>above 100Hz   | 0.413V - 0.612V | 48                |

| 1           | 6.71        | Advance=25deg<br>above 100Hz   | 0.206V - 0.406V | 40                |

| Default = 0 | 5.37        | Advance=20deg<br>above 100Hz   | 0.000V – 0.200V | 32                |

Table 2a EFF Parameters Selection

#### Load curves for 4 poles motor

Load curves for 6 poles motor

Load curves for 8 poles motor

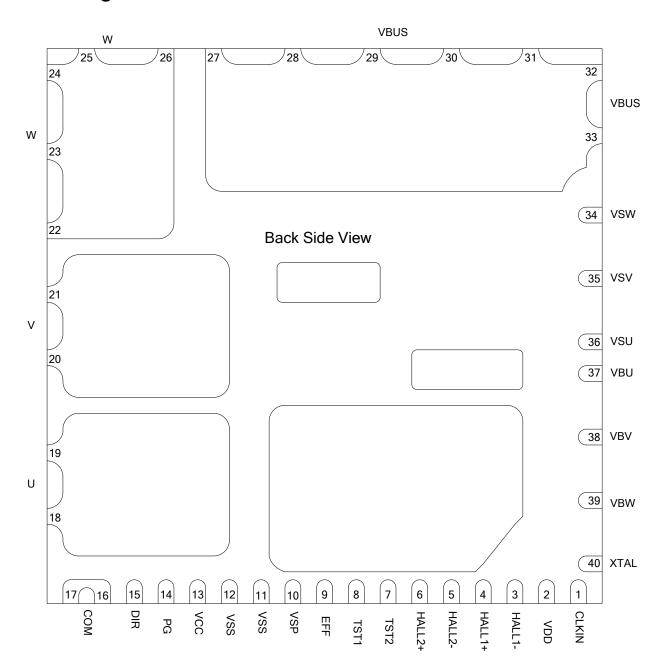

### **Lead Definitions**

| Symbol       | Pin#                                                             | Description                                                                                                                                                                             |  |  |

|--------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VSP          | 10                                                               | Voltage Set Point analog input. Provides the value of the PWM modulation index to the controller.                                                                                       |  |  |

| <b>PG</b> 14 |                                                                  | Provides speed feedback to through pulses per revolution. It is an open drain output 15V tolerant.  Output is a square wave of a 3 pulses per electrical cycle of fundamental frequency |  |  |

| DIR          | 15                                                               | Motor Direction Input (internally pulled up high = $U\rightarrow V\rightarrow W$ )                                                                                                      |  |  |

| EFF          | 9                                                                | Load curve selection parameter Input for efficiency improvement                                                                                                                         |  |  |

| XTAL         | 40                                                               | Clock buffer output                                                                                                                                                                     |  |  |

| CLKIN        | 1                                                                | Clock buffer input                                                                                                                                                                      |  |  |

| VSS          | 11                                                               | Logic ground                                                                                                                                                                            |  |  |

| СОМ          | 16,17                                                            | Analog input ITRIP and Power Ground and Low side MOSFET cource                                                                                                                          |  |  |

| vcc          | 13                                                               | 15V supply voltage                                                                                                                                                                      |  |  |

| HALL1+       | 4                                                                | Hall sensor 1 positive input                                                                                                                                                            |  |  |

| HALL1-       | 3                                                                | Hall sensor 1 negative input                                                                                                                                                            |  |  |

| HALL2+       | 6                                                                | Hall sensor 2 positive input                                                                                                                                                            |  |  |

| HALL2-       | 5                                                                | Hall sensor 2 negative input                                                                                                                                                            |  |  |

| TST1         | 8 Pin for factory testing – connect to VDD in normal application |                                                                                                                                                                                         |  |  |

| TST2         | Fin for factory testing – connect to VSS in normal application   |                                                                                                                                                                                         |  |  |

| VDD          | 2                                                                | 3.3V output                                                                                                                                                                             |  |  |

| U            | 18,19                                                            | U phase output                                                                                                                                                                          |  |  |

| ٧            | 20,21                                                            | V phase output                                                                                                                                                                          |  |  |

| w            | 22,23,24,<br>25,26                                               | W phase output                                                                                                                                                                          |  |  |

| VBU          | 37                                                               | Phase U High side Bootstrap capacitor positive                                                                                                                                          |  |  |

| VBV          | 38                                                               | Phase V High side Bootstrap capacitor positive                                                                                                                                          |  |  |

| VBW          | 39                                                               | Phase W High side Bootstrap capacitor positive                                                                                                                                          |  |  |

| vsu          | 36                                                               | Phase U High side Bootstrap capacitor negative                                                                                                                                          |  |  |

| VSV          | 35                                                               | Phase V High side Bootstrap capacitor negative                                                                                                                                          |  |  |

| VSW          | 34                                                               | Phase W High side Bootstrap capacitor negative                                                                                                                                          |  |  |

| DCBUS        | 27,28,29,<br>30,31,32,<br>33                                     | DC Bus voltage                                                                                                                                                                          |  |  |

# **Lead Assignments**

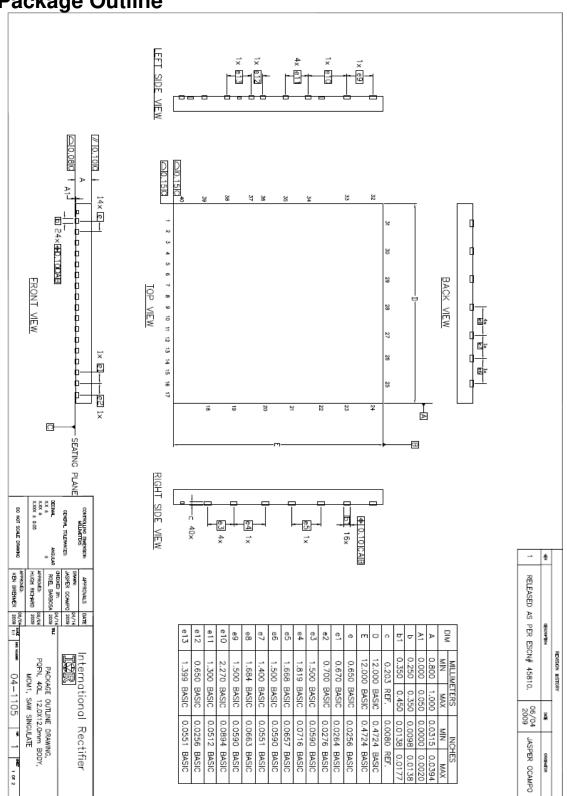

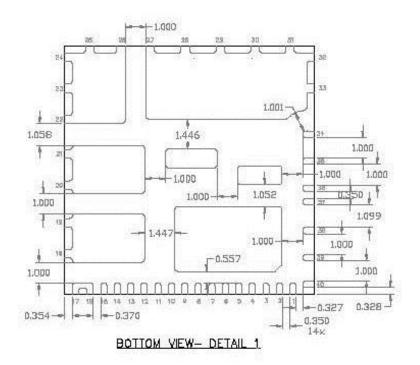

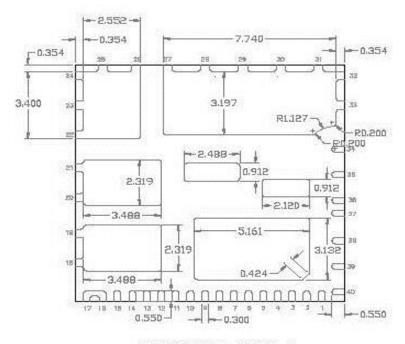

**Package Outline**

BOTTOM VIEW- DETAIL 2

Dimension in mm<sup>2</sup>

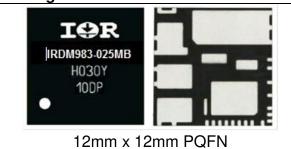

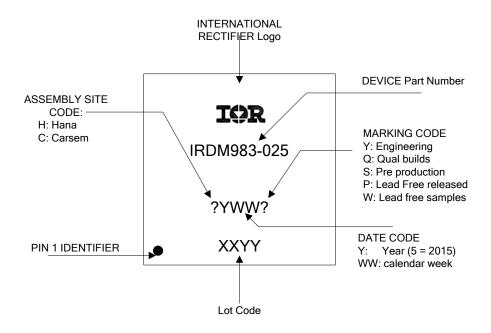

# **Package Marking**

| Part number   | Internal MOSFET |

|---------------|-----------------|

| IRDM983-025MB | 500V 2A         |

| IRDM983-035MB | 500V 3A         |