Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

January 16, 2009 Datasheet No. - PD97375

## **IRS21956S**

## Floating Input, High and Low(Dual mode) Side Driver

#### **Features**

- Low side programmable ramp gate drive

- Low side generic gate drive integrated using the same low side output pin

- High side generic gate driver

- Under voltage lockout for VDD, VCC & VBS

- Floating 5V input logic compatible

- Tolerant to negative transient voltage on Vs

- Shoot through prevention

- RoHS compliant

**Product Summary**

| Topology                                     | PDP           |

|----------------------------------------------|---------------|

| V <sub>OFFSET</sub>                          | ≤ 600 V       |

| LO SR <sub>+</sub>                           | 4.5V/us       |

| I <sub>o+</sub> & I <sub>o-</sub> (typical)  | 0.5A & 0.5A   |

| t <sub>ON</sub> & t <sub>OFF</sub> (typical) | 300ns & 280ns |

**Package Options**

| Table of Contents                           | Page |

|---------------------------------------------|------|

| Description                                 | 3    |

| Simplified Block Diagram                    | 4    |

| Typical Application Diagram                 | 5    |

| Qualification Information                   | 7    |

| Absolute Maximum Ratings                    | 8    |

| Recommended Operating Conditions            | 8    |

| Static Electrical Characteristics           | 9    |

| DV / Linear (Stepwise) Mode                 | 10   |

| Dynamic Electrical Characteristics          | 10   |

| Timing Diagram and logic truth table        | 11   |

| Input/Output Pin Equivalent Circuit Diagram | 16   |

| Lead Definitions                            | 17   |

| Lead Assignments                            | 18   |

| Package Details                             | 19   |

| Tape and Reel Details                       | 20   |

| Part Marking Information                    | 21   |

| Ordering Information                        | 22   |

Not recommended for new designs. No replacement is available International IRS21956S

## Description

The IRS21956 is high voltage and programmable ramp slope control gate driver for MOSFET and IGBT with single low side dual mode driver, high side driver and floating 5V input. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The floating logic input is compatible with standard 5V CMOS or LSTTL output. The output driver features a programmable slope control by external R/C and input signals. The floating channels can be used to drive an N-channel power MOSFET or IGBT in the high side configuration, which operates up to 600 volts above the COM ground.

www.irf.com © 2008 International Rectifier

**IRS21956S**

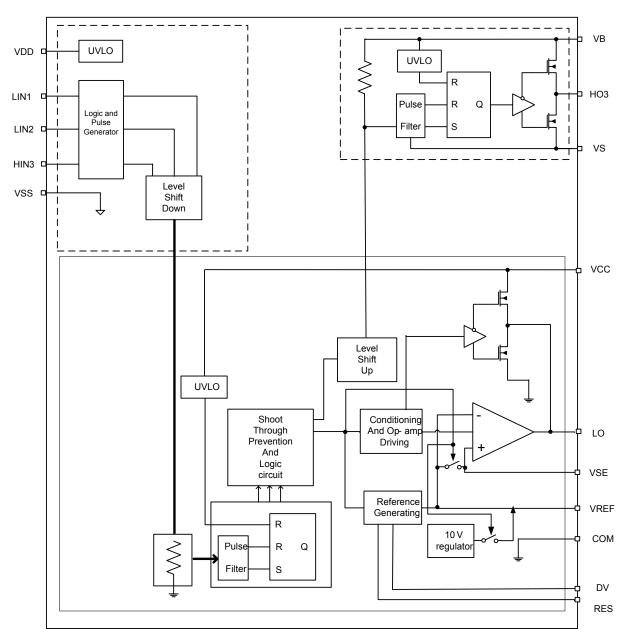

## **Simplified Block Diagram**

www.irf.com © 2008 International Rectifier 4

**IRS21956S**

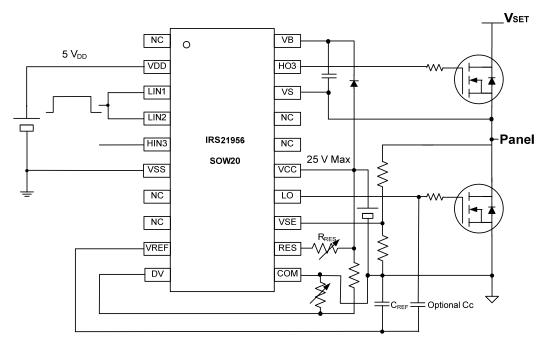

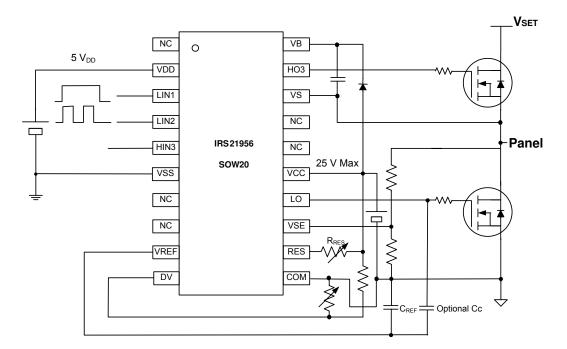

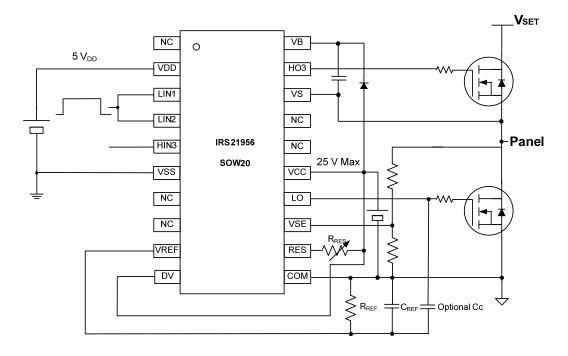

# **Typical Connection Diagram**

### A) Linear Ramp driver's connection diagram

### B) Stepwise linear Ramp driver's connection diagram

### C) Exponential Ramp driver's connection diagram

Not recommended for new designs. No replacement is available International

IOR Rectifier

**IRS21956S**

## Qualification Information<sup>†</sup>

|                            |                   |                                                                                                                                                                     | Industrial <sup>††</sup>                               |  |  |

|----------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|

| Qualification Level        |                   | Comments: This family of ICs has passed JEDEC's Industrial qualification. IR's Consumer qualification level is granted by extension of the higher Industrial level. |                                                        |  |  |

| Moisture Sensitivity Level |                   | SOIC20W                                                                                                                                                             | MSL3 <sup>†††</sup> 260°C<br>(per IPC/JEDEC J-STD-020) |  |  |

|                            | Machine Model     | Class B                                                                                                                                                             |                                                        |  |  |

| ESD                        | Waciline Woder    | (per JEDEC standard JESD22-A115)                                                                                                                                    |                                                        |  |  |

| LSD                        | Human Body Model  |                                                                                                                                                                     | Class 2                                                |  |  |

|                            | Tiuman Body Model | (per EIA/JEDEC standard EIA/JESD22-A114)                                                                                                                            |                                                        |  |  |

| IC Latch-Up Test           |                   | Class I, Level A                                                                                                                                                    |                                                        |  |  |

|                            |                   | (per JESD78)                                                                                                                                                        |                                                        |  |  |

| RoHS Compliant             |                   |                                                                                                                                                                     | Yes                                                    |  |  |

- Qualification standards can be found at International Rectifier's web site http://www.irf.com/

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

© 2008 International Rectifier www.irf.com 7

TOR Rectifier

# **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All

voltage parameters are absolute voltages referenced to COM.

| Symbol               | Definition                                                        | Min                  | Max                  | Units |

|----------------------|-------------------------------------------------------------------|----------------------|----------------------|-------|

| V <sub>DD</sub>      | Floating Input Supply Voltage                                     | -0.3                 | 625                  | V     |

| $V_{SS}$             | Floating Input Supply Return Voltage                              | V <sub>DD</sub> -25  | V <sub>DD</sub> +0.3 | V     |

| $V_{IN}$             | Logic input voltage (LIN1,LIN2,HIN3)                              | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| V <sub>CC</sub>      | Low side supply voltage                                           | -0.3                 | 25                   | V     |

| $V_{DV}, V_{VREF}$   | Low side inputs voltage                                           | COM-0.3              | V <sub>CC</sub> +0.3 | V     |

| $V_{VSE}, V_{RES}$   | Low side inputs voltage                                           | COM-0.3              | V <sub>CC</sub> +0.3 | V     |

| $V_{LO}$             | Low side gate drive output voltage                                | COM-0.3              | V <sub>CC</sub> +0.3 | V     |

| $V_{B}$              | High side floating well supply voltage                            | -0.3                 | 625                  | V     |

| Vs                   | High side floating well supply return voltage                     | V <sub>B</sub> -25   | V <sub>B</sub> +0.3  | V     |

| $V_{HO}$             | Floating gate drive output voltage                                | V <sub>S</sub> -0.3  | V <sub>B</sub> +0.3  | V     |

| dV <sub>SS</sub> /dt | Allowable V <sub>SS</sub> offset supply transient relative to COM | -                    | 50                   | V/ns  |

| dV <sub>S</sub> /dt  | Allowable V <sub>S</sub> offset supply transient relative to COM  | -                    | 50                   | V/ns  |

| P <sub>D</sub>       | Package Power Dissipation @ T <sub>A</sub> <=+25°C                | -                    | 1.0                  | W     |

| R <sub>θ</sub> JA    | Thermal Resistance, Junction to Ambient                           | -                    | 120                  | °C/W  |

| T <sub>J</sub>       | Junction Temperature                                              | -55                  | 150                  | °C    |

| Ts                   | Storage Temperature                                               | -55                  | 150                  | °C    |

| T <sub>L</sub>       | Lead temperature (Soldering, 10 seconds)                          | -                    | 300                  | °C    |

## **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM.

The offset rating are tested with supplies of  $(V_{CC}-COM) = (V_B-V_S)=15V$ .

| Symbol                 | Definition                                    | Min                  | Max                | Units |

|------------------------|-----------------------------------------------|----------------------|--------------------|-------|

| $V_{DD}$               | Floating Input Supply voltage                 | V <sub>SS</sub> +4.5 | V <sub>SS</sub> +6 | V     |

| $V_{SS}$               | Floating Input Supply offset voltage          | -0.3                 | 600                | V     |

| $V_{IN}$               | LIN1, LIN2, HIN3 input voltage                | $V_{SS}$             | $V_{DD}$           | V     |

| $V_{CC}$               | Low side supply voltage                       | 10                   | 20                 | V     |

| $V_{LO}$               | Low side gate drive output voltage            | COM                  | $V_{CC}$           | V     |

| $V_{RES}$              | RES input voltage                             | COM                  | $V_{CC}$           | V     |

| $V_{DV}$               | DV input voltage                              | COM                  | $V_{CC}$           | V     |

| V <sub>VREF, VSE</sub> | VREF and VSE input voltage                    | COM                  | V <sub>CC</sub> -3 | V     |

| $V_{B}$                | High side floating well supply voltage        | V <sub>S</sub> +10   | V <sub>S</sub> +20 | V     |

| Vs                     | High side floating well supply offset voltage | Note2††              | 600                | V     |

| $V_{HO}$               | Floating gate drive output voltage            | Vs                   | $V_B$              | V     |

| T <sub>A</sub>         | Ambient Temperature                           | -40                  | 125                | °C    |

$<sup>\</sup>dagger$  V<sub>S</sub> and V<sub>B</sub> voltages will be tolerant to short negative transient spikes. These will be defined and specified in the future.

<sup>††</sup> Logic operation for Vs of -5 to 600V. Logic state held for Vs of -5V to  $-V_{BS}$ . (Please refer to Design Tip DT97-3 for more details).

#### **Static Electrical Characteristics**

$(V_{CC}\text{-COM}) = (V_B\text{-}V_S) = 15\text{V}$ . TA = 25°C. The VIN, VIN TH and IIN parameters are referenced to  $V_{SS}$ . The Vo and Io parameters are referenced to respective VS, COM and are applicable to the respective output leads HO3, LO. The  $V_{CCUV}$  parameters are referenced to COM. The  $V_{BSUV}$  parameters are referenced to  $V_S$ . The  $V_{DDUV}$  parameters are referenced to  $V_{SS}$ .

| Symbol                       | Definition                                                   | Min | Тур | Max | Units | Test Conditions                                                       |

|------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|-----------------------------------------------------------------------|

| V <sub>DDUV</sub> +          | V <sub>DD</sub> supply undervoltage positive going threshold |     | 4.0 |     |       |                                                                       |

| $V_{\text{DDUV}}$            | V <sub>DD</sub> supply undervoltage negative going threshold |     | 3.9 |     |       |                                                                       |

| V <sub>CCUV</sub> +          | V <sub>CC</sub> supply undervoltage positive going threshold | 7.8 | 8.7 | 9.6 | V     |                                                                       |

| V <sub>CCUV</sub> -          | V <sub>CC</sub> supply undervoltage negative going threshold | 7.2 | 8.0 | 8.8 | V     |                                                                       |

| $V_{BSUV}$ +                 | V <sub>BS</sub> supply undervoltage positive going threshold | 7.8 | 8.7 | 9.6 |       |                                                                       |

| $V_{BSUV}$                   | V <sub>BS</sub> supply undervoltage negative going threshold | 7.2 | 8.0 | 8.8 |       |                                                                       |

| I <sub>LK1</sub>             | High side floating well offset supply leakage current        |     |     | 50  |       | V <sub>B</sub> = V <sub>S</sub> = 600V                                |

| I <sub>LK2</sub>             | High side floating well offset supply leakage current        |     |     | 50  | uA    | V <sub>DD</sub> = V <sub>SS</sub> = 300V                              |

| $I_{QDD}$                    | Quiescent VDD supply current                                 |     | 145 | 250 | uA    | IN1, 2, 3 = 0Vor 5V                                                   |

| $I_{QBS}$                    | Quiescent VBS supply current                                 |     | 65  | 120 | uA    | HIN3 = 5V or 0V                                                       |

| Iqcc                         | Quiescent VCC supply current                                 |     | 1   | 1.5 | mA    | LIN1, 2 = 0V,<br>RES=130kohm                                          |

| IQCC                         | Quiescent voo supply current                                 |     | 5   | 7   | mA    | LIN1, 2 = 5V,<br>RES=130kohm                                          |

| V <sub>IH</sub>              | Logic "1" input voltage                                      | 3.5 |     |     |       |                                                                       |

| VIL                          | Logic "0" input voltage                                      |     |     | 0.8 | V     |                                                                       |

| lın+                         | Logic "1" input bias current                                 |     | 5   |     |       | VIN= 5V                                                               |

| lin-                         | Logic "0" input bias current                                 |     | 0   |     | uA    | V <sub>IN</sub> = 0V                                                  |

| lo+_<br>HO3, LO              | Output high short circuit pulsed current                     |     | 0.5 |     |       | Vo=15V,Vin=5V,<br>PW<=10us                                            |

| <b>lo</b><br>HO3, LO         | Output low short circuit pulsed current                      |     | 0.5 |     | Α     | Vo=0V,Vin=0V,<br>PW<=10us                                             |

| V <sub>OL</sub> _<br>HO3, LO | Low level output voltage                                     |     | 35  | 150 | mV    | lo=2mA                                                                |

| V <sub>OH</sub> _<br>HO3, LO | High level output voltage, Vbias-Vo                          |     | 15  | 80  | IIIV  | lo=2mA                                                                |

| DV exp+                      | Positive DV input threshold for exponential ramp             |     | 10  |     | V     | C <sub>REF</sub> =1nF, V <sub>SE</sub> open R <sub>RES</sub><br>=130K |

IOR Rectifier

IRS21956S

## DV / Linear (Stepwise) Mode

| Symbol | Definition                | Min  | Тур | Max  | Units | Test Conditions                                          |

|--------|---------------------------|------|-----|------|-------|----------------------------------------------------------|

| VREF,  | VREF. DV reference valled |      | 0.5 | 0.6  | V     | DV=500mV, $C_{REF}$ =1nF, $V_{SE}$ open $R_{RES}$ =130K, |

| hold   | DV reference voltage      | 2.82 | 3   | 3.18 | V     | DV=3V, $C_{REF}$ =1nF, $V_{SE}$ open $R_{RES}$ =130K,    |

## **Dynamic Electrical Characteristics**

$(V_{CC}\text{-COM})=(V_B\text{-}V_S)=15V$ . TA = 25°C. C<sub>L</sub> = 1000pF unless otherwise specified. All parameters are reference to COM.

| Symbol                 | Definition                               | Min | Тур | Max | Units | Test Conditions                                                                                                     |

|------------------------|------------------------------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------------------------------------------|

| Internal C             | perational Amplifier Characteristic      |     |     |     |       |                                                                                                                     |

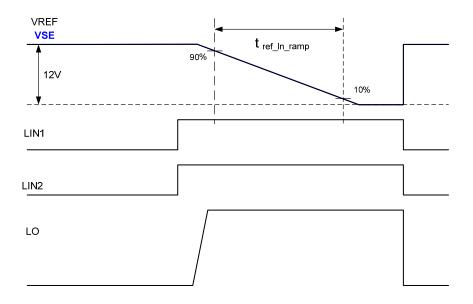

| t ref_In_ramp          | Linear ramp reference 10% to 90%         | 130 | 190 | 250 | μs    | $C_{REF}$ =1nF, $V_{SE}$ open $R_{RES}$ =130K, $V_{DV}$ =COM                                                        |

| Gm                     | OTA transconductance                     |     | 12  |     | mS    | $CL_LO=1nF$ , $V_{DV}=V_{CC}$ , $R_{RES}=130K$ , dc bias 5V                                                         |

| G <sub>open loop</sub> | Open loop gain                           | 45  | 60  |     | dB    | $Cc = 1nF$ , $V_{DV} = V_{CC}$ , $R_{RES} = 130K$                                                                   |

| BW <sub>SS</sub>       | Small signal bandwidth                   |     | 3.5 |     | MHz   | $ \begin{array}{c} \text{Cc =1nF} \ \ V_{\text{DV}} = V_{\text{CC}}, \\ R_{\text{RES}} = 130 \text{K} \end{array} $ |

| Vos                    | Input offset voltage                     |     | 20  |     | mV    | $V_{DV} = V_{CC}$ , $R_{RES} = 130$ K                                                                               |

| LO <sub>SR+</sub>      | Output positive slew rate                |     | 4.5 |     | V/µs  | $CL_LO=1nF, V_{DV}=V_{CC,}$<br>$R_{RES}=130K$                                                                       |

| CMRR                   | Common mode rejection ratio              | 55  | 65  |     | dB    | $V_{DV} = V_{CC}$ , $R_{RES} = 130$ K                                                                               |

| PSRR                   | Power supply rejection ratio             | 55  | 65  |     | dB    | $V_{DV} = V_{CC}$ , $R_{RES} = 130$ K                                                                               |

| Propagat               | ion Delay Characteristics                |     |     |     |       |                                                                                                                     |

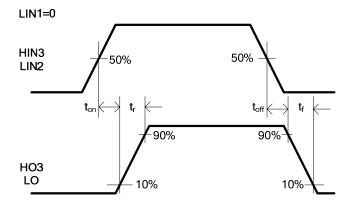

| t on                   | Turn-on delay (HO3, LO)                  |     | 300 | 400 |       |                                                                                                                     |

| t off                  | Turn-off delay (HO3, LO)                 |     | 280 | 380 | 1     |                                                                                                                     |

| t <sub>r</sub>         | Turn-on rise from 10% to 90%             |     | 25  | 60  | ns    | Gate Drive Mode                                                                                                     |

| t <sub>f</sub>         | Turn-off fall from 90% to 10%            |     | 15  | 40  |       | C <sub>L</sub> =1nF                                                                                                 |

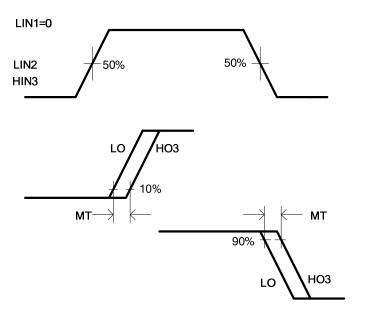

| MT                     | Delay matching, HO3 & LO turn-<br>on/off |     |     | 50  |       |                                                                                                                     |

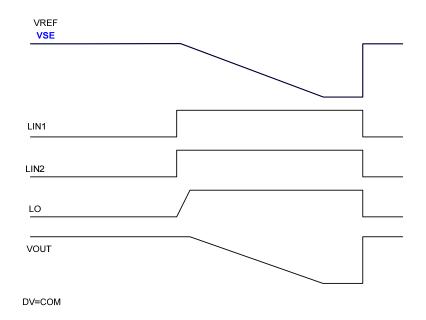

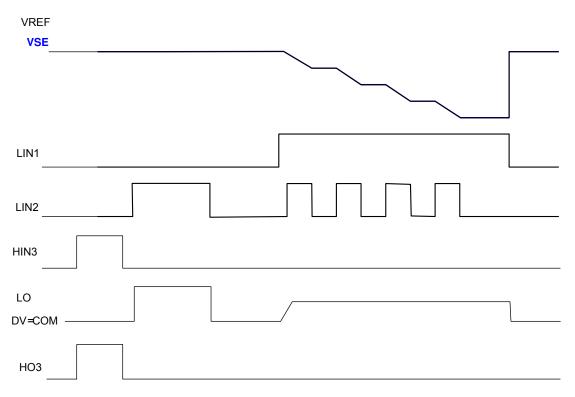

Figure 1A1 Input/Output Timing Diagram: Linear Ramp

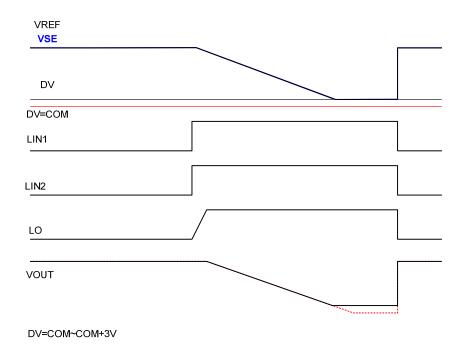

Figure 1A2 Input/Output Timing Diagram: Linear Ramp with voltage difference

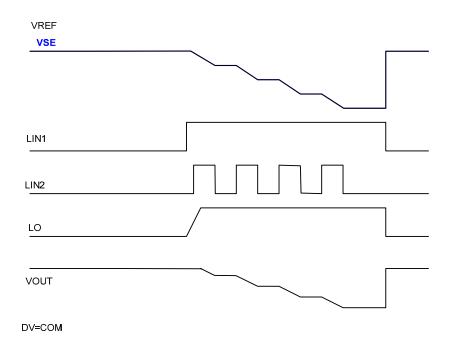

Figure 1B Input/Output Timing Diagram: Stepwise linear Ramp

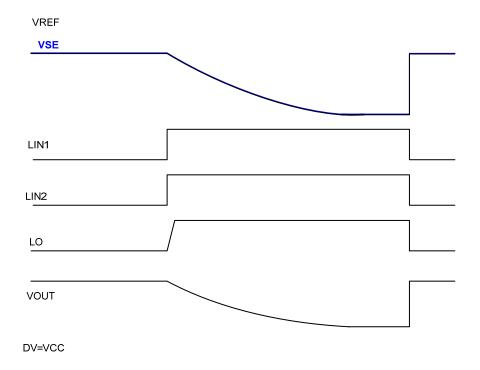

Figure 1C Input/Output Timing Diagram: Exponential Ramp

Not recommended for new designs. No replacement is available

International

TOR Rectifier

**IRS21956S**

Figure 1D Input/Output Timing Diagram: LO/HO3 outputs

## **Logic Truth Table**

| LIN1 | LIN2      | HIN3 | HO3 | OTA of LO                           | Gate driver of LO    |

|------|-----------|------|-----|-------------------------------------|----------------------|

| 0    | 0         | 0    | 0   | High impedance (HIZ)                | 0                    |

| 0    | 0         | 1    | 1   | High impedance (HIZ)                | 0                    |

| 0    | 1         | 0    | 0   | High impedance (HIZ)                | 1                    |

| 0    | 1         | 1    | 0   | High impedance (HIZ)                | 0                    |

| 1    | 1         | 0    | 0   | Linear/Exp ramp<br>depend on DV pin | High impedance (HIZ) |

| 1    | 1         | 1    | 0   | High impedance (HIZ)                | 0                    |

| 1    | Step(0/1) | 0    | 0   | Stepwise linear if DV pin is COM    | High impedance (HIZ) |

| 1    | Step(0/1) | 1    | 0   | High impedance (HIZ)                | 0                    |

Figure 2 Timing Definitions of V<sub>REF</sub>

Figure 3 Switching Time Waveform Definitions of LO and HO3

**IRS21956S**

**Figure 4 Delay Matching Waveform Definitions**

**IRS21956S**

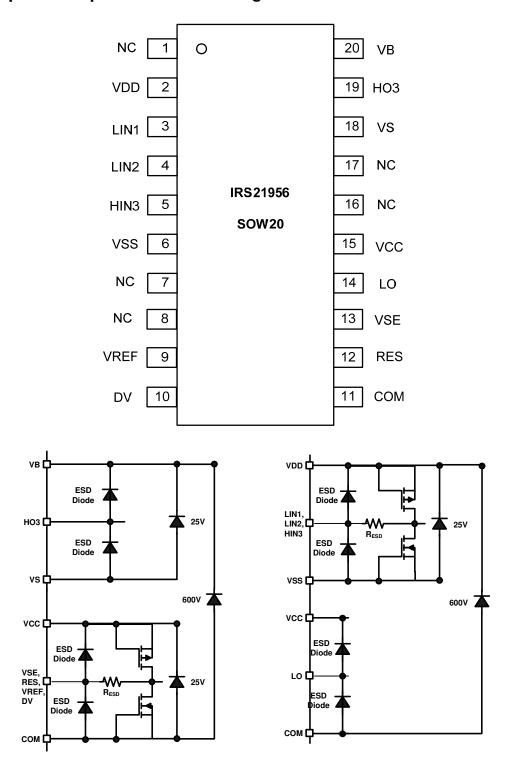

## Input/Output Pin Equivalent Circuit Diagram

## **Lead Definitions**

| PIN# | Symbol | Description                                                   |

|------|--------|---------------------------------------------------------------|

| 1    | NC     | No Connection                                                 |

| 2    | VDD    | Floating input supply voltage                                 |

| 3    | LIN1   | Logic input for LO ramp control                               |

| 4    | LIN2   | Logic input for low side gate driver outputs, in phase        |

| 5    | HIN3   | Logic input for high side gate driver output                  |

| 6    | VSS    | Floating input supply return                                  |

| 7    | NC     | No Connection                                                 |

| 8    | NC     | No Connection                                                 |

| 9    | VREF   | External programmable R/C input for ramp generation           |

| 10   | DV     | Ramp selection and programmable difference voltage (DV) input |

| 11   | COM    | Low side supply return                                        |

| 12   | RES    | Adjustable current source resistor input                      |

| 13   | VSE    | Voltage sense input                                           |

| 14   | LO     | Low side gate driver output                                   |

| 15   | VCC    | Low side supply voltage                                       |

| 16   | NC     | No Connection                                                 |

| 17   | NC     | No Connection                                                 |

| 18   | VS     | High side gate drive floating supply return                   |

| 19   | HO3    | High side gate driver output                                  |

| 20   | VB     | High side gate drive floating supply                          |

**IRS21956S**

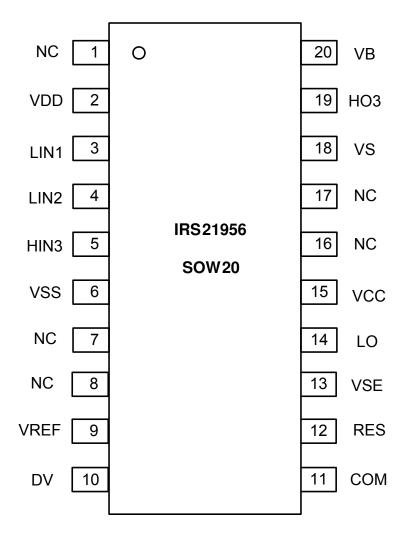

# **Lead Assignments**

Package 20 pin SOW

**IRS21956S**

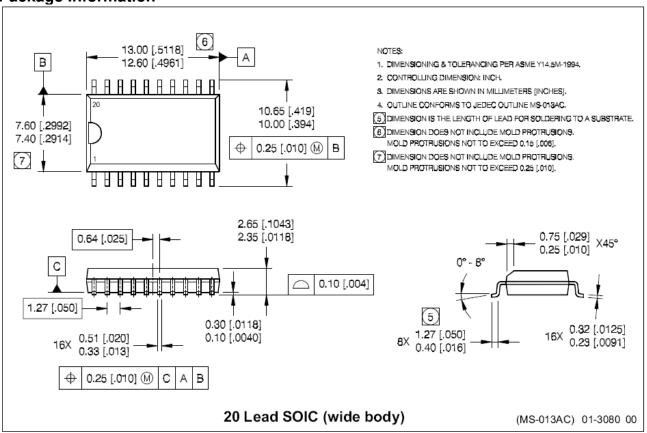

## **Package Information**

www.irf.com © 2008 International Rectifier 19

## **Package Details:**

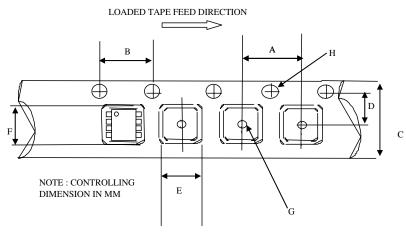

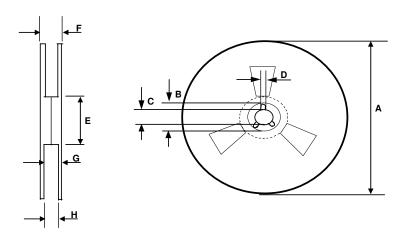

CARRIER TAPE DIMENSION FOR 20SOICW

|      | Me    | tric  | Imp   | erial |

|------|-------|-------|-------|-------|

| Code | Min   | Max   | Min   | Max   |

| Α    | 11.90 | 12.10 | 0.468 | 0.476 |

| В    | 3.90  | 4.10  | 0.153 | 0.161 |

| С    | 23.70 | 24.30 | 0.933 | 0.956 |

| D    | 11.40 | 11.60 | 0.448 | 0.456 |

| E    | 10.80 | 11.00 | 0.425 | 0.433 |

| F    | 13.20 | 13.40 | 0.520 | 0.528 |

| G    | 1.50  | n/a   | 0.059 | n/a   |

| Н    | 1.50  | 1.60  | 0.059 | 0.062 |

REEL DIMENSIONS FOR 20SOICW

|        | Me     | tric   | Imperial |        |  |  |  |  |

|--------|--------|--------|----------|--------|--|--|--|--|

| Code   | Min    | Max    | Min      | Max    |  |  |  |  |

| Α      | 329.60 | 330.25 | 12.976   | 13.001 |  |  |  |  |

| B<br>C | 20.95  | 21.45  | 0.824    | 0.844  |  |  |  |  |

| С      | 12.80  | 13.20  | 0.503    | 0.519  |  |  |  |  |

| D      | 1.95   | 2.45   | 0.767    | 0.096  |  |  |  |  |

| E<br>F | 98.00  | 102.00 | 3.858    | 4.015  |  |  |  |  |

|        | n/a    | 30.40  | n/a      | 1.196  |  |  |  |  |

| G<br>H | 26.50  | 29.10  | 1.04     | 1.145  |  |  |  |  |

| Н      | 24.40  | 26.40  | 0.96     | 1.039  |  |  |  |  |

IOR Rectifier

IRS21956S

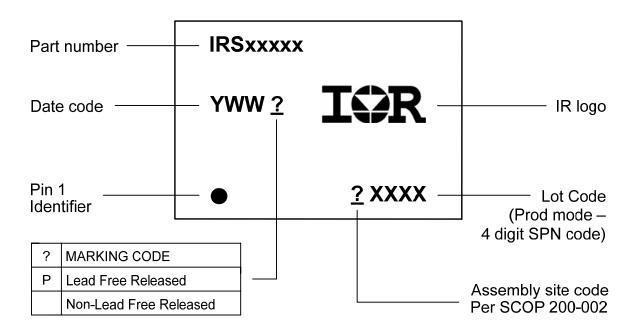

## **Part Marking Information**

Not recommended for new designs. No replacement is available International IRS21956S

IOR Rectifier

## **Ordering Information**

| Base Part Number | Package Type | Standard Pack |          | Olate Bank Namehan   |

|------------------|--------------|---------------|----------|----------------------|

|                  |              | Form          | Quantity | Complete Part Number |

| IRS21956         | SOIC20W      | Tube/Bulk     | 38       | IRS21956SPBF         |

|                  |              | Tape and Reel | 1000     | IRS21956STRPBF       |

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center <a href="http://www.irf.com/technical-info/">http://www.irf.com/technical-info/</a>

#### **WORLD HEADQUARTERS:**

233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105