### imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

#### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### VRM 8.5 COMPATIBLE 5-BIT PROGRAMMABLE SYNCHRONOUS BUCK CONTROLLER IC WITH TRIPLE LDO CONTROLLER

#### **FEATURES**

- Meets Latest VRM 8.5 Specification

- Provides Single Chip Solution for Vcore, 1.2V AGTL+, 1.8V and VDDQ

- On-Board 5-Bit DAC and Decoder programs the output voltage from 1.050V to 1.825V

- Loss-less Short Circuit Protection

- Synchronous operation allows maximum efficiency

- Patented architecture allows fixed frequency operation as well as 100% duty cycle when operating with a changing load

- Minimum Part Count, No External Compensation

- Soft-Start

- High current totem pole driver for directly driving an external Power MOSFET

- Power Good Function

#### **APPLICATIONS**

- Pentium III with VRM 8.5 Specification

- DC to DC Converters

#### DESCRIPTION

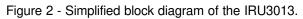

The IRU3013 controller IC is specifically designed for Intel Pentium III™ microprocessor applications as described in the VRM 8.5 specification. The IC provides a single chip solution for the Vcore, 1.2V AGTL+, 1.8V and a third uncommitted LDO controller that can be used either as 1.2V power good detector or to provide 1.5V AGP bus in applications that this voltage is required. The IRU3013 features a patented topology that, in combination with a few external components, (\*Note: See application current in Figure 3) will provide in excess of 30A of output current for an onboard Vcore synchronous converter while automatically providing the output voltage specified in VRM 8.5 specification. The IRU3013 also features, loss-less current sensing by using the RDS(ON) of the high side Power MOSFET as the sensing resistor, a Power Good window comparator that switches its open collector output low when the output is outside of a  $\pm 10\%$  window. Other features of the device are: Under-voltage lockout for both 5V and 12V supplies, an external programmable softstart function, and the ability to program the oscillator frequency by connecting an external capacitor.

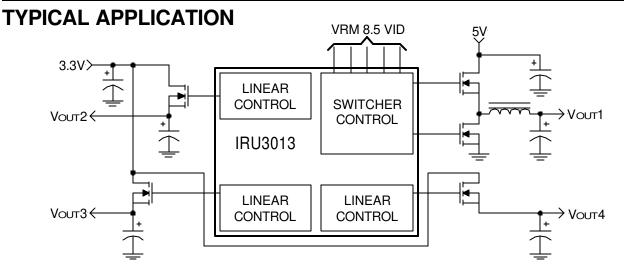

Figure 1 - Typical application of IRU3013. Note: Pentium III is trade mark of Intel Corp.

#### PACKAGE ORDER INFORMATION

| T₄(°C)  | C) DEVICE PACKAGE |                            |  |

|---------|-------------------|----------------------------|--|

| 0 To 70 | IRU3013CQ         | 24-Pin Plastic QSOP NB (Q) |  |

| 0 To 70 | IRU3013CW         | 24-Pin Plastic SOIC WB (W) |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| V5 Supply Voltage                    | 10V            |

|--------------------------------------|----------------|

| V12 Supply Voltage                   | 20V            |

| All Other Pins                       | 7V             |

| Storage Temperature Range            | -65°C To 150°C |

| Operating Junction Temperature Range | 0°C To 125°C   |

#### PACKAGE INFORMATION

| 24-PIN PLAST  | TIC QSOP (Q) | 24-PIN WIDE BODY | PLASTIC SOIC (W) |

|---------------|--------------|------------------|------------------|

| Ct 1          | 24 Lin2      | .ct 1            | 24 Lin2          |

| Lin1 2        | 23 D0        | Lin1 2           | 23 D0            |

| VFB1 3        | 22 D1        | VFB1 3           | 22 D1            |

| VFB2 4        | 21 D2        | VFB2 4           | 21 D2            |

| V5 5          | 20 D3        | V5 5             | 20 D3            |

| OVP 6         | 19 D25       | OVP 6            | 19 D25           |

| PGd 7         | 18 VFB3      | PGd 7            | 18 VFB3          |

| <u>CS-8</u>   | 17 SS        | <u>.</u> CS- 8   | 17 SS            |

| CS+ 9         | 16 Lin4      | <u>CS+ 9</u>     | 16 Lin4          |

| HDrv 10       | 15 VFB4      | HDrv 10          | 15 VFB4          |

| PGnd 11       | 14 V12       | PGnd 11          | 14 V12           |

| <u>Gnd 12</u> | 13 LDrv      | Gnd 12           | 13 LDrv          |

| θja=8         | 8°C/W        | θ_JA=80          | 0°C/W            |

#### **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, these specifications apply over V12=12V, V5=5V and T<sub>A</sub>=0 to 70°C. Typical values refer to T<sub>A</sub>=25°C. Low duty cycle pulse testing is used which keeps junction and case temperatures equal to the ambient temperature.

| PARAMETER                      | SYM | TEST CONDITION                                                           | MIN    | TYP    | MAX    | UNITS |

|--------------------------------|-----|--------------------------------------------------------------------------|--------|--------|--------|-------|

| VID Section                    |     |                                                                          |        |        |        |       |

| DAC Output Voltage (Note 1)    |     |                                                                          | 0.98Vs | Vs     | 1.02Vs | V     |

| DAC Output Line Regulation     |     | 4.5 <vcc<5.5< td=""><td></td><td></td><td></td><td></td></vcc<5.5<>      |        |        |        |       |

|                                |     | 10.5 <v12<13v< td=""><td></td><td>0.2</td><td></td><td>%</td></v12<13v<> |        | 0.2    |        | %     |

| DAC Output Temp Variation      |     |                                                                          |        | 0.5    |        | %     |

| VID Input LO                   |     |                                                                          |        |        | 0.4    | V     |

| VID Input HI                   |     |                                                                          | 2      |        |        | V     |

| VID Input Internal Pull-up     |     |                                                                          |        |        |        |       |

| Resistor to 5V                 |     |                                                                          |        | 27     |        | KΩ    |

| Power Good Section             |     |                                                                          |        |        |        |       |

| Under-Voltage Lower Trip Point |     | Vout Ramping Down                                                        |        | 0.90Vs |        | V     |

| Under-Voltage Upper Trip Point |     | Vout Ramping Up                                                          |        | 0.92Vs |        | V     |

| UV Hysteresis                  |     |                                                                          |        | 0.02Vs |        | V     |

| Over-Voltage Upper Trip Point  |     | Vout Ramping Up                                                          |        | 1.10Vs |        | V     |

| Over-Voltage Lower Trip Point  |     | Vout Ramping Down                                                        |        | 1.08Vs |        | V     |

| OV Hysterises                  |     |                                                                          |        | 0.02Vs |        | V     |

| Power Good Output LO           |     | R∟= 3mA                                                                  |        | 0.3    |        | V     |

| Power Good Output HI           |     | R∟= 5K Pull-Up to 5V                                                     |        | 4.95   |        | V     |

| Soft-Start Section             |     |                                                                          |        |        |        |       |

| Soft-Start Current             |     | CS+ = 0V, CS- = 5V                                                       |        | 10     |        | μA    |

| PARAMETER                    | SYM | TEST CONDITION    | MIN | TYP    | MAX | UNITS |

|------------------------------|-----|-------------------|-----|--------|-----|-------|

| UVLO Section                 |     |                   |     |        |     |       |

| UVLO Threshold - 12V         |     | Supply Ramping Up |     | 9      |     | V     |

| UVLO Hysteresis - 12V        |     |                   |     | 0.5    |     | V     |

| UVLO Threshold - 5V          |     | Supply Ramping Up |     | 4      |     | V     |

| UVLO Hysteresis - 5V         |     |                   |     | 0.3    |     | V     |

| Error Comparator Section     |     |                   |     |        |     |       |

| Input Offset Voltage         |     |                   | -2  |        | +2  | mV    |

| Delay to Output              |     | VDIFF = 10mV      |     |        | 100 | ns    |

| Current Limit Section        |     |                   |     |        |     |       |

| CS Threshold Set Current     |     |                   | 120 | 150    | 200 | μA    |

| CS Comp Offset Voltage       |     |                   | -5  |        | +5  | mV    |

| Hiccup Duty Cycle            |     | Css = 0.1µF       |     |        | 2   | %     |

| Supply Current Section       |     |                   |     |        |     |       |

| Operating Supply Current     |     | C∟ = 3000pF       |     |        |     |       |

|                              |     | V5                |     | 20     |     |       |

|                              |     | V12               |     | 14     |     | mA    |

| Output Drivers Section       |     |                   |     |        |     |       |

| Rise Time                    |     | C∟ = 3000pF       |     | 70     | 100 | ns    |

| Fall Time                    |     | C∟ = 3000pF       |     | 70     | 130 | ns    |

| Dead Band Time               |     | C∟ = 3000pF       |     | 200    |     | ns    |

| Oscillator Section           |     |                   |     |        |     |       |

| Osc Frequency                |     | Ct = 150pF        |     | 220    |     | KHz   |

| Osc Valley                   |     |                   |     |        | 0.2 | V     |

| Osc Peak                     |     |                   |     | V5     |     | V     |

| LDO Controller Section       |     |                   |     |        |     |       |

| VFB1 and VFB2 (Pins 3 and 4) |     |                   |     | 1.200  |     |       |

| V <sub>FB</sub> 4 (Pin 15)   |     |                   |     | 0.800  |     | V     |

| Input Bias Current           |     |                   |     |        | 2   | μA    |

| Lin 1, 2, 3 Drive Current    |     |                   |     | 30     |     | mA    |

| OVP Section                  |     |                   |     |        |     |       |

| OVP Threshold                |     |                   |     | 1.17Vs |     | V     |

| OVP Source Current           |     |                   |     | 5      |     | mA    |

Note: Vs refers to the set point voltage given in table 1.

| D25 | D3 | D2 | D1 | D0 | Vs    | D25 | D3 | D2 | D1 | D0 | Vs    |

|-----|----|----|----|----|-------|-----|----|----|----|----|-------|

| 0   | 1  | 1  | 1  | 1  | 1.300 | 1   | 1  | 1  | 1  | 1  | 1.325 |

| 0   | 1  | 1  | 1  | 0  | 1.350 | 1   | 1  | 1  | 1  | 0  | 1.375 |

| 0   | 1  | 1  | 0  | 1  | 1.400 | 1   | 1  | 1  | 0  | 1  | 1.425 |

| 0   | 1  | 1  | 0  | 0  | 1.450 | 1   | 1  | 1  | 0  | 0  | 1.475 |

| 0   | 1  | 0  | 1  | 1  | 1.500 | 1   | 1  | 0  | 1  | 1  | 1.525 |

| 0   | 1  | 0  | 1  | 0  | 1.550 | 1   | 1  | 0  | 1  | 0  | 1.575 |

| 0   | 1  | 0  | 0  | 1  | 1.600 | 1   | 1  | 0  | 0  | 1  | 1.625 |

| 0   | 1  | 0  | 0  | 0  | 1.650 | 1   | 1  | 0  | 0  | 0  | 1.675 |

| 0   | 0  | 1  | 1  | 1  | 1.700 | 1   | 0  | 1  | 1  | 1  | 1.725 |

| 0   | 0  | 1  | 1  | 0  | 1.750 | 1   | 0  | 1  | 1  | 0  | 1.775 |

| 0   | 0  | 1  | 0  | 1  | 1.800 | 1   | 0  | 1  | 0  | 1  | 1.825 |

| 0   | 0  | 1  | 0  | 0  | 1.050 | 1   | 0  | 1  | 0  | 0  | 1.075 |

| 0   | 0  | 0  | 1  | 1  | 1.100 | 1   | 0  | 0  | 1  | 1  | 1.125 |

| 0   | 0  | 0  | 1  | 0  | 1.150 | 1   | 0  | 0  | 1  | 0  | 1.175 |

| 0   | 0  | 0  | 0  | 1  | 2.200 | 1   | 0  | 0  | 0  | 1  | 1.225 |

| 0   | 0  | 0  | 0  | 0  | 2.250 | 1   | 0  | 0  | 0  | 0  | 1.275 |

Table 1 - Set point voltage vs. VID codes.

#### **PIN DESCRIPTIONS**

| PIN#              | PIN SYMBOL        | PIN DESCRIPTION                                                                                     |

|-------------------|-------------------|-----------------------------------------------------------------------------------------------------|

| <u>r IIN</u><br>1 | Ct                | This pin programs the oscillator frequency in the range of 50 KHz to 500KHz by means of             |

| 1                 | Ol.               | an external capacitor connected from this pin to the ground.                                        |

| 2                 | Lin1              | Controls the gate of an external MOSFET for the AGTL+ linear regulator or 1.8V supply.              |

| 3                 | V <sub>FB</sub> 1 | This pin provides the feedback for the linear regulator that its output drive is Lin1 pin.          |

| 4                 | VFB1<br>VFB2      | This pin provides the feedback for the linear regulator that its output drive is Lin2 pin.          |

| 5                 | VFBZ<br>V5        | 5V supply voltage.                                                                                  |

| 6                 | OVP               | This pin provides an over voltage flag when the feedback pin V $\oplus$ 3 voltage exceeds 17%(Typi- |

| 0                 | 01                | cal) of the set point for the Vcore output.                                                         |

| 7                 | PGd               | This pin is an open collector output that switches LO when the output of the converter is           |

| '                 | r du              | not within $\pm 10\%$ (typ) of the nominal output voltage. When PGd pin switches LO the             |

|                   |                   | output saturation voltage is less than 0.4V at 3mA.                                                 |

| 8                 | CS-               | This pin is connected to the Source of the power MOSFET for the Core supply and it is               |

| 0                 | 00                | the negative input for the internal current sensing circuitry.                                      |

| 9                 | CS+               | This pin is connected to the Drain of the power MOSFET of the Core supply. It provides the          |

| Ũ                 | 001               | positive sensing input for the internal current sensing circuitry. An external resistor pro-        |

|                   |                   | grams the CS threshold depending on the Rbs of the power MOSFET. An external capaci-                |

|                   |                   | tor is placed in parallel with the programming resistor to provide high frequency noise             |

|                   |                   | filtering.                                                                                          |

| 10                | HDrv              | Output driver for the high side power MOSFET.                                                       |

| 11                | PGnd              | This is the power ground pin and must be connected directly to the gnd plane close to the           |

|                   |                   | source of the synchronous MOSFET. A high frequency capacitor (typically $1\mu$ F) must be           |

|                   |                   | connected from V12 pin to this pin for noise free operation.                                        |

| 12                | Gnd               | This pin must be connected directly to the ground plane. A high frequency capacitor (0.1            |

|                   |                   | to $1\mu$ F) must be connected from V5 and V12 pins to this pin for noise free operation.           |

| 13                | LDrv              | Output driver for the power MOSFET, which is used as a synchronous switched rectifier.              |

| 14                | V12               | This pin is connected to the 12V supply and serves as the power Vcc pin for the output              |

|                   |                   | drivers. A high frequency capacitor (0.1 to 1µF) must be connected directly from this pin           |

|                   |                   | to Gnd pin in order to supply large instantaneous current pulses to the power MOSFET                |

|                   |                   | during the transitions.                                                                             |

| 15                | V <sub>FB</sub> 4 | This pin provides the feedback for the linear regulator that its output drive is Lin4 pin.          |

| 16                | Lin4              | This pin controls the gate of an external MOSFET for either the AGP Bus linear regulator            |

|                   |                   | or can be used as Power good detector for 1.2V AGTL+ bus.                                           |

| 17                | SS                | This pin provides the soft-start for the switching regulator. An internal current source            |

|                   |                   | charges an external capacitor that is connected from this pin to the ground which ramps             |

|                   |                   | up the outputs of the switching regulator, preventing the outputs from overshooting as well         |

|                   |                   | as limiting the inrush current. The second function of the Soft-Start cap is to provide long        |

|                   |                   | off time (HICCUP) for the synchronous MOSFET during current limiting.                               |

| 18                | Vfb3              | This pin is connected directly to the output of the Core supply to provide feedback to the          |

|                   |                   | Error comparator.                                                                                   |

| 19                | D25               | This pin programs the output voltage in 25mV steps based on the VID table. 40K internal             |

|                   |                   | pull-up to Vcc.                                                                                     |

| 20                | D3                | MSB input to the DAC that programs the output voltage. This pin can be pulled-up exter-             |

|                   |                   | nally by a 10K resistor to either 3.3V or 5V supply. 40K internal pull-up to Vcc.                   |

| 21                | D2                | Input to the DAC that programs the output voltage. This pin can be pulled-up externally by          |

|                   | <b>D</b> 4        | a 10K resistor to either 3.3V or 5V supply. 40K internal pull-up to Vcc.                            |

| 22                | D1                | Input to the DAC that programs the output voltage. This pin can be pulled-up externally by          |

|                   | <b>D</b> 2        | a $10K\Omega$ resistor to either 3.3V or 5V supply. 40K internal pull-up to Vcc.                    |

| 23                | D0                | LSB input to the DAC that programs the output voltage. This pin can be pulled-up exter-             |

| - 04              | 1:-0              | nally by a 10K resistor to either 3.3V or 5V supply. 40K internal pull-up to Vcc.                   |

| _24               | Lin2              | Controls the gate of an external MOSFET for the AGTL+ linear regulator or 1.8V supply.              |

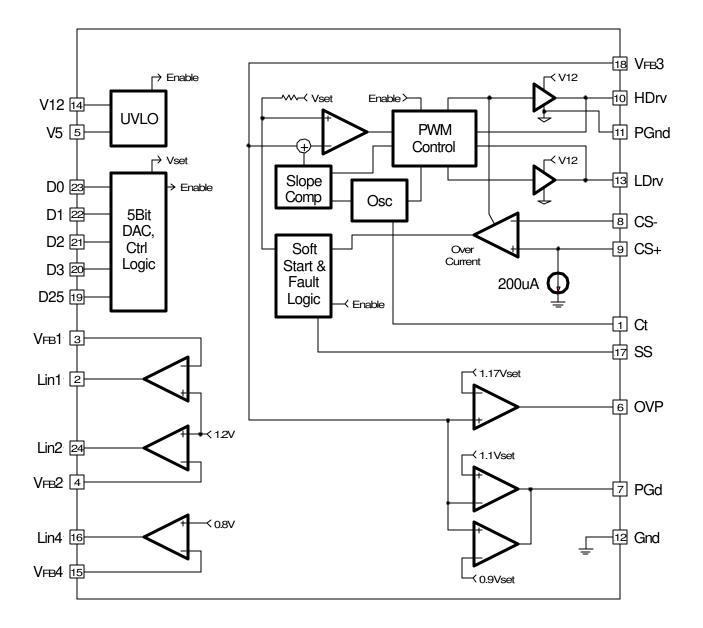

#### **BLOCK DIAGRAM**

Rev. 1.4 08/20/02

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Data and specifications subject to change without notice. Visit us at www.irf.com for sales contact information 02/01

Internationa **ICR** Rectifier

# TYPICAL APPLICATION

IRU3013

## International

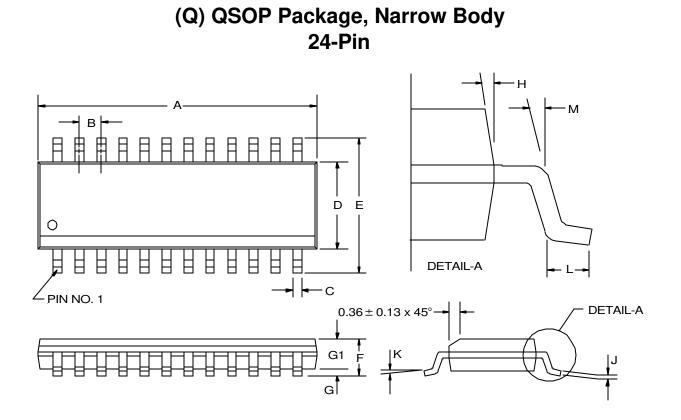

|        | 24-PIN |      |  |  |  |  |  |  |

|--------|--------|------|--|--|--|--|--|--|

| SYMBOL | MIN    | MAX  |  |  |  |  |  |  |

| Α      | 8.55   | 8.74 |  |  |  |  |  |  |

| В      | 0.635  | BSC  |  |  |  |  |  |  |

| С      | 0.20   | 0.30 |  |  |  |  |  |  |

| D      | 3.81   | 3.99 |  |  |  |  |  |  |

| E      | 5.79   | 6.20 |  |  |  |  |  |  |

| F      | 1.35   | 1.75 |  |  |  |  |  |  |

| G      | 0.10   | 0.25 |  |  |  |  |  |  |

| G1     | 1.37   | 1.57 |  |  |  |  |  |  |

| Н      | 9° E   | BSC  |  |  |  |  |  |  |

| J      | 0.19   | 0.25 |  |  |  |  |  |  |

| K      | 0°     | 8°   |  |  |  |  |  |  |

| L      | 0.40   | 1.27 |  |  |  |  |  |  |

| М      | 7°=    | ± 3° |  |  |  |  |  |  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

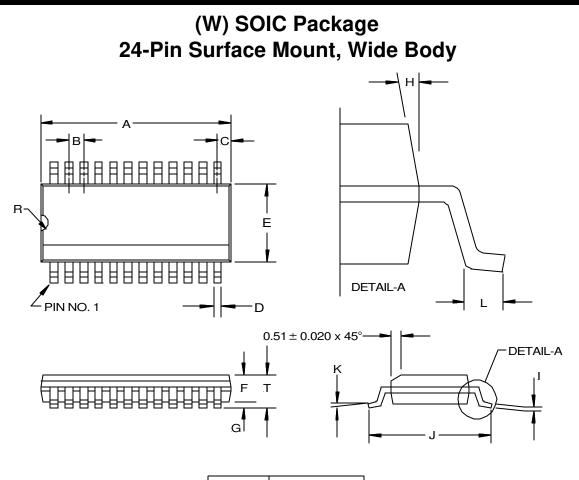

| SYMBOL | 24-PIN |       |  |  |

|--------|--------|-------|--|--|

|        | MIN    | MAX   |  |  |

| А      | 15.20  | 15.40 |  |  |

| В      | 1.27   | BSC   |  |  |

| С      | 0.66   | REF   |  |  |

| D      | 0.36   | 0.46  |  |  |

| E      | 7.40   | 7.60  |  |  |

| F      | 2.44   | 2.64  |  |  |

| G      | 0.10   | 0.30  |  |  |

| I      | 0.23   | 0.32  |  |  |

| J      | 10.11  | 10.51 |  |  |

| K      | 0°     | 8°    |  |  |

| L      | 0.51   | 1.01  |  |  |

| R      | 0.63   | 0.89  |  |  |

| Т      | 2.44   | 2.64  |  |  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

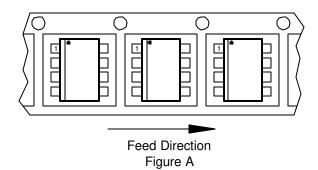

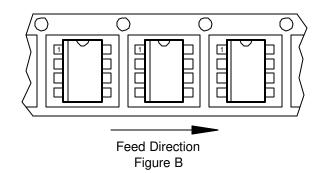

#### PACKAGE SHIPMENT METHOD

| PKG<br>DESIG | PACKAGE<br>DESCRIPTION    | PIN<br>COUNT | PARTS<br>PER TUBE | PARTS<br>PER REEL | T & R<br>Orientation |

|--------------|---------------------------|--------------|-------------------|-------------------|----------------------|

| Q            | QSOP Plastic, Narrow Body | 24           |                   | 1500              | Fig A                |

| W            | SOIC, Wide Body           | 24           | 31                | 1000              | Fig B                |

International IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 02/01