Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# IS43/46DR83200A IS43/46DR16160A

## 32Mx8, 16Mx16 DDR2 DRAM

#### **AUGUST 2012**

#### **FEATURES**

- $VDD = 1.8V \pm 0.1V$ ,  $VDDQ = 1.8V \pm 0.1V$

- JEDEC standard 1.8V I/O (SSTL 18-compatible)

- Double data rate interface: two data transfers per clock cycle

- Differential data strobe (DQS, DQS)

- · 4-bit prefetch architecture

- On chip DLL to align DQ and DQS transitions with CK

- 4 internal banks for concurrent operation

- Programmable CAS latency (CL) 3, 4, 5, and 6 supported

- Posted CAS and programmable additive latency (AL) 0, 1, 2, 3, 4, and 5 supported

- WRITE latency = READ latency 1 tCK

- Programmable burst lengths: 4 or 8

- Adjustable data-output drive strength, full and reduced strength options

- On-die termination (ODT)

#### **OPTIONS**

- Configuration(s): 32Mx8 (8Mx8x4 banks) IS43/46DR83200A 16Mx16 (4Mx16x4 banks) IS43/46DR16160A

- · Package:

x8: 60-ball TW-BGA (8mm x 10.5mm) x16: 84-ball TW-BGA (8mm x 12.5mm) Timing – Cycle time

2.5ns @CL=6 DDR2-800E

3.0ns @CL=5 DDR2-667D

3.75ns @CL=4 DDR2-533C

5.0ns @CL=3 DDR2-400B

• Temperature Range:

Commercial (0°C  $\leq$  Tc  $\leq$  85°C)

Industrial (-40°C  $\leq$  Tc  $\leq$  95°C; -40°C  $\leq$  Ta  $\leq$  85°C)

Automotive, A1 (-40°C  $\leq$  Tc  $\leq$  95°C; -40°C  $\leq$  Ta  $\leq$  85°C)

Automotive, A2 (-40°C  $\leq$  Tc; Ta  $\leq$  105°C)

Tc = Case Temp, TA = Ambient Temp

#### **DESCRIPTION**

ISSI's 256Mb DDR2 SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double-data rate architecture is essentially a 4n-prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O balls.

#### **ADDRESS TABLE**

| Parameter               | 32M x 8             | 16M x 16             |

|-------------------------|---------------------|----------------------|

| Configuration           | 8M x 8 x 4<br>banks | 4M x 16 x 4<br>banks |

| Refresh Count           | 8K/64ms             | 8K/64ms              |

| Row Addressing          | 8K (A0-A12)         | 8K (A0-A12)          |

| Column<br>Addressing    | 1K (A0-A9)          | 512 (A0-A8)          |

| Bank Addressing         | BA0, BA1            | BA0, BA1             |

| Precharge<br>Addressing | A10                 | A10                  |

#### **KEY TIMING PARAMETERS**

| Speed Grade | -25E | -3D  | -37C | -5B |

|-------------|------|------|------|-----|

| tRCD        | 15   | 15   | 15   | 15  |

| tRP         | 15   | 15   | 15   | 15  |

| tRC         | 60   | 60   | 60   | 55  |

| tRAS        | 45   | 45   | 45   | 40  |

| tCK @CL=3   | 5    | 5    | 5    | 5   |

| tCK @CL=4   | 3.75 | 3.75 | 3.75 | 5   |

| tCK @CL=5   | 3    | 3    | _    | _   |

| tCK @CL=6   | 2.5  | _    | _    | _   |

Copyright © 2012 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

#### **GENERAL DESCRIPTION**

Read and write accesses to the DDR2 SDRAM are burst oriented; accesses start at a selected location and continue for a burst length of four or eight in a programmed sequence. Accesses begin with the registration of an Active command, which is then followed by a Read or Write command. The address bits registered coincident with the active command are used to select the bank and row to be accessed (BA0-BA1 select the bank; A0-A12 select the row). The address bits registered coincident with the Read or Write command are used to select the starting column location (A0-A8 for x16) and (A0-A9 for x8) for the burst access and to determine if the auto precharge A10 command is to be issued. Prior to normal operation, the DDR2 SDRAM must be initialized. The following sections provide detailed information covering device initialization, register definition, command descriptions and device operation.

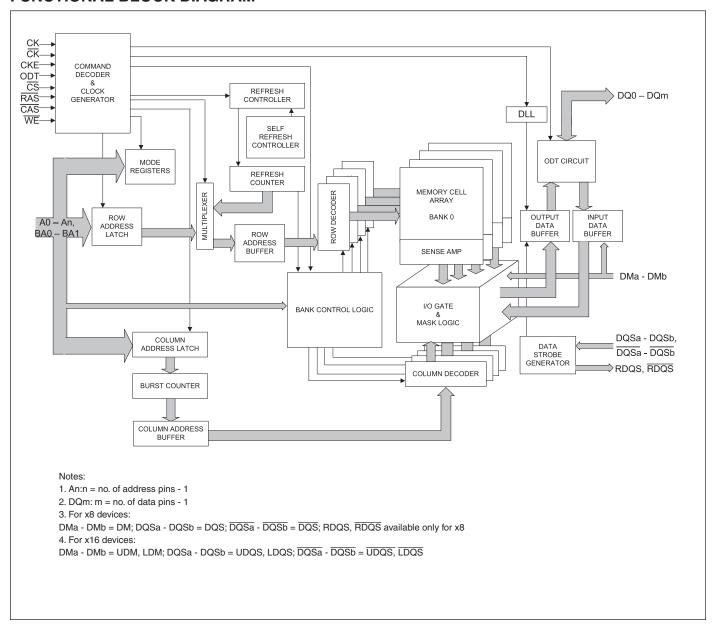

#### **FUNCTIONAL BLOCK DIAGRAM**

## PIN DESCRIPTION TABLE

| Symbol                       | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK                       | Input | Clock: CK and $\overline{\text{CK}}$ are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of $\overline{\text{CK}}$ . Output (read) data is referenced to the crossings of CK and $\overline{\text{CK}}$ (both directions of crossing).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CKE                          | Input | Clock Enable: CKE HIGH activates, and CKE LOW deactivates, internal clock signals and device input buffers and output drivers. Taking CKE LOW provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and exit, and for self refresh entry. CKE is asynchronous for self refresh exit. After VREF has become stable during the power on and initialization sequence, it must be maintained for proper operation of the CKE receiver. For proper self-refresh entry and exit, VREF must be maintained to this input. CKE must be maintained HIGH throughout read and write accesses. Input buffers, excluding CK, $\overline{CK}$ , ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during self refresh. |

| CS                           | Input | Chip Select: All commands are masked when $\overline{CS}$ is registered HIGH. $\overline{CS}$ provides for external Rank selection on systems with multiple Ranks. $\overline{CS}$ is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ODT                          | Input | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR2 SDRAM. When enabled, ODT is applied to each DQ, DQS, DQS, DM signals. The ODT pin will be ignored if the EMR(1) is programmed to disable ODT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RAS, CAS, WE                 | Input | Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DM (x8) or<br>UDM, LDM (x16) | Input | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For x8, the function of DM is enabled by EMRS command to EMR(1) [A11].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BA0 - BA1                    | Input | Bank Address Inputs: BA0 - BA1 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or one of the extended mode registers is to be accessed during a MRS or EMRS command cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A0 - A12                     | Input | Address Inputs: Provide the row address for Active commands and the column address and Auto Precharge bit for Read/Write commands to select one location out of the memory array in the respective bank. A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0 - BA1. The address inputs also provide the op-code during MRS or EMRS commands.                                                                                                                                                                                                                                                                                                                                                           |

| Symbol                                                     | Туре             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ0-7 x8<br>DQ0-15 x16                                     | Input/<br>Output | Data Input/Output: Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQS, (DQS) RDQS, (RDQS) x8  UDQS, (UDQS), LDQS, (LDQS) x16 | Input/<br>Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. The data strobes DQS(n) may be used in single ended mode or paired with optional complementary signals DQS(n) to provide differential pair signaling to the system during both reads and writes. A control bit at EMR(1)[A10] enables or disables all complementary data strobe signals.  x8  DQS corresponds to the data on DQ0-DQ7  RDQS corresponds to the Read data on DQ0-DQ7, and is enabled by EMRS command to EMR(1) [A11].  x16  LDQS corresponds to the data on DQ0-DQ7  UDQS corresponds to the data on DQ0-DQ7  UDQS corresponds to the data on DQ8-DQ15 |

| NC                                                         |                  | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDDQ                                                       | Supply           | DQ Power Supply: 1.8 V +/- 0.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VSSQ                                                       | Supply           | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDDL                                                       | Supply           | DLL Power Supply: 1.8 V +/- 0.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VSSDL                                                      | Supply           | DLL Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD                                                        | Supply           | Power Supply: 1.8 V +/- 0.1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VSS                                                        | Supply           | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VREF                                                       | Supply           | Reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## **PIN CONFIGURATION**

PACKAGE CODE: B 60 BALL TW-BGA (Top View) (8.00 mm x 10.5 mm Body, 0.8 mm Ball Pitch)

| Pin name        | Function                           | Pin name | Function                            |

|-----------------|------------------------------------|----------|-------------------------------------|

| A0 to A12       | Address inputs                     | ODT      | ODT control                         |

| BA0, BA1        | Bank select                        | VDD      | Supply voltage for internal circuit |

| DQ0 to DQ7      | Data input/output                  | VSS      | Ground for internal circuit         |

| DQS, /DQS       | Differential data strobe           | VDDQ     | Supply voltage for DQ circuit       |

| /CS             | Chip select                        | VSSQ     | Ground for DQ circuit               |

| /RAS, /CAS, /WE | Command input                      | VREF     | Input reference voltage             |

| CKE             | Clock enable                       | VDDL     | Supply voltage for DLL circuit      |

| CK, /CK         | Differential clock input           | VSSDL    | Ground for DLL circuit              |

| DM              | Write data mask                    | NC       | No connection                       |

| RDQS, /RDQS     | Differential Redundant Data Strobe |          |                                     |

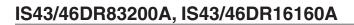

## **PIN CONFIGURATION**

PACKAGE CODE: B 84 BALL TW-BGA (Top View) (8.00 mm x 12.50 mm Body, 0.8 mm Ball Pitch)

|                       | 1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2 3                                         | 4                                                                       | 5 | 6 | 7                      | 8                                                                             | 9                            |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------|---|---|------------------------|-------------------------------------------------------------------------------|------------------------------|

| A B C D E F G H J K L | DQ14 V VDDQ I VD |                                             | )<br>M<br>)<br>Q<br>)<br>1<br>)<br>M<br>)<br>Q<br>)<br>M<br>)<br>Q<br>) |   |   | ODS VDDQ DQ10          | VSSQ<br>VSSQ<br>VSSQ<br>VSSQ<br>VSSQ<br>VSSQ<br>VSSQ<br>VSSQ                  | DQ13  VDDQ  VDDQ  VDDQ       |

| M<br>N<br>P<br>R      | VSSS (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BA0 BA1 | )<br>)<br>)                                                             |   | ( | CAS<br>A2<br>A11<br>NC | $ \begin{array}{c} \overline{CS} \\ A0 \\ A4 \\ A8 \\ NC \end{array} $ or pop | VDD<br>VSS<br>VSS<br>Oulated |

| Pin name        | Function                 | Pin name | Function                            |

|-----------------|--------------------------|----------|-------------------------------------|

| A0 to A12       | Address inputs           | ODT      | ODT control                         |

| BA0, BA1        | Bank select              | VDD      | Supply voltage for internal circuit |

| DQ0 to DQ15     | Data input/output        | VSS      | Ground for internal circuit         |

| LDQS, UDQS      | Differential data strobe | VDDQ     | Supply voltage for DQ circuit       |

| /LDQS, /UDQS    |                          |          |                                     |

| /CS             | Chip select              | VSSQ     | Ground for DQ circuit               |

| /RAS, /CAS, /WE | Command input            | VREF     | Input reference voltage             |

| CKE             | Clock enable             | VDDL     | Supply voltage for DLL circuit      |

| CK, /CK         | Differential clock input | VSSDL    | Ground for DLL circuit              |

| LDM to UDM      | Write data mask          | NC       | No connection                       |

## **ELECTRICAL SPECIFICATIONS**

## **Absolute Maximum DC Ratings**

| Symbol    | Parameter                           | Rating          | Units | Notes |

|-----------|-------------------------------------|-----------------|-------|-------|

| VDD       | Voltage on VDD pin relative to Vss  | - 1.0 V ~ 2.3 V | V     | 1,3   |

| VDDQ      | Voltage on VDDQ pin relative to Vss | - 0.5 V ~ 2.3 V | V     | 1,3   |

| VDDL      | Voltage on VDDL pin relative to Vss | - 0.5 V ~ 2.3 V | V     | 1,3   |

| VIN, VOUT | Voltage on any pin relative to Vss  | - 0.5 V ~ 2.3 V | V     | 1,4   |

| Tstg      | Storage Temperature                 | -55 to +150     | °C    | 1, 2  |

#### Notes

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. VDD and VDDQ must be within 300mV of each other at all times; and VREF must be not greater than 0.6 x VDDQ. When VDD and VDDQ and VDDL are less than 500 mV, Vref may be equal to or less than 300 mV.

- 4. Voltage on any input or I/O may not exceed voltage on VDDQ.

## **AC & DC Recommended Operating Conditions**

## **Recommended DC Operating Conditions (SSTL-1.8)**

| Symbol | Parameter                 |             | Units       | Notes       |   |      |

|--------|---------------------------|-------------|-------------|-------------|---|------|

|        |                           | Min.        | Тур.        | Max.        |   |      |

| VDD    | Supply Voltage            | 1.7         | 1.8         | 1.9         | V | 1    |

| VDDL   | Supply Voltage for DLL    | 1.7         | 1.8         | 1.9         | V | 5    |

| VDDQ   | Supply Voltage for Output | 1.7         | 1.8         | 1.9         | V | 1, 5 |

| VREF   | Input Reference Voltage   | 0.49 x VDDQ | 0.50 x VDDQ | 0.51 x VDDQ | V | 2.3  |

| VTT    | Termination Voltage       | VREF - 0.04 | VREF        | VREF + 0.04 | V | 4    |

#### Notes:

- 1. There is no specific device VDD supply voltage requirement for SSTL\_18 compliance. However under all conditions VDDQ must be less than or equal to VDD.

- 2. The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ.

- 3. Peak to peak ac noise on VREF may not exceed +/-2 % VREF(dc).

- 4. VTT of transmitting device must track VREF of receiving device.

- 5. VDDQ tracks with VDD, VDDL tracks with VDD. AC parameters are measured with VDD, VDDQ and VDDL tied together

## IS43/46DR83200A, IS43/46DR16160A

## **Operating Temperature Condition**

| Symbol | Parameter                   | Rating <sup>(1,2,3)</sup>   | Units |

|--------|-----------------------------|-----------------------------|-------|

| TOPER  | Commercial Temperature      | Tc = 0  to  +85             | °C    |

|        | Industrial Temperature,     | Tc = -40  to  +95           | °C    |

|        | Automotive Temperature (A1) | $T_A = -40 \text{ to } +85$ | °C    |

|        | Automotive Temperature (A2) | Tc = -40  to  +105          | °C    |

|        |                             | Ta = -40 to +105            | °C    |

#### Notes:

- 1. Tc = Operating case temperature at center of package

- 2. TA = Operating ambient temperature immediately above package center.

- 3. Both temperature specifications must be met.

#### **Thermal Resistance**

| Package     | Substrate | Theta-ja<br>(Airflow = 0m/s) | Theta-ja<br>(Airflow = 1m/s) | Theta-ja<br>(Airflow = 2m/s) | Theta-jc | Units |

|-------------|-----------|------------------------------|------------------------------|------------------------------|----------|-------|

| 60-ball BGA | 4-layer   | 39.71                        | 34.21                        | 32.17                        | 3.27     | C/W   |

| 84-ball BGA | 4-layer   | 34.66                        | 30.07                        | 28.66                        | 6.68     | C/W   |

#### **ODT DC Electrical Characteristics**

| PARAMETER/CONDITION                                               | SYMBOL    | MIN | NOM | MAX | UNITS | NOTES |

|-------------------------------------------------------------------|-----------|-----|-----|-----|-------|-------|

| RTT effective impedance value for EMR(1)[A6,A2]=0,1; 75 $\Omega$  | R⊤⊤1(eff) | 60  | 75  | 90  | Ω     | 1     |

| RTT effective impedance value for EMR(1)[A6,A2]=1,0; 150 $\Omega$ | Rтт2(eff) | 120 | 150 | 180 | Ω     | 1     |

| RTT effective impedance value for EMR(1)[A6,A2]=1,1; 50 $\Omega$  | Rтт3(eff) | 40  | 50  | 60  | Ω     | 1     |

| Deviation of VM with respect to VDDQ/2                            | ΔVM       | - 6 |     | + 6 | %     | 1     |

#### Notes:

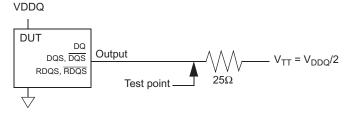

1. Test condition for  $R \pi$  measurements

Measurement Definition for  $R\pi$  (eff): Apply VIH (ac) and VIL (ac) to test pin separately, then measure current I(VIH (ac)) and I(VIL (ac)) respectively. VIH (ac), VIL (ac), and VDDQ values defined in SSTL\_18

RTT (eff)

$$\frac{\text{ViH (ac) - ViL (ac)}}{\text{I(ViH (ac)) - I(ViL (ac))}}$$

Measurement Definition for VM: Measure voltage (VM) at test pin (midpoint) with no load.

$$\Delta VM = [(2 \times VM / VDDQ) - 1] \times 100\%$$

## Input DC logic level

| Symbol  | Parameter           | Min.         | Max.         | Units | Notes |

|---------|---------------------|--------------|--------------|-------|-------|

| VIH(dc) | dc input logic HIGH | VREF + 0.125 | VDDQ + 0.3   | V     |       |

| VIL(dc) | dc input logic LOW  | - 0.3        | VREF - 0.125 | V     |       |

## Input AC logic level

| Symbol   | Parameter           | DDR2-400, DDR2-533 |              | DDR2-667,    | DDR2-800     | Units | Notes |

|----------|---------------------|--------------------|--------------|--------------|--------------|-------|-------|

|          |                     | Min.               | Max.         | Min.         | Max          |       |       |

| VIH (ac) | ac input logic HIGH | VREF + 0.250       | VDDQ + Vpeak | VREF + 0.200 | VDDQ + Vpeak | V     | 1     |

| VIL (ac) | ac input logic LOW  | VSSQ - Vpeak       | VREF - 0.250 | VSSQ - Vpeak | VREF - 0.200 | V     | 1     |

#### Notes:

1. Refer to Overshoot/undershoot specifications for Vpeak value: maximum peak amplitude allowed for overshoot and undershoot.

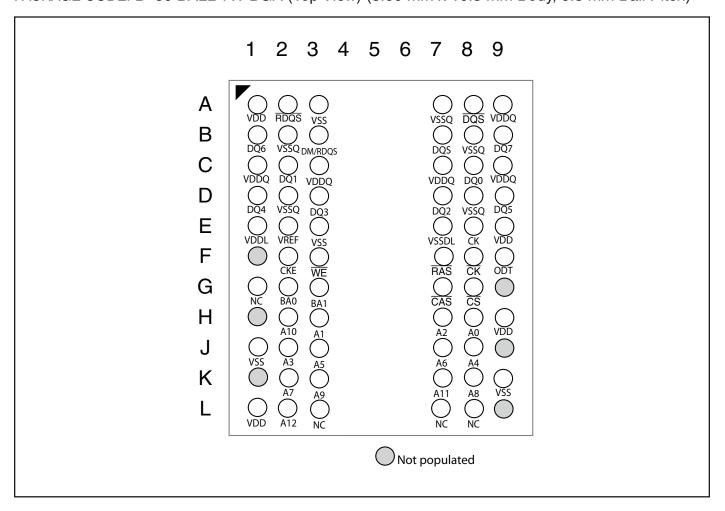

## **AC Input Test Conditions**

| Symbol      | Condition                               | Value      | Units | Notes |

|-------------|-----------------------------------------|------------|-------|-------|

| VREF        | Input reference voltage                 | 0.5 x VDDQ | V     | 1     |

| VSWING(MAX) | Input signal maximum peak to peak swing | 1.0        | V     | 1     |

| SLEW        | Input signal minimum slew rate          | 1.0        | V/ns  | 2, 3  |

#### Notes

- 1. Input waveform timing is referenced to the input signal crossing through the VIH/IL(AC) level applied to the device under test.

- 2. The input signal minimum slew rate is to be maintained over the range from VREF to VIH(ac) min for rising edges and the range from VREF to VIL(ac) max for falling edges as shown in the below figure.

- 3. AC timings are referenced with input waveforms switching from VIL(ac) to VIH(ac) on the positive transitions and VIH(ac) to VIL(ac) on the negative transitions.

## AC input test signal waveform

## IS43/46DR83200A, IS43/46DR16160A

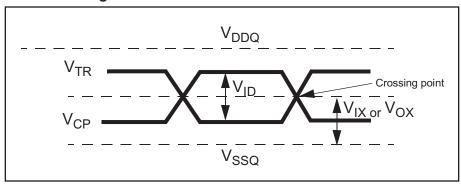

## **Differential input AC Logic Level**

| Symbol   | Parameter                          | Min.               | Max.               | Units | Notes |

|----------|------------------------------------|--------------------|--------------------|-------|-------|

| VID (ac) | ac differential input voltage      | 0.5                | VDDQ               | V     | 1,3   |

| VIX (ac) | ac differential crosspoint voltage | 0.5 x VDDQ - 0.175 | 0.5 x VDDQ + 0.175 | V     | 2     |

#### Notes:

- 1. VID(AC) specifies the input differential voltage |VTR -VCP | required for switching, where VTR is the true input signal (such as CK, DQS and VCP is the complementary input signal (such as CK or DQS). The minimum value is equal to VIH(AC) VIL(AC).

- 2. The typical value of VIX(AC) is expected to be about 0.5 x VDDQ of the transmitting device and VIX(AC) is expected to track variations in VDDQ. VIX(AC) indicates the voltage at which differential input signals must cross.

- 3. Refer to Overshoot/undershoot specifications for Vpeak value: maximum peak amplitude allowed for overshoot and undershoot.

## **Differential signal levels**

## **Differential AC Output Parameters**

| Symbol   | Parameter                          | Min.               | Max.               | Units | Notes |

|----------|------------------------------------|--------------------|--------------------|-------|-------|

| VOX (ac) | ac differential crosspoint voltage | 0.5 x VDDQ - 0.125 | 0.5 x VDDQ + 0.125 | V     | 1     |

#### Note:

1. The typical value of VOX(AC) is expected to be about 0.5 x VDDQ of the transmitting device and VOX(AC) is expected to track variations in VDDQ. VOX(AC) indicates the voltage at which differential output signals must cross.

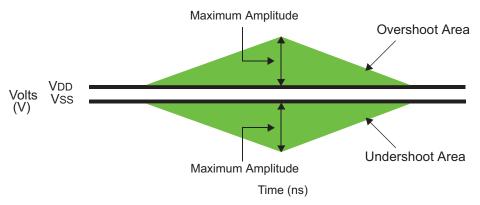

## **OVERSHOOT/UNDERSHOOT SPECIFICATION**

## AC overshoot/undershoot specification for Address and Control pins

| Parameter                                            | Specification |          |          |           |  |

|------------------------------------------------------|---------------|----------|----------|-----------|--|

|                                                      | DDR2-400      | DDR2-533 | DDR2-667 | DDR2-800  |  |

| Maximum peak amplitude allowed for overshoot area    | 0.5V          | 0.5V     | 0.5V     | 0.5V      |  |

| Maximum peak amplitude allowed for undershoot area   | 0.5V          | 0.5V     | 0.5V     | 0.5V      |  |

| Maximum overshoot area above VDD (see figure below)  | 1.33 V-ns     | 1.0 V-ns | 0.8 V-ns | 0.66 V-ns |  |

| Maximum undershoot area below VSS (see figure below) | 1.33 V-ns     | 1.0 V-ns | 0.8 V-ns | 0.66 V-ns |  |

AC overshoot and undershoot definition for address and control pins

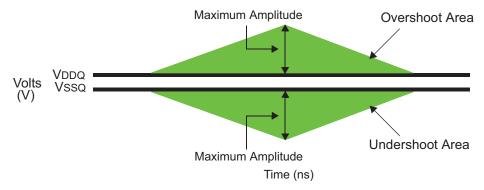

# AC overshoot/undershoot specification for Clock, Data, Strobe, and Mask pins: DQ, $(\overline{U/L/R})$ $\overline{DQS}$ , (U/L/R) DQS, DM, CK, $\overline{CK}$

| Parameter                                             | Specification |           |           |           |  |

|-------------------------------------------------------|---------------|-----------|-----------|-----------|--|

|                                                       | DDR2-400      | DDR2-533  | DDR2-667  | DDR2-800  |  |

| Maximum peak amplitude allowed for overshoot area     | 0.5V          | 0.5V      | 0.5V      | 0.5V      |  |

| Maximum peak amplitude allowed for undershoot area    | 0.5V          | 0.5V      | 0.5V      | 0.5V      |  |

| Maximum overshoot area above VDDQ (See Figure below)  | 0.38 V-ns     | 0.28 V-ns | 0.23 V-ns | 0.23 V-ns |  |

| Maximum undershoot area below VSSQ (See Figure below) | 0.38 V-ns     | 0.28 V-ns | 0.23 V-ns | 0.23 V-ns |  |

AC overshoot and undershoot definition for clock, data, strobe, and mask pins

## **Output Buffer Characteristics**

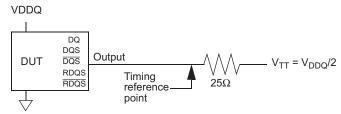

#### **Output AC Test Conditions**

| Symbol | Parameter                                 | SSTL_18    | Units | Notes |

|--------|-------------------------------------------|------------|-------|-------|

| VOTR   | Output Timing Measurement Reference Level | 0.5 x VDDQ | V     | 1     |

#### **Output DC Current Drive**

| Symbol  | Parameter                        | SSTL_18 | Units | Notes   |

|---------|----------------------------------|---------|-------|---------|

| IOH(dc) | Output Minimum Source DC Current | - 13.4  | mA    | 1, 3, 4 |

| IOL(dc) | Output Minimum Sink DC Current   | 13.4    | mA    | 2, 3, 4 |

#### Notes:

- 1. VDDQ = 1.7 V; VOUT = 1420 mV. (VOUT VDDQ)/IOH must be less than 21 Ω for values of VOUT between VDDQ and VDDQ 280 mV.

- 2. VDDQ = 1.7 V; VOUT = 280 mV. VOUT/IOL must be less than 21 Ω for values of VOUT between 0 V and 280 mV.

- 3. The dc value of VREF applied to the receiving device is set to VTT

- 4. The values of IOH(dc) and IOL(dc) are based on the conditions given in Notes 1 and 2. They are used to test device drive current capability to ensure VIH min plus a noise margin and VIL max minus a noise margin are delivered to an SSTL\_18 receiver. The actual current values are derived by shifting the desired driver operating point (see Section 3.3 of JESD8-15A) along a 21 Ω load line to define a convenient driver current for measurement.

#### **OCD Default Characteristics**

| Description                                    | Parameter | Min                                              | Nom | Max | Unit | Notes       |

|------------------------------------------------|-----------|--------------------------------------------------|-----|-----|------|-------------|

| Output impedance                               |           | See full strength default driver characteristics |     |     | Ω    | 1           |

| Output impedance step size for OCD calibration |           | 0                                                |     | 1.5 | Ω    | 6           |

| Pull-up and pull-down mismatch                 |           | 0                                                |     | 4   | Ω    | 1,2,3       |

| Output slew rate                               | Sout      | 1.5                                              |     | 5   | V/ns | 1,4,5,7,8,9 |

#### Notes:

- 1. Absolute Specifications (TOPER; VDD = +1.8V ±0.1V, VDDQ = +1.8V ±0.1V). DRAM I/O specifications for timing, voltage, and slew rate are no longer applicable if OCD is changed from default settings.

- Impedance measurement condition for output source dc current: VDDQ = 1.7 V; VOUT = 1420 mV; (VOUTVDDQ)/IOH must be less than 23.4 Ω for values of VOUT between VDDQ and VDDQ 280 mV. Impedance measurement condition for output sink dc current: VDDQ = 1.7 V; VOUT = 280 mV; VOUT/IOL must be less than 23.4 Ω for values of VOUT between 0 V and 280 mV.

- 3. Mismatch is absolute value between pull-up and pull-down, both are measured at same temperature and voltage.

- 4. Slew rate measured from VIL(ac) to VIH(ac).

- 5. The absolute value of the slew rate as measured from DC to DC is equal to or greater than the slew rate as measured from AC to AC. This is guaranteed by design and characterization.

- 6. This represents the step size when the OCD is near 18  $\Omega$  at nominal conditions across all process corners/variations and represents only the DRAM uncertainty. A 0  $\Omega$  value (no calibration) can only be achieved if the OCD impedance is 18  $\Omega$  +/-0.75  $\Omega$  under nominal conditions.

- 7. DRAM output slew rate specification applies to 400 MT/s, 533 MT/s & 667 MT/s speed bins.

- 8. Timing skew due to DRAM output slew rate mis-match between DQS / DQS and associated DQ's is included in tDQSQ and tQHS specification.

- 9. DDR2 SDRAM output slew rate test load is defined in General Note 3 of the AC Timing specification Table.

## **IDD Specifications & Test Conditions**

| Symbol   | Conditions                                                                                               |                        |     | -25E          | -3D           | -37C          | -5B           | Units |

|----------|----------------------------------------------------------------------------------------------------------|------------------------|-----|---------------|---------------|---------------|---------------|-------|

| - Cymbol | Conditions                                                                                               |                        |     | DDR2-<br>800E | DDR2-<br>667D | DDR2-<br>533C | DDR2-<br>400B |       |

| IDD0     | Operating one bank active-precharge current;                                                             |                        |     |               |               |               |               |       |

|          | tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRASmin(IDD);<br>CKE is HIGH, CS is HIGH between valid commands;  |                        | x8  | 155           | 135           | 120           | 110           | mA    |

|          | Address bus inputs are SWITCHING; Data bus inputs are SV                                                 | WITCHING               | x16 | 155           | 135           | 120           | 110           | 1117  |

| IDD1     | Operating one bank active-read-precharge current;                                                        | viioiiiiva             | 710 | 100           | 100           | 120           | 110           |       |

| 1001     | IOUT = $0mA$ ; BL = 4, CL = $CL(IDD)$ , AL = 0;                                                          |                        |     |               |               |               |               |       |

|          | tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRC tRCD(IDD);                                     | CD =                   |     |               |               |               |               | mA    |

|          | CKE is HIGH, CS is HIGH between valid commands;                                                          |                        | х8  | 190           | 180           | 145           | 115           |       |

|          | Address bus inputs are SWITCHING; Data pattern is same a                                                 | s IDD4W                | x16 | 170           | 140           | 135           | 115           |       |

| IDD2P    | Precharge power-down current; All banks idle; tCK = tCK(IDD); CKE is LOW;                                |                        |     |               |               |               |               |       |

|          | Other control and address bus inputs are STABLE;                                                         |                        |     | 5             | 5             | 5             | 5             | mA    |

|          | Data bus inputs are FLOATING                                                                             |                        |     |               |               |               |               |       |

| IDD2Q    | Precharge quiet standby current; All banks idle;<br>tCK = tCK(IDD);                                      |                        |     |               |               |               |               |       |

|          | CKE is HIGH, CS is HIGH; Other control and address bus inp                                               | outs are               |     |               |               |               |               |       |

|          | STABLE;                                                                                                  |                        | х8  | 80            | 70            | 60            | 50            | mA    |

|          | Data bus inputs are FLOATING                                                                             |                        | x16 | 80            | 70            | 60            | 50            |       |

| IDD2N    | Precharge standby current; All banks idle; tCK = tCK(IDD);                                               |                        |     |               |               |               |               |       |

|          | CKE is HIGH, CS is HIGH; Other control and address bus inp<br>SWITCHING;                                 | outs are               | х8  | 105           | 95            | 75            | 65            | mA    |

|          | Data bus inputs are SWITCHING                                                                            |                        | x16 | 105           | 95            | 75            | 65            |       |

| IDD3P    | Active power-down current; All banks open;<br>tCK = tCK(IDD); CKE is LOW;                                | Power Dov<br>Fast Exit | vn  | 55            | 50            | 40            | 35            | mA    |

|          | Other control and address bus inputs are STABLE; Data bus inputs are FLOATING                            | Power Dov<br>Slow Exit | vn  | 5             | 5             | 5             | 5             |       |

| IDD3N    | Active standby current; All banks open;                                                                  |                        |     |               |               |               |               |       |

|          | tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD);                                                     |                        | 0   | 100           | 440           | 0.5           | 75            | mA    |

|          | CKE is HIGH, CS is HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data | hua inputa             | x8  | 130           | 110           | 95            | 75            |       |

|          | are SWITCHING                                                                                            | bus inputs             | x16 | 130           | 110           | 95            | 75            |       |

| IDD4W    | Operating burst write current; All banks open, Continuous bu                                             |                        |     |               |               |               |               |       |

|          | BL = 4, $CL = CL(IDD)$ , $AL = 0$ ; $tCK = tCK(IDD)$ , $tRAS = tRAS$                                     | max(IDD),              |     |               |               |               |               | mA    |

|          | tRP = tRP(IDD);                                                                                          |                        |     |               |               |               |               |       |

|          | CKE is HIGH, CS is HIGH between valid commands;                                                          |                        | x8  | 385           | 330           | 270           | 210           |       |

## IS43/46DR83200A, IS43/46DR16160A

## **IDD Specifications & Test Conditions (continued)**

| Symbol | Conditions                                                                                                                                                                                                            |     | -25E | -3D           | -37C          | -5B           | Units |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------|---------------|---------------|-------|

|        |                                                                                                                                                                                                                       |     |      | DDR2-<br>667D | DDR2-<br>533C | DDR2-<br>400B |       |

| IDD4R  | Operating burst read current; All banks open, Continuous burst reads, IOUT = 0 mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS is HIGH between valid commands; | x8  | 345  | 300           | 240           | 190           | mA    |

|        | Address bus inputs are SWITCHING; Data pattern is same as IDD4W                                                                                                                                                       | x16 | 310  | 275           | 240           | 190           |       |

| IDD5B  | Burst refresh current; tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval;                                                                                                                                   |     |      |               |               |               | mA    |

|        | CKE is HIGH, CS is HIGH between valid commands; Other control and address bus inputs are SWITCHING;                                                                                                                   | х8  | 255  | 245           | 220           | 200           |       |

|        | Data bus inputs are SWITCHING                                                                                                                                                                                         | x16 | 210  | 195           | 180           | 170           |       |

| IDD6   | Self refresh current;<br>CK and CK at 0 V; CKE ≤ 0.2 V;                                                                                                                                                               |     |      |               |               |               |       |

|        | Other control and address bus inputs are FLOATING;                                                                                                                                                                    | х8  | 9    | 9             | 9             | 9             | mA    |

|        | Data bus inputs are FLOATING                                                                                                                                                                                          | x16 | 3    | 3             | 3             | 3             |       |

| IDD7   | Operating bank interleave read current; All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = $tRCD(IDD) - 1 \times tCK(IDD)$ ;                                                                         |     |      |               |               |               |       |

|        | tCK = tCK(IDD), tRC = tRC(IDD), tRRD = tRRD(IDD),<br>tRCD = 1 x tCK(IDD);                                                                                                                                             | x8  | 290  | 280           | 270           | 265           | mA    |

|        | CKE is HIGH, CS is HIGH between valid commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R;                                                                                        | x16 | 290  | 280           | 270           | 265           |       |

#### Notes:

- 1. IDD specifications are tested after the device is properly initialized

- 2. Input slew rate is specified by AC Parametric Test Condition

- 3. IDD parameters are specified with ODT disabled.

- 4. Data bus consists of DQ, DM, DQS,  $\overline{DQS}$ , RDQS,  $\overline{RDQS}$ , LDQS,  $\overline{LDQS}$ , UDQS, and  $\overline{UDQS}$ . IDD values must be met with all combinations of EMR(1) bits 10 and 11.

- 5. For DDR2-667/800 testing, tCK in the Conditions should be interpreted as tCK(avg)

- 6. For A2 temperature grade with Ta > 85°C, IDD2P and IDD3P (slow) are derated to 60% above the values shown, and IDD6 is derated to x2 above the values shown.

- 7. Definitions for IDD

$LOW = Vin \le VILAC(max)$

$HIGH = Vin \ge VIHAC(min)$

STABLE = inputs stable at a HIGH or LOW level

FLOATING = inputs at VREF = VDDQ/2

SWITCHING = inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control signals, and inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.

## **IDD** testing parameters

| Speed            | DDR2-800 | DDR2-667 | DDR2-533 | DDR2-400 | Units |

|------------------|----------|----------|----------|----------|-------|

| Bin(CL-tRCD-tRP) | 6-6-6    | 5-5-5    | 4-4-4    | 3-3-3    |       |

| CL(IDD)          | 6        | 5        | 4        | 3        | tCK   |

| tRCD(IDD)        | 15       | 15       | 15       | 15       | ns    |

| tRC(IDD)         | 60       | 60       | 60       | 55       | ns    |

| tRRD(IDD)        | 7.5      | 7.5      | 7.5      | 7.5      | ns    |

| tCK(IDD)         | 2.5      | 3        | 3.75     | 5        | ns    |

| tRASmin(IDD)     | 45       | 45       | 45       | 40       | ns    |

| tRASmax(IDD)     | 70       | 70       | 70       | 70       | μs    |

| tRP(IDD)         | 15       | 15       | 15       | 15       | ns    |

| tRFC(IDD)        | 75       | 75       | 75       | 75       | ns    |

## **Input/Output Capacitance:**

| Parameter                                          | Symbol | DDR  | 2-400 | DDR  | 2-667 | DDR  | 2-800 | Units |

|----------------------------------------------------|--------|------|-------|------|-------|------|-------|-------|

|                                                    |        | DDR  | 2-553 |      |       |      |       |       |

|                                                    |        | Min. | Max.  | Min. | Max   | Min. | Max.  |       |

| Input capacitance, CK and CK                       | CCK    | 1.0  | 2.0   | 1.0  | 2.0   | 1.0  | 2.0   | pF    |

| Input capacitance delta, CK and CK                 | CDCK   | _    | 0.25  | _    | 0.25  | _    | 0.25  | pF    |

| Input capacitance, all other input-only pins       | CI     | 1.0  | 2.0   | 1.0  | 2.0   | 1.0  | 1.75  | рF    |

| Input capacitance delta, all other input-only pins | CDI    | ı    | 0.25  | ı    | 0.25  | _    | 0.25  | pF    |

| Input/output capacitance, DQ, DM, DQS, DQS         | CIO    | 2.5  | 4.0   | 2.5  | 3.5   | 2.5  | 3.5   | pF    |

| Input/output capacitance delta, DQ, DM, DQS, DQS   | CDIO   | _    | 0.5   | _    | 0.5   | _    | 0.5   | pF    |

## **Electrical Characteristics & AC Timing Specifications**

Refresh parameters (TOPER; VDDQ = 1.8 V +/- 0.1 V; VDD = 1.8 V +/- 0.1 V)

| Parameter                              |       | Symbol            |     | Units | Notes |

|----------------------------------------|-------|-------------------|-----|-------|-------|

| Refresh to active/Refresh command time | tRFC  |                   | 75  | ns    | 1     |

|                                        |       | -40°C ≤ Tc < 0°C  | 7.8 | μs    | 1,2   |

| Average periodic refresh interval      | tREFI | 0°C ≤ Tc ≤ 85°C   | 7.8 | μs    | 1     |

| Average periodic refresh interval      | INEFI | 85°C < Tc ≤ 95°C  | 3.9 | μs    | 1,2   |

|                                        |       | 95°C < Tc ≤ 105°C | 3.9 | μs    | 1,2,3 |

#### Notes:

- 1. If refresh timing is violated, data corruption may occur and the data must be re-written with valid data before a valid READ can be executed.

- 2. Specified for Industrial and Automotive grade only; not applicable for Commercial grade. TOPER may not be violated.

- 3. Specified for Automotive grade (A2) only; not applicable for any other grade. TOPER may not be violated.

## **Key Timing Parameters by Speed Grade**

|                   | -25E      | -3D       | -37C      | -5B       |

|-------------------|-----------|-----------|-----------|-----------|

| Speed bin (JEDEC) | DDR2-800E | DDR2-667D | DDR2-533C | DDR2-400B |

| CL-tRCD-tRP       | 6-6-6     | 5-5-5     | 4-4-4     | 3-3-3     |

| tRCD              | 15        | 15        | 15        | 15        |

| tRP               | 15        | 15        | 15        | 15        |

| tRC               | 60        | 60        | 60        | 55        |

| tRAS              | 45        | 45        | 45        | 40        |

| tCK(avg)@CL=3     | 5         | 5         | 5         | 5         |

| tCK(avg)@CL=4     | 3.75      | 3.75      | 3.75      | 5         |

| tCK(avg)@CL=5     | 3         | 3         | _         | _         |

| tCK(avg)@CL=6     | 2.5       | _         | _         | _         |

#### Notes:

1. Speed grade options -37C, -3D, and -25E are backward compatible with all the timing specifications for slower grades.

## IS43/46DR83200A, IS43/46DR16160A

**Timing Parameters by Speed Grade (DDR2-400 and DDR2-533)** (For information related to the entries in this table, refer to both the Guidelines and the Specific Notes following this Table.)

| Downstan                                                  | 0          | DDR2              | 2-400   | DDR2-             | 553        | Her!s-   | NI a t a                  |

|-----------------------------------------------------------|------------|-------------------|---------|-------------------|------------|----------|---------------------------|

| Parameter                                                 | Symbol     | Min.              | Max.    | Min.              | Max        | Units    | Notes                     |

| Clock cycle time, CL=x                                    | tCK(avg)   | 5000              | 8000    | 3750              | 8000       | ps       | 35, 36                    |

| CK HIGH pulse width                                       | tCH(avg)   | 0.48              | 0.52    | 0.48              | 0.52       | tCK(avg) | 35, 36                    |

| CK LOW pulse width                                        | tCL(avg)   | 0.48              | 0.52    | 0.48              | 0.52       | tCK(avg) | 35, 36                    |

| DQS latching rising transitions to associated clock edges | tDQSS      | - 0.25            | 0.25    | - 0.25            | 0.25       | tCK(avg) | 30                        |

| DQS falling edge to CK setup time                         | tDSS       | 0.2               | _       | 0.2               | _          | tCK(avg) | 30                        |

| DQS falling edge hold time from CK                        | tDSH       | 0.2               | _       | 0.2               | _          | tCK(avg) | 30                        |

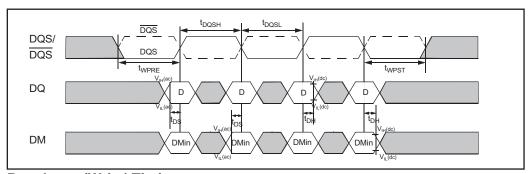

| DQS input HIGH pulse width                                | tDQSH      | 0.35              | _       | 0.35              | _          | tCK(avg) |                           |

| DQS input LOW pulse width                                 | tDQSL      | 0.35              | _       | 0.35              | _          | tCK(avg) |                           |

| Write preamble                                            | tWPRE      | 0.35              | _       | 0.35              | _          | tCK(avg) |                           |

| Write postamble                                           | tWPST      | 0.4               | 0.6     | 0.4               | 0.6        | tCK(avg) | 10                        |

| Address and control input setup time                      | tIS(base)  | 350               | _       | 250               | _          | ps       | 5, 7, 9,<br>22, 29        |

| Address and control input hold time                       | tIH(base)  | 475               | _       | 375               | -          | ps       | 5, 7, 9,<br>23, 29        |

| Control & Address input pulse width for each input        | tIPW       | 0.6               | _       | 0.6               | _          | tCK(avg) |                           |

| DQ and DM input setup time (differential strobe)          | tDS(base)  | 150               | _       | 100               | -          | ps       | 6, 7, 8,<br>20, 28,<br>31 |

| DQ and DM input hold time (differential strobe)           | tDH(base)  | 275               | _       | 225               | -          | ps       | 6, 7, 8<br>21, 28<br>31   |

| DQ and DM input setup time (single-ended strobe)          | tDS1(base) | 25                | _       | - 25              | _          | ps       | 6, 7, 8,<br>25            |

| DQ and DM input hold time (single-ended strobe)           | tDH1(base) | 25                | -       | - 25              | _          | ps       | 6, 7, 8,<br>26            |

| DQ and DM input pulse width for each input                | tDIPW      | 0.35              | _       | 0.35              | _          | tCK(avg) |                           |

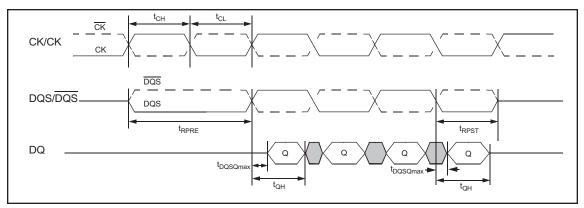

| DQ output access time from CK/CK                          | tAC        | - 600             | + 600   | - 500             | + 500      | ps       | 40                        |

| DQS output access time from CK/ CK                        | tDQSCK     | - 500             | + 500   | - 450             | + 450      | ps       | 40                        |

| Data-out high-impedance time from CK/ CK                  | tHZ        | _                 | tAC max | _                 | tAC<br>max | ps       | 18, 40                    |

| DQS(DQS) low-impedance time from CK/ CK                   | tLZ(DQS)   | tAC min           | tAC max | tAC min           | tAC<br>max | ps       | 18, 40                    |

| DQ low-impedance time from CK/ CK                         | tLZ(DQ)    | 2 x tAC<br>min    | tAC max | 2 x tAC<br>min    | tAC<br>max | ps       | 18, 40                    |

| DQS-DQ skew for DQS and associated DQ signals             | tDQSQ      | _                 | 350     | -                 | 300        | ps       | 13                        |

| CK half pulse width                                       | tHP        | min (tCL,<br>tCH) | -       | min (tCL,<br>tCH) | -          | ps       | 11,12                     |

| DQ hold skew factor                                       | tQHS       | _                 | 450     | _                 | 400        | ps       | 12                        |

| DQ/DQS output hold time from DQS                          | tQH        | tHP -<br>tQHS     | _       | tHP - tQHS        | _          | ps       |                           |

| Read preamble                                             | tRPRE      | 0.9               | 1.1     | 0.9               | 1.1        | tCK(avg) | 19, 41                    |

| Read postamble                                            | tRPST      | 0.4               | 0.6     | 0.4               | 0.6        | tCK(avg) | 19, 42                    |

## Timing Parameters by Speed Grade (DDR2-400 and DDR2-533) cont'd

(For information related to the entries in this table, refer to both the Guidelines and the Specific Notes following this Table.)

| Parameter                                                         | Symbol | DDI         | R2-400                 | DD           | R2-533                   | Units  | Notes         |

|-------------------------------------------------------------------|--------|-------------|------------------------|--------------|--------------------------|--------|---------------|

| raidificter                                                       | Symbol | Min.        | Max.                   | Min.         | Max.                     | Office | Notes         |

| Active to active command period                                   | tRRD   | 7.5         | _                      | 7.5          | _                        | ns     | 4, 32         |

| CAS to CAS command delay                                          | tCCD   | 2           | _                      | 2            | _                        | tCK    |               |

| Write recovery time                                               | tWR    | 15          | _                      | 15           | _                        | ns     | 32            |

| Auto precharge write recovery + precharge time                    | tDAL   | WR + tRP    | _                      | WR + tRP     | _                        | tCK    | 14            |

| Internal write to read command delay                              | tWTR   | 10          | _                      | 7.5          | _                        | ns     | 24, 32        |

| Internal read to precharge command delay                          | tRTP   | 7.5         | _                      | 7.5          | _                        | ns     | 3, 32         |

| CKE minimum pulse width (HIGH and LOW pulse width)                | tCKE   | 3           | _                      | 3            | _                        | tCK    | 27            |

| Exit self refresh to a non-read command                           | tXSNR  | tRFC + 10   | _                      | tRFC + 10    | _                        | ns     | 32            |

| Exit self refresh to a read command                               | tXSRD  | 200         | -                      | 200          | _                        | tCK    |               |

| Exit precharge power down to any non-<br>read command             | tXP    | 2           | _                      | 2            | _                        | tCK    |               |

| Exit active power down to read command                            | tXARD  | 2           | _                      | 2            | _                        | tCK    | 1             |

| Exit active power down to read command (slow exit, lower power)   | tXARDS | 6 - AL      | _                      | 6 - AL       | _                        | tCK    | 1, 2          |

| ODT turn-on delay                                                 | tAOND  | 2           | 2                      | 2            | 2                        | tCK    | 16            |

| ODT turn-on                                                       | tAON   | tAC(min)    | tAC(max)+1             | tAC(min)     | tAC (max)+1              | ns     | 6, 16,<br>40  |

| ODT turn-on (Power-Down mode)                                     | tAONPD | tAC(min)+2  | 2 x tCK + tAC(max)+1   | tAC(min) + 2 | 2 x tCK + tAC(max)+1     | ns     |               |

| ODT turn-off delay                                                | tAOFD  | 2.5         | 2.5                    | 2.5          | 2.5                      | tCK    | 17, 44        |

| ODT turn-off                                                      | tAOF   | tAC(min)    | tAC(max) + 0.6         | tAC(min)     | tAC(max) + 0.6           | ns     | 17, 43,<br>44 |

| ODT turn-off (Power-Down mode)                                    | tAOFPD | tAC(min)+2  | 2.5 x tCK + tAC(max)+1 | tAC(min)+2   | 2.5 x tCK+<br>tAC(max)+1 | ns     |               |

| ODT to power down entry latency                                   | tANPD  | 3           | _                      | 3            | -                        | tCK    |               |

| ODT power down exit latency                                       | tAXPD  | 8           | _                      | 8            | _                        | tCK    |               |

| Mode register set command cycle time                              | tMRD   | 2           | _                      | 2            | _                        | tCK    |               |

| MRS command to ODT update delay                                   | tMOD   | 0           | 12                     | 0            | 12                       | ns     |               |

| OCD drive mode output delay                                       | tOIT   | 0           | 12                     | 0            | 12                       | ns     | 32            |

| Minimum time clocks remains ON after CKE asynchronously drops LOW | tDelay | tlS+tCK+tlH | -                      | tIS+tCK+tIH  | _                        | ns     | 15            |

## Timing Parameters by Speed Grade (DDR2-667 and DDR2-800)

(For information related to the entries in this table, refer to both the Guidelines and the Specific Notes following this Table.)

| P                                                         |           | DDR2                           | -667    | DDR2-                          | 800         | 11. 11   | NI.                   |

|-----------------------------------------------------------|-----------|--------------------------------|---------|--------------------------------|-------------|----------|-----------------------|