Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 1Gb (x16, x32) Mobile LPDDR2 S4 SDRAM

#### **AUGUST 2014**

#### **FEATURES**

- Low-voltage Core and I/O Power Supplies

VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V,

VDD1 = 1.70-1.95V

- High Speed Un-terminated Logic(HSUL\_12) I/O Interface

- Clock Frequency Range: 10MHz to 400MHz (data rate range: 20Mbps to 800 Mbps per I/O)

- Four-bit Pre-fetch DDR Architecture

- Multiplexed, double data rate, command/address inputs

- · Eight internal banks for concurrent operation

- Bidirectional/differential data strobe per byte of data (DQS/DQS#)

- Programmable Read/Write latencies(RL/WL) and burst lengths(4,8 or 16)

- · Per-bank refresh for concurrent operation

- ZQ Calibration

- On-chip temperature sensor to control self refresh rate

- Partial –array self refresh(PASR) Bank & Segment masking

- Deep power-down mode(DPD)

- Operation Temperature

Commercial (Tc = 0°C to 85°C)

Industrial (Tc = -40°C to 85°C)

Automotive, A1 (Tc = -40°C to 85°C)

Automotive, A2 (Tc = -40°C to 105°C)

#### **OPTIONS**

- Configuration:

- 64Mx16 (8M x 16 x 8 banks)

- 32Mx32 (4M x 32 x 8 banks)

#### Package:

- 134-ball BGA for x16 / x32

- 168-ball PoP BGA for x32

#### **DESCRIPTION**

The IS43/46LD16640A/32320A is 1,073,741,824 bits CMOS Mobile Double Data Rate Synchronous DRAMs organized as 8 banks (S4). The deviceis organized as 8 banks of 8Meg words of 16bits or 4Meg words of 32bits. This product uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 4N prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. This product offers fully synchronous operations referenced to both rising and falling edges of the clock. The data paths are internally pipelined and 4n bits prefetched to achieve very high bandwidth.

#### **ADDRESS TABLE**

| Parameter        | 32Mx32  | 64Mx16  |

|------------------|---------|---------|

| Row Addresses    | R0-R12  | R0-R12  |

| Column Addresses | C0-C8   | C0-C9   |

| Bank Addresses   | BA0-BA2 | BA0-BA2 |

| Refresh Count    | 4K      | 4K      |

#### **KEY TIMING PARAMETERS**

| Speed<br>Grade | Data<br>Rate<br>(Mb/s) | Write<br>Latency | Read<br>Latency | tRCD/<br>tRP |

|----------------|------------------------|------------------|-----------------|--------------|

| -25            | 800                    | 3                | 6               | Typical      |

| -3             | 667                    | 2                | 5               | Typical      |

**Note**: Other clock frequencies/data rates supported; please refer to AC timing tables.

Copyright © 2014 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution. Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

#### **BALL ASSIGNMENTS AND DESCRIPTIONS**

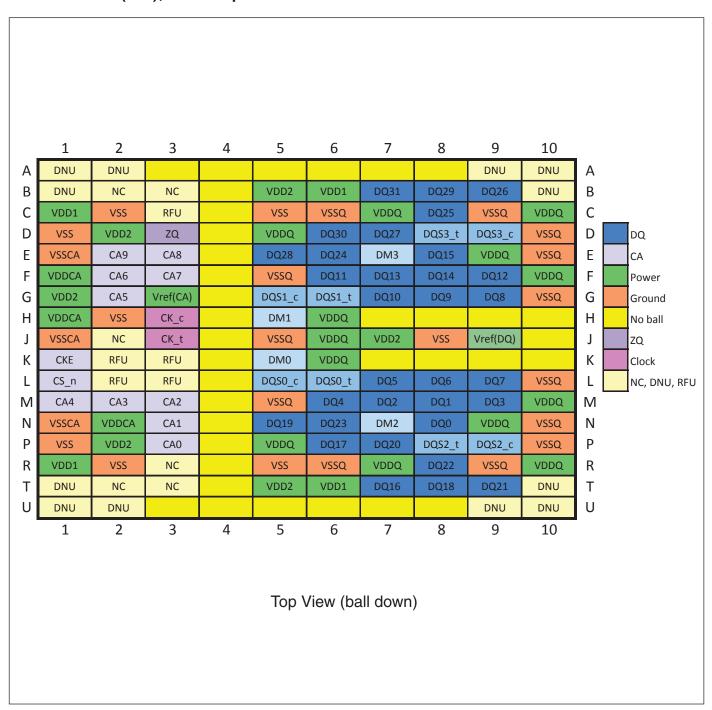

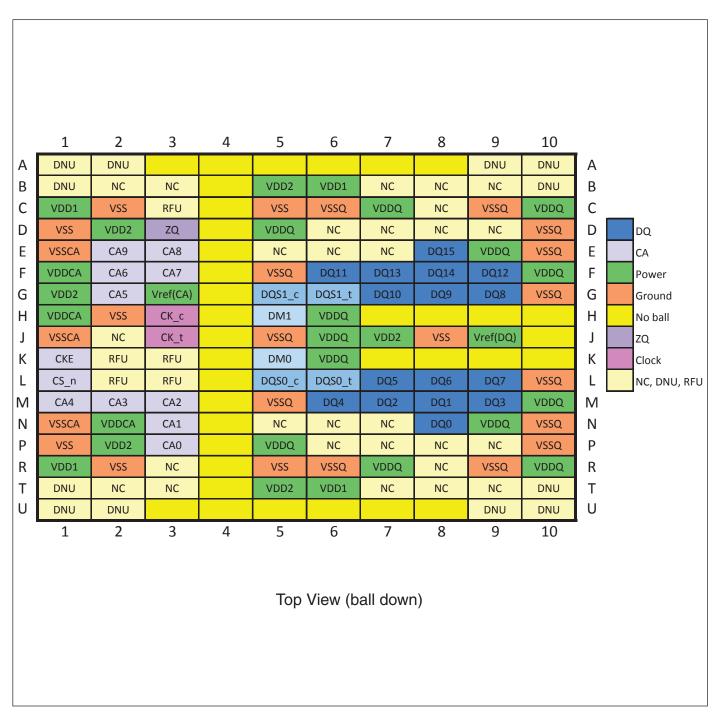

### 134-ball FBGA (x32), 0.65mm pitch

#### **BALL ASSIGNMENTS AND DESCRIPTIONS**

### 134-ball FBGA (x16), 0.65mm pitch

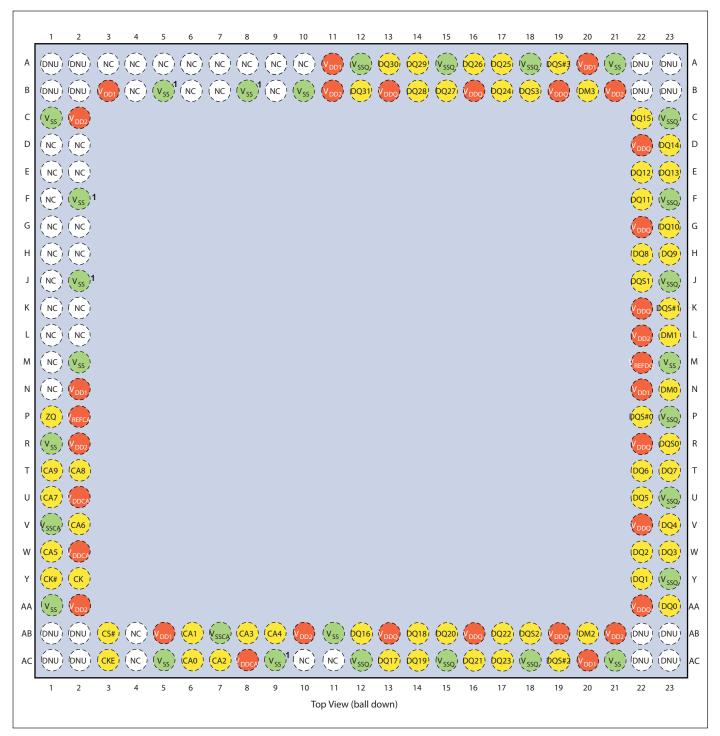

# 168-ball FBGA - 12mm x 12mm (x32), 0.5mm pitch

#### Note:

- 1. Balls labeled Vss¹ (at coordinates B5, B8, F2, J2, AC9) may be connected to Vss or left unconnected.

- 2. Balls indicated as (NC) are no connects.

# INPUT/OUTPUT FUNCTIONAL DESCRIPTION

# **Pad Definition and Description**

| Name                                                                                                   | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                                                                                             | Input | Clock: CK_t and CK_c are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled on both positive and negative edge of CK_t. Single Data Rate (SDR) inputs, CS_n and CKE, are sampled at the positive Clock edge. Clock is defined as the differential pair, CK_t and CK_c. The positive Clock edge is defined by the crosspoint of a rising CK_t and a falling CK_c. The negative Clock edge is defined by the crosspoint of a falling CK_t and a rising CK_c.                                                                                                                                                          |

| CKE                                                                                                    | Input | Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals and therefore device input buffers and output drivers. Power savings modes are entered and exited through CKE transitions.  CKE is considered part of the command code. See Command Truth Table for command code descriptions.  CKE is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                                   |

| CS_n                                                                                                   | Input | Chip Select: CS_n is considered part of the command code. See Command Truth Table for command code descriptions. CS_n is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CA0 - CA9                                                                                              | Input | DDR Command/Address Inputs: Uni-directional command/address bus inputs. CA is considered part of the command code. See Command Truth Table for command code descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DQ0 - DQ15<br>(x16)<br>DQ0 - DQ31<br>(x32)                                                             | I/O   | Data Inputs/Output: Bi-directional data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DQS0_t,<br>DQS0_c,<br>DQS1_t,<br>DQS1_c<br>(x16)<br>DQS0_t -<br>DQS3_t,<br>DQS0_c -<br>DQS3_c<br>(x32) | I/O   | Data Strobe (Bi-directional, Differential): The data strobe is bi-directional (used for read and write data) and differential (DQS_t and DQS_c). It is output with read data and input with write data. DQS_t is edge-aligned to read data and centered with write data.  For x16, DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7; DQS1_t and DQS1_c to the data on DQ8 - DQ15.  For x32 DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7, DQS1_t and DQS1_c to the data on DQ8 - DQ15, DQS2_t and DQS2_c to the data on DQ16 - DQ23, DQS3_t and DQS3_c to the data on DQ24 - DQ31.                                              |

| DM0-DM1<br>(x16)<br>DM0 - DM3<br>(x32)                                                                 | Input | Input Data Mask: For LPDDR2 devices that do not support the DNV feature, DM is the input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS_t. Although DM is for input only, the DM loading shall match the DQ and DQS_t (or DQS_c).  DM0 is the input data mask signal for the data on DQ0-7. For x16 and x32 devices, DM1 is the input data mask signal for the data on DQ8-15. For x32 devices, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is the input data mask signal for the data on DQ24-31. |

| Name                 | Туре   | Description                                                                                                                            |

|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD1}$            | Supply | Core Power Supply 1                                                                                                                    |

| $V_{DD2}$            | Supply | Core Power Supply 2                                                                                                                    |

| $V_{\rm DDCA}$       | Supply | Input Receiver Power Supply: Power supply for CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.                                          |

| $V_{DDQ}$            | Supply | I/O Power Supply: Power supply for Data input/output buffers.                                                                          |

| V <sub>REF(CA)</sub> | Supply | Reference Voltage for CA Command and Control Input Receiver: Reference voltage for all CA0-9, CKE, CS_n, CK_t, and CK_c input buffers. |

| V <sub>REF(DQ)</sub> | Supply | Reference Voltage for DQ Input Receiver: Reference voltage for all Data input buffers.                                                 |

| $V_{SS}$             | Supply | Ground                                                                                                                                 |

| V <sub>SSCA</sub>    | Supply | Ground for Input Receivers                                                                                                             |

| $V_{SSQ}$            | Supply | I/O Ground                                                                                                                             |

| ZQ                   | I/O    | Reference Pin for Output Drive Strength Calibration                                                                                    |

NOTE 1 Data includes DQ and DM.

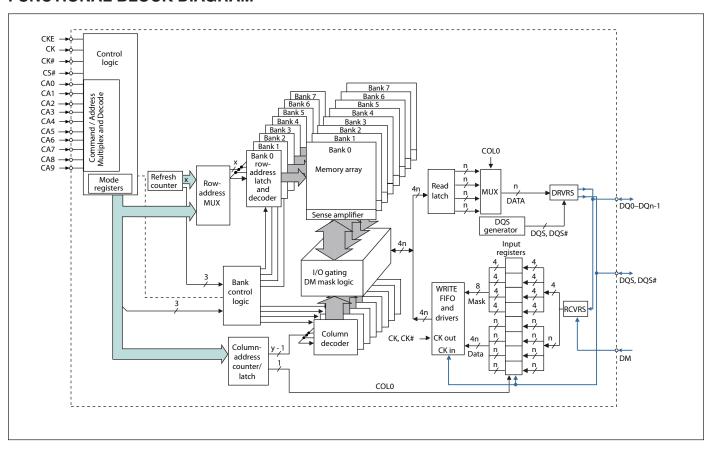

#### **FUNCTIONAL BLOCK DIAGRAM**

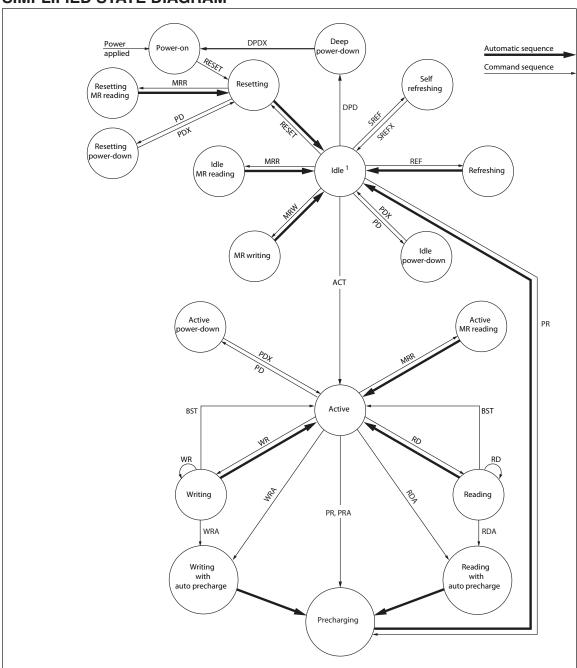

### SIMPLIFIED STATE DIAGRAM

| Abbreviation | Function                      | Abbreviation | Function                      | Abbreviation | Function           |

|--------------|-------------------------------|--------------|-------------------------------|--------------|--------------------|

| ACT          | Active                        | PD           | Enter Power Down              | REF          | Refresh            |

| RD(A)        | Read (w/ Autopre-<br>charge)  | PDX          | Exit Power Down               | SREF         | Enter self refresh |

| WR(A)        | Write (w/ Autopre-<br>charge) | DPD          | Enter Deep Power Down         | SREFX        | Exit self refresh  |

| PR(A)        | Precharge (All)               | DPDX         | Exit Deep Power Down          |              |                    |

| MRW          | Mode Register Write           | BST          | Burst Terminate               |              |                    |

| MRR          | Mode Register Read            | RESET        | Reset is achieved through MRW | command      |                    |

**Note**: For LPDDR2-S4 SDRAM in the idle state, all banks are precharged.

#### **FUNCTIONAL DESCRIPTION**

LPDDR2-S4 is a high-speed SDRAM device internally configured as an 8-Bank memory. This device contains 1,073,741,824 bits (1 Gigabit)

All LPDDR2 devices use a double data rate archiecture on the Command/Address (CA) bus to reduce the number of input pins in the system. The 10-bit CA bus contains command, address, and Bank/Row Buffer information. Each command uses one clock cycle, during which command information is transferred on both the positive and negative edge of the clock.

This LPDDR2-S4 device also uses a double data rate architecture on the DQ pins to achieve high speed operation. The double data rate architecture is essentially a 4n prefetch architecture with an interface designed to transfer two data bits per DQ every clock cycle at the I/O pins. A single read or write access for the memory device effectively consists of a single 4n-bit wide, one clock cycle data transfer at the internal SDRAM core and four corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

Read and write accesses to the LPDDR2 are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

Accesses begin with the registration of an Activate command, which is then followed by a Read or Write command. The address and BA bits registered coincident with the Activate command are used to select the row and the Bank to be accessed. The address bits registered coincident with the Read or Write command are used to select the Bank and the starting column location for the burst access.

Prior to normal operation, the LPDDR2 must be initialized. The following section provides detailed information covering device initialization, register definition, command description and device operation.

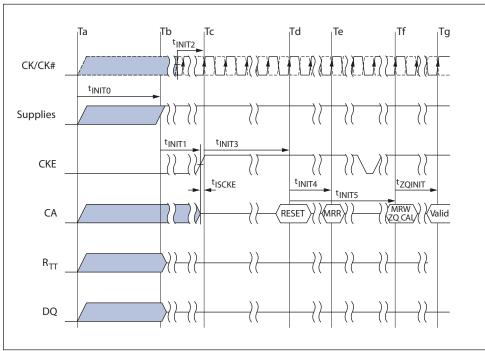

#### POWER-UP AND INITIALIZATION

DDR2 SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation.

The following sequence is required for Power-up and Initialization.

#### 1. Voltage ramp up sequence is required :

A. While applying power, attempt to maintain CKE below 0.2 x VDDCA and all other inputs must be between VILmin and VIHmax. The device outputs remain at High-Z while CKE is held LOW. The voltage ramp time tINIT0 (Tb-Ta) must be no greater than 20 ms from Tb which is point for all supply and reference voltage are within their defined operating ranges, to Ta which is point for any power supply first reaches 300mV.

B. The following conditions apply for voltage ramp after Ta is reached,

- VDD1 must be greater than VDD2-200mV AND

- VDD1 and VDD2 must be greater than VDDCA-200mV AND

- VDD1 and VDD2 must be greater than VDDQ-200mV AND

- VREF must always be less than all other supply voltages

- The voltage difference between any of VSS, VSSQ, and VSSCA pins must not exceed 100mV

#### 2. Start clock and maintain stable condition.

Beginning at Tb, CKE must remain LOW for at least tINIT1 = 100 ns, after which CKE can be asserted HIGH. The clock must be stable at least tINIT2 = 5 × tCK prior to the first CKE LOW-to-HIGH transition (Tc). CKE, /CS, and CA inputs must observe setup and hold requirements (tIS, tIH) with respect to the first rising clock edge (and to subsequent falling and rising edges).

Once the ramping of the supply voltages is complete (Tb), CKE must be maintained LOW. DQ, DM, DQS and DQS# voltage levels must be between VSSQ and VDDQ during voltage ramp to avoid latchup. CK, /CK, /CS, and CA input levels must be between VSSCA and VDDCA during voltage ramp to avoid latch-up

If any Mode Register Read (MRRs) are issued, the clock period must be within the range defined for tCKb (18ns to 100ns). Mode Register Write (MRWs) can be issued at normal clock frequencies as long as all AC timings are met. Some AC parameters could have relaxed timings before the system is appropriately configured. While keeping CKE HIGH, NOP commands must be issued for at least tINIT3 = 200µs (Td).

#### 3. RESET Command

After tINIT3 is satisfied, the MRW RESET command must be issued (Td).

An optional PRECHARGE ALL command can be issued prior to the MRW RESET command. Wait at least tINIT4 while keeping CKE asserted and issuing NOP commands

#### 4. Mode Register Reads and Device Auto Initialization (DAI) Polling:

After tINIT4 is satisfied (Te), only MRR commands and power-down entry/exit commands are supported. After Te, CKE can go LOW in alignment with power-down entry and exit specifications.

Use the MRR command to poll the DAI bit and report when device auto initialization is complete; otherwise, the controller must wait a minimum of tINIT5, or until the DAI bit is set before proceeding.

As the memory output buffers are not properly configured by Te, some AC parameters must have relaxed timings before the system is appropriately configured. After the DAI bit (MR0, DAI) is set to zero by the memory device (DAI complete), the device is in the idle state (Tf). DAI status can be determined by issuing the MRR command to MR0. The device sets the DAI bit no later than tINIT5 after the RESET command. The controller must wait at least tINIT5 or until the DAI bit is set before proceeding

#### 5. ZQ Calibration

After tINIT5 (Tf), the MRR initialization calibration (ZQ\_CAL) command can be issued to the memory (MR10). This command is used to calibrate output impedance over process, voltage, and temperature. In systems where more than one LPDDR2 device exists on the same bus, the controller must not overlap MRR ZQ\_CAL commands. The device is ready for normal operation after tZQINIT.

#### 6. Normal Operation

After tZQINIT (Tg), MRW commands must be used to properly configure the memory . Specifically, MR1, MR2, and MR3 must be set to configure the memory for the target frequency and memory configuration After the initialization sequence is complete, the device is ready for any valid command. After Tg, the clock frequency can be changed using the procedure described in Input Clock Frequency Changes and Clock Stop EventsII.

#### **INITIALIZATION TIMING**

| Symbol  | Parameter                                                                         | Val | ue  | Unit |

|---------|-----------------------------------------------------------------------------------|-----|-----|------|

|         |                                                                                   | min | max |      |

| tINIT0  | Maximum Power Ramp Time                                                           | -   | 20  | ms   |

| tINIT1  | Minimum CKE low time after completion of power ramp                               | 100 | -   | ns   |

| tINIT2  | Minimum stable clock before first CKE high                                        | 5   | -   | tCK  |

| tINIT3  | Minimum idle time after first CKE assertion                                       | 200 | -   | us   |

| tINIT4  | Minimum idle time after Reset command, this time will be about 2 x tRFCab + tRPab | 1   | -   | us   |

| tINIT5  | Maximum duration of Device Auto-Initialization                                    | -   | 10  | us   |

| tCKb    | Clock cycle time during boot                                                      | 18  | 100 | ns   |

| tZQINIT | ZQ initial calibration                                                            | 1   | -   | us   |

Figure - Power Ramp and Initialization Sequence

#### Initialization After RESET (without voltage ramp):

If the RESET command is issued before or after the power-up initialization sequence, the re-initialization procedure must begin at Td

#### **Power-Off Sequence**

Use the following sequence to power off the device. Unless specified otherwise, this procedure is mandatory and applies to S4 devices.

While powering off, CKE must be held LOW (≤ 0.2 × VDDCA); all other inputs must be between VILmin and VIHmax. The device outputs remain at High-Z while CKE is held LOW.

DQ, DM, DQS, and /DQS voltage levels must be between VSSQ and VDDQ during the power-off sequence to avoid latch-up. CK, /CK, /CS, and CA input levels must be between VSSCA and VDDCA during the power-off sequence to avoid latch-up.

Tx is the point where any power supply drops below the minimum value specified in the DC operating condition table.

Tz is the point where all power supplies are below 300mV. After Tz, the device is powered off

Required Power Supply Conditions Between Tx and Tz:

- VDD1 must be greater than VDD2 200mV

- VDD1 must be greater than VDDCA 200mV

- VDD1 must be greater than VDDQ 200mV

- VREF must always be less than all other supply voltages

The voltage difference between VSS, VSSQ, and VSSCA must not exceed 100mV.

For supply and reference voltage operating conditions, see Recommended DC Operating Conditions table.

#### **Uncontrolled Power-Off Sequence**

When an uncontrolled power-off occurs, the following conditions must be met:

- 1.At Tx, when the power supply drops below the minimum values specified, all power supplies must be turned off and all power-supply current capacity must be at zero, except for any static charge remaining in the system.

- 2.After Tz , the device must power off. The time between Tx and Tz must not exceed 20ms. During this period, the relative voltage between power supplies is uncontrolled. VDD1 and VDD2 must decrease with a slope lower than  $0.5 \text{ V/}\mu\text{s}$  between Tx and Tz.

An uncontrolled power-off sequence can occur a maximum of 400 times over the life of the device

#### **Mode Register Definition**

LPDDR2 devices contain a set of mode registers used for programming device operating parameters, reading device information and status, and for initiating special operations such as DQ calibration, ZQ calibration, and device reset.

# **Mode Register Assignment**

The MRR command is used to read from a register. The MRW command is used to write to a register.

| Mode Reg | gister Assignr                   | nent            |                         |                     |           |      |          |           |      |         |     |  |

|----------|----------------------------------|-----------------|-------------------------|---------------------|-----------|------|----------|-----------|------|---------|-----|--|

| MR#      | MA <7:0>                         | Function        | Access                  | OP7                 | OP6       | OP5  | OP4      | OP3       | OP2  | OP1     | OP0 |  |

| 0        | 00 <sub>H</sub>                  | Device Info.    | R                       |                     |           | (RF  | U)       | 1         |      | DI      | DAI |  |

| 1        | 01н                              | Device Feature1 | W                       | nW                  | 'R (for A | AP)  | WC       | ВТ        |      | BL      |     |  |

| 2        | 02 <sub>H</sub>                  | Device Feature2 | W                       |                     | (RF       | RL 8 | RL & WL  |           |      |         |     |  |

| 3        | 03н                              | I/O Config-1    | I/O Config-1 W (RFU) DS |                     |           |      |          |           |      |         |     |  |

| 4        | 04н                              | Refresh Rate    | R                       | TUF (RFU)           |           |      |          |           |      | fresh R | ate |  |

| 5        | 05 <sub>H</sub>                  | Basic Config-1  | R                       | LPDDR2 Manufacturer |           |      |          |           |      | er ID   |     |  |

| 6        | 06н                              | Basic Config-2  | R                       |                     |           |      | Revisi   | on ID1    |      |         |     |  |

| 7        | 07н                              | Basic Config-3  | R                       |                     |           |      | Revisi   | on ID2    |      |         |     |  |

| 8        | 08 <sub>H</sub>                  | Basic Config-4  | R                       | I/O w               | vidth     |      | Den      | sity      |      | Ту      | ре  |  |

| 9        | 09н                              | Test Mode       | W                       |                     |           | Vend | or-Spec  | ific Test | Mode | •       |     |  |

| 10       | 0A <sub>H</sub>                  | IO Calibration  | W                       |                     |           | (    | Calibrat | ion Cod   | е    |         |     |  |

| 11~15    | 0B <sub>H</sub> ~0F <sub>H</sub> | (reserved)      |                         | (RFU)               |           |      |          |           |      |         |     |  |

| Mode Reg | jister Assignr                   | ment       |        |              |     |     |      |      |     |     |     |

|----------|----------------------------------|------------|--------|--------------|-----|-----|------|------|-----|-----|-----|

| MR#      | MA <7:0>                         | Function   | Access | OP7          | OP6 | OP5 | OP4  | OP3  | OP2 | OP1 | OP0 |

| 16       | 10 <sub>H</sub>                  | PASR_BANK  | W      |              |     |     | Bank | Mask |     |     |     |

| 17       | 11 <sub>H</sub>                  | PASR_Seg   | W      | Segment Mask |     |     |      |      |     |     |     |

| 18-19    | 12 <sub>н</sub> -13 <sub>н</sub> | (Reserved) |        |              |     |     | (R   | FU)  |     |     |     |

| Mode Reg | ister Assignr                    | nent                      |         |     |       |          |            |          |         |          |     |

|----------|----------------------------------|---------------------------|---------|-----|-------|----------|------------|----------|---------|----------|-----|

| MR#      | MA <7:0>                         | Function                  | Access  | ОР7 | OP6   | OP5      | OP4        | OP3      | OP2     | OP1      | OP0 |

| 20-31    | 18 <sub>H</sub> -1F <sub>H</sub> | Reserved                  |         |     |       | <u>'</u> | <u>'</u>   |          |         |          |     |

| Mode Reg | ister Assignr                    | ment (Reset Command & RF  | U part) |     |       |          |            |          |         |          |     |

| MR#      | MA <7:0>                         | Function                  | Access  | ОР7 | OP6   | OP5      | OP4        | ОР3      | OP2     | OP1      | OP0 |

| 32       | 20н                              | DQ calibration pattern A  | R       |     | See " | Data Ca  | alibration | n Patter | n Desci | ription" |     |

| 33-39    | 21 <sub>H</sub> -27 <sub>H</sub> | (Do Not Use)              |         |     |       |          |            |          |         |          |     |

| 40       | 28н                              | DQ calibration pattern B  | R       |     | See " | Data Ca  | alibration | n Patter | n Desci | ription" |     |

| 41-47    | 29 <sub>н</sub> -2F <sub>н</sub> | (Do Not Use)              |         |     |       |          |            |          |         |          |     |

| 48-62    | 30 <sub>н</sub> -3Е <sub>н</sub> | (Reserved)                |         |     |       |          | (RI        | FU)      |         |          |     |

| 63       | 3F <sub>н</sub>                  | Reset                     | W       |     |       |          | 2          | X        |         |          |     |

| 64-126   | 40 <sub>н</sub> -7Е <sub>н</sub> | (Reserved)                |         |     |       |          | (RI        | FU)      |         |          |     |

| 127      | 7F <sub>H</sub>                  | (Do Not Use)              |         |     |       |          |            |          |         |          |     |

| 128-190  | 80 <sub>H</sub> -BE <sub>H</sub> | (Reserved for Vendor Use) |         |     |       |          | (RI        | FU)      |         |          |     |

| 191      | BF <sub>H</sub>                  | (Do Not Use)              |         |     |       |          |            |          |         |          |     |

| 192-254  | С0 <sub>н</sub> -FЕ <sub>н</sub> | (Reserved for Vendor Use) |         |     |       |          | (RI        | FU)      |         |          |     |

| 255      | FF <sub>H</sub>                  | (Do Not Use)              |         |     |       |          |            |          |         |          |     |

- 1. RFU bits shall be set to '0' during Mode Register writes.

- 2.RFU bits shall be read as '0' during Mode Register reads.

- 3.All Mode Registers that are specified as RFU or write-only shall return undefined data when read and DQS shall be toggled.

- 4.All Mode Registers that are specified as RFU shall not be written.

- 5.See Vendor Device Datasheets for details on Vendor Specific Mode Registers.

- 6. Writes to read-only registers shall have no impact on the functionality of the device.

| MR0_D | evice In    | formatio                        | on (MA<    | 7:0> = 0 | )0 <sub>н</sub> ): |      |         |                                        |

|-------|-------------|---------------------------------|------------|----------|--------------------|------|---------|----------------------------------------|

| OP7   | OP6         | OP5                             | OP4        | OP3      | OP2                | OP1  | OP0     |                                        |

|       |             | (RF                             | -U)        |          |                    | DI   | DAI     |                                        |

| 0     | P1          | DI (Dov                         | ice Inforn | action)  |                    | Pose | l-only  | 0 <sub>B</sub> : SDRAM                 |

| O     | F I         | DI (Dev                         | ice inion  | nauon)   |                    | Read | i-Offiy | 1 <sub>B</sub> : Do Not Use            |

| 0     | DΛ          | DAI (Device Auto-Initialization |            |          |                    |      | l-only  | 0 <sub>B</sub> : DAI complete          |

|       | OP0 Status) |                                 |            |          |                    | Read | i-Ority | 1 <sub>B</sub> : DAI still in progress |

| MR1_D | evcie Fe                  | eature 1               | (MA<7: | 0> = 01 | н):   |            |                          |                                                       |

|-------|---------------------------|------------------------|--------|---------|-------|------------|--------------------------|-------------------------------------------------------|

| OP7   | OP6                       | OP5                    | OP4    | OP3     | OP2   | OP1        | OP0                      |                                                       |

| n\    | WR (for A                 | NP)                    | WC     | ВТ      |       | BL         |                          |                                                       |

|       |                           |                        |        |         |       |            |                          | 010 <sub>B</sub> : BL4 (default)                      |

| 0.0   | 40.05                     | DI (D                  | 4  41  | - \     |       | 10/-:4     |                          | 011 <sub>B</sub> : BL8                                |

| OP    | OP<2:0> BL (Burst Length) |                        |        |         |       | VVrite     | e-only                   | 100 <sub>B</sub> : BL16                               |

|       |                           |                        |        |         |       |            |                          | All others: reserved                                  |

| 0     | OP3 BT*1 (Burst Type)     |                        |        |         |       | 10/-:4     |                          | 0 <sub>B</sub> : Sequential (default)                 |

| O     | OP3 BT*1 (Burst Type)     |                        |        | ;)      |       | VVrite     | e-only                   | 1 <sub>B</sub> : Interleaved                          |

| 0     | D4                        | \A\C (\A\              |        |         |       | Write-only |                          | 0 <sub>B</sub> : Wrap (default)                       |

| O     | )P4                       | WC (W                  | rap)   |         |       | VVrite     | e-only                   | 1 <sub>B</sub> : No wrap (allowed for SDRAM BL4 only) |

|       |                           |                        |        |         |       |            |                          | 001 <sub>B</sub> : nWR=3 (default)                    |

|       |                           |                        |        |         |       |            |                          | 010 <sub>B</sub> : nWR=4                              |

|       |                           |                        |        |         |       |            |                          | 011 <sub>B</sub> : nWR=5                              |

| OP    | <7:5>                     | 7:5> nWR <sup>*2</sup> |        |         | Write | e-only     | 100 <sub>B</sub> : nWR=6 |                                                       |

|       |                           |                        |        |         |       |            |                          | 101 <sub>B</sub> : nWR=7                              |

|       |                           |                        |        |         |       |            |                          | 110 <sub>B</sub> : nWR=8                              |

|       |                           |                        |        |         |       |            |                          | All others: reserved                                  |

- BL16, interleaved is not an official combination to be supported.

Programmed value in nWR register is the number of clock cycles which determines when to start internal precharge operation for a write burst with AP enabled. It is determined by RU(tWR/tCK)

| 00 | 00 | 04             | 00             | 14/0 | БТ             | Б. |   | Burst Cycle Number and Burst Address Sequence |   |   |   |   |   |   |   |     |     |     |    |    |    |    |  |  |  |  |  |  |  |  |

|----|----|----------------|----------------|------|----------------|----|---|-----------------------------------------------|---|---|---|---|---|---|---|-----|-----|-----|----|----|----|----|--|--|--|--|--|--|--|--|

| C3 | C2 | C1             | C0             | WC   | ВТ             | BL | 1 | 2                                             | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10  | 11  | 12  | 13 | 14 | 15 | 16 |  |  |  |  |  |  |  |  |

| Х  | х  | 0 <sub>B</sub> | 0 <sub>B</sub> |      |                |    | 0 | 1                                             | 2 | 3 |   |   |   |   |   |     |     |     |    |    |    |    |  |  |  |  |  |  |  |  |

| Х  | х  | 1 <sub>B</sub> | 0в             | wrap | any            |    | 2 | 3                                             | 0 | 1 |   |   |   |   |   |     |     |     |    |    |    |    |  |  |  |  |  |  |  |  |

| х  | х  | х              | 0 <sub>B</sub> |      | 0 <sub>B</sub> |    | 4 |                                               |   |   |   |   |   | 4 | у | y+1 | y+2 | y+3 |    |    |    |    |  |  |  |  |  |  |  |  |

|    |    |                |                | nw   | any            | ny |   |                                               |   |   |   |   |   |   |   |     |     |     |    |    |    |    |  |  |  |  |  |  |  |  |

| C3             | C2             | C1             | C0             | WC   | вт   | BL |   |   |   | Burs | st Cyc | le Nu | ımbe  | r and  | Burs    | t Add | ress | Sequ | ence |    |    |    |

|----------------|----------------|----------------|----------------|------|------|----|---|---|---|------|--------|-------|-------|--------|---------|-------|------|------|------|----|----|----|

| U3             | 62             | Ci             | CU             | WC   | ы    | BL | 1 | 2 | 3 | 4    | 5      | 6     | 7     | 8      | 9       | 10    | 11   | 12   | 13   | 14 | 15 | 16 |

| Х              | 0 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> |      |      |    | 0 | 1 | 2 | 3    | 4      | 5     | 6     | 7      |         |       |      |      |      |    |    |    |

| Х              | 0 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |      |      |    | 2 | 3 | 4 | 5    | 6      | 7     | 0     | 1      |         |       |      |      |      |    |    |    |

| Х              | 1 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> |      | seq  |    | 4 | 5 | 6 | 7    | 0      | 1     | 2     | 3      |         |       |      |      |      |    |    |    |

| х              | 1 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> | ron  |      | 8  | 6 | 7 | 0 | 1    | 2      | 3     | 4     | 5      |         |       |      |      |      |    |    |    |

| Х              | 0 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> | wrap |      | 0  | 0 | 1 | 2 | 3    | 4      | 5     | 6     | 7      |         |       |      |      |      |    |    |    |

| Х              | 0 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |      | int  |    | 2 | 3 | 0 | 1    | 6      | 7     | 4     | 5      |         |       |      |      |      |    |    |    |

| Х              | 1 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> |      | IIIL |    | 4 | 5 | 6 | 7    | 0      | 1     | 2     | 3      |         |       |      |      |      |    |    |    |

| х              | 1 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |      |      |    | 6 | 7 | 4 | 5    | 2      | 3     | 0     | 1      |         |       |      |      |      |    |    |    |

| Х              | х              | х              | 0в             | nw   | any  |    |   |   |   |      |        |       | illeg | al (no | t allov | ved)  |      |      |      |    |    |    |

| 0в             | 0в             | 0в             | 0в             |      |      |    | 0 | 1 | 2 | 3    | 4      | 5     | 6     | 7      | 8       | 9     | Α    | В    | С    | D  | Е  | F  |

| 0 <sub>B</sub> | 0 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |      |      |    | 2 | 3 | 4 | 5    | 6      | 7     | 8     | 9      | Α       | В     | С    | D    | Е    | F  | 0  | 1  |

| 0 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> |      |      |    | 4 | 5 | 6 | 7    | 8      | 9     | Α     | В      | С       | D     | E    | F    | 0    | 1  | 2  | 3  |

| 0в             | 1 <sub>B</sub> | 1 <sub>B</sub> | 0в             |      | seq  |    | 6 | 7 | 8 | 9    | Α      | В     | С     | D      | Е       | F     | 0    | 1    | 2    | 3  | 4  | 5  |

| 1 <sub>B</sub> | 0в             | 0в             | 0в             | wrap |      | 16 | 8 | 9 | Α | В    | С      | D     | Е     | F      | 0       | 1     | 2    | 3    | 4    | 5  | 6  | 7  |

| 1 <sub>B</sub> | 0 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |      |      | 10 | Α | В | С | D    | Е      | F     | 0     | 1      | 2       | 3     | 4    | 5    | 6    | 7  | 8  | 9  |

| 1 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> |      |      |    | С | D | Е | F    | 0      | 1     | 2     | 3      | 4       | 5     | 6    | 7    | 8    | 9  | Α  | В  |

| 1 <sub>B</sub> | 1 <sub>B</sub> | 1 <sub>B</sub> | 0в             |      |      |    | Е | F | 0 | 1    | 2      | 3     | 4     | 5      | 6       | 7     | 8    | 9    | Α    | В  | С  | D  |

| х              | х              | х              | 0в             |      | int  |    |   |   |   |      |        |       | illeg | al (no | t allov | ved)  |      |      |      |    |    |    |

| Х              | х              | х              | 0 <sub>B</sub> | nw   | any  |    |   |   |   |      |        |       | illeg | al (no | t allov | ved)  |      |      |      |    |    |    |

- 1. C0 input is not present on CA bus. It is implied zero.

- 2. For BL=4, the burst address represents C1~C0.

- 3. For BL=8, the burst address represents C2~C0.

- 4. For BL=16, the burst address represents C3~C0.

- 5. For no-wrap, BL4, the burst must not cross the page boundary or the sub-page boundary. The variabley can start at any address with C0 equal to 0, but must not start at any address shown below

# **Non-Wrap Restrictions**

| Width | 64Mb           | 128Mb/256Mb              | 512Mb/1Gb/2Gb      | 4Gb/8Gb            |

|-------|----------------|--------------------------|--------------------|--------------------|

|       | Canı           | not cross full page boun | dary               |                    |

| X16   | FE, FF, 00, 01 | 1FE, 1FF, 000, 001       | 3FE, 3FF, 000, 001 | 7FE, 7FF, 000, 001 |

| X32   | 7E, 7F, 00, 01 | FE, FF, 00, 01           | 1FE, 1FF, 000, 001 | 3FE, 3FF, 000, 001 |

|       | Canr           | not cross sub-page bour  | ndary              |                    |

| X16   | 7E, 7F, 80, 81 | 0FE, 0FF, 100, 101       | 1FE, 1FF, 200, 201 | 3FE, 3FF, 400, 401 |

| X32   | none           | none                     | None               | none               |

Note: Non-wrap BL=4 data orders shown are prohibited.

| 1R2_D   | evcie Fe | ature 2                       | (MA<7: | 0> = 02 <sub>1</sub> |                               |      |                               |                                         |

|---------|----------|-------------------------------|--------|----------------------|-------------------------------|------|-------------------------------|-----------------------------------------|

| OP7     | OP6      | OP5                           | OP4    | OP3                  | OP2                           | OP1  | OP0                           |                                         |

|         | (RI      | =U)                           |        |                      | RL 8                          | k WL |                               |                                         |

|         |          |                               |        |                      |                               |      |                               | 0001 <sub>B</sub> : RL3 / WL1 (default) |

|         |          |                               |        |                      | 0010 <sub>B</sub> : RL4 / WL2 |      |                               |                                         |

|         |          |                               |        |                      | Write-only                    |      | 0011 <sub>B</sub> : RL5 / WL2 |                                         |

| OP•     | <3:0>    | RL & WL (Read Latency & Write |        |                      |                               |      | 0100 <sub>B</sub> : RL6 / WL3 |                                         |

| 01 -0.0 |          | Latency                       | /)     |                      |                               |      |                               | 0101 <sub>B</sub> : RL7 / WL4           |

|         |          |                               |        |                      |                               |      |                               | 0110 <sub>B</sub> : RL8 / WL4           |

|         |          |                               |        |                      |                               |      |                               | All others: reserved                    |

| MR3_I/0 | MR3_I/O Configuration 1 (MA<7:0> = 03 <sub>H</sub> ): |                    |           |      |      |        |                                      |                                                |  |  |  |  |  |

|---------|-------------------------------------------------------|--------------------|-----------|------|------|--------|--------------------------------------|------------------------------------------------|--|--|--|--|--|

| ОР7     | OP6                                                   | OP5                | OP4       | ОР3  | OP2  | OP1    | OP0                                  |                                                |  |  |  |  |  |

| (RFU)   |                                                       |                    |           |      |      |        |                                      |                                                |  |  |  |  |  |

|         |                                                       |                    |           |      |      |        |                                      | 0000 <sub>B</sub> : reserved                   |  |  |  |  |  |

|         |                                                       |                    |           |      |      |        | 0001 <sub>B</sub> : 34.3 ohm typical |                                                |  |  |  |  |  |

|         |                                                       | DS (Drive Strength |           |      |      |        |                                      | 0010 <sub>B</sub> : 40.0 ohm typical (default) |  |  |  |  |  |

| OP      | :3:0>                                                 |                    |           | ath) | 41-) |        | e-only                               | 0011 <sub>B</sub> : 48.0 ohm typical           |  |  |  |  |  |

| UF V    | 3.07                                                  | ווט) פט            | ve Strent | gui) |      | vviile | -Orliy                               | 0100 <sub>B</sub> : 60.0 ohm typical           |  |  |  |  |  |

|         |                                                       |                    |           |      |      |        |                                      | 0101 <sub>B</sub> : reserved                   |  |  |  |  |  |

|         |                                                       |                    |           |      |      |        |                                      | 0110 <sub>B</sub> : 80.0 ohm typical           |  |  |  |  |  |

|         |                                                       |                    |           |      |      |        | All others: reserved                 |                                                |  |  |  |  |  |

| MR4_D | R4_Device Temperature (MA<7:0> = 04 <sub>H</sub> ): |                             |                    |  |      |          |                                                      |                                                                                     |  |  |  |  |  |

|-------|-----------------------------------------------------|-----------------------------|--------------------|--|------|----------|------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| OP7   | OP6                                                 | OP6 OP5 OP4 OP3 OP2 OP1 OP0 |                    |  |      |          |                                                      |                                                                                     |  |  |  |  |  |

| TUF   |                                                     | (RI                         | =U)                |  | SDRA | M Refres | h Rate                                               |                                                                                     |  |  |  |  |  |

|       |                                                     |                             |                    |  |      |          |                                                      |                                                                                     |  |  |  |  |  |

|       |                                                     |                             |                    |  |      |          |                                                      | 000 <sub>B</sub> : 4 x t <sub>REFI</sub> , SDRAM Low Temp. operating limit exceeded |  |  |  |  |  |

|       |                                                     |                             |                    |  |      |          | 001 <sub>B</sub> : 4 × tREFI, 4 × tREFIpb, 4 × tREFW |                                                                                     |  |  |  |  |  |

| OP<   | OP<2:0>                                             |                             | SDRAM Refresh Rate |  |      | Read     | d-only                                               | 010 <sub>B</sub> : 2 × tREFI, 2 × tREFIpb, 2 × tREFW,                               |  |  |  |  |  |

|       |                                                     |                             |                    |  |      |          |                                                      | 011 <sub>B</sub> : 1 × tREFI, 1 × tREFIpb, 1 × tREFW (<= 85C)                       |  |  |  |  |  |

|       |                                                     |                             |                    |  |      |          |                                                      | 100 <sub>B</sub> : RFU                                                              |  |  |  |  |  |

|      |                                     |           | 101 <sub>B</sub> : 0.25 × tREFI, 0.25 × tREFIpb, 0.25 × tREFW,                |

|------|-------------------------------------|-----------|-------------------------------------------------------------------------------|

|      |                                     |           | don't re-rate SDRAM AC timing                                                 |

|      |                                     |           | $110_B$ : $0.25 \times t$ REFI, $0.25 \times t$ REFIpb, $0.25 \times t$ REFW, |

|      |                                     |           | derate SDRAM AC timing                                                        |

|      |                                     |           | 111 <sub>B</sub> : SDRAM High temperature operating limit                     |

|      |                                     |           | exceeded                                                                      |

| 0.07 | TUE (Tamana anatuma Um data Ela er) | Dood only | O <sub>B</sub> : (no used)                                                    |

| OP7  | TUF (Temperature Update Flag)       | Read-only | 1 <sub>B</sub> : (always)                                                     |

- 1. A Mode Register Read from MR4 will reset OP7 to "0".

- 2. OP7 is reset to "0" at power-up.

- 3. If OP2 equals "1", the device temperature is greater than 85C.4. OP7 is set to "1", if OP2~OP0 has changed at any time since the last read of MR4.

- 5. LPDDR2 might not operate properly when OP<2:0> = 000B or 111B.

- 6. For specified operating temperature range and maximum operating temperature.

- 7. LPDDR2 devices must be derated by adding 1.875ns to the following core timing parameters: tRCD, tRC, tRAS, tRP, and tRRD. The tDQSCK parameter must be derated Prevailing clock frequency specifications and related setup and hold timings remain unchanged.

- 8. The recommended frequency for reading MR4 is provided in "Temperature Sensor"

| MR5_Ba                  | MR5_Basic Configuration 1 (MA<7:0> = 05 <sub>H</sub> ): |     |         |           |      |        |                                           |  |  |  |  |  |

|-------------------------|---------------------------------------------------------|-----|---------|-----------|------|--------|-------------------------------------------|--|--|--|--|--|

| OP7                     | OP6                                                     | OP5 | OP4     | OP3       | OP2  |        |                                           |  |  |  |  |  |

|                         |                                                         | LPD | DDR2 Ma | nufacture |      |        |                                           |  |  |  |  |  |

| OP<7:0> Manufacturer ID |                                                         |     |         |           | Read | d-only | 0001 1011B: ISSI<br>All Others : Reserved |  |  |  |  |  |

| MR6_Ba               | //R6_Basic Configuration 2 (MA<7:0> = 06 <sub>H</sub> ): |  |        |        |      |        |                                   |  |  |  |  |  |

|----------------------|----------------------------------------------------------|--|--------|--------|------|--------|-----------------------------------|--|--|--|--|--|

| ОР7                  | OP7 OP6 OP5 OP4 OP3 OP2 OP1 OP0                          |  |        |        |      |        |                                   |  |  |  |  |  |

|                      |                                                          |  | Revisi | on ID1 |      |        |                                   |  |  |  |  |  |

| OP<7:0> Revision ID1 |                                                          |  |        |        | Read | d-only | 00000000 <sub>B</sub> : A-version |  |  |  |  |  |

| MR7_Ba               | MR7_Basic Configuration 3 (MA<7:0> = 07 <sub>H</sub> ): |  |        |        |      |        |                                   |  |  |  |  |  |

|----------------------|---------------------------------------------------------|--|--------|--------|------|--------|-----------------------------------|--|--|--|--|--|

| OP7                  | OP7 OP6 OP5 OP4 OP3 OP2 OP1 OP0                         |  |        |        |      |        |                                   |  |  |  |  |  |

|                      |                                                         |  | Revisi | on ID2 |      |        |                                   |  |  |  |  |  |

| OP<7:0> Revision ID2 |                                                         |  |        |        | Read | d-only | 00000000 <sub>B</sub> : A-version |  |  |  |  |  |

| P7    | OP6              | OP5     | OP4 | OP3   | OP2 | OP1  | OP0    |                                      |

|-------|------------------|---------|-----|-------|-----|------|--------|--------------------------------------|

| I/O v | width            |         | De  | nsity | 1   | Ту   | /ре    |                                      |

|       |                  |         |     |       |     |      |        |                                      |

|       |                  |         |     |       |     |      |        | 00 <sub>B</sub> : S4 SDRAM           |

| OD.   | <1:0>            | Tuno    |     |       |     | Door | d-only | 01 <sub>B</sub> : Reserved           |

| OF    | 1.0~             | Type    |     |       |     | Read | a-orny | 10 <sub>B</sub> : Reserved           |

|       |                  |         |     |       |     |      |        | 11 <sub>B</sub> : Reserved           |

|       |                  |         |     |       |     |      |        | 0000 <sub>B</sub> : 64Mb (Reserved)  |

|       |                  |         |     |       |     |      |        | 0001 <sub>B</sub> : 128Mb (Reserved) |

|       |                  |         |     |       |     |      |        | 0010 <sub>B</sub> : 256Mb (Reserved) |

|       |                  |         |     |       |     |      |        | 0011 <sub>B</sub> : 512Mb (Reserved) |

|       |                  |         |     |       |     |      |        | 0100 <sub>B</sub> : <b>1Gb</b>       |

| OP<   | <5:2>            | Density | y   |       |     | Read | d-only | 0101 <sub>B</sub> : 2Gb (Reserved)   |

|       |                  |         |     |       |     |      |        | 0110 <sub>B</sub> : 4Gb (Reserved)   |

|       |                  |         |     |       |     |      |        | 0111 <sub>B</sub> : 8Gb (Reserved)   |

|       |                  |         |     |       |     |      |        | 1000 <sub>B</sub> : 16Gb (Reserved)  |

|       |                  |         |     |       |     |      |        | 1001 <sub>B</sub> : 32Gb (Reserved)  |

|       |                  |         |     |       |     |      |        | All others: reserved                 |

|       |                  |         |     |       |     |      |        | 00 <sub>B</sub> : x32                |

| OD:   | OP<7:6>          |         | lth |       |     | Pos  | d only | 01 <sub>B</sub> : x16                |

| UP    | \1.0 <i>&gt;</i> | I/O wid | iui |       |     | Read | d-only | 10 <sub>B</sub> : x8 (Reserved)      |

|       |                  |         |     |       |     |      |        | 11 <sub>B</sub> : not used           |

| MR9_Te | MR9_Test Mode (MA<7:0> = 09 <sub>H</sub> ): |      |           |            |  |  |  |  |  |  |  |  |

|--------|---------------------------------------------|------|-----------|------------|--|--|--|--|--|--|--|--|

| ОР7    | OP7 OP6 OP5 OP4 OP3 OP2 OP1 OP0             |      |           |            |  |  |  |  |  |  |  |  |

|        |                                             | Vend | dor-speci | fic Test N |  |  |  |  |  |  |  |  |

| MR10_0 | IR10_Calibration (MA<7:0> = 0A <sub>H</sub> ): |                  |           |         |            |     |                         |                                                |  |  |  |  |  |

|--------|------------------------------------------------|------------------|-----------|---------|------------|-----|-------------------------|------------------------------------------------|--|--|--|--|--|

| OP7    | OP6                                            | OP5 OP4 OP3 OP2  |           |         |            | OP1 | OP0                     |                                                |  |  |  |  |  |

|        |                                                |                  | Calibrati | on Code |            |     |                         |                                                |  |  |  |  |  |

|        |                                                |                  |           |         |            |     |                         | 0xFF: Calibration command after initialization |  |  |  |  |  |

|        |                                                |                  |           |         |            |     |                         | 0xAB: Long calibration                         |  |  |  |  |  |

| OP<    | 7:0>                                           | Calibration Code |           |         | Write-only |     | 0x56: Short calibration |                                                |  |  |  |  |  |

|        |                                                |                  |           |         |            |     |                         | 0xC3: ZQ Reset                                 |  |  |  |  |  |

|        |                                                |                  |           |         |            |     |                         | All others: Reserved                           |  |  |  |  |  |

- 1. Host processor shall not write MR10 with "Reserved" values.

- 2. LPDDR2 devices shall ignore calibration command, when a "Reserved" values is written into MR10.

- 3. See AC timing table for the calibration latency.

- 4. If ZQ is connected to VSSCA through RZQ, either the ZQ calibration function (see "MRW ZQ Calibration Command") or default

- calibration (through the ZQ RESET command) is supported. If ZQ is connected to VDDCA, the device opeates with default calibration,

- and ZQ calibration commands are ignored. In both cases, the ZQ connection must not change after power is supplied to the device.

- 5. Devices that do not support calibration ignore the ZQ calibration command.

| MR11:1 | 5_(Rese | erved) (I | /IA<7:0> | > = 0B <sub>H</sub> - | 0F <sub>H</sub> ): |     |     |  |

|--------|---------|-----------|----------|-----------------------|--------------------|-----|-----|--|

| ОР7    | OP6     | OP5       | OP4      | OP3                   | OP2                | OP1 | OP0 |  |

|        |         |           | RI       | FU                    |                    |     |     |  |

| MR16_I | PASR_E                 | Bank Ma | sk (MA<  | <7:0> = ( | 010 <sub>н</sub> ): |     |        |                                                                                           |

|--------|------------------------|---------|----------|-----------|---------------------|-----|--------|-------------------------------------------------------------------------------------------|

| OP7    | OP6                    | OP5     | OP4      | OP3       | OP2                 | OP1 | OP0    |                                                                                           |

|        |                        | Bank    | Mask (4- | Bank or 8 | -Bank)              |     |        |                                                                                           |

| OP<    | OP<7:0> Bank Mask Code |         |          |           |                     |     | e-only | $0_B$ : refresh enable to the bank (=unmasked, default) $1_B$ : refresh blocked (=masked) |

| OP | Bank Mask | 4 Bank | 8 Bank |

|----|-----------|--------|--------|

| 0  | XXXXXXX1  | Bank 0 | Bank 0 |

| 1  | XXXXXX1X  | Bank 1 | Bank 1 |

| 2  | XXXXX1XX  | Bank 2 | Bank 2 |

| 3  | XXXX1XXX  | Bank 3 | Bank 3 |

| 4  | XXX1XXXX  | -      | Bank 4 |

| 5  | XX1XXXXX  | -      | Bank 5 |

| 6  | X1XXXXXX  | -      | Bank 6 |

| 7  | 1XXXXXXX  | -      | Bank 7 |

Note: For 4-bank S4 SDRAM, only OP<3:0> are used.

| MR17_I | R17_PASR_Segment Mask (MA<7:0> = 011 <sub>H</sub> ): |     |       |         |     |  |        |                                                                                           |  |  |  |

|--------|------------------------------------------------------|-----|-------|---------|-----|--|--------|-------------------------------------------------------------------------------------------|--|--|--|

| ОР7    | OP6                                                  | OP5 | OP4   | OP3     | OP2 |  |        |                                                                                           |  |  |  |

|        |                                                      |     | Segme | nt Mask |     |  |        |                                                                                           |  |  |  |

| OP<    | OP<7:0> Segment Mask Code                            |     |       |         |     |  | e-only | $0_B$ : refresh enable to the bank (=unmasked, default) $1_B$ : refresh blocked (=masked) |  |  |  |

| Co aum out | OB | Bank Mask | 1Gb              | 2Gb, 4Gb         | 8Gb    |  |  |  |  |

|------------|----|-----------|------------------|------------------|--------|--|--|--|--|

| Segment    | OP | Dank Wask | R12:10           | R13:11           | R14:12 |  |  |  |  |

| 0          | 0  | XXXXXXX1  |                  | 000 <sub>B</sub> |        |  |  |  |  |

| 1          | 1  | XXXXXX1X  |                  | 001 <sub>B</sub> |        |  |  |  |  |

| 2          | 2  | XXXXX1XX  | 010 <sub>B</sub> |                  |        |  |  |  |  |

| 3          | 3  | XXXX1XXX  |                  | 011 <sub>B</sub> |        |  |  |  |  |

| 4          | 4  | XXX1XXXX  |                  | 100 <sub>B</sub> |        |  |  |  |  |

| 5          | 5  | XX1XXXXX  |                  | 101 <sub>B</sub> |        |  |  |  |  |

| 6          | 6  | X1XXXXXX  |                  | 110 <sub>B</sub> |        |  |  |  |  |

| 7          | 7  | 1XXXXXXX  |                  | 111 <sub>B</sub> |        |  |  |  |  |

**Note**: This table indicates the range of row addresses in each masked segment. X is don't care for a particular segment.

| MR18:1 | 9_(Rese    | erved) (I | /IA<7:0> | > = 012 <sub>H</sub>  | - 013 <sub>H</sub> ):             |      |     |  |  |  |  |  |  |

|--------|------------|-----------|----------|-----------------------|-----------------------------------|------|-----|--|--|--|--|--|--|

| OP7    | OP6        | OP5       | OP4      | OP3                   | OP2                               | OP1  | OP0 |  |  |  |  |  |  |

| OP1    | OPO        | OPS       | 074      | UPS                   | UPZ                               | OFI  | OFU |  |  |  |  |  |  |

|        | RFU        |           |          |                       |                                   |      |     |  |  |  |  |  |  |

|        |            |           |          |                       |                                   |      |     |  |  |  |  |  |  |

| MR20:3 | 1_(Do N    | lot Use)  | (MA<7:   | 0> = 01               | 4 <sub>H</sub> - 01F <sub>H</sub> | ):   |     |  |  |  |  |  |  |

| ОР7    | OP6        | OP5       | OP4      | OP3                   | OP2                               | OP1  | OP0 |  |  |  |  |  |  |

|        |            |           | Do No    | ot Use                |                                   |      |     |  |  |  |  |  |  |

|        |            |           |          |                       |                                   |      |     |  |  |  |  |  |  |

| MR32_( | Do Not     | Use) (M   | A<7:0>   | = 020 <sub>H</sub> ): |                                   |      |     |  |  |  |  |  |  |

|        |            |           |          |                       |                                   | 0.74 | 672 |  |  |  |  |  |  |

| OP7    | OP6        | OP5       | OP4      | OP3                   | OP2                               | OP1  | OP0 |  |  |  |  |  |  |

|        |            |           | Do No    | ot Use                |                                   |      |     |  |  |  |  |  |  |

|        |            |           |          |                       |                                   |      |     |  |  |  |  |  |  |

| MR33:3 | 9_(Do N    | lot Use)  | (MA<7:   | 0> = 02               | 1 <sub>H</sub> - 027 <sub>H</sub> | ):   |     |  |  |  |  |  |  |

| OP7    | OP6        | OP5       | OP4      | OP3                   | OP2                               | OP1  | OP0 |  |  |  |  |  |  |

|        |            |           |          |                       |                                   | _    |     |  |  |  |  |  |  |

|        |            |           | Do No    | ot Use                |                                   |      |     |  |  |  |  |  |  |

|        |            |           |          |                       |                                   |      |     |  |  |  |  |  |  |

| MR40_( | Do Not     | Use) (M   | A<7:0>   | = 028 <sub>H</sub> ): | I                                 | I    |     |  |  |  |  |  |  |

| ОР7    | OP6        | OP5       | OP4      | OP3                   | OP2                               | OP1  | OP0 |  |  |  |  |  |  |

|        |            |           | Do No    | ot Use                |                                   |      |     |  |  |  |  |  |  |

|        |            |           |          |                       |                                   |      |     |  |  |  |  |  |  |

| MR41:4 | 7_(Do N    | lot Use)  | (MA<7:   | 0> = 02               | 9 <sub>H</sub> - 02F <sub>H</sub> | ı):  |     |  |  |  |  |  |  |

| OP7    | OP6        | OP5       | OP4      | OP3                   | OP2                               | OP1  | OP0 |  |  |  |  |  |  |

| _      |            |           |          |                       |                                   | _    |     |  |  |  |  |  |  |

|        | Do Not Use |           |          |                       |                                   |      |     |  |  |  |  |  |  |

| MR48:6 | 2_(Rese | erved) (I | VIA<7:0> | > = 030 <sub>H</sub> | - 03E <sub>н</sub> ): |     |     |  |

|--------|---------|-----------|----------|----------------------|-----------------------|-----|-----|--|

| OP7    | OP6     | OP5       | OP4      | OP3                  | OP2                   | OP1 | OP0 |  |

|        |         |           | RI       | -U                   |                       |     |     |  |

| MR63_F | Reset (N | /IA<7:0> | = 03F <sub>H</sub> ) | : MRW | only |     |     |  |

|--------|----------|----------|----------------------|-------|------|-----|-----|--|

| ОР7    | OP6      | OP5      | OP4                  | OP3   | OP2  | OP1 | OP0 |  |

|        | I        | I        | )                    | Κ     | I    | I   | I   |  |

Note: For additional information on MRW RESET, see "Mode Register Write Command" on Timing Spec.

| MR64:1 | 26_(Res | served) | (MA<7:0 | )> = 040 | <sub>н</sub> - <b>07Е</b> н) | ):  |     |  |

|--------|---------|---------|---------|----------|------------------------------|-----|-----|--|

| OP7    | OP6     | OP5     | OP4     | OP3      | OP2                          | OP1 | OP0 |  |

|        | 1       | 1       | RI      | FU       | ı                            | ı   | 1   |  |

| MR127_ | _(Do No | t Use) (I | MA<7:0> | > = 07F <sub>H</sub> | ):  |     |     |  |

|--------|---------|-----------|---------|----------------------|-----|-----|-----|--|

| OP7    | OP6     | OP5       | OP4     | OP3                  | OP2 | OP1 | OP0 |  |

|        | ı       | ı         | Do No   | ot Use               | ı   | I   |     |  |

| MR128: | 190_(Re | eserved | for Ven | dor Use | e) (MA<7 | ':0> = 08 | 30 <sub>н</sub> - 0ВЕ | :н): |

|--------|---------|---------|---------|---------|----------|-----------|-----------------------|------|

| OP7    | OP6     | OP5     | OP4     | OP3     | OP2      | OP1       | OP0                   |      |

|        | I       | I       | RI      | FU      | I        |           | I                     |      |

| MR191_ | _(Do No | t Use) (I | /IA<7:0> | > = 0BF <sub>+</sub> | <sub>i</sub> ): |     |     |  |

|--------|---------|-----------|----------|----------------------|-----------------|-----|-----|--|

| OP7    | OP6     | OP5       | OP4      | OP3                  | OP2             | OP1 | OP0 |  |

|        |         |           | Do No    | ot Use               |                 |     |     |  |

| MR192:254_(Reserved for Vendor Use) (MA<7:0> = 0C0 <sub>H</sub> - 0FE <sub>H</sub> ): |     |     |     |     |     |     |     |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|--|--|--|

| OP7                                                                                   | OP6 | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 |  |  |  |  |  |  |  |

| RFU                                                                                   |     |     |     |     |     |     |     |  |  |  |  |  |  |  |

| MR255_(Do Not Use) (MA<7:0> = 0FF <sub>H</sub> ): |     |     |       |        |     |     |     |  |  |  |  |  |

|---------------------------------------------------|-----|-----|-------|--------|-----|-----|-----|--|--|--|--|--|

| OP7                                               | OP6 | OP5 | OP4   | OP3    | OP2 | OP1 | OP0 |  |  |  |  |  |

|                                                   | I   |     | Do No | ot Use |     |     |     |  |  |  |  |  |

#### **Truth Tables**

Truth tables provide complementary information to the state diagram. They also clarify device behavior and applicable restrictions when considering the actual state of the banks.

Unspecified operations and timings are illegal. To ensure proper operation after an illegal event, the device must be powered down and then restarted using the specified initialization sequence before normal operation can continue.

#### **Command Truth Table**

Table 49: Command Truth Table

Notes 1–11 apply to all parameters conditions

| Notes 1–11 apply       | Comma    | CA Pins |     |         |     |       |     |     |     |     |          |     |          |            |

|------------------------|----------|---------|-----|---------|-----|-------|-----|-----|-----|-----|----------|-----|----------|------------|

|                        | CKE      |         |     |         |     |       |     |     |     |     |          |     |          | CK         |

| Command                | CK( n-1) | CK( n)  | CS# | CA0     | CA1 | CA2   | CA3 | CA4 | CA5 | CA6 | CA7      | CA8 | CA9      | Edge       |

| MRW                    | Н        | Н       | L   | L       | L   | L     | L   | MA0 | MA1 | MA2 | MA3      | MA4 | MA5      | <b>-</b>   |

|                        | Н        | Н       | Х   | MA6     | MA7 | OP0   | OP1 | OP2 | OP3 | OP4 | OP5      | OP6 | OP7      | 4          |

| MRR                    | Н        | Н       | L   | L       | L   | L     | Н   | MA0 | MA1 | MA2 | MA3      | MA4 | MA5      | <b>-</b>   |

|                        | Н        | Н       | Х   | MA6     | MA7 | X     |     |     |     |     |          |     |          | 7_         |

| REFRESH<br>(per bank)  | Н        | Н       | L   | L       | L   | H L X |     |     |     |     |          |     |          |            |

|                        | Н        | Н       | Х   |         |     | X     |     |     |     |     |          |     |          | 7_         |

| REFRESH<br>(all banks) | Н        | Н       | L   | L       | L   | н н х |     |     |     |     |          |     |          | F          |

|                        | Н        | Н       | Х   |         |     | X     |     |     |     |     |          |     |          |            |

| Enter self<br>refresh  | Н        | L       | L   | L       | L   | Н Х   |     |     |     |     |          |     |          | <u>-</u>   |

|                        | Х        | L       | Х   |         |     | X     |     |     |     |     |          |     | ₹.       |            |

| ACTIVATE               | Н        | Н       | L   | L       | Н   | R8    | R9  | R10 | R11 | R12 | BA0      | BA1 | BA2      | <u>-</u> F |

| (bank)                 | Н        | Н       | Х   | R0      | R1  | R2    | R3  | R4  | R5  | R6  | R7       | R13 | R14      | 7_         |

| WRITE (bank)           | Н        | Н       | L   | Н       | L   | L     | RFU | RFU | C1  | C2  | BA0      | BA1 | BA2      | Ŧ          |

|                        | Н        | Н       | Х   | AP      | C3  | C4    | C5  | C6  | C7  | C8  | C9       | C10 | C11      | ₹.         |

| READ (bank)            | Н        | Н       | L   | Н       | L   | Н     | RFU | RFU | C1  | C2  | BA0      | BA1 | BA2      | <u>-</u> F |