# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ISD2360**

# Digital ChipCorder with Embedded Flash

# **3-Channel Audio Playback**

## TABLE OF CONTENTS

| 1 GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2 FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4              |

| 3 BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 4 PINOUT CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7              |

| 5 PIN DESCRIPTION – QFN32                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| 6 DEVICE OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| <ul> <li>6.1 AUDIO STORAGE</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10<br>10       |

| 7 MEMORY FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 7.1.1       Voice Prompts                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| 8 SPI INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14             |

| 9 SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 10 GPIO VOICE MACRO TRIGGERS                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| <ul> <li>10.1 ASSIGN PLAYBACK CHANNEL FOR THE GPIO TRIGGER</li> <li>10.2 VOICE MACRO EXAMPLES</li> <li>10.2.1 POI/PU/WAKEUP Voice Macros</li> <li>10.2.2 Example: Cycle through a sequence of messages</li> <li>10.2.3 Example: Looping short sounds. Interrupt to stop playback.</li> <li>10.2.4 Example: Uninterruptable Trigger, smooth audio.</li> <li>10.2.5 Example: Continuous Play until re-trigger.</li> <li>10.2.6 Example: Level Hold Trigger.</li> </ul> |                |

| 11 CHANNEL SELECTION AND EXECUTION CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                           | 21             |

| 11.1       SELECT CHANNEL FOR THE PLYABCK AND MIXING                                                                                                                                                                                                                                                                                                                                                                                                                 | 21<br>22       |

| 12 ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| <ul> <li>12.1 OPERATING CONDITIONS</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                         | 23<br>23<br>23 |

# ηυνοτοη

| 12  | 2.4 SPI TIMING             | 25 |

|-----|----------------------------|----|

| 13  | APPLICATION DIAGRAM        |    |

|     | 3.1 SPI MODE APPLICATION   |    |

| 13  | 3.2 STANDALONE APPLICATION | 27 |

|     | PACKAGE SPECIFICATION      | -  |

| ORE | DERING INFORMATION         | 30 |

| 15  | REVISION HISTORY           |    |

### nuvoTon

### **1 GENERAL DESCRIPTION**

The ISD2360 is a 3-channel digital ChipCorder<sup>®</sup> providing single-chip storage and playback of high quality audio. The device features digital de-compression, comprehensive memory management, flash storage, integrated audio signal path with up to 3 channel concurrent playback and Class D speaker driver capable of delivering power of 0.95W. This family utilizes flash memory to provide non-volatile audio playback with duration up to 64 seconds (based on 8kHz/4bit ADPCM compression) for a single-chip audio playback solution.

The ISD2360 can be controlled and programmed through an SPI serial interface or operated standalone by triggers applied to the device's six GPIO pins.

The ISD2360 requires no external clock sources or components except a speaker to deliver quality audio prompts or sound effects to enhance user interfaces.

In addition the part can provide non-volatile flash storage in 1Kbyte sectors eliminating the need for additional serial EEPROM/Flash devices.

Compared to previous ChipCorder series, this device provides higher sampling frequencies, improved SNR, lower power, fast programming time and integrated program verification.

#### 2 FEATURES

- Duration

- o ISD2360 64 seconds based on 8kHz/4bit ADPCM in 2Mbit of flash storage (256KB)

- Audio Management

- Store pre-recorded audio (Voice Prompts) using high guality digital compression

- Use simple index based command for playback no address needed.

- Execute pre-programmed macro scripts (Voice Macros) designed to control the configuration of the device and playback Voice Prompts sequences.

- Path and playback Control

- Up to 3 channel audio streaming can be mixed and played back concurrently

- Each channel has independent counter which enables user micro-management on VM execution

- Mask Jump allows branch execution depending on internal register or external GPIO pin status

- Control

- Serial SPI interface for microprocessor control and programming.

- Stand-alone control where customized Voice Macro scripts are assigned to GPIO trigger pins.

- Sample Rate

- o 7 sampling frequencies 4, 5.3, 6.4, 8, 12.8, 16 and 32 kHz are available.

- Each Voice Prompt can have optimal sample rate.

- Compression Algorithms

- ο μ-Law: 6, 7 or 8 bits per sample

- Differential μ-Law: 6, 7 or 8 bits per sample

- PCM: 8, 10 or 12 bits per sample

- Enhanced ADPCM: 2, 3, 4 or 5 bits per sample

- Variable-bit-rate optimized compression. This allows best possible compression given a metric of SNR and background noise levels.

- Oscillator

- Internal oscillator with internal reference: factory trimmed to ±1% deviation at room temperature.

### nuvoTon

- Output

- $\circ$  PWM: Class D speaker driver to direct drive an 8 $\Omega$  speaker or buzzer.

- Delivers 400mW at 3V supply.

- Delivers 1W at 5V supply

- I/Os

- o SPI interface: MISO, MOSI, SCLK, SSB for commands and digital audio data

- o 6 general purpose I/O pins multiplexed with SPI interface.

- Flash Storage

- 2Mbit of storage for combined audio/data.

- Fast programming time (20µs/byte)

- Erase sector size 1Kbyte, sector erase time 2ms.

- o Integrated memory checksum calculation for fast verification.

- Endurance >100K cycles. Retention > 10 years

- Operating Voltage: 2.4-5.5V

- Package:

- Green, QFN32

- Temperature Options:

- Industrial: -40°C to 85°C

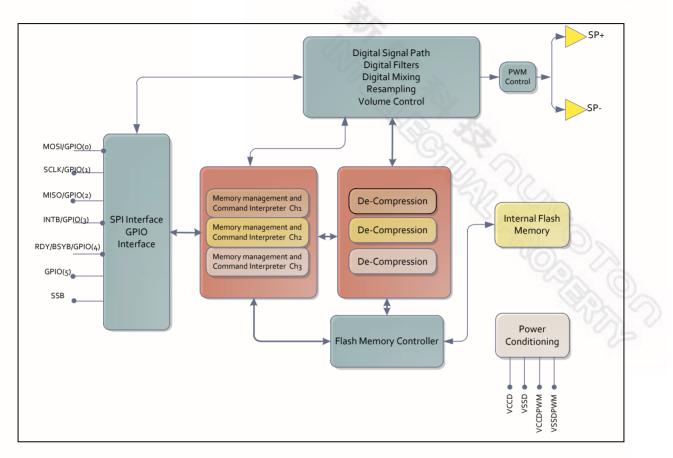

### 3 BLOCK DIAGRAM

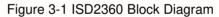

### **4 PINOUT CONFIGURATION**

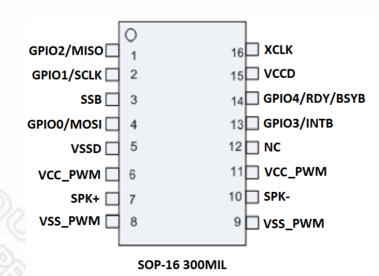

Figure 4-2 ISD2360 16-Lead SOP Pin Configuration.

- 7 -

nuvoTon

| Pin Pin Name I/O Fu<br>Number |                      |     | Function                                                                                                                                                                                                   |  |  |  |  |

|-------------------------------|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 2                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 3                             | MOSI /<br>GPIO0      | I   | Master-Out-Slave-In. Serial input to the ISD2360 from the host.<br>Can be configured as a general purpose I/O pin.                                                                                         |  |  |  |  |

| 4                             | VSSD                 |     | Digital Ground.                                                                                                                                                                                            |  |  |  |  |

| 5                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 6                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 7                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 8                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 9                             | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 10                            | V <sub>CCD</sub> PWM | I   | Digital Power for the PWM Driver.                                                                                                                                                                          |  |  |  |  |

| 11                            | SPK+                 | 0   | PWM driver positive output. This SPK+ output, together with SPK- pin provide a differential output to drive 8Ω speaker or buzzer. During power down this pin is in tri-state.                              |  |  |  |  |

| 12                            | V <sub>SSD</sub> PWM | I   | Digital Ground for the PWM Driver.                                                                                                                                                                         |  |  |  |  |

| 13                            | V <sub>SSD</sub> PWM | I   | Digital Ground for the PWM Driver.                                                                                                                                                                         |  |  |  |  |

| 14                            | SPK-                 | 0   | PWM driver negative output. This SPK- output, together with SPK+ pin, provides a differential output to drive $8\Omega$ speaker or buzzer. During power down this pin is tri-state.                        |  |  |  |  |

| 15                            | V <sub>CCD</sub> PWM | I   | Digital Power for the PWM Driver.                                                                                                                                                                          |  |  |  |  |

| 16                            | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 17                            | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 18                            | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 19                            | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 20                            | NC                   |     | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

| 21                            | INTB /<br>GPIO3      | 0   | Active low interrupt request pin. This pin is an open-drain output.<br>Can be configured as a general purpose I/O pin.                                                                                     |  |  |  |  |

| 22                            | RDY/BSYB /<br>GPIO4  | 0   | An output pin to report the status of data transfer on the SPI interface.<br>"High" indicates that ISD2360 is ready to accept new SPI commands<br>or data. Can be configured as a general purpose I/O pin. |  |  |  |  |

| 23                            | NC                   | (0) | This pin should be left unconnected.                                                                                                                                                                       |  |  |  |  |

#### PIN DESCRIPTION - OFN32 5

- 8 -

### nuvoTon

| Pin<br>Number | Pin Name         | I/O | Function                                                                                                                                                                                                                                                     |

|---------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                         |

| 25            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                         |

| 26            | V <sub>CCD</sub> | I   | Digital Power.                                                                                                                                                                                                                                               |

| 27            | GPIO5            | I/O | General purpose I/O pin                                                                                                                                                                                                                                      |

| 28            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                         |

| 29            | MISO /<br>GPIO2  | 0   | Master-In-Slave-Out. Serial output from the ISD2360 to the host. This pin is in tri-state when SSB=1.<br>Can be configured as a general purpose I/O pin.                                                                                                     |

| 30            | SCLK / GPI1      | I   | Serial Clock input to the ISD2360 from the host.<br>Can be configured as a general purpose input pin.                                                                                                                                                        |

| 31            | SSB              | I   | Slave Select input to the ISD2360 from the host. When SSB is low device is selected and responds to commands on the SPI interface. When asserted, GPIO0/1/2 automatically configure to MOSI/SCLK and MISO respectively. SSB has an internal pull-up to Vccd. |

| 32            | NC               |     | This pin should be left unconnected.                                                                                                                                                                                                                         |

- 2-

### nuvoTon

### 6 DEVICE OPERATION

Playback of audio stored on the ISD2360 can be accomplished by either sending SPI commands via the serial interface or triggered by signal edges applied to GPIO pins. The device is programmed via the SPI interface either in-system or utilizing commercially available gang programmers.

#### 6.1 AUDIO STORAGE

The audio compression and customization of the ISD2360 is rapidly achieved with the supplied ISD2360VPE or Voice Prompt Editor. This software tool allows the developer to take audio clips in standard wave file format and re-sample and compress them for download to the ISD2360.

Audio is stored in the ISD2360 as series of **Voice Prompts**: these units of audio can be of any length – the compression and sample rate of each Voice Prompt can be individually selected. A powerful feature of the ISD2360 is presence of a scripting ability **Voice Macros**. A Voice Macro can contain commands to play individual Voice Prompts and configure the ISD2360. A Voice Macro can be associated with a GPIO pin such that it is triggered by a transition on that pin. In this way stand-alone systems can be developed without the need for micro-controller interaction. Voice Macros can also be executed via the SPI command interface. Both Voice Prompts and Voice Macros are addressed via a simple sequential index address, no absolute memory address is required, thus audio source material or voice macro function can be updated (or changed for multi-language implementation) without the need to update microcontroller code.

#### **6.2 DEVICE CONFIGURATION**

The ISD2360 is configured by writing to a set of configuration registers. This can be accomplished either by sending configuration via the serial SPI interface or executing Voice Macros containing configuration commands. Most configuration registers are reset to their default values when the device is powered down to ensure lowest possible standby current. Exceptions to this are registers that control the configuration of GPIO pins and Jump registers that contain the Voice Macro index to execute for GPIO triggers. Configuration registers may be initialized automatically in customizable Voice Macros that are executed on a power-on reset or power-up condition.

#### **6.3 GPIO CONFIGURATION**

The six GPIO pins of the ISD2360 can be configured for a variety of purposes. Each pin can be configured to trigger a Voice Macro function. Each pin also has an alternate function allowing the pins to be configured as SPI, interrupt or oscillator reference pins.

### nuvoTon

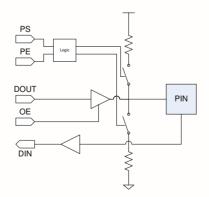

The structure of the GPIO pads is shown in Figure 6-1. Configuration registers allow the user to control pull-up and pull down resistors, enable the pin as an output or set the output value. See ISD2360 Design Guide for details on the configuration options.

### 6.4 OSCILLATOR AND SAMPLE RATES

The ISD2360 has an internal oscillator trimmed at manufacturing that requires no external components to operate. This oscillator provides an internal clock source that operates the ISD2360 at a maximum audio sample rate  $F_{smax}$  of 32kHz. The sample rates available for audio storage at this maximum sample rate are shown in Table 6-1. The sample rate is selected during compression using the ISD2360 Voice Prompt Editor software.

| SR[2:0] | Ratio to F <sub>Smax</sub> | Sample Rate F <sub>5</sub> (kHz) |

|---------|----------------------------|----------------------------------|

| 0       | 8                          | 4                                |

| 1       | 6                          | 5.44                             |

| 2       | 5                          | 6.4                              |

| 3       | 4                          | 8                                |

| 4       | 2.5                        | 12.8                             |

| 5       | 2                          | 16                               |

| 6       | 1                          | 32                               |

| Table 6-1 | Available | Sample | Rates. |

|-----------|-----------|--------|--------|

|-----------|-----------|--------|--------|

### 7 MEMORY FORMAT

The memory of the ISD2360 consists of byte addressable flash memory that is erasable in 1Kbyte sectors. Erased memory has a value of 0xFF. Writing to the memory allows host to change bits from erased '1' state to programmed '0' state.

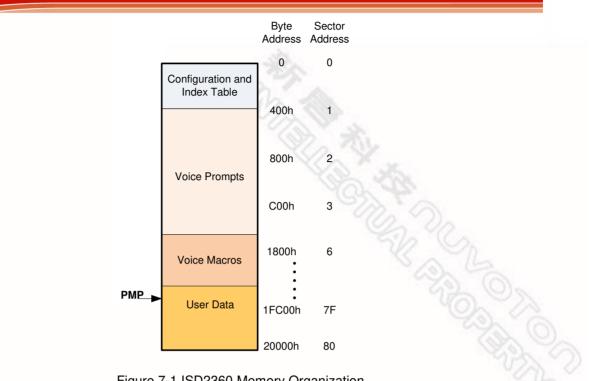

The memory of the ISD2360 is organized into four distinct regions as shown in Figure 7-1. The four regions are:

- 1. **Configuration and Index Table**: The first region of memory contains configuration data for the device and the index table that points to the Voice Prompt and Voice Macro data. The ISD2360VPE creates this section for download to the device.

- 2. Voice Macros: This section contains the script code of all the projects Voice Macros.

- 3. Voice Prompts: This section contains the compressed audio data for all Voice Prompts.

- 4. **User Data**: An optional section containing memory sectors allocated by the developer for generic use by the host controller.

- 11 -

Figure 7-1 ISD2360 Memory Organization

#### 7.1.1 Voice Prompts

NUVOTON

Voice prompts are pre-recorded audio of any length, from short words, phrases or sound effects to long passages of music. These Voice Prompts can be played back in any order as determined by the application. A Voice Prompt consists of two components:

- 1. An index entry in the Index Table pointing to the pre-recorded audio.

- 2. Compressed pre-recorded audio data.

A Voice Prompt is addressed using its index number to locate and play the pre-recorded audio. This address free approach allows users to easily manage the pre-recorded audio without the need to update the code on the host controller. In addition, the users can store a multitude of pre-recorded audio without the overhead of maintaining a complicated lookup table. To assist customers in creating the Voice Prompts, ISD2360 Voice Prompt Editor and writer are available for development purposes.

### 7.1.2 Voice Macros

Voice Macros are a script that allows users to customize their own play patterns such as play Voice Prompts, insert silence, power-down the device and configure the signal path, including volume control. Voice Macros are executed using a single SPI command and are accessed using the same index structure as Voice Prompts. This means that a Voice Macro (or Voice Prompt) can be updated on the ISD2360 without the need to update code on the host micro-controller since absolute addresses are not needed.

The following locations have been reserved for special Voice Macros: Index 0: Power-On Initialization (POI)

### nuvoTon

Index 1: Power-Up (PU) Index 2: GPIO-Wakeup (WAKEUP)

These Voice Macros allow the users to customize the ISD2360 power-on, power-up and GPIO wake-up procedures and are executed automatically when utilized. If these Voice Macros are not used device will perform default operations on these events.

An example to illustrate the usage of the PU Voice Macro is:

- WR\_CFG(VOLC, 0x0C)

- WR\_CFG(REG2, 0x44)

- WR\_CFG (REG\_GPIO\_AF1 ,0xFF)

- WR\_CFG (REG\_GPIO\_AF0 ,0x10)

- FINISH

The above PU Voice Macro will perform the following:

- Choose Volume Control for -3dB level.

- Configure and power up the signal path to decode compressed audio to speaker driver.

- Set up all GPIOs except GPIO4 for Falling edge trigger and set GPIO4 for both falling and rising edge trigger.

The following is the complete list of the command available for use in Voice Macros:

- WR\_CFG\_REG(*reg n*) Set configuration register *reg* to value *n*.

- PWR\_DN Power down the ISD2360.

- PLAY\_VP(*i*) Play Voice Prompt index *i*.

- PLAY\_VP@(Rn) Indirect Play Voice Prompt of index in register Rn

- PLAY\_VP\_LP(*i*,*cnt*) Loop Play Voice Prompt index *i*, *cnt* times.

- PLAY\_VP\_LP@(Rn,cnt) Indirect Loop Play Voice Prompt index in Rn, cnt times.

- EXE\_VM(*i*) Execute Voice Macro index *i*.

- EXE\_VM@(Rn) Indirect Execute Voice Macro index in register Rn

- PLAY\_SIL(*n*) Play silence for *n* units. A unit is 32ms at master sampling rate of 32 kHz.

- WAIT\_INT Wait until current play command finishes before executing next macro instruction.

- FINISH Finish the voice macro and exit.

These commands are equivalent to the commands available via the SPI interface and are described in Section Error! Reference source not found.

### 7.1.3 User Data

User Data consists of 1KByte multiples of erasable sectors allocated by the user. This can be used as generic non-volatile storage by the host application. The developer has the freedom not to allocate or reserve any memory sectors. A software tool, the ISD2360 Voice Prompt Editor is available to assist customers in allocating such memory.

### 7.2 MEMORY CONTENTS PROTECTION

- ; Set VOLC to 0x0C

- ; Set REG2 to 0x44

- ; Set REG\_GPIO\_AF1 to 0xFF

- ; Set REG\_GPIO\_AF0 to 0x10

- ; Exit Voice Macro

### nuvoTon

Under certain circumstances, it is desirable to protect portions of the internal memory from write/erase or interrogation (read). The ISD2360 provides a method to achieve this by setting a protection memory pointer (PMP) that allows the users to protect memory for an address range from the beginning of memory to this sector containing the PMP pointer. The type of protection is set by three bits in the memory header byte.

Memory protection is activated on power-up of the chip. Therefore, each time the user changes the setting of memory protection, the new setting will not be effective until the chip is reset.

### 8 SPI INTERFACE

This is a standard four-wire serial interface used for communication between ISD2360 and the host. It consists of an active low slave-select (SSB), a serial clock (SCLK), a data input (Master Out Slave In - MOSI), and a data output (Master In Slave Out - MISO). In addition, for some transactions requiring data flow control, a RDY/BSYB signal (pin) is available.

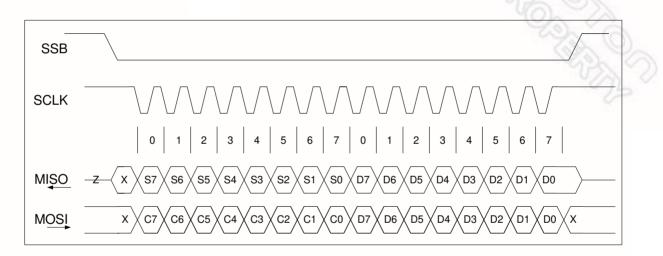

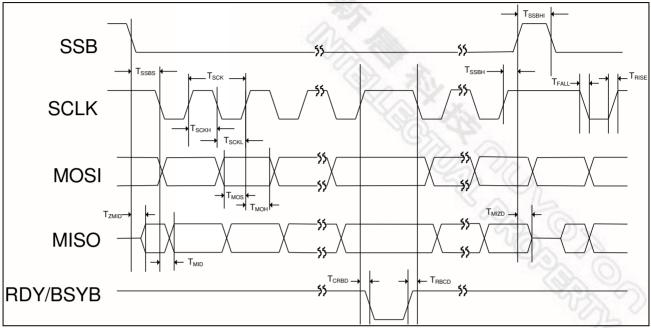

The ISD2360 supports **SPI mode 3:** (1) SCLK must be high when SPI bus is inactive, and (2) data is sampled at SCLK rising edge. A SPI transaction begins on the falling edge of SSB and its waveform is illustrated below:

Figure 8-1 SPI Data Transaction.

A transaction begins with sending a command byte (C7-C0) with the most significant bit (MSB – C7) sent in first. During the byte transmission, the status (S7-S0) of the device is sent out via the MISO pin. After the byte transmission, depending upon the command sent, one or more bytes of data will be sent via the MISO pin.

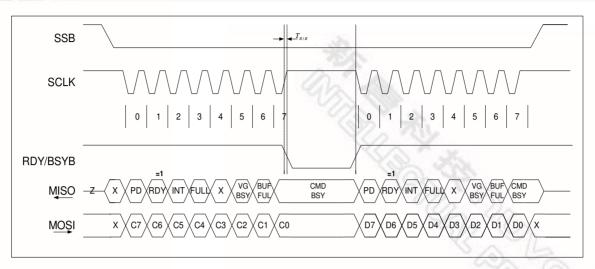

RDY/BSYB pin is used to handshake data into or out of the device. Upon completion of a byte transmission, RDY/BSYB pin could change its state after the rising edge of the SCLK if the built-in 32-byte data buffer is either full or empty. At this point, SCLK must remain high until RDY/BSYB pin returns to high, indicating that the ISD2360 is ready for the next data transmission. See below for timing diagram.

### nuvoTon

Figure 8-2 RDY/BSYB Timing for SPI Writing Transactions.

If the SCLK does not remain high, RDY bit of the status register will be set to zero and be reported via the MISO pin so the host can take the necessary actions (i.e., terminate SPI transmission and retransmit the data when the RDY/BSYB pin returns to high).

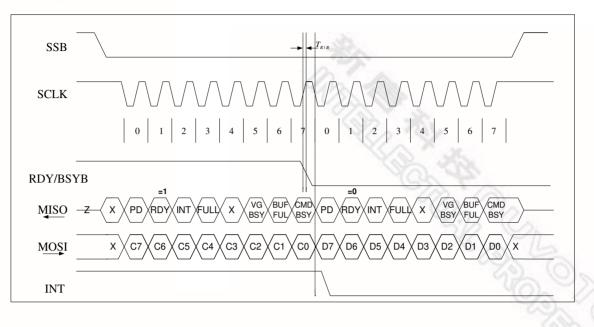

For commands (i.e., DIG\_READ, SPI\_PCM\_READ) that read data from the ISD2360 device, MISO is used to read the data; therefore, the host must monitor the status via the RDY/BSYB pin and take the necessary actions. The INT pin will go low to indicate (1) data overrun/overflow when sending data to the ISD2360; or (2) invalid data from ISD2360. See Figure 8-3 for the timing diagram.

To avoid RDY/BSYB polling for digital operations the following conditions must be met:

- Ensure device is idle (CMD\_BSY=0 in status) before operation.

- Digital Write: Send 32 bytes of data or less in a digital write transaction **or** ensure that there is a 24µs period between each byte sent where SCLK is held high.

- Digital Read: Ensure a 2µs period between last address byte of digital read command and first data byte where SCLK is held high.

- 15 -

gure 8-3 SPI Transaction Ignoring RDY/BSYB

### 9 SIGNAL PATH

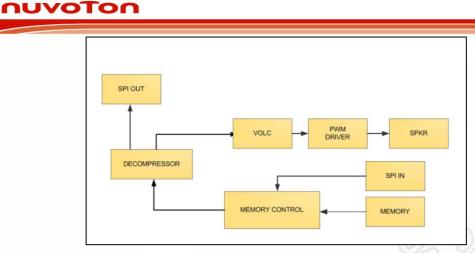

The signal path performs filtering, sample rate conversion, volume control and decompression. A block diagram of the signal path is shown in Figure 9-1. The PWM driver output pins SPK- and SPK+ provide a differential output to drive an  $8\Omega$  speaker or buzzer. During power down these pins are in tristate.

Pre-compressed audio transfers from memory or SPI interface through the de-compressor block to PWM driver or SPI out. The audio level is adjustable via VOLC before going out on to the PWM driver path. The possible path combinations are:

$\mathsf{MEMORY} \to \mathsf{DECOMPRESS} \to \mathsf{SPKR} \ (\mathsf{Playback} \ to \ speaker)$

$MEMORY \rightarrow DECOMPRESS \rightarrow SPI\_OUT (SPI playback)$

SPI\_IN  $\rightarrow$  DECOMPRESS  $\rightarrow$  SPKR (SPI decode to speaker)

For example to playback audio to speaker, enable decompression and PWM (write 0x44 to register 0x02) then send a PLAY\_VP command to play audio.

- 16 -

Figure 9-1 ISD2360 Signal Path

### 10 GPIO VOICE MACRO TRIGGERS

The ISD2360 Voice Macro capability and GPIO flexibility allows the user to configure the device to operate independently of the SPI interface or host micro-controller.

GPIO triggering utilizes the Jump registers R0 through R6. When a GPIO trigger event occurs the ISD2360 executes the Voice Macro whose index is stored in the corresponding Jump register: that is GPIO0 will execute the VM whose index is stored in R0, GPIO1 in R1 etc. The initial values of the R0-R6 registers can be set up in the POI Voice macro which is executed when a power-on reset condition is detected. When the ISD2360 responds to a trigger event, if a Voice Macro is currently being executed, that Voice Macro is first stopped before execution of new Voice Macro.

### 10.1 Assign Playback Channel For The GPIO Trigger

For each GPIO pins, Register 0x14 and 0x15 can assign the playback channel for that GPIO. So once triggered, the playback audio streaming will be routed to that channel.

### 10.2 VOICE MACRO EXAMPLES

Below are some useful examples demonstrating the features Voice trigger macros. The example project can be found in the ISD2360VPE distribution as the ISD2360example project.

### 10.2.1 POI/PU/WAKEUP Voice Macros

These special purpose Voice Macros allow the user to configure the ISD2360 for subsequent trigger events. The POI macro is executed when the chip receives an internal power-on reset condition or the SPI SW\_RESET command is sent.

The POI Voice macro is used to configure the ISD2360 for subsequent trigger events, for example:

: Set Volume to 0dB

- a. CFG(REG2, 0x44)

- b. CFG(VOLC, 0x00)

- c. CFG(R5, 0x03)

- d. CFG(R4, 0x07)

- e. CFG(R3, 0x09)

CFG(R2, 0x0a)

; Set Jump register R3 to 0x09, GPIO3 to trigger VM#9

; Configure signal path to playback

- ; Set Jump register R2 to 0x0a, GPIO2 to trigger VM#A

- g. CFG(R1, 0x0c)

f.

; Set Jump register R1 to 0x0c, GPIO1 to trigger VM#C

; Set Jump register R5 to 0x03, GPIO5 to trigger VM#3 ; Set Jump register R4 to 0x07, GPIO4 to trigger VM#7

### nuvoton

- h. CFG(R0, 0x0e)

- ; Set Jump register R0 to 0x0e, GPIO0 to trigger VM#E

- i. PLAY VP(FastBeep) : Play Voice Prompt FastBeep

- CFG(REG GPIO AF1, 0xff) ; Set up GPIOs to trigger off falling edges

- j. k. CFG(REG GPIO AF0, 0x00)

- Ι. PD

: Power Down

This POI macro will initialize the GPIO configuration such that all GPIO triggers are enabled for falling edges and performs initialization of the jump registers to point to appropriate Voice Macros. It also configures the play path and plays a beep. At the end of the macro the chip powers down.

The GPIO WAKEUP is executed whenever the device is triggered from a power down state.

- a. CFG(REG2, 0x44)

- ; Configure signal path to playback b. CFG(VOLC, 0x00) : Set Volume to 0dB

- ; Set Jump register R4 to 0x07, GPIO4 to trigger VM#7 CFG(R4, 0x07) C. d.

- CFG(R2, 0x0a) ; Set Jump register R2 to 0x0a, GPIO2 to trigger VM#A e.

- Finish ; Exit Voice Macro, stay powered up.

This GPIO WAKEUP macro sets up the play path as settings in these registers are reset during power down. It also resets jump registers R4 and R2 to default conditions.

### 10.2.2 Example: Cycle through a sequence of messages.

In this example a high-to-low transition on GPIO5 will initially trigger VM#3 as defined in the POI initialization macro. In VM#3 the Voice Prompt "One" is played and jump register R5 set to VM#4. Thus the next high-to-low transition on GPIO5 will trigger VM#4 and play Voice Prompt "Two". Similarly next trigger will play "Three" then "Four" and back to "One". Notice the difference in VM#4 where a WAIT INTERRUPT command has been inserted before the setting of the jump register. If the GPIO5/SW6 button is pushed rapidly, so that play is interrupted, "Two" will continue to be repeated. Other Voice Macros, because the jump register is changed first, will always progress to the next step in sequence.

| VM#3: R5_Cour | nt_One (GPIO5) |                                                |

|---------------|----------------|------------------------------------------------|

| a.            | CFG(R5, 0x04)  | ; Configure GPIO5 to play VM#4 on next trigger |

| b.            | Play(One)      | ; Play voice prompt "One"                      |

| С.            | PD             | ; Power Down                                   |

VM#4:Two

а.

b.

C.

d.

а

b.

- Play(Two) ; Play voice prompt "Two"

- : Wait until Play finishes Wait Interrupt

- CFG(R5, 0x05) ; Configure GPIO5 to play VM#5 on next trigger

- : Power Down

- VM#5: Three

- CFG(R5, 0x06) а

PD

Play(Three) b. PD

Play(Four)

- ; Play voice prompt "Three" : Power Down

- c. VM#6: Four

- CFG(R5, 0x03) ; Configure GPIO5 to play VM# 3 on next trigger

; Configure GPIO5 to play VM#6 on next trigger

- ; Play voice prompt "Four "

- PD c.

- : Power Down

### nuvoTon

#### 10.2.3 Example: Looping short sounds. Interrupt to stop playback.

This example demonstrates how to loop short sound samples and use a trigger interrupt to stop playback. A trigger on GPIO4 will play a series of Voice Prompts until it is interrupted by another trigger to stop playback. VM#7 was associated with the GPIO4 trigger in the POI routine. The first action of this VM is to change the trigger VM to VM#8, thus if GPIO4 is re-triggered while the Voice Macro is running it will execute the power down voice macro rather than start the play sequence again. The next command sets the LRMP bit of REG1, under normal operation the compressor ramps signal level to zero after a sound sample is played to prevent a DC voltage appearing on the output. The LRMP bit prevents this from happening while a sample is looping allowing continuous audio. To loop a sound sample, the audio should be edited such that the last sample loops smoothly to the first. To do this, create the sample in a sound editor at the sample rate desired for storage then find the first sample that returns to the initial condition and cut back audio to one before this sample. Note that tones require different lengths to fulfill these conditions at a given sample rate and thus loop numbers vary to produce the same length of output audio.

At the end of the VM REG1 is reset and the trigger is re-enabled back to VM#7 before powering down.

#### • VM#7: R4\_PlayLoop (GPIO4)

- a. CFG(R4, 0x08) ; Configure GPIO4 to execute VM# 8 on next trigger.

- b. CFG(REG1, 0x20) ; Configure LRMP bit in REG1

- c. LOOP\_VP(Do,20) ; LOOP "Do" 20 times.

- d. LOOP\_VP(Re,250) ; LOOP "Re" 250 times.

- e. LOOP\_VP(Mi,5) ; LOOP "Mi" 5 times.

- f. LOOP\_VP(Fa,33) ; LOOP "Fa" 33 times.

- g. LOOP\_VP(So,10) ; LOOP "So" 10 times

- h. LOOP\_VP(La,10) ; LOOP "La" 10 times

- i. LOOP\_VP(Si,7) ; LOOP "Si" 7 times.

- j. Silence (128 ms) ; Insert 128ms of silence

- k. CFG(REG1, 0x00) ; Reset REG1

- CFG(R4, 0x07) ; Configure GPIO4 to execute VM#7 on next trigger.

- m. PD ; Power Down

- VM#8: PD\_R4

- a. CFG(REG1, 0x00)

b. CFG(R4, 0x07)

- ; Configure Register one to its default value 00

- ; Configure GPIO4 to execute VM#7 on next trigger.

c. PD

Ι.

; Power Down

#### 10.2.4 Example: Uninterruptable Trigger, smooth audio.

In this example a single trigger on GPIO3 will sequence through several messages until all messages are played the playback cannot be interrupted by any other trigger. The example also demonstrates how to use begin and end segments to create smooth playback. Each "note" consists of concatenating three voice prompts, for instance "So\_begin" "So" and "So\_end". The begin and end prompts ramp the audio smoothly to avoid sudden transients in sound level. The middle, full amplitude, section is created by looping a short sample.

At the beginning of the Voice Macro, all triggers are disabled so that Voice Macro cannot be interrupted from any source. The NRMP bit of REG1 is set so that concatenation of audio occurs without any ramp down between prompts. At the end of the macro, interrupts are re-enabled and device is powered down.

### nuvoton

### • VM#9: R3\_Non-Int\_Smooth (GPIO3)

- a. CFG(REG\_GPIO\_AF1, 0x00)

- b. CFG(REG1, 0x04)

- c. PLAY\_VP(So\_begin)

- d. LOOP\_VP(So,10)

- e. PLAY\_VP(So\_end)

- f. PLAY\_VP(Fa\_begin)

- g. LOOP VP(Fa,33)

- h. PLAY VP(Fa end)

- i. PLAY VP(Mi begin)

- i. LOOP VP(Mi,5)

- k. PLAY VP(Mi end)

- I. PLAY\_VP(Re\_begin)

- m. LOOP VP(Re,250)

- n. PLAY VP(Re end)

- o. PLAY VP(Do begin)

- p. LOOP VP(Do,20)

- g. PLAY VP(Do end)

- r. Wait Interrupt

- s. CFG(REG1, 0x00)

- t. CFG(REG\_GPIO\_AF1, 0x3f)

- u. PD

- ; Wait for audio to finish ; Reset NRMP bit

- ; Re-enable interrupts

- ; Power down device.

### 10.2.5 Example: Continuous Play until re-trigger.

In this example a single trigger on GPIO2 will sequence through several messages with pause in between each message. Messages are played in a loop indefinitely until another trigger occurs on GPIO2 to stop playback.

### VM0#A: R2\_Loop\_VM (GPIO2)

- a. CFG(R2, 0x0b) b. PLAY VP(One)

- ; Set Trigger to VM#B (PD\_R2) ; Play "One"

- c. Silence (256 ms)

- ; pause 256ms ; Play "Two"

- d. PLAY\_VP(two)

- e. Silence (256 ms)

- f. PLAY\_VP(three)

- g. Silence (736 ms)

- h. PLAY\_VP(four)

- i. Silence (256 ms)

- j. EXE\_VM(0xA)

- k. Finish

- VM0#B: PD\_R2

b.

a. CFG(R2, 0x0a)

PD

; Power Down.

; Execute VM#A (repeat)

; Reset Trigger to VM#A

- ; Disable all triggers. : Set NRMP bit

- ; Play "So begin"

- , Flay S0\_begin

- ; Loop "So" 10 times.

- ; Play "So\_end"

### NUVOTON

### 10.2.6 Example: Level Hold Trigger.

In this example holding GPIO1 will play several messages. Releasing GPIO1 will stop the playback. No other triggers will affect operation.

- VM#C: R1 Level Hold (GPIO1)

- a. CFG(REG GPIO AF0.0x02)

- b. CFG(REG GPIO AF1, 0x02)

- c. CFG(R1, 0x0d)

- d. CFG(REG1, 0x20)

- e. LOOP VP(Re,200)

- f. Silence (32 ms)

- g. LOOP VP(Mi,4)

- h. Silence (32 ms)

- LOOP VP(Fa,20) i.

- j. Silence (32 ms)

- k. CFG(REG1, 0x00)

- PLAY VP(applause) ١.

- m. PD

- VM#D: PD R1

- a. CFG(REG GPIO AF0, 0x00)

- b. CFG(REG GPIO AF1, 0x3f)

- c. CFG(REG1, 0x00)

- d. CFG(R1, 0x0c)

- e. PD

- : Enable rising edge trigger for GPIO2

- ; Disable all triggers except GPIO2

- ; Set Trigger to VM#D (PD R1)

- A COLORED LAND ; Disable rising edge trigger

- ; Re-enable all triggers.

- ; Ensure REG1 reset

- ; Set trigger to VM#C

- ; Power Down.

#### CHANNEL SELECTION AND EXECUTION CONTROL 11

#### SELECT CHANNEL FOR THE PLYABCK AND MIXING 11.1

For any play command such as PLAY\_VM or PLAY\_VP, etc, the playback occurs in either one channel or all three channels. In other words, user can either specify one single active channel for next playback operation, or make the next play operation happen in all three channels. Channel selection can be achieved by configuring register 0x0C.

To mix two different sound effects from two channels, e.g. channel #0 and channel #1, user can first configure channel #0 as the active channel by writing 0bxxxxxx00 into register 0x0C, then send a play command to play the first sound effect; then configure channel #1 as the active channel by writing 0bxxxxxx01 into register 0x0C, then send another play command to play the second sound effect. This way sound effect mixing can be achieved.

By Default, play operations will always happen in channel #0.

11.2 **EXECUTION CONTROL**

### nuvoTon

The ISD2360 implemented several commands which allow user add fine control in a VM script execution.

### 11.2.1 Conditional Branch and Unconditional Jump

The ISD2360 can do mask branch which judges device's current pin status and its internal status register value against the value in mask register, to decide if jump to a memory address (and start execution from there) or continue executing the next script command inside the current VM. This gives the possibility of multi-tasking, i.e. let the ISD2360 do something during the play.

The ISD2360 can also do an absolute jump, which jumps to a memory address and start execution from there.

The new start address should be a valid command entry address; otherwise it will cause unknown behavior. The scope for the mask jump and absolute jump is global, i.e. the full range of the flash size.

#### 11.2.2 Execution Delay / Pause

The ISD2360 has time counter for each channel. So it allows customer add delay during a VM execution. This adds the convenience for certain operations such as GPIO driving with time control.

### **12 ELECTRICAL CHARACTERISTICS**

12.1 **OPERATING CONDITIONS**

### **OPERATING CONDITIONS (INDUSTRIAL PACKAGED PARTS)**

| CONDITIONS                                       | VALUES                               |

|--------------------------------------------------|--------------------------------------|

| Operating temperature range (Case temperature)   | -40°C to +85°C                       |

| Supply voltage (V <sub>DD</sub> ) <sup>[1]</sup> | +2.4V to +5.5V                       |

| Ground voltage (V <sub>SS</sub> ) <sup>[2]</sup> | 0V                                   |

| Input voltage (V <sub>DD</sub> ) <sup>[1]</sup>  | 0V to 5.5V                           |

| Voltage applied to any pins                      | $(V_{SS}$ –0.3V) to $(V_{DD}$ +0.3V) |

NOTES:

$^{[1]}V_{DD} = V_{CCD} = V_{CCPWM}$

<sup>[2]</sup>  $V_{SS} = V_{SSD} = V_{SSPWM}$

#### 12.2 **AC PARAMETERS**

### 12.2.1 Internal Oscillator

| PARAMETER                 | SYMBOL            | MIN | ТҮР   | МАХ | UNITS | CONDITIONS          |

|---------------------------|-------------------|-----|-------|-----|-------|---------------------|

| Sample rate with Internal | F <sub>smax</sub> | -1% | 32kHz | +1% | kHz   | Vdd = 3V.           |

| Oscillator                | -                 |     |       |     |       | At room temperature |

### 12.2.2 Speaker Outputs

Notes:

| PARAMETER                | SYMBOL                       | MIN | TYP <sup>[1]</sup> | MAX  | UNITS | CONDITIONS                  |

|--------------------------|------------------------------|-----|--------------------|------|-------|-----------------------------|

| SNR, Memory to SPK+/SPK- | SNR <sub>MEM_SPK</sub>       |     | 60                 |      | dB    | Load 150Ω <sup>[2][3]</sup> |

| Output Power             | P <sub>OUT_SPK</sub> VCC=5.0 |     |                    | 0.95 | W     | Load 8Ω <sup>[2]</sup>      |

| THD, Memory to SPK+/SPK- | THD %                        |     | <1%                |      |       | Load 8Ω <sup>[2]</sup>      |

| Minimum Load Impedance   | R <sub>L(SPK)</sub>          | 4   | 8                  |      | Ω     |                             |

<sup>[1]</sup>Conditions  $V_{cc}=3V$ ,  $T_A=25^{\circ}C$  unless otherwise stated. <sup>[2]</sup>Based on 12-bit PCM.

<sup>[3]</sup> All measurements are C-message weighted.

| PARAMETER               | SYMBOL                   | MIN                             | <b>TYP</b> <sup>[1]</sup> | MAX             | UNITS | CONDITIONS             |

|-------------------------|--------------------------|---------------------------------|---------------------------|-----------------|-------|------------------------|

| Supply Voltage          | V <sub>DD</sub>          | 2.4                             |                           | 5.5             | V     |                        |

| Input Low Voltage       | V <sub>IL</sub>          | V <sub>SS</sub> -0.3            |                           | $0.3 x V_{DD}$  | V     | Ç.,                    |

| Input High Voltage      | V <sub>IH</sub>          | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |                           | V <sub>DD</sub> | V     |                        |

| Output Low Voltage      | V <sub>OL</sub>          | V <sub>SS</sub> -0.3            |                           | $0.3 x V_{DD}$  | V     | I <sub>OL</sub> = 1mA  |

| Output High Voltage     | V <sub>OH</sub>          | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |                           | V <sub>DD</sub> | V     | I <sub>OH</sub> = -1mA |

| Pull-up Resistance      | R <sub>PU</sub>          |                                 | 50                        |                 | kΩ    | a ha                   |

| Pull-down Resistance    | R <sub>PD</sub>          |                                 | 10                        |                 | kΩ    | 82 On                  |

| INTB Output Low Voltage | V <sub>OH1</sub>         |                                 |                           | 0.4             | V     | 02 12                  |

| Playback Current        | I <sub>DD_Playback</sub> |                                 | 3                         |                 | mA    | No Load <sup>[2]</sup> |

| Standby Current         | I <sub>SB</sub>          |                                 | <1                        | 10              | μA    | V <sub>DD</sub> = 3.6V |

| Input Leakage Current   | IIL                      |                                 |                           | ±1              | μA    | Force V <sub>DD</sub>  |

Notes:

<sup>[1]</sup>Conditions  $V_{DD}=3V$ ,  $T_A=25$ °C unless otherwise stated <sup>[2]</sup>To calculate total current, add load dissipation into application specific load.

12.4 SPI TIMING

### Figure 12-1 SPI Timing

| SYMBOL             | DESCRIPTION                                                      | MIN  | ТҮР | MAX  | UNIT |

|--------------------|------------------------------------------------------------------|------|-----|------|------|

| Т <sub>SCK</sub>   | SCLK Cycle Time                                                  | 60   |     |      | ns   |

| Т <sub>SCKH</sub>  | SCLK High Pulse Width                                            | 25   |     |      | ns   |

| T <sub>SCKL</sub>  | SCLK Low Pulse Width                                             | 25   |     |      | ns   |

| T <sub>RISE</sub>  | Rise Time for All Digital Signals                                |      |     | 10   | ns   |

| T <sub>FALL</sub>  | Fall Time for All Digital Signals                                |      |     | 10   | ns   |

| T <sub>SSBS</sub>  | SSB Falling Edge to 1 <sup>st</sup> SCLK Falling Edge Setup Time | 30   |     |      | ns   |

| T <sub>SSBH</sub>  | Last SCLK Rising Edge to SSB Rising Edge Hold Time               | 30ns |     | 50us |      |

| T <sub>SSBHI</sub> | SSB High Time between SSB Lows                                   | 20   |     |      | ns   |

| T <sub>MOS</sub>   | MOSI to SCLK Rising Edge Setup Time                              | 15   |     |      | ns   |

| Т <sub>мон</sub>   | SCLK Rising Edge to MOSI Hold Time                               | 15   |     |      | ns   |

| T <sub>ZMID</sub>  | Delay Time from SSB Falling Edge to MISO Active                  |      |     | 12   | ns   |

| T <sub>MIZD</sub>  | Delay Time from SSB Rising Edge to MISO Tri-state                |      |     | 12   | ns   |

| T <sub>MID</sub>   | Delay Time from SCLK Falling Edge to MISO                        |      |     | 12   | ns   |

| T <sub>CRBD</sub>  | Delay Time: SCLK Rising Edge to RDY/BSYB Falling Edge            |      |     | 12   | ns   |

| T <sub>RBCD</sub>  | Delay Time: RDY/BSYB Rising Edge to SCLK Falling Edge            | 0    |     |      | ns   |