# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## ISL24010

## NOT RECOMMENDED FOR NEW DESIGNS NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

High Voltage TFT-LCD Logic Driver

The ISL24010 is a high voltage TFT-LCD logic driver with a +40V and -20V (momentary absolute max) output voltage swing capability. It is manufactured using the Intersil's proprietary monolithic high voltage bipolar process and is capable of driving a 3000pF load in 500ns.

The ISL24010 will level shift a digital input signal to an output voltage nearly equal to its output supply voltages. The ISL24010 has 3 supplies.  $V_{ON1}$  and  $V_{ON2}$  are positive supplies with a voltage range between +10V and +40V (absolute max).  $V_{OFF}$  is the negative supply with a voltage range between -5V and -20V (absolute max). Outputs 1 through 6 are connected to  $V_{ON1}$  and  $V_{OFF}$ . Outputs 7 and 8 are connected to  $V_{ON2}$  and  $V_{OFF}$ . This configuration enables outputs 1 through 6 to provide slicing to the row drivers to reduce flicker, and outputs 7 and 8 to control possible supply lines.  $V_{ON2}$  should remain constant. It is possible to tie  $V_{ON1}$  and  $V_{ON2}$  supplies together, if independent control as described above is not desired.  $V_{ON2}$  is required to be greater than or equal to  $V_{ON1}$  at all times.

The ISL24010 is available in TSSOP-20 pin package. It is specified for operation over the -40 $^{\circ}$ C to +85 $^{\circ}$ C industrial temperature range.

#### **Ordering Information**

| PART<br>NUMBER              | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE                                   | PKG.<br>DWG. # |

|-----------------------------|-----------------|------------------------|-------------------------------------------|----------------|

| ISL24010IVZ<br>(See Note)   | 24010IVZ        | -40 to +85             | 20 Ld TSSOP<br>(Pb-free)                  | M20.173        |

| ISL24010IVZ-T<br>(See Note) | 24010IVZ        | -40 to +85             | 20 Ld TSSOP<br>Tape and Reel<br>(Pb-free) | M20.173        |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

age Level Shifter for TFT/LCD Panels

vember 4, 2005

FN6124.0

#### Features

- 0V to 5.5V (absolute max) Input Voltage Range

- +40V and -20V (momentary absolute max) Output Voltage Range

- 10mA Output Continuous Current (all 8 channels)

- · 25mA Output Peak Current (all 8 channels)

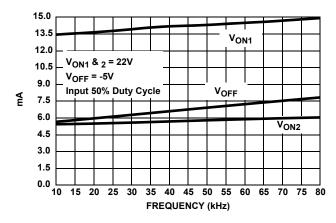

- Rise/Fall Times 150ns/210ns

- Propagation Delay 250ns

- 50kHz Input Logic Frequency

- · 20 Ld TSSOP Pb-Free Plus Anneal (RoHS Compliant)

#### Applications

TFT-LCD panels

#### Pinout

20 Ld TSSOP TOP VIEW GND 20 V<sub>ON1</sub> OUT1 19 IN1 OUT2 IN2 18 17 OUT3 IN3 16 OUT4 IN4 IN5 15 OUT5 14 OUT6 IN6 IN7 13 OUT7 12 OUT8 IN8 ۹ 11 V<sub>ON2</sub> VOFF

## Functional Diagram

| IN1   and V <sub>OFF</sub> OUT2   IN2   OUT3   IN3   CH3   IN4   OUT5   IN5   OUT6   IN6   CH6   IN7   and V <sub>OFF</sub> IN8   CH8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | Connected to V <sub>ON1</sub> |         | OUT1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------|---------|------|

| IN2 I OUT3   IN3 I CH3 I   IN4 I CH4 OUT5   IN5 I OUT5   IN6 CH6 I   IN7 I and V <sub>OFF</sub> OUT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IN1 |                               |         | OUT2 |

| IN3 IN3 IN3 IN3 IN4 IN4 IN4 IN5 IN5 IN5 IN5 IN5 IN6 IN6 IN6 IN6 IN7 <td>IN2</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                      | IN2 |                               |         |      |

| IN4 Image: CH4 | IN3 |                               | Снз — + |      |

| IN4 OUT5   IN5 OUT5   IN6 CH6   IN7 OUT7   IN7 OUT7   OUT7   CH8 OUT8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | ▶                             |         | OUT4 |

| IN5 OUT6   IN6 CH6   IN7 Connected to VON2   IN7 CH8   OUT7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IN4 | │                             |         | OUT5 |

| IN6 Image: CH6 Image: CH6   Image: Large constraints Image: CH6 Image: CH6   Image: Constraints Image: CH7 Image: CH7   Image: CH7 <td>IN5</td> <td></td> <td>CH5</td> <td>→</td>                                                   | IN5 |                               | CH5     | →    |

| IN7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN6 | ►   ►                         |         |      |

| IN7 Connected to V <sub>ON2</sub> CH7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | <u> </u>                      |         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | Connected to V <sub>ON2</sub> |         | OUT7 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IN7 | l and V <sub>OFF</sub>        |         | OUT8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IN8 | │                             |         | →    |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Driver Positive Supply Voltage Range, (V <sub>ON</sub> ) +5V to +40V              |

|-----------------------------------------------------------------------------------|

| Power Supply Voltage Range, (V <sub>ON</sub> to V <sub>OFF</sub> )+10V to +60V    |

| Negative Supply Voltage Range, (V <sub>OFF</sub> )20V to -5V                      |

| Supply Turn-on Slew Rate 10V/µs                                                   |

| Input Voltage Range, All Inputs                                                   |

| Output Voltage Range, All Outputs V <sub>OFF</sub> -0.5V to V <sub>ON</sub> +0.5V |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)                       | $\theta_{JA}$ (°C/W) |

|------------------------------------------------------------|----------------------|

| 20 Ld TSSOP Package                                        | 140                  |

| I <sub>OUT</sub> (continuous, all 8 channels)              | 80mA                 |

| T <sub>AMBIENT</sub> 40                                    |                      |

| T <sub>JUNCTION</sub> ···································· |                      |

| T <sub>STORAGE</sub> 65°                                   | C to +150°C          |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on a HIGH effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| Electrical Specifications | V <sub>ON</sub> = 22V, V <sub>OFF</sub> = -5V, T <sub>A</sub> = -40°C to +85°C Unless Otherwise Specified. Typical values tested at 25°C |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER            | DESCRIPTION                    | CONDITION                                                                                  | MIN                       | ТҮР   | MAX                       | UNIT |

|----------------------|--------------------------------|--------------------------------------------------------------------------------------------|---------------------------|-------|---------------------------|------|

| Power<br>Supplies    | Recommended Operating Voltages |                                                                                            | -5<br>(V <sub>OFF</sub> ) |       | 22<br>(V <sub>ON</sub> )  | V    |

| I(V <sub>ON</sub> )  | Supply Current                 | All Inputs low or high<br>No load<br>V <sub>ON</sub> = V <sub>ON1</sub> + V <sub>ON2</sub> |                           | 1.8   | 4.0                       | mA   |

| I(V <sub>OFF</sub> ) | Supply Current                 | All Inputs low or high<br>No load                                                          | -4.0                      | -1.8  |                           | mA   |

| I <sub>IN</sub>      | Input Leakage                  | Each Input low or high<br>High = 1.8V, Low = 0.8V                                          | -8.0                      | ± 2.0 | 8.0                       | μA   |

| VOH                  | High Level Output Voltage      | IOH = -100μA<br>V <sub>ON</sub> = 22V<br>RL = 100pF in parallel with 5kΩ                   | (V <sub>ON</sub> - 1.5V)  | 21.2  |                           | V    |

| VOL                  | Low Level Output Voltage       | IOH = +100μA<br>V <sub>OFF</sub> = -5V<br>RL = 100pF in parallel with 5kΩ                  |                           | -4.3  | (V <sub>OFF</sub> + 1.5V) | V    |

| VIH                  | High Level Input Voltage       |                                                                                            | 1.8                       |       |                           | V    |

| VIL                  | Low Level Input Voltage        |                                                                                            |                           |       | 0.8                       | V    |

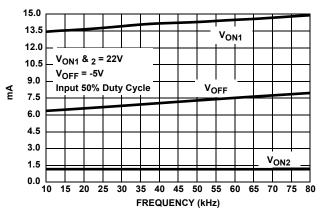

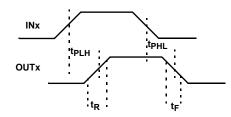

| tplh                 | Low to High Prop Delay         | 50% to 50%, Tested with RL = 100pF in parallel with 5k $\Omega$ , f = 50kHz                |                           | 300   | 500                       | ns   |

| tphl                 | High to Low Prop Delay         | Measured at 50% to 50%<br>f = 50kHz<br>RL = 100pF in parallel with $5k\Omega$ ,            |                           | 250   | 500                       | ns   |

| ttlh                 | Rise Time                      | Measured at 10% to 90%<br>f = 50kHz<br>RL = 100pF in parallel with $5k\Omega$              |                           | 150   | 500                       | ns   |

| tthl                 | Fall Time                      | Measured at 10% to 90%<br>f = 50kHz<br>RL = 100pF in parallel with $5k\Omega$              |                           | 210   | 500                       | ns   |

#### **Pin Descriptions**

| PIN NUMBER<br>TSSOP-20 | PIN NAME | EQUIVALENT<br>CIRCUIT                        | DESCRIPTION                                                                                                                           |

|------------------------|----------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | GND      | 4                                            | Ground pin                                                                                                                            |

| 2                      | IN1      | 1                                            | Level shifter input 1                                                                                                                 |

| 3                      | IN2      | 1                                            | Level shifter input 2                                                                                                                 |

| 4                      | IN3      | 1                                            | Level shifter input 3                                                                                                                 |

| 5                      | IN4      | 1                                            | Level shifter input 4                                                                                                                 |

| 6                      | IN5      | 1                                            | Level shifter input 5                                                                                                                 |

| 7                      | IN6      | 1                                            | Level shifter input 6                                                                                                                 |

| 8                      | IN7      | 1                                            | Level shifter input 7                                                                                                                 |

| 9                      | IN8      | 1                                            | Level shifter input 8                                                                                                                 |

| 10                     | VOFF     | 4                                            | Negative output supply for all channels                                                                                               |

| 11                     | VON2     | 4                                            | Positive output supply for channels 7 and 8. $V_{ON2}$ is required to be greater than or equal to $V_{ON1}.$                          |

| 12                     | OUT8     | 3                                            | Lever shifter output 8                                                                                                                |

| 13                     | OUT7     | 3                                            | Lever shifter output 7                                                                                                                |

| 14                     | OUT6     | 2                                            | Lever shifter output 6                                                                                                                |

| 15                     | OUT5     | 2                                            | Lever shifter output 5                                                                                                                |

| 16                     | OUT4     | 2                                            | Lever shifter output 4                                                                                                                |

| 17                     | OUT3     | 2                                            | Lever shifter output 3                                                                                                                |

| 18                     | OUT2     | 2                                            | Lever shifter output 2                                                                                                                |

| 19                     | OUT1     | 2                                            | Lever shifter output 1                                                                                                                |

| 20                     | VON1     | 4                                            | Positive output supply for channels 1 through 6. $V_{ON1}$ is required to be less than or equal to $V_{ON2}.$                         |

|                        |          | Von2<br>Voff                                 | $\begin{array}{c} \cdots & \downarrow & V_{ON1} \\ \cdots & \downarrow & \downarrow & 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0$ |

|                        |          | V <sub>ON2</sub><br>V <sub>ON1</sub><br>Voff |                                                                                                                                       |

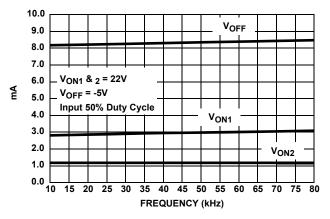

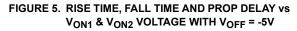

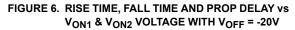

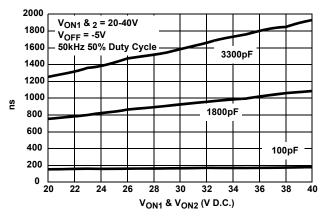

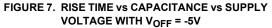

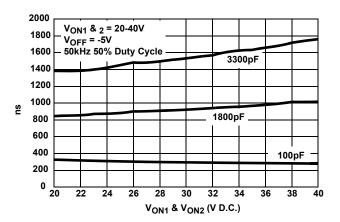

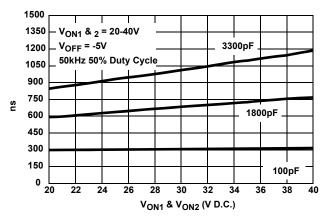

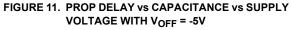

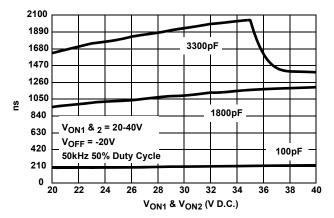

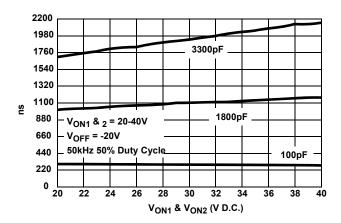

*Typical Performance Curves*  $T_A = 25^{\circ}C$ , Output load parallel RC (RL =  $5k\Omega$ , CL = 100pF) unless otherwise specified.

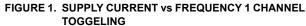

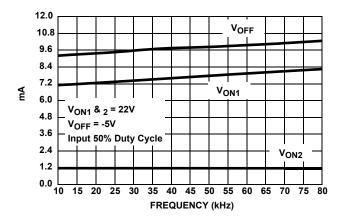

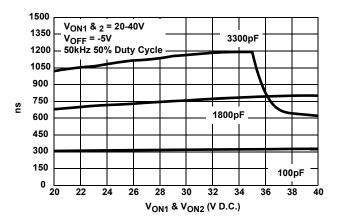

Typical Performance Curves T<sub>A</sub> = 25°C, Output load parallel RC (RL = 5kΩ, CL = 100pF) unless otherwise specified. (Continued)

FIGURE 8. RISE TIME vs CAPACITANCE vs SUPPLY VOLTAGE WITH V\_{OFF} = -20V

FIGURE 10. FALL TIME vs CAPACITANCE vs SUPPLY VOLTAGE WITH V<sub>OFF</sub> = -20V

Typical Performance Curves T<sub>A</sub> = 25°C, Output load parallel RC (RL = 5kΩ, CL = 100pF) unless otherwise specified. (Continued)

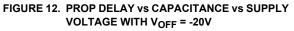

FIGURE 13. TRANSIENT RESPONSE vs LOAD CAPACITANCE

#### Application Information

#### General

The ISL24010 is an Octal voltage level shifter. The part was designed to level shifts a digital input signal to +22V and -5V for TFT-LCD displays. The device is capable of level shifting a CMOS logic signal between +40V and -20V.

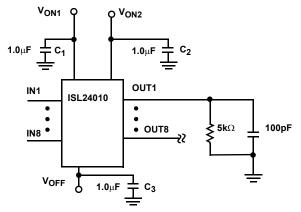

#### Power Supply Decoupling

The ISL24010 requires a 0.1 $\mu$ F decoupling capacitor as close to the V<sub>ON1</sub>, V<sub>ON2</sub> and V<sub>OFF</sub> power supply pins for a large load equal to 5k $\Omega$  in parallel with 100pF (Figure 16). This will deduce any dv/dt between the different supplies and prevent the internal ESD clamp from turning on and damaging the part.

#### **Power Supply Sequence**

The ISL24010 requires that V<sub>ON2</sub> be greater than or equal to V<sub>ON1</sub> at all times. Therefore, if V<sub>ON1</sub> and Von 2 are different supplies, then V<sub>ON2</sub> needs to be turned on before V<sub>ON1</sub>. The reason for this requirement is shown in Circuit 4 in the Pin Description Table. The ESD protection diode between V<sub>ON2</sub> and Von 1 will forward bias if V<sub>ON1</sub> becomes a diode drop greater than V<sub>ON2</sub>. Recommended power supply sequence: V<sub>ON2</sub>, V<sub>ON1</sub>, V<sub>OFF</sub> then input logic signals.

The ESD protection scheme is based on diodes from the pins to the V<sub>ON2</sub> supply and a dV/dt- triggered clamp. This dV/dt triggered clamp imposes a maximum supply turn-on slew rate of 10V/ $\mu$ s. This clamp will trigger if the supply powers up too fast, causing amps of current to flow. Ground and V<sub>ON1</sub> are treated as I/O pins with this protection scheme. In applications where the dV/dt supply ramp could exceed 10V/ $\mu$ s, such as hot plugging, additional methods should be employed to ensure the rate of rise is not exceeded.

#### Latch-up Proof

The ISL24010 is manufactured in a high voltage DI process that isolates every transistor in it's own tub making the part latch-up proof.

#### Input Pin Connections

Unused inputs must be tied to ground. Failure to tie unused input pins to ground will result in a rail to rail oscillations on the respective output pins and higher unwanted power dissipation in the part. Under these conditions, the temperature of the part could get very hot.

#### Limiting the Output Current

No output short circuit current limit exists on this part. All applications need to limit the output current to less than 80mA. Adequate thermal heat sinking of the parts is also required.

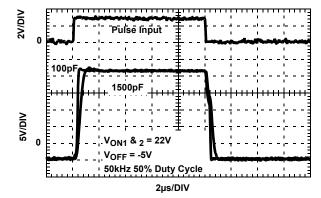

### Application Diagram (TV)

FIGURE 14. TYPICAL TV APPLICATION CIRCUIT

#### Application Diagram (Monitor)

#### Test Circuit

If the output load is a series 200 $\Omega$  resistor and a 3300pF then C1, C2 and C3 can be reduced to 0.47pF.

FIGURE 16. TEST LOAD AND TIMING DEFINITIONS

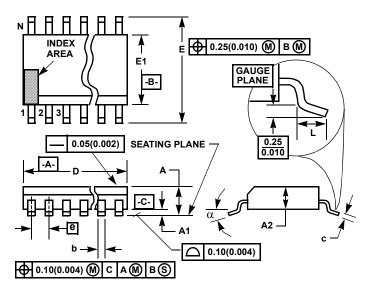

#### Thin Shrink Small Outline Plastic Packages (TSSOP)

#### NOTES:

- 1. These package dimensions are within allowable dimensions of JEDEC MO-153-AC, Issue E.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E1" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.15mm (0.006 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total in excess of "b" dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm (0.0027 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact. (Angles in degrees)

#### M20.173

20 LEAD THIN SHRINK SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES         |                | MILLIMETERS    |                |       |

|--------|----------------|----------------|----------------|----------------|-------|

| SYMBOL | MIN            | MAX            | MIN            | MAX            | NOTES |

| А      | -              | 0.047          | -              | 1.20           | -     |

| A1     | 0.002          | 0.006          | 0.05           | 0.15           | -     |

| A2     | 0.031          | 0.051          | 0.80           | 1.05           | -     |

| b      | 0.0075         | 0.0118         | 0.19           | 0.30           | 9     |

| С      | 0.0035         | 0.0079         | 0.09           | 0.20           | -     |

| D      | 0.252          | 0.260          | 6.40           | 6.60           | 3     |

| E1     | 0.169          | 0.177          | 4.30           | 4.50           | 4     |

| е      | 0.026 BSC      |                | 0.65 BSC       |                | -     |

| E      | 0.246          | 0.256          | 6.25           | 6.50           | -     |

| L      | 0.0177         | 0.0295         | 0.45           | 0.75           | 6     |

| Ν      | 20             |                | 2              | 20             | 7     |

| α      | 0 <sup>0</sup> | 8 <sup>0</sup> | 0 <sup>0</sup> | 8 <sup>0</sup> | -     |

Rev. 1 6/98

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <u>www.intersil.com</u>