Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Single, Dual, Quad General Purpose Micropower, RRIO Operational Amplifiers

#### ISL28114, ISL28214, ISL28414

The ISL28114, ISL28214 and ISL28414 are single, dual and quad channel general purpose micropower, rail-to-rail input and output operational amplifiers with supply voltage range of 1.8V to 5.5V. Key features are a low supply current of  $390\mu A$  maximum per channel at room temperature, a low bias current and a wide input voltage range, which enables the ISL28x14 devices to be excellent general purpose op-amps for a wide range of applications.

The ISL28114 is available in the SC70-5 and SOT23-5 packages, the ISL28214 is in the MSOP8, SO8 and SOT23-8 packages, and the ISL28414 is in the TSSOP14, SOIC14 packages. All devices operate across the extended temperature range of -40  $^{\circ}$ C to +125  $^{\circ}$ C.

#### **Related Literature**

- See <u>AN1519</u> for "ISL28213/14SOICEVAL2Z Evaluation Board User's Guide"

- See <u>AN1520</u> for "ISL28113/14SOT23EVAL1Z Evaluation Board User's Guide"

- See <u>AN1542</u> for "ISL28213/14MSOPEVAL2Z Evaluation Board User's Guide"

- See <u>AN1547</u> for "ISL28414TSSOPEVAL1Z Evaluation Board User's Guide"

#### **Features**

| • Low current consumption   | 390μΑ               |

|-----------------------------|---------------------|

| • Wide supply range         | 1.8V to 5.5V        |

| Gain bandwidth product      | 5MHz                |

| Input bias current          | 20pA, Max.          |

| Operating temperature range | 40°C to +125°C      |

| Packages                    |                     |

| - ISL28114 (single)         | SC70-5, SOT23-5     |

| - ISL28214 (dual)           | MSOP8, S08, S0T23-8 |

| - ISL28414 (quad)           | SOIC14, TSSOP14     |

## **Applications**

- · Power supply control/regulation

- · Process control

- · Signal ban/buffers

- · Active filters

- · Current shunt sensing

- · Transimpedance amp

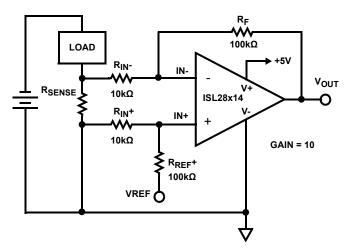

SINGLE-SUPPLY, LOW-SIDE CURRENT SENSE AMPLIFIER

FIGURE 1. TYPICAL APPLICATION

## **Ordering Information**

| PART NUMBER (Note 4)                          | PART<br>MARKING         | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |  |  |  |  |

|-----------------------------------------------|-------------------------|-----------------------------|----------------|--|--|--|--|

| ISL28114FEZ-T7 (Notes 1, 2)                   | BKA (Note 5)            | 5 Ld SC-70                  | P5.049         |  |  |  |  |

| ISL28114FEZ-T7A ( <u>Notes 1</u> , <u>2</u> ) | BKA ( <u>Note 5</u> )   | 5 Ld SC-70                  | P5.049         |  |  |  |  |

| ISL28114FHZ-T7 (Notes 1, 2)                   | BDBA (Note 5)           | 5 Ld SOT-23                 | P5.064A        |  |  |  |  |

| ISL28114FHZ-T7A (Notes 1, 2)                  | BDBA (Note 5)           | 5 Ld SOT-23                 | P5.064A        |  |  |  |  |

| ISL28214FUZ ( <u>Note 2</u> )                 | 8214Z                   | 8 Ld MSOP                   | M8.118A        |  |  |  |  |

| ISL28214FUZ-T7 (Notes 1, 2)                   | 8214Z                   | 8 Ld MSOP                   | M8.118A        |  |  |  |  |

| ISL28214FBZ (Note 2)                          | 28214 FBZ               | 8 Ld SOIC                   | M8.15E         |  |  |  |  |

| ISL28214FBZ-T7 (Notes 1, 2)                   | 28214 FBZ               | 8 Ld SOIC                   | M8.15E         |  |  |  |  |

| ISL28214FBZ-T13 (Notes 1, 2)                  | 28214 FBZ               | 8 Ld SOIC                   | M8.15E         |  |  |  |  |

| ISL28214FHZ-T7 (Notes 1, 3)                   | BELA (Note 5)           | 8 Ld SOT-23                 | P8.064         |  |  |  |  |

| ISL28214FHZ-T7A ( <u>Notes 1</u> , <u>3</u> ) | BELA (Note 5)           | 8 Ld SOT-23                 | P8.064         |  |  |  |  |

| ISL28414FVZ (Note 2)                          | 28414 FVZ               | 14 Ld TSSOP                 | MDP0044        |  |  |  |  |

| ISL28414FVZ-T7 (Notes 1, 2)                   | 28414 FVZ               | 14 Ld TSSOP                 | MDP0044        |  |  |  |  |

| ISL28414FVZ-T13 ( <u>Notes 1</u> , <u>2</u> ) | 28414 FVZ               | 14 Ld TSSOP                 | MDP0044        |  |  |  |  |

| ISL28414FBZ ( <u>Note 2</u> )                 | 28414 FBZ               | 14 Ld SOIC                  | MDP0027        |  |  |  |  |

| ISL28414FBZ-T7 (Notes 1, 2)                   | 28414 FBZ               | 14 Ld SOIC                  | MDP0027        |  |  |  |  |

| ISL28414FBZ-T13 ( <u>Notes 1</u> , <u>2</u> ) | 28414 FBZ               | 14 Ld SOIC                  | MDP0027        |  |  |  |  |

| ISL28114S0T23EVAL1Z                           | <b>Evaluation Board</b> |                             | ,              |  |  |  |  |

| ISL28214MSOPEVAL2Z                            | <b>Evaluation Board</b> |                             |                |  |  |  |  |

| ISL28214SOICEVAL2Z                            | Evaluation Board        | Evaluation Board            |                |  |  |  |  |

| ISL28414TSSOPEVAL1Z                           | <b>Evaluation Board</b> |                             |                |  |  |  |  |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate-e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL28114</u>, <u>ISL28214</u>, <u>ISL28414</u>. For more information on MSL please see Tech Brief <u>TB363</u>.

- 5. The part marking is located on the bottom of the part.

Submit Document Feedback 2 intersil FN6800.9

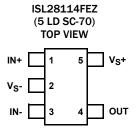

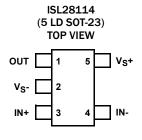

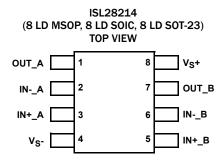

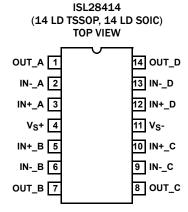

## **Pin Configurations**

## **Pin Descriptions**

|                                         |            | PI          | N NUMBER                                |                            |                         |                                                   |

|-----------------------------------------|------------|-------------|-----------------------------------------|----------------------------|-------------------------|---------------------------------------------------|

| PIN NAME                                | 5 Ld SC-70 | 5 Ld SOT-23 | 8 Ld MSOP,<br>8 Ld SOIC,<br>8 Ld SOT-23 | 14 Ld TSSOP,<br>14 LD SOIC | DESCRIPTION             | CIRCUITS                                          |

| OUT_A OUT_B OUT_C OUT_D                 | 4          | 1           | 1<br>7                                  | 1<br>7<br>8<br>14          | Output                  | V+ OUT V- CIRCUIT 1                               |

| V <sub>S</sub> -                        | 2          | 2           | 4                                       | 11                         | Negative supply voltage | V+ CAPACITIVELY TRIGGERED ESD CLAMP  V- CIRCUIT 2 |

| IN+<br>IN+_A<br>IN+_B<br>IN+_C<br>IN+_D | 1          | 3           | 3<br>5                                  | 3<br>5<br>10<br>12         | Positive Input          | IN                                                |

| IN-<br>INA<br>INB<br>INC<br>IND         | 3          | 4           | 2<br>6                                  | 2<br>6<br>9<br>13          | Negative Input          | CIRCUIT 3                                         |

| V <sub>S</sub> +                        | 5          | 5           | 8                                       | 4                          | Positive supply voltage | See <u>"CIRCUIT 2"</u>                            |

3

#### Absolute Maximum Ratings (TA = +25°C)

| Supply Voltage                     | 6.5V           |

|------------------------------------|----------------|

| Supply Turn-on Voltage Slew Rate   | 1V/µs          |

| Differential Input Current         | 20mA           |

| Differential Input Voltage         | $V_{+} + 0.5V$ |

| Input Voltage                      | $V_{+} + 0.5V$ |

| ESD Rating                         |                |

| Human Body Model                   | 4000V          |

| Machine Model (ISL28114, ISL28214) | 350V           |

| Machine Model (ISL28414)           | 400V           |

| Charged Device Model               | 2000V          |

#### **Thermal Information**

| Thermal Resistance (Typical)            | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------------|----------------------|----------------------|

| 5 Ld SC-70 (Notes 6, 7)                 | 250                  | N/A                  |

| 5 Ld SOT-23 (Notes 6, 7)                | 225                  | N/A                  |

| 8 Ld MSOP (Notes 6, 7)                  | 180                  | 100                  |

| 8 Ld SOIC Package (Notes 6, 7)          | 126                  | 90                   |

| 8 Ld SOT-23 Package (Notes 6, 7)        | 240                  | 168                  |

| <b>14</b> Ld TSSOP Package (Notes 6, 7) | 120                  | 40                   |

| <b>14</b> Ld SOIC Package (Notes 6, 7)  | 90                   | 50                   |

| Ambient Operating Temperature Range     | 4                    | 0°C to +125°C        |

| Storage Temperature Range               | 6                    | 5°C to +150°C        |

| Operating Junction Temperature          |                      | +125°C               |

| Pb-free Reflow Profile                  |                      | see <u>TB493</u>     |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 6. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 7. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

**Electrical Specifications**  $V_S$ + = 5V,  $V_S$ - = 0V,  $R_L$  = Open,  $V_{CM}$  =  $V_S$ /2,  $T_A$  = +25°C, unless otherwise specified. **Boldface limits apply over** the operating temperature range, -40°C to +125°C, unless otherwise specified.

| PARAMETER                          | DESCRIPTION                                     | TEST CONDITIONS               | MIN<br>(Note 8) | ТҮР       | MAX<br>( <u>Note 8</u> ) | UNIT  |

|------------------------------------|-------------------------------------------------|-------------------------------|-----------------|-----------|--------------------------|-------|

| DC SPECIFICATIONS                  |                                                 | -                             | <b>'</b>        | <u>U.</u> | "                        |       |

| v <sub>os</sub>                    | Input Offset Voltage                            |                               | -4              | 0.5       | 4                        | mV    |

|                                    |                                                 | -40°C to +125°C               | -5              |           | 5                        | mV    |

| TCV <sub>OS</sub>                  | Input Offset Voltage Temperature<br>Coefficient | -40°C to +125°C               |                 | 5         |                          | μV/°C |

| I <sub>OS</sub>                    | Input Offset Current                            |                               |                 | 1         | 30                       | pA    |

| I <sub>B</sub>                     | Input Bias Current                              | ISL28114                      | -20             | 3         | 20                       | pA    |

|                                    |                                                 |                               | -100            |           | 100                      | pA    |

|                                    |                                                 | ISL28214, ISL28414            | -20             | 3         | 20                       | pA    |

|                                    |                                                 |                               | -50             |           | 50                       | pA    |

| Common Mode Input<br>Voltage Range |                                                 |                               | - 0.1           |           | 5.1                      | V     |

| CMRR                               | Common Mode Rejection Ratio                     | VCM = -0.1V to 5.1V           |                 | 72        |                          | dB    |

|                                    |                                                 | -40°C to +125°C               |                 | 70        |                          | dB    |

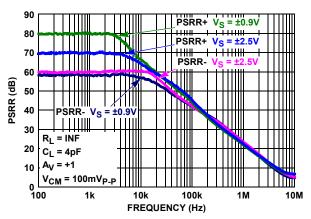

| PSRR                               | Power Supply Rejection Ratio                    | V <sub>S</sub> = 1.8V to 5.5V |                 | 71        |                          | dB    |

|                                    |                                                 | -40°C to +125°C               |                 | 70        |                          | dB    |

| v <sub>oh</sub>                    | Output Voltage Swing, High                      | R <sub>L</sub> = 10kΩ         | 4.985           | 4.993     |                          | V     |

|                                    |                                                 |                               | 4.98            |           |                          | V     |

| V <sub>OL</sub>                    | Output Voltage Swing, Low                       | R <sub>L</sub> = 10kΩ         |                 | 13        | 15                       | mV    |

|                                    |                                                 |                               |                 |           | 20                       | mV    |

| V <sub>+</sub>                     | Supply Voltage                                  |                               | 1.8             |           | 5.5                      | V     |

| I <sub>S</sub>                     | Supply Current per Amplifier                    | R <sub>L</sub> = OPEN         |                 | 300       | 390                      | μΑ    |

|                                    |                                                 |                               |                 |           | 475                      | μΑ    |

| I <sub>SC+</sub>                   | Output Source Short Circuit Current             | R <sub>L</sub> = 10Ω to V-    |                 | -31       |                          | mA    |

| I <sub>SC-</sub>                   | Output Sink Short Circuit Current               | $R_L = 10\Omega$ to V+        |                 | 26        |                          | mA    |

Submit Document Feedback 4 intersil FN6800.9

June 11, 2015

**Electrical Specifications**  $V_S$ + = 5V,  $V_S$ - = 0V,  $R_L$  = Open,  $V_{CM}$  =  $V_S/2$ ,  $T_A$  = +25°C, unless otherwise specified. **Boldface limits apply over** the operating temperature range, -40°C to +125°C, unless otherwise specified. (Continued)

| PARAMETER                                      | DESCRIPTION                                   | TEST CONDITIONS                                                                                                          | MIN<br>(Note 8) | TYP              | MAX<br>(Note 8) | UNIT              |

|------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-------------------|

| AC SPECIFICATIONS                              |                                               |                                                                                                                          |                 | "                |                 |                   |

| GBWP                                           | Gain Bandwidth Product                        | $\begin{aligned} &V_{S}=\pm 2.5V\\ &A_{V}=100,R_{F}=100k\Omega,R_{G}=1k\Omega,\\ &R_{L}=10k\OmegatoV_{CM} \end{aligned}$ |                 | 5                |                 | MHz               |

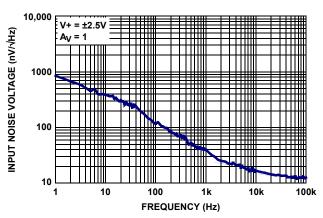

| e <sub>N</sub> V <sub>P-P</sub>                | Peak-to-Peak Input Noise Voltage              | V <sub>S</sub> = ±2.5V<br>f = 0.1Hz to 10Hz                                                                              |                 | 12               |                 | μV <sub>P-P</sub> |

| e <sub>N</sub>                                 | Input Noise Voltage Density                   | V <sub>S</sub> = ±2.5V<br>f = 1kHz                                                                                       |                 | 40               |                 | nV/√(Hz)          |

|                                                |                                               | V <sub>S</sub> = ±2.5V<br>f = 10kHz                                                                                      |                 | 16               |                 | nV/√(Hz)          |

| i <sub>N</sub>                                 | Input Noise Current Density                   | V <sub>S</sub> = ±2.5V<br>f = 1kHz                                                                                       |                 | 8                |                 | fA/√(Hz)          |

| z <sub>IN</sub>                                | Input Impedance                               |                                                                                                                          |                 | 10 <sup>12</sup> |                 | Ω                 |

| C <sub>in</sub>                                | Differential Input Capacitance                | V <sub>S</sub> = ±2.5V                                                                                                   |                 | 1.0              |                 | pF                |

|                                                | Common Mode Input Capacitance                 | f = 1MHz                                                                                                                 |                 | 1.3              |                 | pF                |

| TRANSIENT RESPON                               | ISE                                           |                                                                                                                          |                 |                  |                 |                   |

| SR                                             | Slew Rate                                     | V <sub>OUT</sub> = 0.5V to 4.5V                                                                                          |                 | 2.5              |                 | V/µs              |

| t <sub>r</sub> , t <sub>f</sub> , Small Signal | Rise Time, t <sub>r</sub> 10% to 90%          | V <sub>S</sub> = ±2.5V                                                                                                   |                 | 37               |                 | ns                |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%          | $A_V = +1$ , $V_{OUT} = 0.05V_{P-P}$ , $R_F = 0\Omega$ , $R_L = 10k\Omega$ , $C_L = 15pF$                                |                 | 42               |                 | ns                |

| t <sub>s</sub>                                 | Settling Time to 0.1%, 4V <sub>P-P</sub> Step | $\begin{split} &V_S=\pm 2.5V\\ &A_V=+1,R_F=0\Omega,R_L=10k\Omega,\\ &C_L=1.2pF \end{split}$                              |                 | 5.6              |                 | μs                |

#### NOTE:

<sup>8.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

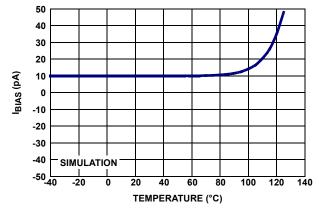

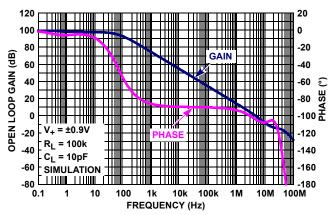

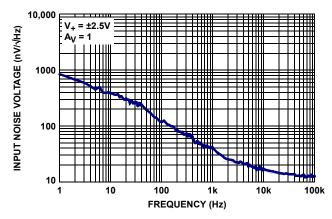

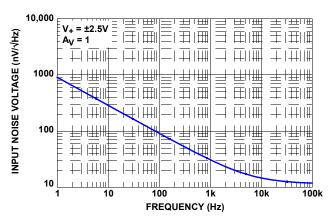

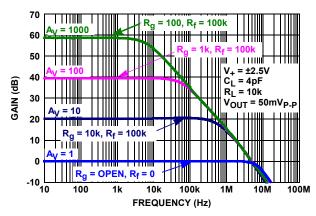

## Typical Performance Curves $v_S = \pm 2.5 \text{V}, v_{CM} = 0 \text{V}, R_L = \text{Open, unless otherwise specified.}$

FIGURE 2. INPUT BIAS CURRENT vs TEMPERATURE

FIGURE 3. INPUT NOISE VOLTAGE SPECTRAL DENSITY

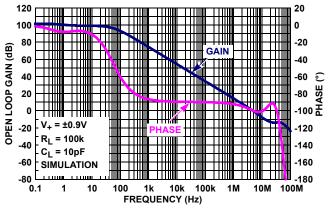

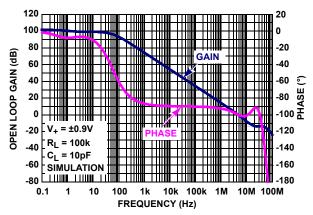

FIGURE 4. OPEN-LOOP GAIN, PHASE vs FREQUENCY,  $R_L$  = 100k $\Omega$ ,  $C_L$  = 10pF,  $V_S$  = ±0.9V

FIGURE 5. OPEN-LOOP GAIN, PHASE vs FREQUENCY, R  $_L$  = 100k  $\Omega,$  C  $_L$  = 10pF, V  $_S$  =  $\pm 2.5 V$

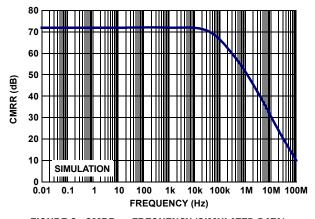

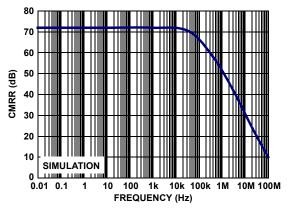

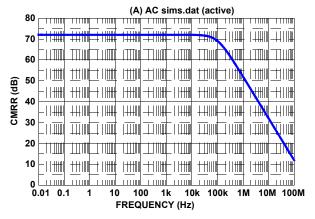

FIGURE 6. CMRR vs FREQUENCY (SIMULATED DATA)

FIGURE 7. PSRR vs FREQUENCY,  $V_S = \pm 0.9V$ ,  $\pm 2.5V$

## Typical Performance Curves $v_S = \pm 2.5 \text{V}, V_{CM} = 0 \text{V}, R_L = 0 \text{pen}, \text{ unless otherwise specified.}$ (Continued)

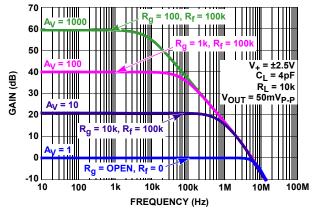

FIGURE 8. FREQUENCY RESPONSE vs CLOSED LOOP GAIN

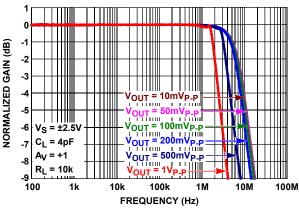

FIGURE 9. FREQUENCY RESPONSE vs V<sub>OUT</sub>

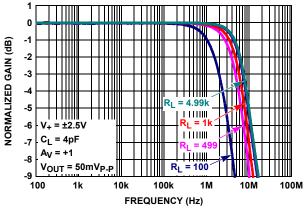

FIGURE 10. GAIN vs FREQUENCY vs RL

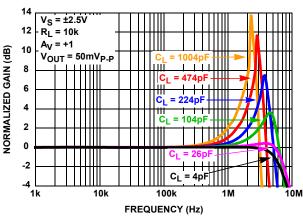

FIGURE 11. GAIN vs FREQUENCY vs CL

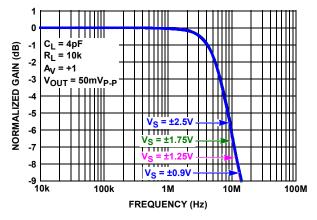

FIGURE 12. GAIN vs FREQUENCY vs SUPPLY VOLTAGE

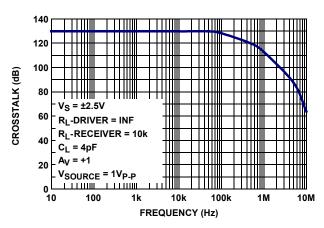

FIGURE 13. CROSSTALK, VS = ±2.5V

Submit Document Feedback FN6800.9 intersil June 11, 2015

## **Typical Performance Curves** $v_S = \pm 2.5 \text{V}, v_{CM} = 0 \text{V}, R_L = \text{Open, unless otherwise specified.}$ (Continued)

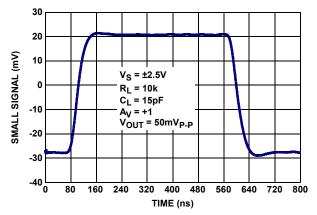

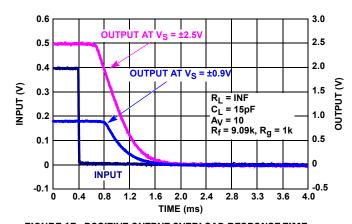

FIGURE 14. SMALL SIGNAL TRANSIENT RESPONSE,  $V_S = \pm 2.5V$

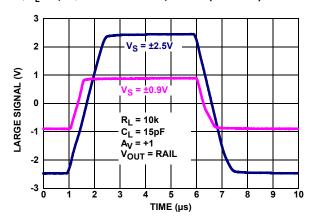

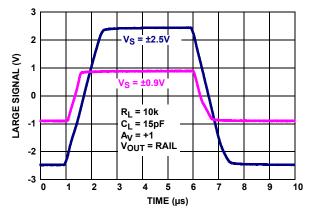

FIGURE 15. LARGE SIGNAL TRANSIENT RESPONSE vs  $R_L$ ,  $V_S = \pm 0.9V$ ,  $\pm 2.5V$

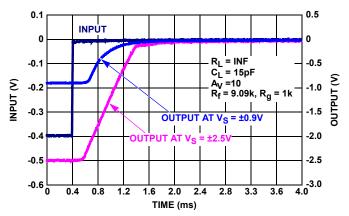

FIGURE 16. NEGATIVE OUTPUT OVERLOAD RESPONSE TIME,  $V_S = \pm 0.9V, \pm 2.5V$

FIGURE 17. POSITIVE OUTPUT OVERLOAD RESPONSE TIME,  $V_S = \pm 0.9V, \pm 2.5V$

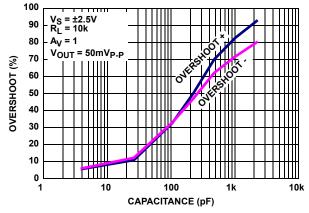

FIGURE 18. % OVERSHOOT vs LOAD CAPACITANCE,  $V_S = \pm 2.5V$

intersil

## **Applications Information**

#### **Functional Description**

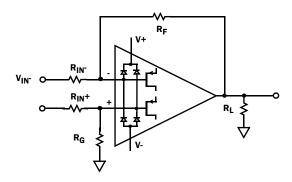

The ISL28114, ISL28214 and ISL28414 are single, dual and quad, CMOS rail-to-rail input, output (RRIO) micropower operational amplifiers. They are designed to operate from single supply (1.8V to 5.5V) or dual supply ( $\pm 0.9V$  to  $\pm 2.75V$ ). The parts have an input common mode range that extends 100mV above and below the power supply voltage rails. The output stage can swing to within 15mV of the supply rails with a  $10k\Omega$  load.

#### **Input ESD Diode Protection**

All input terminals have internal ESD protection diodes to both positive and negative supply rails, limiting the input voltage to within one diode beyond the supply rails. For applications where the input differential voltage is expected to exceed 0.5V, an external series resistor must be used to ensure the input currents never exceed 20mA (see Figure 19).

FIGURE 19. INPUT ESD DIODE CURRENT LIMITING

#### **Output Phase Reversal**

Output phase reversal is a change of polarity in the amplifier transfer function when the input voltage exceeds the supply voltage. The ISL28114, ISL28214 and ISL28414 are immune to output phase reversal, even when the input voltage is 1V beyond the supplies.

#### **Unused Channels**

If the application requires less than all amplifiers one channel. the user must configure the unused channel(s) to prevent it from oscillating. The unused channel(s) will oscillate if the input and output pins are floating. This will result in higher than expected supply currents and possible noise injection into the channel being used. The proper way to prevent this oscillation is to short the output to the inverting input and ground the positive input (as shown in Figure 20).

FIGURE 20. PREVENTING OSCILLATIONS IN UNUSED CHANNELS

#### **Power Dissipation**

It is possible to exceed the +125°C maximum junction temperatures under certain load, power supply conditions and ambient temperature conditions. It is therefore important to calculate the maximum junction temperature ( $T_{IM\Delta X}$ ) for all applications to determine if power supply voltages, load conditions, or package type need to be modified to remain in the safe operating area. These parameters are related using Equation 1:

$$T_{JMAX} = T_{MAX} + \theta_{JA} x PD_{MAXTOTAL}$$

(EQ. 1)

#### Where:

- P<sub>DMAXTOTAL</sub> is the sum of the maximum power dissipation of each amplifier in the package (PDMAX)

- PD<sub>MAX</sub> for each amplifier can be calculated using <u>Equation 2</u>:

$$PD_{MAX} = V_{S} \times I_{qMAX} + (V_{S} - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_{L}}$$

(EQ. 2)

#### Where:

- T<sub>MAX</sub> = Maximum ambient temperature

- θ<sub>JA</sub> = Thermal resistance of the package

- PD<sub>MAX</sub> = Maximum power dissipation of 1 amplifier

- V<sub>S</sub> = Total supply voltage

- I<sub>aMAX</sub> = Maximum quiescent supply current of 1 amplifier

- VOLITMAX = Maximum output voltage swing of the application

- R<sub>I</sub> = Load resistance

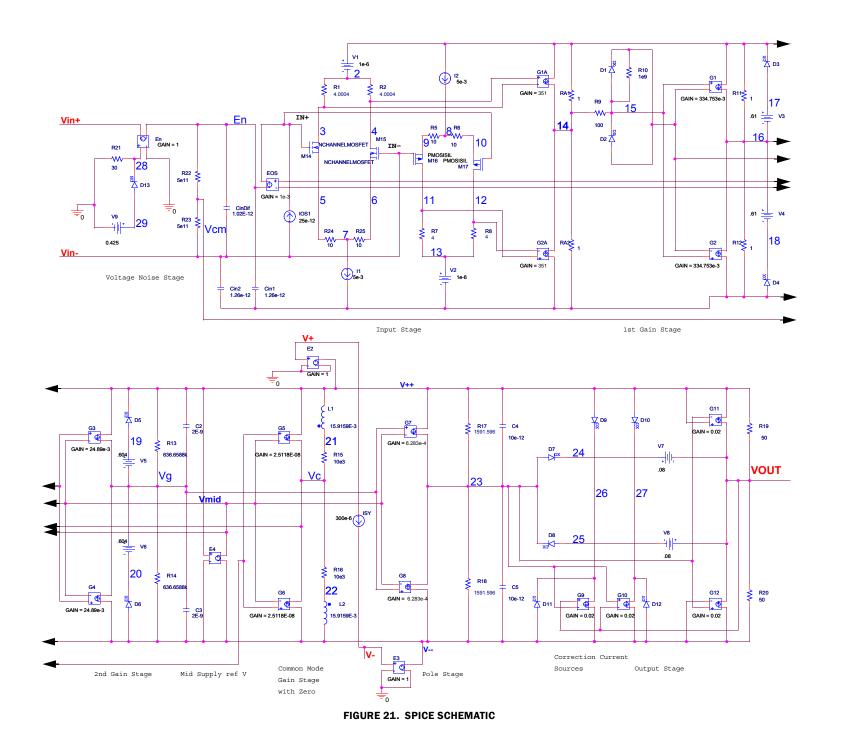

#### ISL28114, ISL28214 and ISL28414 SPICE Model

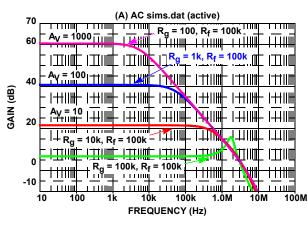

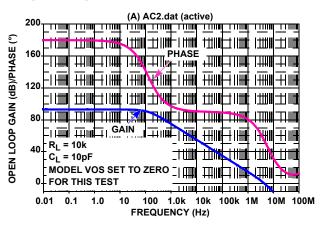

Figure 21 on page 11 shows the SPICE model schematic and Figure 22 on page 12 shows the net list for the SPICE model. The model is a simplified version of the actual device and simulates important AC and DC parameters. AC parameters incorporated into the model are: 1/f and flatband noise, Slew Rate, CMRR, Gain and Phase. The DC parameters are IOS, total supply current and output voltage swing. The model uses typical parameters given in the "Electrical Specifications" Table beginning on page 4. The AVOL is adjusted for 90dB with the dominate pole at 125Hz. The CMRR is set 72dB, f = 80kHz). The input stage models the actual device to present an accurate AC representation. The model is configured for ambient temperature of +25°C.

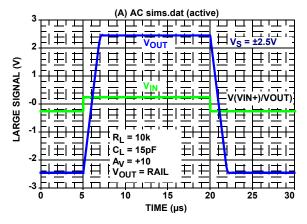

Figures 23 through 30 show the characterization vs simulation results for the Noise Voltage, Closed Loop Gain vs Frequency, Large Signal 5V Step Response and CMRR and Open Loop Gain Phase

#### **LICENSE STATEMENT**

The information in this SPICE model is protected under the United States copyright laws. Intersil Corporation hereby grants users of this macro-model hereto referred to as "Licensee", a nonexclusive, nontransferable license to use this model as long as the Licensee abides by the terms of this agreement. Before using this macro-model, the Licensee should read this license. If the Licensee does not accept these terms, permission to use the model is not granted.

The Licensee may not sell, loan, rent, or license the macro-model, in whole, in part, or in modified form, to anyone outside the Licensee's company. The Licensee may modify the macro-model to suit his/her specific applications, and the Licensee may make copies of this macro-model for use within their company only.

This macro-model is provided "AS IS, WHERE IS, AND WITH NO WARRANTY OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE."

In no event will Intersil be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of this macro-model. Intersil reserves the right to make changes to the product and the macro-model without prior notice.

Submit Document Feedback 10 Intersil FN6800.9

June 11, 2015

```

*ISL28114 Macromodel - covers following

R R15 VC 21 10e3

*products

*Voltage Noise

R R16 22 VC 10e3

*ISL28114

E En VIN+ EN 28 0 1

R R22 EN VCM 5e11

*ISL28214

D D13 29 28 DN

R_R23 VCM VIN- 5e11

*ISL28414

V_V9 29 0 0.425

L_L1 21 V++ 15.9159e-3

R R21 28 0 30

L L2 22 V-- 15.9159e-3

*Revision History:

*Revision C, LaFontaine October 20th 2011

*Input Stage

*Pole Stage

M M14 3 1 5 5 NCHANNELMOSFET

*Model for Noise to match measured part,

G G7 V++ 23 VG VMID 6.283e-4

* quiescent supply currents,

M M15 4 VIN- 6 6 NCHANNELMOSFET

G G8 V-- 23 VG VMID 6.283e-4

*CMRR 72dB

M_M16 11 VIN- 9 9 PMOSISIL

R_R17 23 V++ 1591.596

*fcm=100kHz, AVOL 90dB f=125Hz, SR =

M M17 12 1 10 10 PMOSISIL

R R18 V-- 23 1591.596

I I1 7 V-- DC 5e-3

*2.5V/us, GBWP 5MHz, 2nd pole 10Mhz

C C4 23 V++ 10e-12

C_C5 V-- 23 10e-12

output voltage clamp and short ckt current

I_I2 V++ 8 DC 5e-3

I_IOS VIN- 1 DC 25e-12

*Output Stage with Correction Current

G G1A V++ 14 4 3 351

G_G2A V-- 14 11 12 351

*Copyright 2011 by Intersil Corporation

Sources

*Refer to data sheet "LICENSE

V V1 V++ 2 1e-6

G G9 26 V-- VOUT 23 0.02

*STATEMENT" Use of this model indicates

V V2 13 V-- 1e-6

G_G10 27 V-- 23 VOUT 0.02

G_G11 VOUT V++ V++ 23 0.02

*your acceptance with the terms and

R R1 3 2 4.0004

*provisions in the License Statement.

R R2 4 2 4.0004

G G12 V-- VOUT 23 V-- 0.02

R R3 5 7 10

V V7 24 VOUT .08

*Intended use:

R_R47610

V_V8 VOUT 25 .08

D_D7 23 24 DX

*This Pspice Macromodel is intended to give

R R5 9 8 10

*typical DC and AC performance

R R6 8 10 10

D_D8 25 23 DX

*characteristics under a wide range of

R R7 13 11 4

D D9 V++ 26 DX

*external circuit configurations using

R_R8 13 12 4

D_D10 V++ 27 DX

*compatible simulation platforms - such as

R RA1 14 V++ 1

D D11 V-- 26 DY

*iSim PE.

R RA2 V-- 14 1

D D12 V-- 27 DY

C CinDif VIN- EN 1.02E-12

R R19 VOUT V++ 50

*Device performance features supported by

C_Cin1 V-- EN 1.26e-12

R R20 V-- VOUT 50

C_Cin2 V-- VIN- 1.26e-12

.model pmosisil pmos (kp=16e-3 vto=-0.6)

*this model:

*Typical, room temp., nominal power supply

.model NCHANNELMOSFET nmos (kp=3e-3

*voltages used to produce the following

*1st Gain Stage

vto=0.6)

.model DN D(KF=6.69e-9 AF=1)

*characteristics:

G_G1 V++ 16 15 VMID 334.753e-3

*Open and closed loop I/O impedances

G G2 V-- 16 15 VMID 334.753e-3

.MODEL DX D(IS=1E-12 Rs=0.1)

*Open loop gain and phase

V_V3 17 16 .61

.MODEL DY D(IS=1E-15 BV=50 Rs=1)

*Closed loop bandwidth and frequency

V V4 16 18 .61

.ends ISL28114

D_D1 15 VMID DX

D D2 VMID 15 DX

*Loading effects on closed loop frequency

*response

D D3 17 V++ DX

D D4 V-- 18 DX

*Input noise terms including 1/f effects

*Slew rate

R R9 15 14 100

*Input and Output Headroom limits to I/O

R R10 15 VMID 1e9

R R11 16 V++ 1

*voltage swing

R_R12 V-- 16 1

*Supply current at nominal specified supply

*voltages

*2nd Gain Stage

*Device performance features NOT

G_G3 V++ VG 16 VMID 24.893e-3

*supported by this model

G G4 V-- VG 16 VMID 24.893e-3

*Harmonic distortion effects

V V5 19 VG .604

*Disable operation (if any)

V_V6 VG 20 .604

*Thermal effects and/or over temperature

D_D5 19 V++ DX

D D6 V-- 20 DX

*parameter variation

*Limited performance variation vs. supply

R_R13 VG V++ 636.658e3

R R14 V-- VG 636.658e3

*voltage is modeled

*Part to part performance variation due to

C C2 VG V++ 2E-09

C_C3 V-- VG 2E-09

*normal process parameter spread

*Any performance difference arising from

*Mid supply Ref

*different packaging

E_E4 VMID V-- V++ V-- 0.5

* source

* Connections: +input

E E2 V++ 0 V+ 0 1

E E3 V-- 0 V- 0 1

-input

I_ISY V+ V- DC 300e-6

+Vsupply

-Vsupply

*Common Mode Gain Stage with Zero

output

G G5 V++ VC VCM VMID 2.5118E-8

```

FIGURE 22. SPICE NET LIST

G G6 V-- VC VCM VMID 2.5118E-8

E EOS 1 EN VC VMID 1e-3

.subckt ISL28114 Vin+ Vin- V+ V- VOUT

source ISL28114 DS rev2

#### **Characterization vs Simulation Results**

FIGURE 23. CHARACTERIZED INPUT NOISE VOLTAGE

FIGURE 24. SIMULATED INPUT NOISE VOLTAGE

FIGURE 25. CHARACTERIZED CLOSED LOOP GAIN vs FREQUENCY

FIGURE 26. SIMULATED CLOSED LOOP GAIN vs FREQUENCY

FIGURE 27. CHARACTERIZED LARGE SIGNAL TRANSIENT RESPONSE vs  $R_L$ ,  $V_S = \pm 0.9V$ ,  $\pm 2.5V$

FIGURE 28. SIMULATED LARGE SIGNAL TRANSIENT RESPONSE vs  $R_L, V_S = \pm 0.9V, \pm 2.5V$

Submit Document Feedback 13 FN6800.9

June 11, 2015

#### **Characterization vs Simulation Results (Continued)**

FIGURE 29. SIMULATED (DESIGN) OPEN-LOOP GAIN, PHASE vs FREQUENCY

FIGURE 30. SIMULATED (SPICE) OPEN-LOOP GAIN, PHASE vs FREQUENCY

FIGURE 31. SIMULATED (DESIGN) CMRR

FIGURE 32. SIMULATED (SPICE) CMRR

Submit Document Feedback

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to Web to make sure you have the latest Rev.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 11, 2015      | FN6800.9 | Electrical Spec table, page 5 - Input Noise Voltage Density (eN) added a spec at 10kHz (typical spec).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| October 26, 2012   | FN6800.8 | Added SOT23-8 package on page 1 to description and features. Ordering Information on page 2 - Added ISL28214FHZ parts and Note 5 reference. Added Lead Finish Note to Ordering information for 8 LD SOT-23 parts. Thermal Information on page 4 - Added 8 LD SOT-23 package with Tja and Tjc Added P8.064 POD on page 23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| April 13, 2012     | FN6800.7 | Changed the low supply current in "Features" and description on page 1 from 360µA to 390µA. Removed ISL28114FEV1Z-T7 Coming Soon parts from "Ordering Information" on page 2. Removed applicable pinout from page 3. On page 4, changed MIN/MAX limits for "VOS" at 25 °C from -5/5mV to -4/4mV. On page 4, changed MIN/MAX limits for "VOS" at -40 °C to 125 °C from -6/6mV to -5/5mV. On page 4, changed "TCVOS" TYP from 2µV/°C to 5µV/°C. On page 4, changed MAX limit for "Is" MAX at 25 °C from 360µA to 390µA. On page 4, changed MAX limit for "Is" MAX at -40 °C to 125 °C from 400µA to 475µA. Revised Figure 8 on page 7. Revised Figure 11 on page 7. Revised Figure 18 on page 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| January 3, 2012    | FN6800.6 | Revised "SPICE SCHEMATIC" on page 11 and "SPICE NET LIST" on page 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| May 18, 2011       | FN6800.5 | - On page 3, Pin Descriptions: Circuit 3 diagram, removed anti-parallel diodes from the IN+ to INterminals.  - On page 4, Absolute Maximum Ratings: changed Differential Input Voltage from "0.5V" to "V-0.5V to V+ + 0.5V"  - On page 4, updated CMRR and PSRR parameters in Electrical Specifications table with test condition specifying -40°C to 125°C typical parameter.  - On page 5, updated Note 8, referenced in MIN and MAX column headings of Electrical Specifications table, from "Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested." to new standard "Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design."  - On page 9, under "Input ESD Diode Protection," removed "They also contain back to-back diodes across the input terminals." Removed "Although the amplifier is fully protected, high input slew rates that exceed the amplifier slew rate (±2.5V/µs) may cause output distortion."  - On page 9, Figure 19: updated circuit schematic by removing back-to-back input protection diodes.  - On page 11 replaced SPICE schematic (Figure 21)  - On page 12 replaced SPICE Netlist (Figure 22)  - On page 14 replaced Figure 24  - On page 14 replaced Figure 32 |

| September 23, 2010 | FN6800.4 | Added new SC70 pinout package extension as follows:  Added to Related Literature on page 1 "See AN1547 for "ISL28414TSSOPEVAL1Z Evaluation Board User's Guide".  Added to ordering information ISL28114FEV1Z-T7 and ISL28114FEV1Z-T7A and Evaluation boards.  Added to Pin Configurations new pinout for ISL28114FEV1Z.  Added in Pin Descriptions ISL28114FEV1Z SC70 pin description column.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| July 28, 2010      |          | Changed Note 7 on page page 4 from "For $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside." to "For $\theta_{JC}$ , the "case temp" location is taken at the package top center."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| May 13, 2010       |          | Added "Related Literature" on page 1.  Changed package outline drawing from MDP0038 to P5.064A on page 2 and page 18.  MDP0038 package contained 2 packages for both the 5 and 6 Ld SOT-23. MDP0038 was obsoleted and the packages were separated and made into 2 separate package outline drawings; P5.064A and P6.064A. Changes to the 5 Ld SOT-23 were to move dimensions from table onto drawing, add land pattern and add JEDEC reference number.  Added Note 5 to "Ordering Information" on page 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Submit Document Feedback 15 FN6800.9

June 11, 2015

## Revision History (Continued)

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to Web to make sure you have the latest Rev. (Continued)

| DATE              | REVISION | CHANGE                                                                                                                                                                       |

|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 16, 2009 | FN6800.3 | Removed "Coming Soon" from MSOP package options in the "Ordering Information" on page 2. Updated the Theta JA for the MSOP package option from 170°C/W to 180°C/W on page 4. |

| November 17, 2009 | FN6800.2 | Removed "Coming Soon" from SC70 and SOT-23 package options in the "Ordering Information" on page 2.                                                                          |

| November 12, 2009 | FN6800.1 | Changed theta Ja to 250 from 300. Added license statement (page 10) and reference in spice model (page 12).                                                                  |

| October 23, 2009  | FN6800.0 | Initial Release                                                                                                                                                              |

## **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

Submit Document Feedback 16 intersil FN6800.9

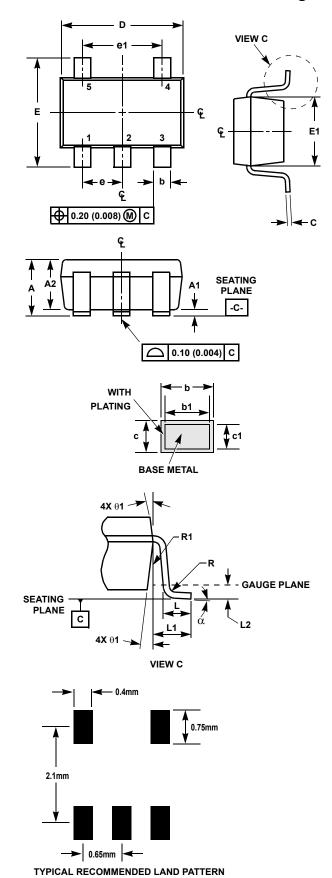

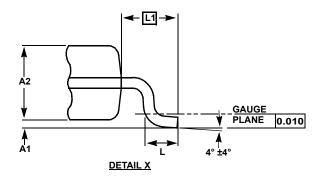

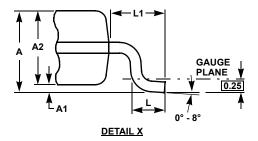

## Small Outline Transistor Plastic Packages (SC70-5)

P5.049

5 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE

|        | INC   | HES            | MILLIMETERS |                |       |

|--------|-------|----------------|-------------|----------------|-------|

| SYMBOL | MIN   | MAX            | MIN         | MAX            | NOTES |

| Α      | 0.031 | 0.043          | 0.80        | 1.10           | -     |

| A1     | 0.000 | 0.004          | 0.00        | 0.10           | -     |

| A2     | 0.031 | 0.039          | 0.80        | 1.00           | -     |

| b      | 0.006 | 0.012          | 0.15        | 0.30           | -     |

| b1     | 0.006 | 0.010          | 0.15        | 0.25           |       |

| С      | 0.003 | 0.009          | 0.08        | 0.22           | 6     |

| c1     | 0.003 | 0.009          | 0.08        | 0.20           | 6     |

| D      | 0.073 | 0.085          | 1.85        | 2.15           | 3     |

| Е      | 0.071 | 0.094          | 1.80        | 2.40           | -     |

| E1     | 0.045 | 0.053          | 1.15        | 1.35           | 3     |

| е      | 0.025 | 0.0256 Ref     |             | Ref            | -     |

| e1     | 0.051 | 0.0512 Ref     |             | Ref            | -     |

| L      | 0.010 | 0.018          | 0.26        | 0.46           | 4     |

| L1     | 0.017 | Ref.           | 0.420       | Ref.           | -     |

| L2     | 0.006 | BSC            | 0.15 BSC    |                |       |

| α      | 0°    | 8 <sup>0</sup> | 0°          | 8 <sup>0</sup> | -     |

| N      | Ę     | 5              | 5           |                | 5     |

| R      | 0.004 | -              | 0.10        | -              |       |

| R1     | 0.004 | 0.010          | 0.15        | 0.25           |       |

Rev. 3 7/07

#### NOTES:

- 1. Dimensioning and tolerances per ASME Y14.5M-1994.

- 2. Package conforms to EIAJ SC70 and JEDEC MO-203AA.

- 3. Dimensions D and E1 are exclusive of mold flash, protrusions, or gate burrs.

- 4. Footlength L measured at reference to gauge plane.

- 5. "N" is the number of terminal positions.

- 6. These Dimensions apply to the flat section of the lead between 0.08mm and 0.15mm from the lead tip.

- 7. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only.

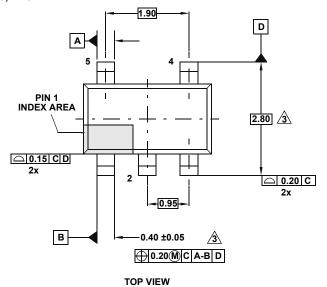

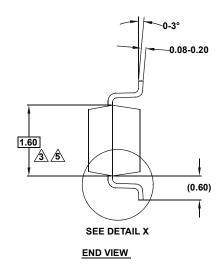

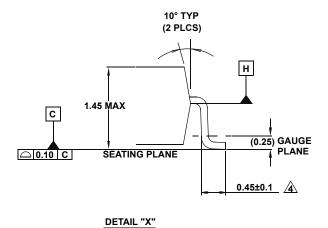

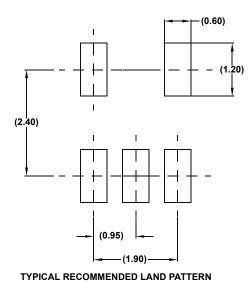

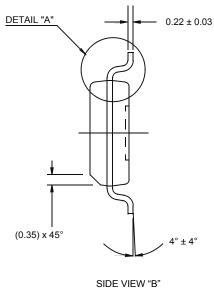

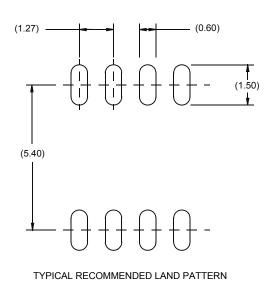

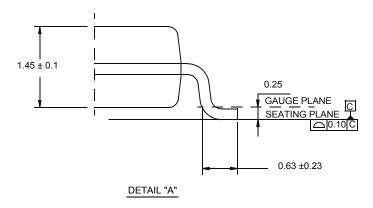

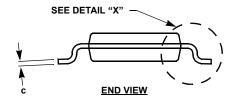

## **Package Outline Drawing**

#### P5.064A

5 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE Rev 0, 2/10

NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 3. Dimension is exclusive of mold flash, protrusions or gate burrs.

- 4. Foot length is measured at reference to guage plane.

- 5. This dimension is measured at Datum "H".

- 6. Package conforms to JEDEC MO-178AA.

Submit Document Feedback 18 intersil FN6800.9

June 11, 2015

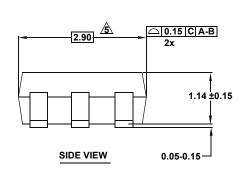

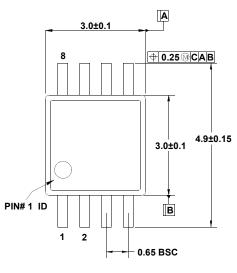

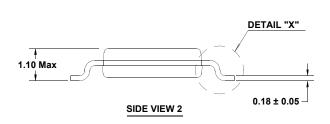

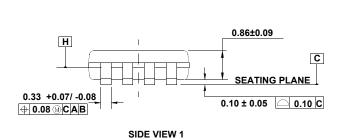

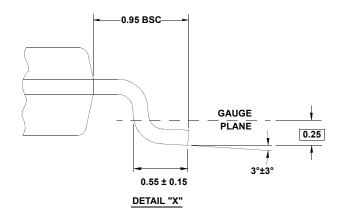

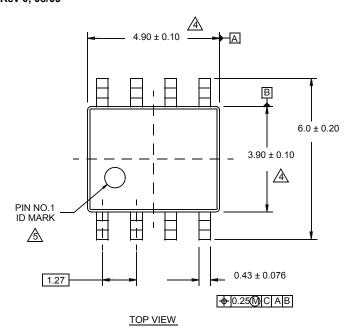

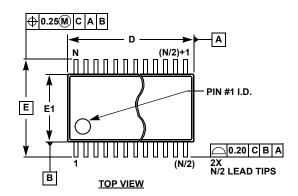

## **Package Outline Drawing**

#### M8.118A

**8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE (MSOP)** Rev 0, 9/09

**TOP VIEW**

#### NOTES:

- 1. Dimensions are in millimeters.

- Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSE Y14.5m-1994.

- Plastic or metal protrusions of 0.15mm max per side are not

- Plastic interlead protrusions of 0.25mm max per side are not included.

- 5. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 6. This replaces existing drawing # MDP0043 MSOP 8L.

Submit Document Feedback 19 intersil FN6800.9

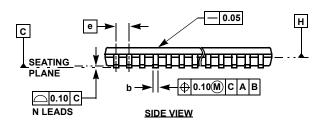

## **Package Outline Drawing**

#### M8.15E **8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE** Rev 0, 08/09

#### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- Unless otherwise specified, tolerance: Decimal ± 0.05

- Dimension does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 identifier may be either a mold or mark feature.

- Reference to JEDEC MS-012.

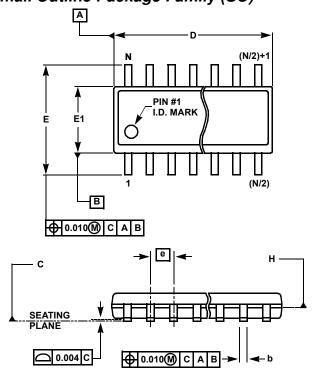

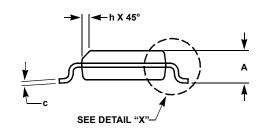

## Small Outline Package Family (SO)

#### **MDP0027**

#### **SMALL OUTLINE PACKAGE FAMILY (SO)**

|        |       | INCHES |                  |                           |                  |                  |                  |           |       |

|--------|-------|--------|------------------|---------------------------|------------------|------------------|------------------|-----------|-------|

| SYMBOL | SO-8  | SO-14  | SO16<br>(0.150") | SO16 (0.300")<br>(SOL-16) | SO20<br>(SOL-20) | SO24<br>(SOL-24) | SO28<br>(SOL-28) | TOLERANCE | NOTES |

| Α      | 0.068 | 0.068  | 0.068            | 0.104                     | 0.104            | 0.104            | 0.104            | MAX       | -     |

| A1     | 0.006 | 0.006  | 0.006            | 0.007                     | 0.007            | 0.007            | 0.007            | ±0.003    | -     |

| A2     | 0.057 | 0.057  | 0.057            | 0.092                     | 0.092            | 0.092            | 0.092            | ±0.002    | -     |

| b      | 0.017 | 0.017  | 0.017            | 0.017                     | 0.017            | 0.017            | 0.017            | ±0.003    | -     |

| С      | 0.009 | 0.009  | 0.009            | 0.011                     | 0.011            | 0.011            | 0.011            | ±0.001    | -     |

| D      | 0.193 | 0.341  | 0.390            | 0.406                     | 0.504            | 0.606            | 0.704            | ±0.004    | 1, 3  |

| Е      | 0.236 | 0.236  | 0.236            | 0.406                     | 0.406            | 0.406            | 0.406            | ±0.008    | -     |

| E1     | 0.154 | 0.154  | 0.154            | 0.295                     | 0.295            | 0.295            | 0.295            | ±0.004    | 2, 3  |

| е      | 0.050 | 0.050  | 0.050            | 0.050                     | 0.050            | 0.050            | 0.050            | Basic     | -     |

| L      | 0.025 | 0.025  | 0.025            | 0.030                     | 0.030            | 0.030            | 0.030            | ±0.009    | -     |

| L1     | 0.041 | 0.041  | 0.041            | 0.056                     | 0.056            | 0.056            | 0.056            | Basic     | -     |

| h      | 0.013 | 0.013  | 0.013            | 0.020                     | 0.020            | 0.020            | 0.020            | Reference | -     |

| N      | 8     | 14     | 16               | 16                        | 20               | 24               | 28               | Reference | -     |

**NOTES**

Rev. M 2/07

- 1. Plastic or metal protrusions of 0.006" maximum per side are not included.

- 2. Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994

Submit Document Feedback

intersil

## Thin Shrink Small Outline Package Family (TSSOP)

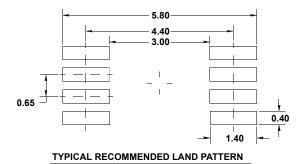

## MDP0044 THIN SHRINK SMALL OUTLINE PACKAGE FAMILY

|        |       | MIL   |       |       |       |             |

|--------|-------|-------|-------|-------|-------|-------------|

| SYMBOL | 14 LD | 16 LD | 20 LD | 24 LD | 28 LD | TOLERANCE   |

| Α      | 1.20  | 1.20  | 1.20  | 1.20  | 1.20  | Max         |

| A1     | 0.10  | 0.10  | 0.10  | 0.10  | 0.10  | ±0.05       |

| A2     | 0.90  | 0.90  | 0.90  | 0.90  | 0.90  | ±0.05       |

| b      | 0.25  | 0.25  | 0.25  | 0.25  | 0.25  | +0.05/-0.06 |

| С      | 0.15  | 0.15  | 0.15  | 0.15  | 0.15  | +0.05/-0.06 |

| D      | 5.00  | 5.00  | 6.50  | 7.80  | 9.70  | ±0.10       |

| Е      | 6.40  | 6.40  | 6.40  | 6.40  | 6.40  | Basic       |

| E1     | 4.40  | 4.40  | 4.40  | 4.40  | 4.40  | ±0.10       |

| е      | 0.65  | 0.65  | 0.65  | 0.65  | 0.65  | Basic       |

| L      | 0.60  | 0.60  | 0.60  | 0.60  | 0.60  | ±0.15       |

| L1     | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | Reference   |

Rev. F 2/07

#### NOTES:

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

- Dimension "E1" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm per side.

- 3. Dimensions "D" and "E1" are measured at dAtum Plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

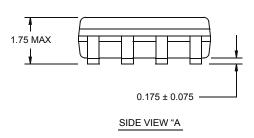

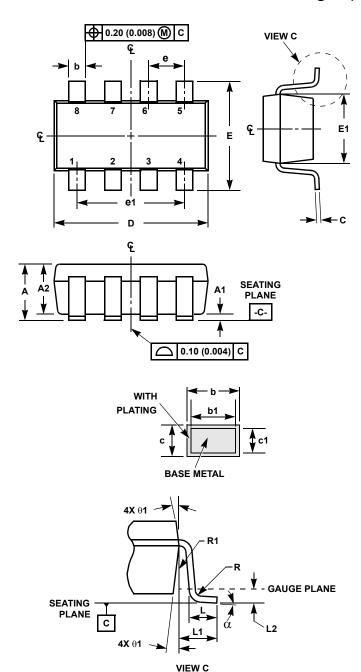

#### Small Outline Transistor Plastic Packages (SOT23-8)

P8.064 **8 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE**

|        | INCHES     |                | MILLIMETERS |                |       |

|--------|------------|----------------|-------------|----------------|-------|

| SYMBOL | MIN        | MAX            | MIN         | MAX            | NOTES |

| Α      | 0.036      | 0.057          | 0.90        | 1.45           | -     |

| A1     | 0.000      | 0.0059         | 0.00        | 0.15           | -     |

| A2     | 0.036      | 0.051          | 0.90        | 1.30           | -     |

| b      | 0.009      | 0.015          | 0.22        | 0.38           | -     |

| b1     | 0.009      | 0.013          | 0.22        | 0.33           |       |

| С      | 0.003      | 0.009          | 0.08        | 0.22           | 6     |

| c1     | 0.003      | 0.008          | 0.08        | 0.20           | 6     |

| D      | 0.111      | 0.118          | 2.80        | 3.00           | 3     |

| E      | 0.103      | 0.118          | 2.60        | 3.00           | -     |

| E1     | 0.060      | 0.067          | 1.50        | 1.70           | 3     |

| е      | 0.0256 Ref |                | 0.65 Ref    |                | -     |

| e1     | 0.0768 Ref |                | 1.95 Ref    |                | -     |

| L      | 0.014      | 0.022          | 0.35        | 0.55           | 4     |

| L1     | 0.024 Ref. |                | 0.60 Ref.   |                |       |

| L2     | 0.010 Ref. |                | 0.25 Ref.   |                |       |

| N      | 8          |                | 8           |                | 5     |

| R      | 0.004      | -              | 0.10        | -              |       |

| R1     | 0.004      | 0.010          | 0.10        | 0.25           |       |

| α      | 0°         | 8 <sup>0</sup> | 0°          | 8 <sup>0</sup> | -     |

Rev. 2 9/03

#### NOTES:

- 1. Dimensioning and tolerance per ASME Y14.5M-1994.

- 2. Package conforms to EIAJ SC-74 and JEDEC MO178BA.

- 3. Dimensions D and E1 are exclusive of mold flash, protrusions, or gate burrs.

- 4. Footlength L measured at reference to gauge plane.

- 5. "N" is the number of terminal positions.

- 6. These Dimensions apply to the flat section of the lead between 0.08mm and 0.15mm from the lead tip.

- 7. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com