Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Data Sheet September 7, 2010 FN6123.3

## I<sup>2</sup>C LCD Module Calibrator

The ISL45045 is specifically designed to work in notebook applications where the system's EEPROM is powered up before the rest of the devices on the  $I^2C$  bus. This enables data to be downloaded to a graphics card. The ESD protection scheme on the SDA, SCL and SCL\_S pins prevent the loading of the  $I^2C$  bus during the initialization period prior to full power-up of the notebook.

The VCOM voltage of an LCD panel needs to be adjusted to remove flicker. This part provides a digital interface to control the sink-current output that attaches to an external voltage divider. The increase in output sink current lowers the voltage on the external divider, which is applied to an external VCOM buffer amplifier. The desired VCOM setting is loaded from an external source via a standard two-wire I<sup>2</sup>C serial interface. At power-up, the part automatically comes up at the last programmed setting in an on-board 7-bit EEPROM.

An external resistor attaches to the SET pin and sets the full-scale sink current that determines the lowest voltage of the external voltage divider.

The ISL45045 is available in an 10 Ld 3mmx3mm TDFN package with a maximum thickness of 0.8mm for ultra thin LCD panel design.

## **Ordering Information**

| PART<br>NUMBER<br>(Note) | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG.<br># |

|--------------------------|-----------------|------------------------|----------------------|-------------------|

| ISL45045IRZ              | 045Z            | 0 to +85               | 10 Ld 3x3 TDFN       | L10.3x3A          |

| ISL45045IRZ-T*           | 045Z            | 0 to +85               | 10 Ld 3x3 TDFN       | L10.3x3A          |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- · 128-Step Adjustable Sink Current Output

- 2.25V to 3.6V Logic Supply Voltage Operating Range (2.6V Minimum Programming Voltage)

- Analog Supply Voltage Range 4.5V to 18V for VDD from 2.6V to 3.6V; 4.5V to 13V for VDD from 2.25V to 3.6V

- SDA, SCL, SCL\_S pins tolerant to system power-up sequences (i.e will not alter I<sup>2</sup>C bus state)

- I<sup>2</sup>C Interface (Slave and Transmitter) -- Address: 1001111

- · On-board 7-bit EEPROM

- Output adjustment SET Pin

- · Output Guaranteed Monotonic Over-Temperature

- Thin 10 Ld 3mmx3mm DFN (0.8mm max)

- · Pb-Free (RoHS Compliant)

### **Applications**

· LCD Panels

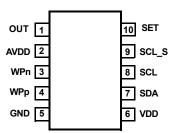

### **Pinout**

ISL45045 (10 LD TDFN) TOP VIEW

## Pin Descriptions

| PIN              | TYPE   | PULL U/D             | FUNCTION                                                                                                                                                                                                                                       | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT              | Output |                      | Adjustable Sink Current Output Pin. The Current sinks into the OUT pin is equal to the DAC setting times the maximum adjustable sink current divided by 128. See SET pin function description for the maximum adjustable sink current setting. | 500Ω<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AV <sub>DD</sub> | Supply |                      | High-Voltage Analog Supply. Bypass to GND with 0.1μF Capacitor.                                                                                                                                                                                | AV <sub>DD</sub> ->600kΩ ->600k |

| WPn              | Input  | Pull-Down            | Write Protection Active Low. CMOS Level.                                                                                                                                                                                                       | WPn PULL DOWN GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WPp              | Output |                      | Output Pin. Opposite Logic Level of WPn Pin.                                                                                                                                                                                                   | WPp WPn WPn WPn GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND              | Supply |                      | Ground.                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDD              | Supply |                      | System Power Supply Input. Bypass to GND With 0.1µF Capacitor.                                                                                                                                                                                 | VDD  dV/dT  TRIGGER  GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDA              | In/Out | Open Drain<br>Output | I <sup>2</sup> C Serial Data Input/Output.                                                                                                                                                                                                     | SDA DE CONTROL OF TRIGGER GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## Pin Descriptions (Continued)

| PIN   | TYPE   | PULL U/D             | FUNCTION                                                                                                                                                                                                                     | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL   | In/Out | Open Drain<br>Output | Serial Clock Input for Internal and Inter-IC Use.                                                                                                                                                                            | SCL DE CONTROL OF THE |

| SCL_S | Input  |                      | Serial Clock Input.                                                                                                                                                                                                          | SCL_S GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SET   | Analog |                      | Maximum Sink Current Adjustment Point. Connect a resistor from SET to GND to set the maximum adjustable sink current of the OUT pin. The maximum adjustable sink current is equal to (AV <sub>DD</sub> /20) divided by RSET. | SET D D D D D D D D D D D D D D D D D D D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

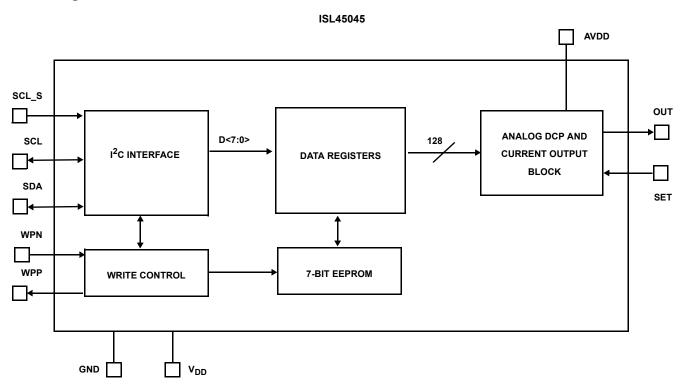

## Block Diagram

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to Ground |

|---------------------------|

| SET0.3V to +4V            |

| AVDD0.3V to +20V          |

| Output Voltages to GND    |

| OUT0.3V to +20V           |

| ESD Rating                |

| Human Body Model          |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | $\theta_{JA}$ (°C/W) |

|--------------------------------------------------|----------------------|

| 10 Ld TDFN Package                               | 90                   |

| Moisture Sensitivity (see Technical Brief TB363) |                      |

| All Packages                                     | Level 1              |

| Maximum Junction Temperature (Plastic Package)   | +150°C               |

| Maximum Storage Temperature Range65°             | C to +150°C          |

| Pb-free Reflow Profile                           | ee link below        |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                      |

| Erase/Write Cycles                               | 10,000               |

| Data Retention                                   | ars @ +85°C          |

### **Operating Conditions**

Temperature Range . . . . . . . . . . 0°C to +85°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE

1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

### **Electrical Specifications**

Test Conditions:  $V_{DD}$  = 3V, AVDD = 10V, OUT = 5V,  $R_{SET}$  = 24.9k $\Omega$ ; Unless Otherwise Specified. Typicals are at  $T_A$  = +25°C

| PARAMETER                                          | SYMBOL             | TEST CONDITIONS                   | TEMP<br>(°C) | MIN<br>(Note 7) | TYP      | MAX<br>(Note 7) | UNITS |

|----------------------------------------------------|--------------------|-----------------------------------|--------------|-----------------|----------|-----------------|-------|

| DC CHARACTERISTICS                                 |                    |                                   |              |                 |          |                 | •     |

| V <sub>DD</sub> Supply Range Operating             | $V_{DD}$           |                                   | Full         | 2.25            | -        | 3.6             | V     |

| V <sub>DD</sub> Supply Range EEPROM<br>Programming | V <sub>DD</sub>    |                                   | Full         | 2.6             | -        | 3.6             | V     |

| V <sub>DD</sub> Supply Current                     | I <sub>DD</sub>    | (Note 4)                          | Full         | -               | -        | 50              | μΑ    |

| AVDD Supply Range                                  | AVDD               | VDD range 2.6V to 3.6V            | Full         | 4.5             | -        | 18              | V     |

|                                                    |                    | VDD range 2.25V to 3.6V           |              | 4.5             | -        | 13              | V     |

| AVDD Supply Current                                | IAVDD              | (Note 2)                          | Full         | -               | -        | 25              | μΑ    |

| SET Voltage Resolution                             | SET <sub>VR</sub>  |                                   | Full         |                 | 7        | l .             | Bits  |

| SET Differential Nonlinearity                      | SET <sub>DN</sub>  | Monotonic Over-Temperature        | Full         | -               | -        | ±1              | LSB   |

| SET Zero-Scale Error                               | SETZSE             |                                   | Full         | -               | -        | ±2              | LSB   |

| SET Full-Scale Error                               | SET <sub>FSE</sub> |                                   | Full         | -               | -        | ±8              | LSB   |

| SET Current                                        | ISET               | Through R <sub>SET</sub> (Note 5) | Full         | -               | 20       | -               | μΑ    |

| SET External Resistance                            | SETER              | To GND, AVDD = 20V                | Full         | 10              | -        | 200             | kΩ    |

|                                                    |                    | To GND, AVDD = 4.5V               | Full         | 2.25            | -        | 45              | kΩ    |

| AVDD to SET Voltage<br>Attenuation                 | AVDD to<br>SET     | (Note 3)                          | Full         | -               | 1:20     | -               | V/V   |

| OUT Settling Time                                  | OUT <sub>ST</sub>  | to ±0.5 LSB Error Band (Note 3)   | Full         | -               | 8        | -               | μs    |

| OUT Voltage Range                                  | V <sub>OUT</sub>   |                                   | Full         | VSET + 0.5V     | -        | 13              | V     |

| SET Voltage Drift                                  | SET <sub>VD</sub>  | (Note 3)                          | 25 to 55     | -               | <10      | -               | mV    |

| SDA, SCL, SCL_S, WPn Input<br>Logic High           | VIH                |                                   | Full         | 0.7*VDD         | -        | -               | V     |

| SDA, SCL, SCL_S, WPn Input<br>Logic Low            | VIL                |                                   | Full         | -               | -        | 0.3*VDD         | V     |

| SDA, SCL, SCL_S, WPn<br>Hysteresis                 |                    | (Note 3)                          | Full         | -               | 0.22*VDD | -               | V     |

FN6123.3 September 7, 2010

### **Electrical Specifications**

Test Conditions:  $V_{DD}$  = 3V, AVDD = 10V, OUT = 5V,  $R_{SET}$  = 24.9k $\Omega$ ; Unless Otherwise Specified. Typicals are at  $T_A$  = +25°C **(Continued)**

| PARAMETER                                             | SYMBOL             | TEST CONDITIONS            | TEMP<br>(°C) | MIN<br>(Note 7) | TYP         | MAX<br>(Note 7) | UNITS |

|-------------------------------------------------------|--------------------|----------------------------|--------------|-----------------|-------------|-----------------|-------|

| WPn IL                                                | IL <sub>WPN</sub>  |                            | Full         | 15              | 25          | 35              | μΑ    |

| SDA, SCL Output Logic High                            | VOHS               | @ 3mA                      | Full         | 0.4             | -           | -               | V     |

| SDA, SCL Output Logic Low                             | VOLS               | @ 3mA                      | Full         | -               | -           | 0.4             | V     |

| WPp Output Logic High                                 | VOH <sub>WPP</sub> | @ 3mA                      | Full         | VDD - 0.4       | -           | -               | V     |

| WPp Output Logic Low                                  | VOLWPP             | @ 3mA                      | Full         | 0.4             | -           | -               | V     |

| WPp Delay                                             | t <sub>DWPP</sub>  |                            | Full         | -               | -           | 100             | ns    |

| SCL_S to SCL On Resistance                            |                    |                            | Full         | -               | -           | 75              | Ω     |

| Delay From SCL_S to SCL                               | ts                 |                            | Full         | -               | -           | 60              | ns    |

| I <sup>2</sup> C                                      |                    |                            |              |                 |             |                 |       |

| SCL Clock Frequency                                   | F <sub>SCL</sub>   |                            | Full         | 0               | -           | 400             | kHz   |

| I <sup>2</sup> C Clock High Time                      | tsch               |                            | Full         | 0.6             | -           | -               | μs    |

| I <sup>2</sup> C Clock Low Time                       | t <sub>SCL</sub>   |                            | Full         | 1.3             | -           | -               | μs    |

| I <sup>2</sup> C Spike Rejection Filter Pulse Width   | t <sub>DSP</sub>   |                            | Full         | 0               | -           | 50              | ns    |

| I <sup>2</sup> C Data Set-up Time                     | t <sub>SDS</sub>   |                            | Full         | 100             | -           | -               | ns    |

| I <sup>2</sup> C Data Hold Time                       | t <sub>SDH</sub>   |                            | Full         | 0               | -           | 900             | ns    |

| I <sup>2</sup> C SDA, SCL Input Rise Time             | t <sub>ICR</sub>   | Dependent on Load (Note 6) | Full         | -               | 20 + 0.1*Cb | 1000            | ns    |

| I <sup>2</sup> C SDA, SCL Input Fall Time             | t <sub>ICF</sub>   | (Note 6)                   | Full         | -               | 20 + 0.1*Cb | 300             | ns    |

| I <sup>2</sup> C Bus Free Time Between Stop and Start | t <sub>BUF</sub>   |                            | Full         | 1.3             | -           | -               | μs    |

| I <sup>2</sup> C Repeated Start Condition<br>Set-up   | t <sub>STS</sub>   |                            | Full         | 0.6             | -           | -               | μs    |

| I <sup>2</sup> C Repeated Start Condition<br>Hold     | t <sub>STH</sub>   |                            | Full         | 0.6             | -           | -               | μs    |

| I <sup>2</sup> C Stop Condition Set-up                | t <sub>SPS</sub>   |                            | Full         | 0.6             | -           | -               | μs    |

| I <sup>2</sup> C Bus Capacitive Load                  | Cb                 |                            | Full         | -               | -           | 400             | pF    |

| Capacitance on SDA                                    | C <sub>SDA</sub>   |                            | Full         | -               | -           | 10              | pF    |

| Capacitance on SCL, SCL_S                             | CS                 | WPn = 0                    | Full         | -               | -           | 10              | pF    |

|                                                       |                    | WPn = 1                    |              | -               | -           | 22              | pF    |

| Write Cycle Time                                      | t <sub>W</sub>     |                            | Full         | -               | -           | 100             | ms    |

#### NOTES:

- 2. Tested at AVDD = 18V.

- 3. Simulated and Determined via Design and NOT Directly Tested.

- 4. Simulated Maximum Current Draw when Programming EEPROM is 23mA, should be considered when designing Power Supply.

- 5. A Typical Current of  $20\mu$ A is Calculated using the AVDD = 10V and  $R_{SET} = 24.9k\Omega$ . The maximum suggested SET Current should be  $120\mu$ A.

- 6. Simulated and Designed According to I<sup>2</sup>C Specifications.

- 7. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

#### Truth Tables

**TABLE 1. DVR WRITE PROTECTION TRUTH TABLE**

|                                           | INPUT                  |                          |             | OUTPUT                          |                                 |

|-------------------------------------------|------------------------|--------------------------|-------------|---------------------------------|---------------------------------|

| WPn                                       | SCL_S                  | SCL                      | WPp         | REGISTER                        | EEPROM                          |

| LOW                                       | UNUSED                 | INPUT                    | HIGH        | Write Protect                   | Write Protect                   |

| HIGH                                      | CONNECTED TO<br>SCL    | CONNECTED TO SCL_S       | LOW         | Writeable                       | Writeable                       |

| HIGH to LOW                               | DISCONECTS<br>FROM SCL | DISCONECTS<br>FROM SCL_S | LOW to HIGH | EEPROM is Read into<br>Register | EEPROM is Read into<br>Register |

| FLOAT<br>(Pull-Down Resistor<br>Included) | UNUSED                 | INPUT                    | HIGH        | Write Protect                   | Write Protect                   |

NOTE: When the device is not write-protected SCL\_S and SCL signals should not be driven at the same time. When SCL\_S signal is "Unused" should be left floating.

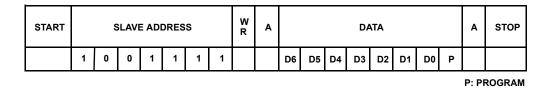

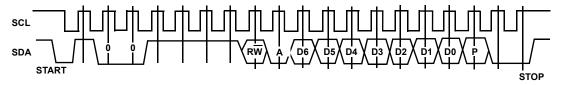

### I<sup>2</sup>C Bus Format

## Application Information

This device provides the ability to reduce the flicker of an LCD panel by adjustment of the VCOM voltage during production test and alignment. A 128-step resolution is provided under digital control, which adjusts the sink current of the output. The output is connected to an external voltage divider, so that the device will have the capability to reduce the voltage on the output by increasing the output sink current.

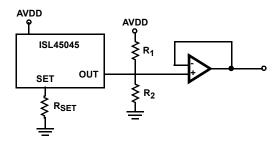

FIGURE 1. OUTPUT CONNECTION CIRCUIT EXAMPLE

When Read Operation, don't care P. P = 1: Register Writing P = 0: EEPROM Writing (Program)

The adjustment of the output is provided by the two-wire I<sup>2</sup>C serial interface.

#### Adjustable Sink Current Output

The device provides an output sink current which lowers the voltage on the external voltage divider. Equations 1 and 2 control the output. See Figure 1.

$$I_{OUT} = \frac{Setting}{128} X \frac{AVDD}{20(R_{SET})}$$

(EQ. 1)

$$V_{OUT} = \left(\frac{R2}{R1 + R2}\right) VAVDD \left(1 - \frac{Setting}{128} X \frac{R1}{20(R_{SET})}\right) \qquad \text{(EQ. 2)}$$

Note: Where (Setting) is indicated, must be an integer between 1 and 128.

## Ramp-up of the VDD Power Supply

It is required that the ramp-up from 10% VDD to 90% VDD achieved in less than or equal to 10ms to assure that the EEPROM and Power-on-reset circuits are synchronized and the correct value is read from the EEPROM Memory.

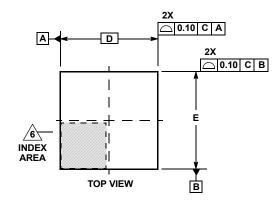

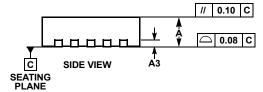

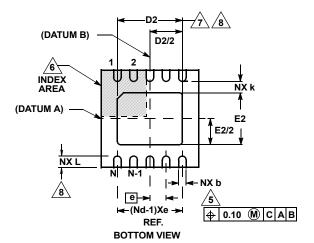

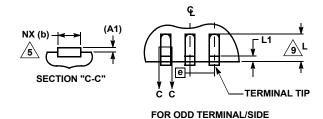

### Thin Dual Flat No-Lead Plastic Package (TDFN)

L10.3x3A

#### 10 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE

|        | ı    |          |      |       |

|--------|------|----------|------|-------|

| SYMBOL | MIN  | NOMINAL  | MAX  | NOTES |

| А      | 0.70 | 0.75     | 0.80 | -     |

| A1     | -    | -        | 0.05 | -     |

| A3     |      | 0.20 REF |      | -     |

| b      | 0.20 | 0.25     | 0.30 | 5, 8  |

| D      | 2.95 | 3.0      | 3.05 | -     |

| D2     | 2.25 | 2.30     | 2.35 | 7, 8  |

| E      | 2.95 | 3.0      | 3.05 | -     |

| E2     | 1.45 | 1.50     | 1.55 | 7, 8  |

| е      |      | -        |      |       |

| k      | 0.25 | -        | -    | -     |

| L      | 0.25 | 0.30     | 0.35 | 8     |

| N      |      | 2        |      |       |

| Nd     |      | 3        |      |       |

Rev. 3 3/06

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd refers to the number of terminals on D.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- Compliant to JEDEC MO-229-WEED-3 except for D2 dimensions.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com