# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **inter<sub>sil</sub>**

Data Sheet

#### December 3, 2015

## FN9104.5

## Dual Power Distribution Controller

The ISL6161 is a HOT SWAP dual supply power distribution controller that can be used in PCI-Express applications.

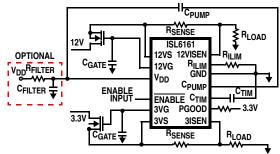

Two external N-Channel MOSFETs are driven to distribute and control power while providing load fault isolation. At turn-on, the gate of each external N-Channel MOSFET is charged with a 10 $\mu$ A current source. Capacitors on each gate (see the "Typical Application Diagram" on page 1), create a programmable ramp (soft turn-on) to control in-rush currents. A built-in charge pump supplies the gate drive for the 12V supply N-Channel MOSFET switch.

Overcurrent protection is facilitated by two external current sense resistors and FETs. When the current through either resistor exceeds the user programmed value, the controller enters the current regulation mode. The time-out capacitor,  $C_{TIM}$ , starts charging as the controller enters the time-out period. Once  $C_{TIM}$  charges to a 2V threshold, both the N-Channel MOSFETs are latched off. In the event of a hard and fast fault of at least 3x the programmed current limit level, the N-Channel MOSFET gates are pulled low immediately before entering the time-out period. The controller is reset by a rising edge on the ENABLE pin.

The ISL6161 constantly monitors both output voltages and reports either one being low on the PGOOD output as a low. The 12V PGOOD Vth is ~10.8V and the 3.3V Vth is ~2.8V nominally.

## Typical Application Diagram

## Features

- HOT SWAP Dual Power Distribution and Control for +12V and +3.3V

- Provides Fault Isolation

- Programmable Current Regulation Level

- Programmable Time-Out

- Charge Pump Allows the Use of N-Channel MOSFETs

- Power-Good and Overcurrent Latch Indicators

- Adjustable Turn-On Ramp

- Protection During Turn-On

- Two Levels of Current Limit Detection Provide Fast Response to Varying Fault Conditions

- 1µs Response Time to Dead Short

- 3µs Response Time to 200% Current Overshoot

- Pb-Free Available (RoHS compliant)

## Applications

- PCI-Express Applications

- Power Distribution and Control

- Hot Plug, Hot Swap Components

## **Ordering Information**

| PART<br>NUMBER                                                                                                  | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE                 | PKG.<br>DWG. # |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------|------------------------|-------------------------|----------------|--|

| ISL6161IBZA*<br>(Note)<br>No longer<br>available or<br>supported,<br>recommended<br>replacement:<br>ISL6161CBZA | ISL6161 IBZ     | -40 to +85             | 14 Ld SOIC<br>(Pb-free) | M14.15         |  |

| ISL6161CBZA*<br>(Note)                                                                                          | 6161CBZ         | 0 to +70               | 14 Ld SOIC<br>(Pb-free) | M14.15         |  |

| *Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel                                   |                 |                        |                         |                |  |

\*Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020

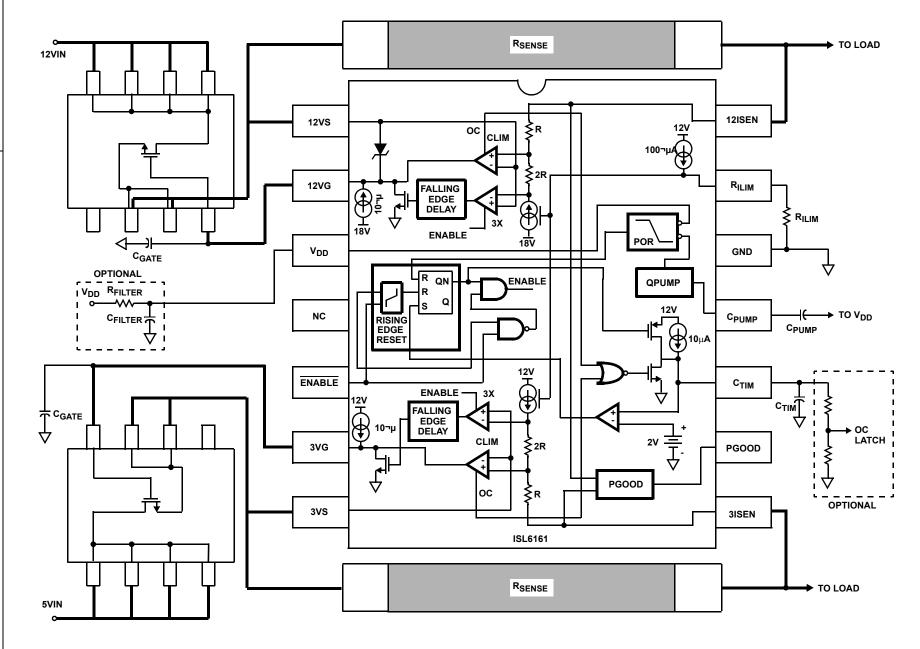

Simplified Schematic

2 intersil

ISL6161

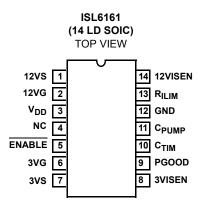

## Pinout

## **Pin Descriptions**

| PIN NUMBER                                                                                                               | SYMBOL            | FUNCTION                                                                                                                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                        | 12VS 12V Source   |                                                                                                                                                                                                                                                          | Connect to source of associated external N-Channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2                                                                                                                        |                   |                                                                                                                                                                                                                                                          | Connect to the gate of associated N-Channel MOSFET switch. A capacitor from this node to ground sets the turn-on ramp. At turn-on this capacitor will be charged to ~17.4V by a 10 $\mu$ A current source.                                                                                                                                                                                                                                                                                            |

| 3                                                                                                                        | V <sub>DD</sub>   | Chip Supply                                                                                                                                                                                                                                              | Connect to 12V supply. This can be either connected directly to the +12V rail supplying the load voltage or to a dedicated $V_{DD}$ +12V supply. If the former is chosen, special attention to $V_{DD}$ decoupling must be paid to prevent sagging as heavy loads are switched on.                                                                                                                                                                                                                    |

| 4                                                                                                                        | NC                | Not Connected                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5                                                                                                                        | ENABLE            | Enable/Reset                                                                                                                                                                                                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6                                                                                                                        | 3VG               | 3V Gate                                                                                                                                                                                                                                                  | Connect to the gate of the external 3V N-Channel MOSFET. A capacitor from this node to ground sets the turn-on ramp. At turn-on, this capacitor will be charged to ~11.4V by a $10\mu$ A current source.                                                                                                                                                                                                                                                                                              |

| 7                                                                                                                        | 3VS               | 3 Source                                                                                                                                                                                                                                                 | Connect to the source side of 3V external N-Channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8                                                                                                                        | 3VISEN            | 3V Current Sense                                                                                                                                                                                                                                         | Connect to the load side of the 3V sense resistor to measure the voltage drop across this resistor between 3VS and 3VISEN pins.                                                                                                                                                                                                                                                                                                                                                                       |

| 9                                                                                                                        | PGOOD             | Power-Good indicator                                                                                                                                                                                                                                     | Indicates that all output voltages are within specification. PGOOD is driven by an open drain N-Channel MOSFET. It is pulled low when any output is not within specification.                                                                                                                                                                                                                                                                                                                         |

| 10 C <sub>TIM</sub> Current Limit Timing Connect a capacitor from this pin to ground. This capacitor controls the time b |                   | Connect a capacitor from this pin to ground. This capacitor controls the time between the onset of current limit and chip shutdown (current limit time-out). The duration of current limit time-out (in seconds) = $200k\Omega \times C_{TIM}$ (Farads). |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11                                                                                                                       | C <sub>PUMP</sub> | Charge Pump<br>Capacitor                                                                                                                                                                                                                                 | Connect a 0.1 $\mu F$ capacitor between this pin and $V_{DD}$ (pin 3). Provides charge storage for 12VG drive.                                                                                                                                                                                                                                                                                                                                                                                        |

| 12                                                                                                                       | GND               | Chip Ground                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13                                                                                                                       | R <sub>ILIM</sub> | Current Limit Set<br>Resistor                                                                                                                                                                                                                            | A resistor connected between this pin and ground determines the current level at which current limit is activated. This current is determined by the ratio of the R <sub>ILIM</sub> resistor to the sense resistor (R <sub>SENSE</sub> ). The current at current limit onset is equal to $10\mu A \times (R_{ILIM}/R_{SENSE})$ . The ISL6161 is limited to a $10k\Omega$ min. value (OC Vth = $100mV$ ) resistor whereas the ISL6161 can accommodate a $5k\Omega$ resistor for a lower OC Vth (50mV). |

| 14                                                                                                                       | 12VISEN           | 12V Current Sense                                                                                                                                                                                                                                        | Connect to the load side of sense resistor to measure the voltage drop across this resistor.                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Absolute Maximum Ratings T<sub>A</sub> = +25°C

| V <sub>DD</sub> 0.3V to +16V          |

|---------------------------------------|

| 12VG, C <sub>PUMP</sub> 0.3V to 21V   |

| 12VISEN, 12VS                         |

| 3VISEN, 3VS                           |

| PGOOD, R <sub>ILIM</sub> 0.3V to 7.5V |

| ENABLE, C <sub>TIM</sub> , 3VG        |

| ESD Classification                    |

#### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range |               |  |

|--------------------------------------|---------------|--|

| Temperature Range (T <sub>A</sub> )  |               |  |

| ISL6161IB                            | 40°C to +85°C |  |

| ISL6161CB                            | 0°C to +70°C  |  |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| SOIC Package                                     | 67                     |

| Maximum Junction Temperature (Plastic Package)   |                        |

| Maximum Storage Temperature Range65°             | 'C to +150°C           |

| Pb-Free Reflow Profilese                         | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

2. All voltages are relative to GND, unless otherwise specified.

| Electrical Specifications | $V_{DD}$ = 12V, $C_{VG}$ = 0.01µF, $C_{TIM}$ = 0.1µF, $R_{SENSE}$ = 0.1Ω, $C_{BULK}$ = 220µF, ESR = 0.5Ω, $T_A$ = $T_J$ = -40°C to +85°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | production tested.                                                                                                                                                                                                                                                                                                               |

| PARAMETER                                                                   | SYMBOL                 | TEST CONDITIONS                                                               | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------|------|------|------|-------|

| 12V CONTROL SECTION                                                         |                        |                                                                               |      |      |      |       |

| Current Limit Threshold Voltage                                             | V <sub>IL12V</sub>     | R <sub>ILIM</sub> = 10kΩ                                                      | 92   | 100  | 108  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | R <sub>ILIM</sub> = 5kΩ                                                       | 47   | 53   | 59   | mV    |

| 3x Current Limit Threshold Voltage                                          | 3 x V <sub>IL12V</sub> | R <sub>ILIM</sub> = 10kΩ                                                      | 250  | 300  | 350  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | $R_{ILIM} = 5k\Omega$                                                         | 100  | 165  | 210  | mV    |

| ±20% Current Limit Response Time<br>(Current within 20% of Regulated Value) | 20%iLrt                | 200% Current Overload, $R_{ILIM}$ = 10k $\Omega$ , $R_{SHORT}$ = 6.0 $\Omega$ | -    | 2    | -    | μs    |

| ±10% Current Limit Response Time<br>(Current within 10% of Regulated Value) | 10%iLrt                | 200% Current Overload, $R_{ILIM}$ = 10k $\Omega$ , $R_{SHORT}$ = 6.0 $\Omega$ | -    | 4    | -    | μs    |

| ±1% Current Limit Response Time<br>(Current within 1% of Regulated Value)   | 1%iLrt                 | 200% Current Overload, $R_{ILIM}$ = 10k $\Omega$ , $R_{SHORT}$ = 6.0 $\Omega$ | -    | 10   | -    | μs    |

| Response Time to Dead Short                                                 | RT <sub>SHORT</sub>    | C <sub>12VG</sub> = 0.01µF                                                    | -    | 500  | -    | ns    |

| Gate Turn-On Time                                                           | t <sub>ON12V</sub>     | C <sub>12VG</sub> = 0.01µF                                                    | -    | 12   | -    | ms    |

| Gate Turn-On Current                                                        | I <sub>ON12V</sub>     | C <sub>12VG</sub> = 0.01µF                                                    | 8    | 10   | 12   | μA    |

| 3x Gate Discharge Current                                                   | 3Xdisl                 | 12VG = 18V                                                                    | -    | 0.75 | -    | А     |

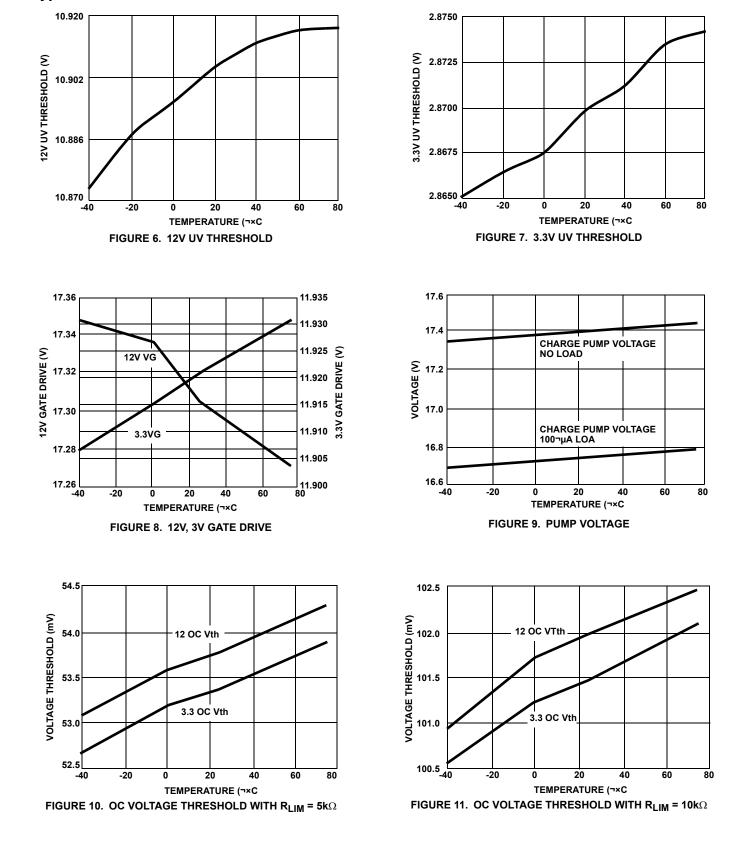

| 12V Undervoltage Threshold                                                  | 12V <sub>VUV</sub>     |                                                                               | 10.5 | 10.8 | 11.0 | V     |

| Charge Pumped 12VG Voltage                                                  | V12VG                  | C <sub>PUMP</sub> = 0.1µF                                                     | 16.8 | 17.3 | 17.9 | V     |

| 3.3V CONTROL SECTION                                                        |                        |                                                                               |      |      |      |       |

| Current Limit Threshold Voltage                                             | V <sub>IL3V</sub>      | R <sub>ILIM</sub> = 10kΩ                                                      | 92   | 100  | 108  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | $R_{ILIM} = 5k\Omega$                                                         | 47   | 53   | 59   | mV    |

| 3x Current Limit Threshold Voltage                                          | 3 x V <sub>IL3V</sub>  | R <sub>ILIM</sub> = 10kΩ                                                      | 250  | 300  | 350  | mV    |

| (Voltage Across Sense Resistor)                                             |                        | $R_{ILIM} = 5k\Omega$                                                         | 100  | 155  | 210  | mV    |

| ±20% Current Limit Response Time<br>(Current within 20% of Regulated Value) |                        | 200% Current Overload, $R_{ILIM}$ = 10k $\Omega$ , $R_{SHORT}$ = 2.5 $\Omega$ | -    | 2    | -    | μs    |

| ±10% Current Limit Response Time<br>(Current within 10% of Regulated Value) |                        | 200% Current Overload, $R_{ILIM}$ = 10k $\Omega$ , $R_{SHORT}$ = 2.5 $\Omega$ | -    | 4    | -    | μs    |

#### **Electrical Specifications**

$V_{DD}$  = 12V,  $C_{VG}$  = 0.01µF,  $C_{TIM}$  = 0.1µF,  $R_{SENSE}$  = 0.1Ω,  $C_{BULK}$  = 220µF, ESR = 0.5Ω,  $T_A$  =  $T_J$  = -40°C to +85°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued)

| PARAMETER                                                                 | SYMBOL                 | TEST CONDITIONS                                                               | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------|------|------|------|-------|

| ±1% Current Limit Response Time<br>(Current within 1% of Regulated Value) |                        | 200% Current Overload, $R_{ILIM}$ = 10k $\Omega$ , $R_{SHORT}$ = 2.5 $\Omega$ | -    | 10   | -    | μs    |

| Response Time To Dead Short                                               | RT <sub>SHORT</sub>    | C <sub>VG</sub> = 0.01µF                                                      | -    | 500  |      | ns    |

| Gate Turn-On Time                                                         | t <sub>ON3V</sub>      | C <sub>VG</sub> = 0.01µF                                                      | -    | 5    | -    | ms    |

| Gate Turn-On Current                                                      | I <sub>ON3V</sub>      | C <sub>VG</sub> = 0.01µF                                                      | 8    | 10   | 12   | μA    |

| 3x Gate Discharge Current                                                 | 3xdisl                 | $C_{VG}$ = 0.01µF, ENABLE = Low                                               |      | 0.75 | -    | А     |

| 3.3V Undervoltage Threshold                                               | 3.3V <sub>VUV</sub>    |                                                                               | 2.7  | 2.85 | 3.0  | V     |

| 3.3VG High Voltage                                                        | 3VG                    |                                                                               | 11.2 | 11.9 | -    | V     |

| SUPPLY CURRENT AND IO SPECIFICAT                                          | TIONS                  |                                                                               |      |      |      |       |

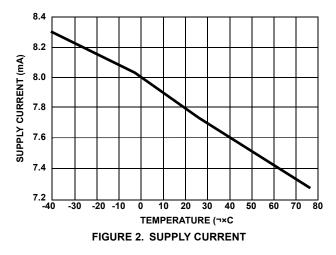

| V <sub>DD</sub> Supply Current                                            | I <sub>VDD</sub>       |                                                                               | 4    | 8    | 10   | mA    |

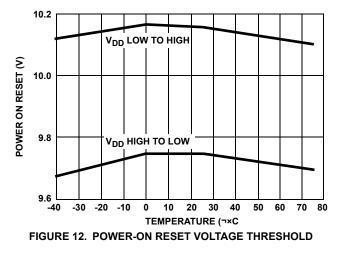

| V <sub>DD</sub> POR Rising Threshold                                      |                        |                                                                               | 9.5  | 10.0 | 10.7 | V     |

| V <sub>DD</sub> POR Falling Threshold                                     |                        |                                                                               | 9.0  | 9.4  | 9.8  | V     |

| Current Limit Time-Out                                                    | t <sub>ILIM</sub>      | C <sub>TIM</sub> = 0.1µF                                                      | -    | 20   | -    | ms    |

| ENABLE Pull-up Voltage                                                    | PWRN_V                 | ENABLE pin open                                                               | 1.8  | 2.4  | 3.2  | V     |

| ENABLE Rising Threshold                                                   | PWR_Vth                |                                                                               | 1.1  | 1.5  | 2    | V     |

| ENABLE Hysteresis                                                         | PWR_hys                |                                                                               | 0.1  | 0.2  | 0.3  | V     |

| ENABLE Pull-Up Current                                                    | PWRN_I                 |                                                                               | 60   | 80   | 100  | μA    |

| Current Limit Time-Out Threshold (C <sub>TIM</sub> )                      | C <sub>TIM</sub> _Vth  |                                                                               | 1.8  | 2    | 2.2  | V     |

| C <sub>TIM</sub> Charging Current                                         | C <sub>TIM</sub> _I    |                                                                               | 8    | 10   | 12   | μA    |

| C <sub>TIM</sub> Discharge Current                                        | C <sub>TIM</sub> _disI |                                                                               | 1.7  | 2.6  | 3.5  | mA    |

| C <sub>TIM</sub> Pull-Up Current                                          | C <sub>TIM</sub> _disI | V <sub>CTIM</sub> = 8V                                                        | 3.5  | 5    | 6.5  | mA    |

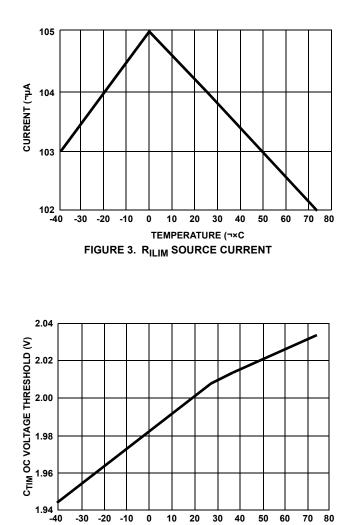

| RILIM Pin Current Source Output                                           | R <sub>ILIM</sub> lo   |                                                                               | 90   | 100  | 110  | μA    |

| Charge Pump Output Current                                                | Qpmp_lo                | C <sub>PUMP</sub> = 0.1μF, C <sub>PUMP</sub> = 16V                            | 320  | 560  | 900  | μA    |

| Charge Pump Output Voltage                                                | Qpmp_Vo                | No load                                                                       | 17.2 | 17.4 | -    | V     |

| Charge Pump Output Voltage - Loaded                                       | Qpmp_VIo               | Load current = 100µA                                                          | 16.2 | 16.7 | -    | V     |

| Charge Pump POR Rising Threshold                                          | Qpmp + Vth             |                                                                               | 15.6 | 16   | 16.5 | V     |

| Charge Pump POR Falling Threshold                                         | Qpmp - Vth             |                                                                               | 15.2 | 15.7 | 16.2 | V     |

## ISL6161 Description and Operation

The ISL6161 is a multi-featured +12V and +3.3V dual power supply distribution controller. Its features include programmable current regulation (CR) limiting and time to latch off.

At turn-on, the gate capacitor of each external N-Channel MOSFET is charged with a  $10\mu$ A current source. These capacitors create a programmable ramp (soft turn-on). A charge pump supplies the gate drive for the 12V supply control FET switch driving that gate to 17V.

The load currents pass through two external current sense resistors. When the voltage across either resistor quickly exceeds the user programmed Current Regulation voltage threshold (CRVth) level, the controller enters current regulation. The CRVth is set by the external resistor value on  $R_{ILIM}$  pin. At

this time, the time-out capacitor,  $C_{TIM}$ , starts charging with a 10µA current source and the controller enters the time-out period. The length of the time-out period is set by the single external capacitor (see Table 2) placed from the  $C_{TIM}$  pin (pin 10) to ground and is characterized by a lowered gate drive voltage to the appropriate external N-Channel MOSFET. Once  $C_{TIM}$  charges to 2V, an internal comparator is tripped resulting in both N-Channel MOSFETs being latched off. If the voltage across the sense resistors rises slowly in response to an OC condition, then the CR mode is entered at ~95% of the programmed CR level. This difference is due to the necessary hysteresis and response time in the CR control circuitry.

Table 1 shows  $R_{SENSE}$  and  $R_{ILIM}$  recommendations and resulting CR level for the PCI-Express add-in card connector sizes specified.

| PCI-EXPRESS<br>ADD-IN CARD<br>CONNECTOR | R <sub>ILIM</sub><br>(kΩ) | 3.3V R <sub>SENSE</sub><br>(mΩ),<br>NOMINAL<br>CR (A) | 12V R <sub>SENSE</sub><br>(mΩ),<br>NOMINAL<br>CR (A) | NOMINAL<br>CRVth<br>(mV) |

|-----------------------------------------|---------------------------|-------------------------------------------------------|------------------------------------------------------|--------------------------|

| X1                                      | 10                        | 30, 3.3                                               | 150, 0.7                                             | 100                      |

|                                         | 4.99                      | 15, 3.5                                               | 90, 0.6                                              | 53                       |

| X4/X8                                   | 10                        | 30, 3.3                                               | 40, 2.5                                              | 100                      |

|                                         | 4.99                      | 15, 3.5                                               | 20, 2.6                                              | 53                       |

| X16                                     | 10                        | 30, 3.3                                               | 16, 6.3                                              | 100                      |

|                                         | 4.99                      | 15, 3.5                                               | 8, 6.6                                               | 53                       |

#### TABLE 1. R<sub>SENSE</sub> AND R<sub>ILIM</sub> RECOMMENDATIONS

NOTE: Nominal CR Vth = R<sub>ILIM</sub> x 10µA.

| TABLE 2.                                                   |     |  |  |  |  |

|------------------------------------------------------------|-----|--|--|--|--|

| C <sub>TIM</sub> CAPACITOR NOMINAL TIME-OUT F<br>(µF) (ms) |     |  |  |  |  |

| 0.022                                                      | 4.4 |  |  |  |  |

| 0.047                                                      | 9.4 |  |  |  |  |

| 0.1                                                        | 20  |  |  |  |  |

NOTE: Nominal time-out period in seconds = C<sub>TIM</sub> x 200kΩ.

The ISL6161 responds to a load short (defined as a current level 3x the OC set point with a fast transition) by immediately driving the relevant N-Channel MOSFET gate to 0V in ~3 $\mu$ s. The gate voltage is then slowly ramped up, soft-starting the N-Channel MOSFET to the programmed current regulation limit level. This is the start of the time-out period if the abnormal load condition still exists. The programmed current regulation level is held until either the OC event passes or the time-out period expires. If the former is the case, then the N-Channel MOSFET is fully enhanced and the C<sub>TIM</sub> charging current is diverted away from the capacitor. If the time-out period expires prior to OC resolution, then both gates are quickly pulled to 0V turning off both N-Channel MOSFETs simultaneously.

Upon any UV condition, the PGOOD signal will pull low when tied high through a resistor to the logic supply. This pin is a fault indicator but not the OC latch-off indicator. For an OC latch-off indication, monitor CTIM, pin 10. This pin will rise rapidly to 12V once the time-out period expires. See "Simplified Schematic" on page 2 for OC latch-off circuit suggestion.

The ISL6161 is reset by a rising edge on the ENABLE pin and is turned on by the ENABLE pin being driven low.

#### ISL6161 Application Considerations

In a non PCI-Express, motor drive application, **Current loop stabilization** is facilitated through a small value resistor in series with the gate timing capacitor. As the ISL6161 drives a highly inductive current load, instability characterized by the gate voltage repeatedly ramping up and down may appear. A simple method to enhance stability is provided by the substitution of a larger value gate resistor. Typically, this situation can be avoided by eliminating long point-to-point wiring to the load.

With the ENABLE internal pull-up, the ISL6161 is well suited for implementation on either side of the connector where a motherboard prebiased condition or a load board staggered connection is present. In either case, the ISL6161 turns on in a soft-start mode protecting the supply rail from sudden current loading.

During the **Time-Out delay period** with the ISL6161 in current limit mode, the V<sub>GS</sub> of the external N-Channel MOSFETs is reduced driving the N-Channel MOSFET switch into a high  $r_{DS(ON)}$  state. Thus, avoid extended time-out periods as the external N-Channel MOSFETs may be damaged or destroyed due to excessive internal power dissipation. Refer to the MOSFET manufacturers data sheet for SOA information.

With the high levels of in-rush current e.g., highly capacitive loads and motor start-up currents, **choosing the current regulation (CR) level** is crucial to provide both protection and still allow for this in-rush current without latching off. Consider this in addition to the time-out delay when choosing MOSFETs for your design.

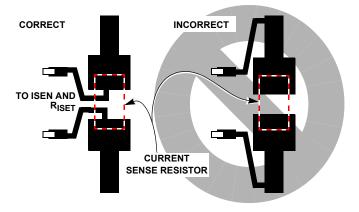

**Physical layout of R<sub>SENSE</sub> resistors** is critical to avoid inadvertently lowering the CR and trip levels. Ideally, trace routing between the R<sub>SENSE</sub> resistors and the ISL6161 should be as direct and as short as possible with zero current in the sense lines.

FIGURE 1. SENSE RESISTOR PCB LAYOUT

Open load detection can be accomplished by monitoring the ISEN pins. Although gated off, the external FET  $\mathsf{I}_{\text{DSS}}$  will cause the ISEN pin to float above ground to some voltage when there is no attached load. If this is not desired, 5k resistors from the xISEN pins to ground will prevent the outputs from floating when the external switch FETs are disabled and the outputs are open.

#### Typical Performance Curves

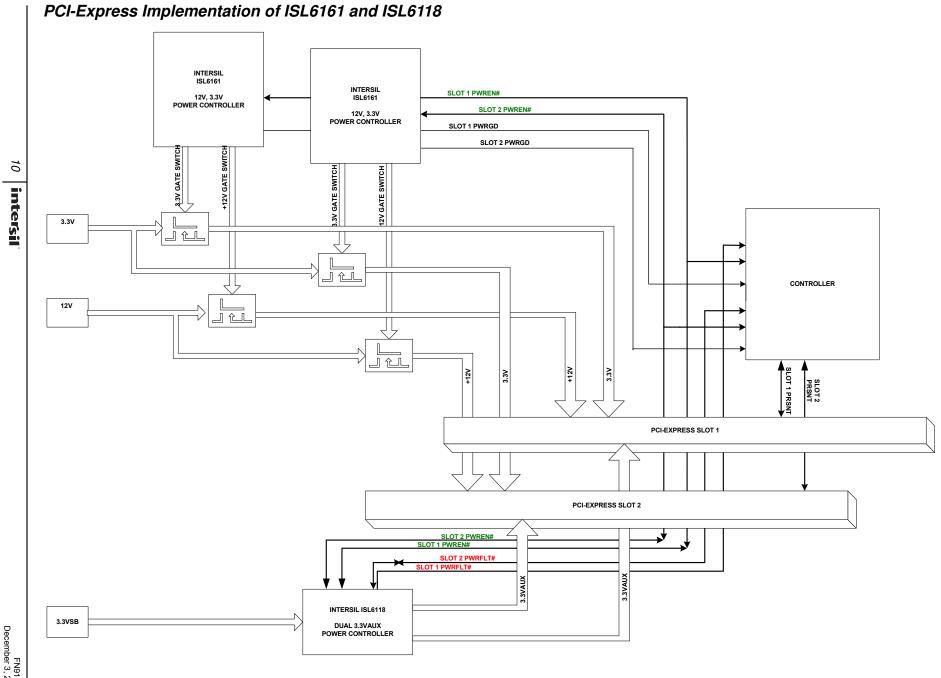

For PCI-Express applications, the ISL6161 and the ISL6118 provide the fundamental hotswap function for the +12V and +3.3V main rails and the +3.3V aux respectively, as shown in the "PCI-Express Implementation of ISL6161 and ISL6118" on page 10.

10.7 C<sub>TIM</sub> CURRENT SOURCE (µA 10.6 10.5 10.4 10.3 └─ -40 -30 -20 -10 10 20 30 40 50 60 70 80 0 TEMPERATURE (¬×C FIGURE 4. CTIM CURRENT SOURCE

FIGURE 5. CTIM OC VOLTAGE THRESHOLD

TEMPERATURE (¬×C

-30 -20 -10 0 10 20 30 40 50 60 70 80

#### Typical Performance Curves (Continued)

Typical Performance Curves (Continued)

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE             | REVISION | CHANGE                                                                                                                                                                                                                                |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 3, 2015 | FN9104.5 | Added Rev History and About Intersil Verbiage.<br>Updated Ordering Information on page 1<br>Updated POD M14.15 to most current version. Rev change is as follows:<br>Added land pattern and moved dimensions from table onto drawing. |

#### About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <u>www.intersil.com</u>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9001 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

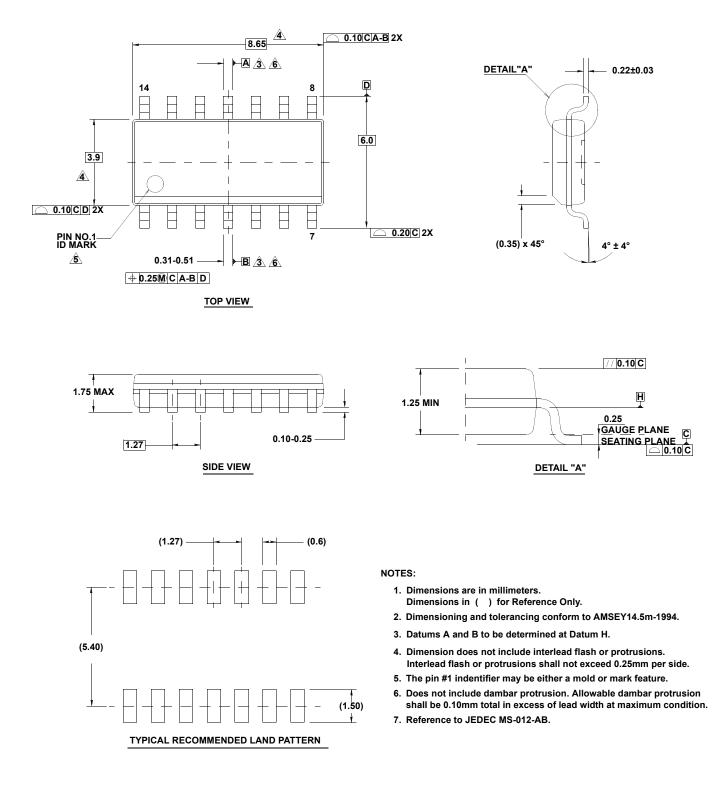

## Package Outline Drawing

#### M14.15

14 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 1, 10/09