Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Data Sheet May 5, 2008 FN9160.4

## Dual Advanced Synchronous Rectified Buck MOSFET Drivers with Pre-POR OVP

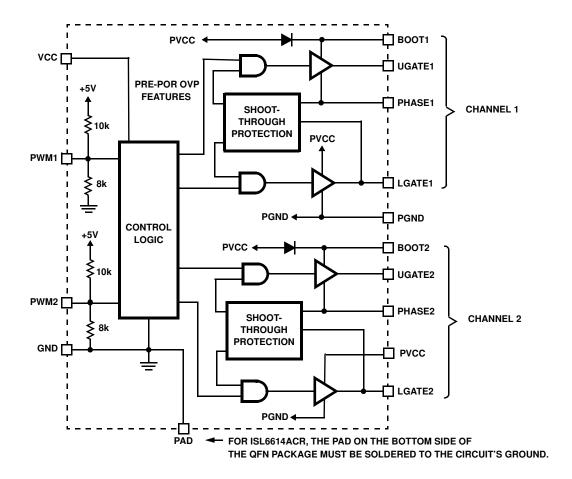

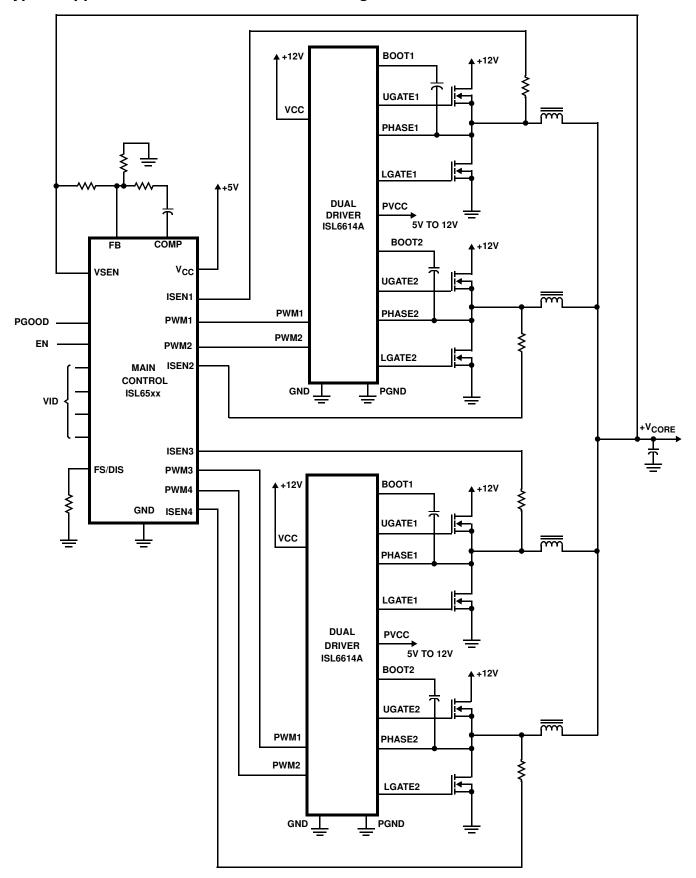

The ISL6614A integrates two ISL6613A MOSFET drivers and is specifically designed to drive two Channel MOSFETs in a synchronous rectified buck converter topology. These drivers combined with HIP63xx or ISL65xx Multi-Phase Buck PWM controllers and N-Channel MOSFETs form complete core voltage regulator solutions for advanced microprocessors.

The ISL6614A drives both the upper and lower gates simultaneously over a range from 5V to 12V. This drive voltage provides the flexibility necessary to optimize applications involving trade-offs between gate charge and conduction losses.

An advanced adaptive zero shoot-through protection is integrated to prevent both the upper and lower MOSFETs from conducting simultaneously and to minimize the dead time. These products add an overvoltage protection feature operational before VCC exceeds its turn-on threshold, at which the PHASE node is connected to the gate of the low side MOSFET (LGATE). The output voltage of the converter is then limited by the threshold of the low side MOSFET, which provides some protection to the microprocessor if the upper MOSFET(s) is shorted during startup.

The ISL6614A also features a three-state PWM input which, working together with Intersil's multi-phase PWM controllers, prevents a negative transient on the output voltage when the output is shut down. This feature eliminates the Schottky diode that is used in some systems for protecting the load from reversed output voltage events.

## **Features**

- · Pin-to-pin Compatible with HIP6602 SOIC Family

- Quad N-Channel MOSFET Drives for Two Synchronous Rectified Bridges

- · Advanced Adaptive Zero Shoot-Through Protection

- Body Diode Detection

- Auto-zero of r<sub>DS(ON)</sub> Conduction Offset Effect

- · Adjustable Gate Voltage (5V to 12V) for Optimal Efficiency

- · Internal Bootstrap Schottky Diode

- · Bootstrap Capacitor Overcharging Prevention

- · Supports High Switching Frequency (up to 1MHz)

- 3A Sinking Current Capability

- Fast Rise/Fall Times and Low Propagation Delays

- · Three-State PWM Input for Output Stage Shutdown

- Three-State PWM Input Hysteresis for Applications With Power Sequencing Requirement

- · Pre-POR Overvoltage Protection

- VCC Undervoltage Protection

- Expandable Bottom Copper Pad for Enhanced Heat Sinking

- · QFN Package:

- Compliant to JEDEC PUB95 MO-220 QFN Quad Flat No Leads - Package Outline

- Near Chip Scale Package Footprint, which Improves PCB Efficiency and has a Thinner Profile

- Pb-Free Plus Anneal Available (RoHS Compliant)

## **Applications**

- · Core Regulators for Intel® and AMD® Microprocessors

- High Current DC/DC Converters

- High Frequency and High Efficiency VRM and VRD

#### Related Literature

- Technical Brief TB363 "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

- Technical Brief 400 and 417 for Power Train Design, Layout Guidelines, and Feedback Compensation Design

# **Ordering Information**

| PART NUMBER             | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE                    | PKG.<br>DWG.# |

|-------------------------|-----------------|---------------------|----------------------------|---------------|

| ISL6614ACB*             | 6614ACB         | 0 to +85            | 14 Ld SOIC                 | M14.15        |

| ISL6614ACBZ*<br>(Note)  | 6614ACBZ        | 0 to +85            | 14 Ld SOIC<br>(Pb-free)    | M14.15        |

| ISL6614ACBZA*<br>(Note) | 6614ACBZ        | 0 to +85            | 14 Ld SOIC<br>(Pb-free)    | M14.15        |

| ISL6614ACR*             | 66 14ACR        | 0 to +85            | 16 Ld 4x4 QFN              | L16.4x4       |

| ISL6614ACRZ*<br>(Note)  | 66 14ACRZ       | 0 to +85            | 16 Ld 4x4 QFN<br>(Pb-free) | L16.4x4       |

| ISL6614AIB*             | 6614AIB         | -40 to +85          | 14 Ld SOIC                 | M14.15        |

| ISL6614AIBZ*<br>(Note)  | 6614AIBZ        | -40 to +85          | 14 Ld SOIC<br>(Pb-free)    | M14.15        |

| ISL6614AIR*             | 66 14AIR        | -40 to +85          | 16 Ld 4x4 QFN              | L16.4x4       |

| ISL6614AIRZ*<br>(Note)  | 66 14AIRZ       | -40 to +85          | 16 Ld 4x4 QFN<br>(Pb-free) | L16.4x4       |

<sup>\*</sup>Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

2

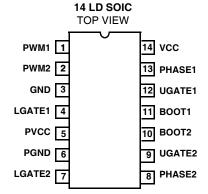

## **Pinouts**

ISL6614ACB, ISL6614ACBZ, ISL6614ACBZA, ISL6614AIB, ISL6614AIBZ

ISL6614ACR, ISL6614ACRZ, ISL6614AIR, ISL6614AIRZ 16 LD 4X4 QFN

TOP VIEW

| Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW | Top VIEW |

FN9160.4 May 5, 2008

# Block Diagram

Typical Application - 4 Channel Converter Using ISL65xx and ISL6614A Gate Drivers

## **Absolute Maximum Ratings**

| Supply Voltage (VCC)                                                            |

|---------------------------------------------------------------------------------|

| Supply Voltage (PVCC)                                                           |

| BOOT Voltage (V <sub>BOOT-GND</sub> )                                           |

| Input Voltage (V <sub>PWM</sub> )                                               |

| UGATE V <sub>PHASE</sub> - 0.3V <sub>DC</sub> to V <sub>BOOT</sub> + 0.3V       |

| V <sub>PHASE</sub> - 3.5V (<100ns Pulse Width, 2μJ) to V <sub>BOOT</sub> + 0.3V |

| LGATE                                                                           |

| GND - 5V (<100ns Pulse Width, 2µJ) to VPVCC + 0.3V                              |

| PHASE GND - 0.3V <sub>DC</sub> to 15V <sub>DC</sub>                             |

| GND - 8V (<400ns, 20µJ) to 30V (<200ns, V <sub>BOOT-GND</sub> <36V)             |

| ESD Rating                                                                      |

| Human Body Model Class I JEDEC STD                                              |

## **Thermal Information**

| SOIC Package (Note 1)                                                                                                                       | Thermal Resistance (Typical)            | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|------------------------|

| Maximum Junction Temperature (Plastic Package) +150°C Maximum Storage Temperature Range65°C to +150°C Pb-free reflow profile see link below | SOIC Package (Note 1)                   | 90                   | N/A                    |

| Maximum Storage Temperature Range65°C to +150°C Pb-free reflow profile                                                                      | QFN Package (Notes 2, 3)                | 48                   | 8.5                    |

| Pb-free reflow profile see link below                                                                                                       | Maximum Junction Temperature (Plastic P | ackage)              | +150°C                 |

| ·                                                                                                                                           | Maximum Storage Temperature Range       | 65°                  | °C to +150°C           |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp                                                                                            | Pb-free reflow profile                  |                      | ee link below          |

|                                                                                                                                             | http://www.intersil.com/pbfree/Pb-FreeR | leflow.asp           |                        |

## **Recommended Operating Conditions**

| Ambient Temperature Range              | 40°C to +85°C  |

|----------------------------------------|----------------|

| Maximum Operating Junction Temperature | +125°C         |

| Supply Voltage, VCC                    | 12V ±10%       |

| Supply Voltage Range, PVCC             | 5V to 12V ±10% |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

- 2. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 3. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

## **Electrical Specifications** Recommended Operating Conditions, Unless Otherwise Noted.

| PARAMETER                                | SYMBOL            | TEST CONDITIONS                                    | MIN  | TYP  | MAX   | UNITS |  |  |  |

|------------------------------------------|-------------------|----------------------------------------------------|------|------|-------|-------|--|--|--|

| VCC SUPPLY CURRENT                       |                   |                                                    |      |      |       |       |  |  |  |

| Bias Supply Current                      | I <sub>VCC</sub>  | f <sub>PWM</sub> = 300kHz, V <sub>PVCC</sub> = 12V | -    | 7.1  | -     | mA    |  |  |  |

| Gate Drive Bias Current                  | I <sub>PVCC</sub> | f <sub>PWM</sub> = 300kHz, V <sub>PVCC</sub> = 12V | -    | 9.7  | -     | mA    |  |  |  |

| POWER-ON RESET AND ENABLE                |                   |                                                    | II.  |      |       | II.   |  |  |  |

| VCC Rising Threshold                     |                   | 0°C to +85°C                                       | 9.35 | 9.80 | 10.05 | V     |  |  |  |

|                                          |                   | -40°C to +85°C                                     | 8.35 | -    | 10.05 | V     |  |  |  |

| VCC Falling Threshold                    |                   | 0°C to +85°C                                       | 7.35 | 7.60 | 8.00  | V     |  |  |  |

|                                          |                   | -40°C to +85°C                                     | 6.35 | -    | 8.00  | V     |  |  |  |

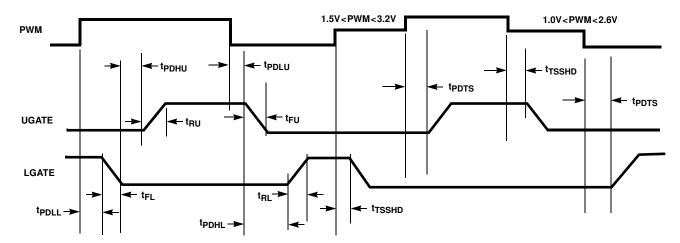

| PWM INPUT (See "TIMING DIAGRAM" on pa    | nge 8)            |                                                    |      | -    |       |       |  |  |  |

| Input Current                            | I <sub>PWM</sub>  | V <sub>PWM</sub> = 5V                              | -    | 500  | -     | μΑ    |  |  |  |

|                                          |                   | V <sub>PWM</sub> = 0V                              | -    | -460 | -     | μΑ    |  |  |  |

| PWM Rising Threshold                     |                   | V <sub>CC</sub> = 12V                              | -    | 3.00 | -     | V     |  |  |  |

| PWM Falling Threshold                    |                   | V <sub>CC</sub> = 12V                              | -    | 2.00 | -     | V     |  |  |  |

| Typical Three-State Shutdown Window      |                   | V <sub>CC</sub> = 12V                              | 1.80 | -    | 2.40  | V     |  |  |  |

| Three-State Lower Gate Falling Threshold |                   | V <sub>CC</sub> = 12V                              | -    | 1.50 | -     | V     |  |  |  |

| Three-State Lower Gate Rising Threshold  |                   | V <sub>CC</sub> = 12V                              | -    | 1.00 | -     | V     |  |  |  |

| Three-State Upper Gate Rising Threshold  |                   | V <sub>CC</sub> = 12V                              | -    | 3.20 | -     | V     |  |  |  |

| Three-State Upper Gate Falling Threshold |                   | V <sub>CC</sub> = 12V                              | -    | 2.60 | -     | V     |  |  |  |

| Shutdown Hold-off Time                   | tTSSHD            |                                                    | -    | 245  | -     | ns    |  |  |  |

| UGATE Rise Time                          | t <sub>RU</sub>   | V <sub>PVCC</sub> = 12V, 3nF Load, 10% to 90%      | -    | 26   | -     | ns    |  |  |  |

| LGATE Rise Time                          | t <sub>RL</sub>   | V <sub>PVCC</sub> = 12V, 3nF Load, 10% to 90%      | -    | 18   | -     | ns    |  |  |  |

| UGATE Fall Time                          | t <sub>FU</sub>   | V <sub>PVCC</sub> = 12V, 3nF Load, 90% to 10%      | -    | 18   | -     | ns    |  |  |  |

intersil FN9160.4 May 5, 2008

# ISL6614A

## **Electrical Specifications** Recommended Operating Conditions, Unless Otherwise Noted. (Continued)

| PARAMETER                                    | SYMBOL                 | TEST CONDITIONS                               | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|------------------------|-----------------------------------------------|------|------|------|-------|

| LGATE Fall Time                              | t <sub>FL</sub>        | V <sub>PVCC</sub> = 12V, 3nF Load, 90% to 10% | -    | 12   | -    | ns    |

| UGATE Turn-On Propagation Delay (Note 4)     | tpDHU                  | V <sub>PVCC</sub> = 12V, 3nF Load, Adaptive   | -    | 10   | -    | ns    |

| LGATE Turn-On Propagation Delay (Note 4)     | t <sub>PDHL</sub>      | V <sub>PVCC</sub> = 12V, 3nF Load, Adaptive   | -    | 10   | -    | ns    |

| UGATE Turn-Off Propagation Delay (Note 4)    | t <sub>PDLU</sub>      | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 10   | -    | ns    |

| LGATE Turn-Off Propagation Delay (Note 4)    | t <sub>PDLL</sub>      | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 10   | -    | ns    |

| LG/UG Three-State Propagation Delay (Note 4) | t <sub>PDTS</sub>      | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 10   | -    | ns    |

| OUTPUT (Note 4)                              |                        |                                               |      |      |      |       |

| Upper Drive Source Current                   | lu_source              | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 1.25 | -    | Α     |

| Upper Drive Source Impedance                 | R <sub>U_SOURCE</sub>  | 150mA Source Current                          | 1.25 | 2.0  | 3.0  | Ω     |

| Upper Drive Sink Current                     | I <sub>U_SINK</sub>    | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 2    | -    | Α     |

| Upper Drive Transition Sink Impedance        | R <sub>U_SINK_TR</sub> | 70ns With Respect To PWM Falling              | -    | 1.3  | 2.2  | Ω     |

| Upper Drive DC Sink Impedance                | R <sub>U_SINK_DC</sub> | 150mA Source Current                          | 0.9  | 1.65 | 3.0  | Ω     |

| Lower Drive Source Current                   | I <sub>L_SOURCE</sub>  | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 2    | -    | Α     |

| Lower Drive Source Impedance                 | R <sub>L_SOURCE</sub>  | 150mA Source Current                          | 0.85 | 1.25 | 2.2  | Ω     |

| Lower Drive Sink Current                     | I <sub>L_SINK</sub>    | V <sub>PVCC</sub> = 12V, 3nF Load             | -    | 3    | -    | Α     |

| Lower Drive Sink Impedance                   | R <sub>L_SINK</sub>    | 150mA Sink Current                            | 0.60 | 0.80 | 1.35 | Ω     |

## NOTE:

<sup>4.</sup> Limits should be considered typical and are not production tested.

# Functional Pin Description

| PKG. PIN<br>NUMBER |            | PIN    |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SOIC               | QFN SYMBOL |        | FUNCTION                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 1                  | 15         | PWM1   | The PWM signal is the control input for the Channel 1 driver. The PWM signal can enter three distinct states during operation, see "Three-State PWM Input" on page 8 for further details. Connect this pin to the PWM output of the controller.                                                            |  |  |  |  |  |

| 2                  | 16         | PWM2   | The PWM signal is the control input for the Channel 2 driver. The PWM signal can enter three distinct states during operation, see "Three-State PWM Input" on page 8 for further details. Connect this pin to the PWM output of the controller.                                                            |  |  |  |  |  |

| 3                  | 1          | GND    | Bias and reference ground. All signals are referenced to this node.                                                                                                                                                                                                                                        |  |  |  |  |  |

| 4                  | 2          | LGATE1 | Lower gate drive output of Channel 1. Connect to gate of the low-side power N-Channel MOSFET.                                                                                                                                                                                                              |  |  |  |  |  |

| 5                  | 3          | PVCC   | This pin supplies power to both the lower and higher gate drives in ISL6614A. Its operating range is +5V to 12V. Place a high quality low ESR ceramic capacitor from this pin to GND.                                                                                                                      |  |  |  |  |  |

| 6                  | 4          | PGND   | It is the power ground return of both low gate drivers.                                                                                                                                                                                                                                                    |  |  |  |  |  |

| -                  | 5, 8       | N/C    | No Connection.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 7                  | 6          | LGATE2 | Lower gate drive output of Channel 2. Connect to gate of the low-side power N-Channel MOSFET.                                                                                                                                                                                                              |  |  |  |  |  |

| 8                  | 7          | PHASE2 | Connect this pin to the SOURCE of the upper MOSFET and the DRAIN of the lower MOSFET in Channel 2. This pin provides a return path for the upper gate drive.                                                                                                                                               |  |  |  |  |  |

| 9                  | 9          | UGATE2 | Upper gate drive output of Channel 2. Connect to gate of high-side power N-Channel MOSFET.                                                                                                                                                                                                                 |  |  |  |  |  |

| 10                 | 10         | BOOT2  | Floating bootstrap supply pin for the upper gate drive of Channel 2. Connect the bootstrap capacitor between this pin and the PHASE2 pin. The bootstrap capacitor provides the charge to turn on the upper MOSFET. See "Internal Bootstrap Device" on page 9 for guidance in choosing the capacitor value. |  |  |  |  |  |

| 11                 | 11         | BOOT1  | Floating bootstrap supply pin for the upper gate drive of Channel 1. Connect the bootstrap capacitor between this pin and the PHASE1 pin. The bootstrap capacitor provides the charge to turn on the upper MOSFET. See "Internal Bootstrap Device" on page 9 for guidance in choosing the capacitor value. |  |  |  |  |  |

| 12                 | 12         | UGATE1 | Upper gate drive output of Channel 1. Connect to gate of high-side power N-Channel MOSFET.                                                                                                                                                                                                                 |  |  |  |  |  |

| 13                 | 13         | PHASE1 | Connect this pin to the SOURCE of the upper MOSFET and the DRAIN of the lower MOSFET in Channel 1. This pin provides a return path for the upper gate drive.                                                                                                                                               |  |  |  |  |  |

| 14                 | 14         | VCC    | Connect this pin to a +12V bias supply. It supplies power to internal analog circuits. Place a high quality low ESR ceramic capacitor from this pin to GND.                                                                                                                                                |  |  |  |  |  |

| -                  | 17         | PAD    | Connect this pad to the power ground plane (GND) via thermally enhanced connection.                                                                                                                                                                                                                        |  |  |  |  |  |

FN9160.4 May 5, 2008

## Description

FIGURE 1. TIMING DIAGRAM

#### Operation

Designed for versatility and speed, the ISL6614A MOSFET driver controls both high-side and low-side N-Channel FETs of two half-bridge power trains from two externally provided PWM signals.

Prior to VCC exceeding its POR level, the Pre-POR overvoltage protection function is activated during initial startup; the upper gate (UGATE) is held low and the lower gate (LGATE), controlled by the Pre-POR overvoltage protection circuits, is connected to the PHASE. Once the VCC voltage surpasses the VCC Rising Threshold (See "Electrical Specifications" table on page 5), the PWM signal takes control of gate transitions. A rising edge on PWM initiates the turn-off of the lower MOSFET (see "TIMING DIAGRAM" on page 8). After a short propagation delay [tPDLL], the lower gate begins to fall. Typical fall times [tFI] are provided in the "Electrical Specifications" table on page 6. Adaptive shoot-through circuitry monitors the PHASE voltage and determines the upper gate delay time [tpDHU]. This prevents both the lower and upper MOSFETs from conducting simultaneously. Once this delay period is complete, the upper gate drive begins to rise [t<sub>RU</sub>] and the upper MOSFET turns on.

A falling transition on PWM results in the turn-off of the upper MOSFET and the turn-on of the lower MOSFET. A short propagation delay [ $t_{PDLU}$ ] is encountered before the upper gate begins to fall [ $t_{FU}$ ]. Again, the adaptive shoot-through circuitry determines the lower gate delay time,  $t_{PDHL}$ . The PHASE voltage and the UGATE voltage are monitored, and the lower gate is allowed to rise after PHASE drops below a level or the voltage of UGATE to PHASE reaches a level depending upon the current direction (See the following section for details). The lower gate then rises [ $t_{RL}$ ], turning on the lower MOSFET.

# Advanced Adaptive Zero Shoot-Through Deadtime Control (Patent Pending)

These drivers incorporate a unique adaptive deadtime control technique to minimize deadtime, resulting in high efficiency from the reduced freewheeling time of the lower MOSFETs' body-diode conduction, and to prevent the upper and lower MOSFETs from conducting simultaneously. This is accomplished by ensuring either rising gate turns on its MOSFET with minimum and sufficient delay after the other has turned off.

During turn-off of the lower MOSFET, the PHASE voltage is monitored until it reaches a -0.2V/+0.8V trip point for a forward/reverse current, at which time the UGATE is released to rise. An auto-zero comparator is used to correct the r<sub>DS(ON)</sub> drop in the phase voltage preventing from false detection of the -0.2V phase level during r<sub>DS(ON)</sub> conduction period. In the case of zero current, the UGATE is released after 35ns delay of the LGATE dropping below 0.5V. During the phase detection, the disturbance of LGATE's falling transition on the PHASE node is blanked out to prevent falsely tripping. Once the PHASE is high, the advanced adaptive shoot-through circuitry monitors the PHASE and UGATE voltages during a PWM falling edge and the subsequent UGATE turn-off. If either the UGATE falls to less than 1.75V above the PHASE or the PHASE falls to less than +0.8V, the LGATE is released to turn on.

#### Three-State PWM Input

A unique feature of these drivers and other Intersil drivers is the addition of a shutdown window to the PWM input. If the PWM signal enters and remains within the shutdown window for a set holdoff time, the driver outputs are disabled and both MOSFET gates are pulled and held low. The shutdown state is removed when the PWM signal moves outside the shutdown window. Otherwise, the PWM rising and falling thresholds outlined in the "Electrical Specifications" table on

**intersil** FN9160.4 May 5, 2008

page 5 determine when the lower and upper gates are enabled.

This feature helps prevent a negative transient on the output voltage when the output is shut down, eliminating the Schottky diode that is used in some systems for protecting the load from reversed output voltage events.

In addition, more than 400mV hysteresis also incorporates into the three-state shutdown window to eliminate PWM input oscillations due to the capacitive load seen by the PWM input through the body diode of the controller's PWM output when the power-up and/or power-down sequence of bias supplies of the driver and PWM controller are required.

## Power-On Reset (POR) Function

During initial startup, the VCC voltage rise is monitored. Once the rising VCC voltage exceeds 9.8V (typically), operation of the driver is enabled and the PWM input signal takes control of the gate drives. If VCC drops below the falling threshold of 7.6V (typically), operation of the driver is disabled.

## Pre-POR Overvoltage Protection

Prior to VCC exceeding its POR level, the upper gate is held low and the lower gate is controlled by the overvoltage protection circuits during initial startup. The PHASE is connected to the gate of the low side MOSFET (LGATE), which provides some protection to the microprocessor if the upper MOSFET(s) is shorted during initial startup. For complete protection, the low side MOSFET should have a gate threshold well below the maximum voltage rating of the load/microprocessor.

When VCC drops below its POR level, both gates pull low and the Pre-POR overvoltage protection circuits are not activated until VCC resets.

#### Internal Bootstrap Device

Both drivers feature an internal bootstrap Schottky diode. Simply adding an external capacitor across the BOOT and PHASE pins completes the bootstrap circuit. The bootstrap function is also designed to prevent the bootstrap capacitor from overcharging due to the large negative swing at the trailing-edge of the PHASE node. This reduces voltage stress on the boot to phase pins.

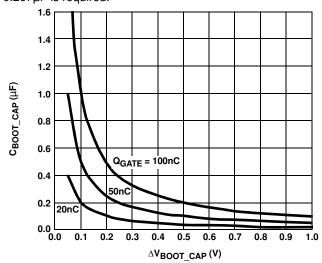

The bootstrap capacitor must have a maximum voltage rating above UVCC + 5V and its capacitance value can be chosen from Equation 1:

$$C_{BOOT\_CAP} \ge \frac{Q_{GATE}}{\Delta V_{BOOT\_CAP}}$$

$$Q_{GATE} = \frac{Q_{G1} \bullet PVCC}{V_{GS1}} \bullet N_{Q1}$$

(EQ. 1)

where  $Q_{G1}$  is the amount of gate charge per upper MOSFET at  $V_{GS1}$  gate-source voltage and  $N_{Q1}$  is the number of control

MOSFETs per channel. The  $\Delta V_{BOOT\_CAP}$  term is defined as the allowable droop in the rail of the upper gate drive.

As an example, suppose two IRLR7821 FETs are chosen as the upper MOSFETs. The gate charge,  $Q_G$ , from the data sheet is 10nC at 4.5V ( $V_{GS}$ ) gate-source voltage. Then the  $Q_{GATE}$  is calculated to be 53nC for PVCC = 12V. We will assume a 200mV droop in drive voltage over the PWM cycle. We find that a bootstrap capacitance of at least  $0.267\mu F$  is required.

FIGURE 2. BOOTSTRAP CAPACITANCE vs BOOT RIPPLE VOLTAGE

#### Gate Drive Voltage Versatility

The ISL6614A provides the user flexibility in choosing the gate drive voltage for efficiency optimization. The ISL6614A ties the upper and lower drive rails together. Simply applying a voltage from 5V up to 12V on PVCC sets both gate drive rail voltages simultaneously. Connecting a SOT-23 package type of dual schottky diodes from the VCC to BOOT1 and BOOT2 can bypass the internal bootstrap devices of both upper gates so that the part can operate as a dual ISL6612 driver, which has a fixed VCC (12V typically) on the upper gate and a programmable lower gate drive voltage.

#### **Power Dissipation**

Package power dissipation is mainly a function of the switching frequency (f<sub>SW</sub>), the output drive impedance, the external gate resistance, and the selected MOSFET's internal gate resistance and total gate charge. Calculating the power dissipation in the driver for a desired application is critical to ensure safe operation. Exceeding the maximum allowable power dissipation level will push the IC beyond the maximum recommended operating junction temperature of +125°C. The maximum allowable IC power dissipation for the SO14 package is approximately 1W at room temperature, while the power dissipation capacity in the QFN packages, with an exposed heat escape pad, is around 2W. See "Layout Considerations" on page 10 for thermal transfer improvement suggestions. When designing the driver into an application, it is recommended that the

calculation in Equation 2 be used to ensure safe operation at the desired frequency for the selected MOSFETs. The total gate drive power losses due to the gate charge of MOSFETs and the driver's internal circuitry and their corresponding average driver current can be estimated with Equations 2 and 3, respectively:

$$P_{Qg\_TOT} = 2 \cdot P_{Qg\_Q1} + 2 \cdot P_{Qg\_Q2} + I_Q \cdot VCC$$

$$P_{Qg\_Q1} = \frac{Q_{G1} \cdot PVCC^2}{V_{GS1}} \cdot f_{SW} \cdot N_{Q1}$$

$$P_{Qg\_Q2} = \frac{Q_{G2} \cdot PVCC^2}{V_{GS2}} \cdot f_{SW} \cdot N_{Q2}$$

$$I_{DR} = \left(\frac{Q_{G1} \bullet N_{Q1}}{V_{GS1}} + \frac{Q_{G2} \bullet N_{Q2}}{V_{GS2}}\right) \bullet f_{SW} \bullet 2 + I_{Q}$$

(EQ. 3)

where the gate charge ( $Q_{G1}$  and  $Q_{G2}$ ) is defined at a particular gate to source voltage ( $V_{GS1}$ and  $V_{GS2}$ ) in the corresponding MOSFET datasheet;  $I_Q$  is the driver's total quiescent current with no load at both drive outputs;  $N_{Q1}$  and  $N_{Q2}$  are number of upper and lower MOSFETs, respectively; PVCC is the drive voltages for both upper and lower FETs, respectively. The  $I_{Q^*}$ VCC product is the quiescent power of the driver without capacitive load and is typically 200mW at 300kHz.

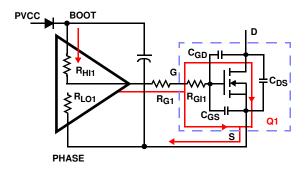

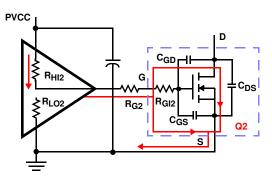

The total gate drive power losses are dissipated among the resistive components along the transition path. The drive resistance dissipates a portion of the total gate drive power losses, the rest will be dissipated by the external gate resistors ( $R_{G1}$  and  $R_{G2}$ ) and the internal gate resistors ( $R_{G11}$  and  $R_{G12}$ ) of MOSFETs. Figures 3 and 4 show the typical upper and lower gate drives turn-on transition path. The power dissipation on the driver can be roughly estimated in Equation 4:

$$\begin{split} &P_{DR} = 2 \bullet P_{DR\_UP} + 2 \bullet P_{DR\_LOW} + I_{Q} \bullet VCC \\ &P_{DR\_UP} = \left(\frac{R_{HI1}}{R_{HI1} + R_{EXT1}} + \frac{R_{LO1}}{R_{LO1} + R_{EXT1}}\right) \bullet \frac{P_{Qg\_Q1}}{2} \\ &P_{DR\_LOW} = \left(\frac{R_{HI2}}{R_{HI2} + R_{EXT2}} + \frac{R_{LO2}}{R_{LO2} + R_{EXT2}}\right) \bullet \frac{P_{Qg\_Q2}}{2} \\ &R_{EXT1} = R_{G1} + \frac{R_{GI1}}{N_{O1}} \qquad \qquad R_{EXT2} = R_{G2} + \frac{R_{GI2}}{N_{O2}} \end{split}$$

FIGURE 3. TYPICAL UPPER-GATE DRIVE TURN-ON PATH

FIGURE 4. TYPICAL LOWER-GATE DRIVE TURN-ON PATH

#### Layout Considerations

For heat spreading, place copper underneath the IC whether it has an exposed pad or not. The copper area can be extended beyond the bottom area of the IC and/or connected to buried copper plane(s) with thermal vias. This combination of vias for vertical heat escape, extended copper plane, and buried planes for heat spreading allows the IC to achieve its full thermal potential.

Place each channel power component as close to each other as possible to reduce PCB copper losses and PCB parasitics: shortest distance between DRAINs of upper FETs and SOURCEs of lower FETs; shortest distance between DRAINs of lower FETs and the power ground. Thus, smaller amplitudes of positive and negative ringing are on the switching edges of the PHASE node. However, some space in between the power components is required for good airflow. The traces from the drivers to the FETs should be kept short and wide to reduce the inductance of the traces and to promote clean drive signals.

intersil FN9160.4 May 5, 2008

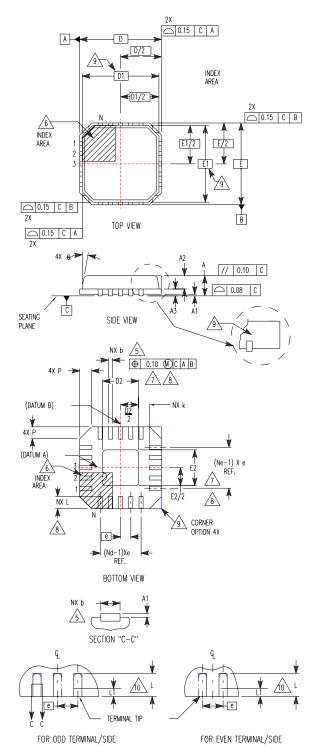

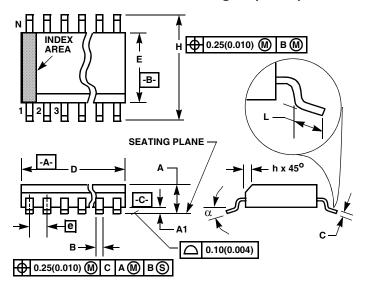

# Quad Flat No-Lead Plastic Package (QFN) Micro Lead Frame Plastic Package (MLFP)

L16.4x4

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

(COMPLIANT TO JEDEC MO-220-VGGC ISSUE C)

| SYMBOL | MIN  | NOMINAL MAX    |      | NOTES |  |  |

|--------|------|----------------|------|-------|--|--|

| Α      | 0.80 | 0.90           | 1.00 | -     |  |  |

| A1     | -    | -              | 0.05 | -     |  |  |

| A2     | -    | -              | 1.00 | 9     |  |  |

| A3     |      | 0.20 REF       |      | 9     |  |  |

| b      | 0.23 | 0.28           | 0.35 | 5, 8  |  |  |

| D      |      | 4.00 BSC       |      | -     |  |  |

| D1     |      | 3.75 BSC       |      | 9     |  |  |

| D2     | 1.95 | 1.95 2.10 2.25 |      |       |  |  |

| E      |      | -              |      |       |  |  |

| E1     |      | 9              |      |       |  |  |

| E2     | 1.95 | 1.95 2.10 2.25 |      |       |  |  |

| е      |      | 0.65 BSC       |      | -     |  |  |

| k      | 0.25 | -              | -    | -     |  |  |

| L      | 0.50 | 0.60           | 0.75 | 8     |  |  |

| L1     | -    | 0.15           |      |       |  |  |

| N      |      | 2              |      |       |  |  |

| Nd     |      | 3              |      |       |  |  |

| Ne     |      | 3              |      |       |  |  |

| Р      | -    | -              | 9    |       |  |  |

| θ      | -    | -              | 12   | 9     |  |  |

Rev. 5 5/04

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd and Ne refer to the number of terminals on each D and E.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- Features and dimensions A2, A3, D1, E1, P & 0 are present when Anvil singulation method is used and not present for saw singulation.

- Depending on the method of lead termination at the edge of the package, a maximum 0.15mm pull back (L1) maybe present. L minus L1 to be equal to or greater than 0.3mm.

intersil FN9160.4 May 5, 2008

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M14.15 (JEDEC MS-012-AB ISSUE C)

14 LEAD NARROW BODY SMALL OUTLINE PLASTIC

PACKAGE

|        | INCHES  |        | MILLIM |         |   |

|--------|---------|--------|--------|---------|---|

| SYMBOL | MIN MAX |        | MIN    | MIN MAX |   |

| Α      | 0.0532  | 0.0688 | 1.35   | 1.75    | - |

| A1     | 0.0040  | 0.0098 | 0.10   | 0.25    | - |

| В      | 0.013   | 0.020  | 0.33   | 0.51    | 9 |

| С      | 0.0075  | 0.0098 | 0.19   | 0.25    | - |

| D      | 0.3367  | 0.3444 | 8.55   | 8.75    | 3 |

| Е      | 0.1497  | 0.1574 | 3.80   | 4.00    | 4 |

| е      | 0.050   | BSC    | 1.27   | BSC     | - |

| Н      | 0.2284  | 0.2440 | 5.80   | 6.20    | - |

| h      | 0.0099  | 0.0196 | 0.25   | 0.50    | 5 |

| L      | 0.016   | 0.050  | 0.40   | 1.27    | 6 |

| N      | 14      |        | 1      | 4       | 7 |

| α      | 0° 8°   |        | 0°     | 8°      | - |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil FN9160.4 May 5, 2008