# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## ISL8723, ISL8724

#### Data Sheet

#### April 22, 2009

## Power Sequencing Controllers

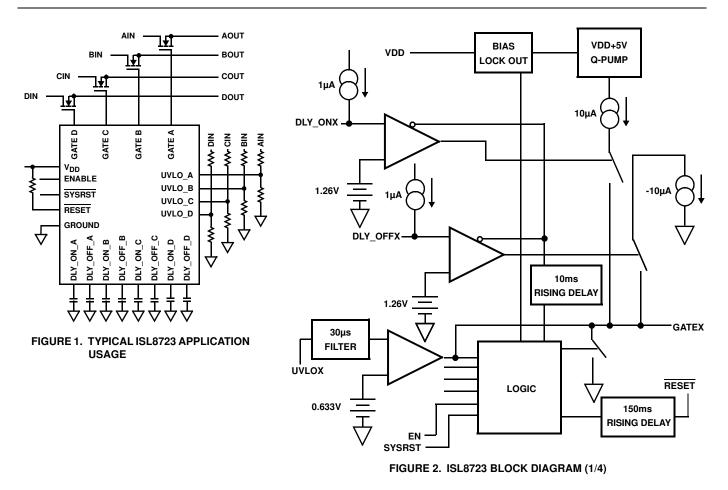

The Intersil ISL8723 and ISL8724 are 4 channel sequencers controlling the on and off sequence of voltages with undervoltage supply fault protection and a "sequence completed" signal (RESET). For larger systems, more than 4 voltages can be sequenced by a simple connection of multiple IC's. These sequencers use an integrated charge pump to drive 4 external low-cost N-channel MOSFET switch gates above the IC bias voltage by 5.3V. These IC's can be biased from and control any supply from 2.5V to 5V and additionally monitor any voltage above 0.7V. Individual product descriptions follow.

The four channel **ISL8723** (ENABLE input), **ISL8724** (ENABLE input) offer the designer 4 voltage control when it is required that all four rails are in minimal compliance prior to turn on and that compliance must be maintained during operation. The **ISL8723** has a low power standby mode when it is disabled suitable for battery powered applications.

External resistors provide flexible voltage threshold programming of monitored voltages. Delay and sequencing timing are programmable by external capacitors for both ramp up and ramp down.

Ordering Information

#### TEMP. PART NUMBER PART RANGE PACKAGE PKG. (Note) MARKING (°C) (Pb-free) DWG. # ISL8723IRZ\* 87 23IRZ 40 to +85 24 Ld 4x4 QFN L24.4x4 ISL8724IRZ\* 87 24IRZ -40 to +85 24 Ld 4x4 QFN L24.4x4 ISL8723EVAL1 **Evaluation Platform**

\*Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- Enables arbitrary turn-on and turn-off sequencing of up to four power supplies (0.7V to 5V)

- Operates from 2.5V to 5V supply voltage

- Supplies V<sub>DD</sub> +5.3V of charge pumped gate drive

- · Adjustable voltage slew rate for each rail

- Multiple sequencers can be easily daisy-chained to sequence an infinite number of independent voltages

- · Glitch immunity

- · Undervoltage lockout for each monitored supply voltage

- 30µA Sleep State (ISL8723)

- Active high (ISL8723) or low (ISL8724) ENABLE input

- Pb-free (RoHS compliant)

## Applications

- Graphics cards

- FPGA/ASIC/microprocessor/PowerPC supply sequencing

- Network Routers

- Telecommunications Systems

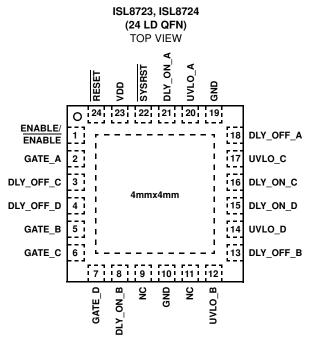

### Pinout

## **Pin Descriptions**

| PIN<br># | PIN<br>NAME       | FUNCTION                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23       | VDD               | Chip Bias                        | Bias IC from nominal 2.5V to 5V                                                                                                                                                                                                                                                                                                                                                                     |

| 10, 19   | GND               | Bias Return                      | IC ground. NOTE: Pin 19 internally tied to GND with $6k\Omega$ . This pin can be tied to GND or left open.                                                                                                                                                                                                                                                                                          |

| 1        | ENABLE/<br>ENABLE | Input to start on/off sequencing | Input to initiate the start of the programmed sequencing of supplies on or off. Enable functionality is disabled for 10ms after UVLO is satisfied. ISL8723 has ENABLE. ISL8724 has ENABLE.                                                                                                                                                                                                          |

| 24       | RESET             | RESET Output                     | RESET provides a high signal ~160ms after all GATEs are fully enhanced. This delay is for stabilization of output voltages. RESET will assert low upon any UVLO not being satisfied or ENABLE/ENABLE being deasserted. The RESET output is an open drain N-channel FET and is guaranteed to be in the correct state for VDD down to 1V and is filtered to ignore fast transients on VDD and UVLO_X. |

| 20       | UVLO_A            | Undervoltage Lock                | These inputs provide for a programmable UV lockout referenced to an internal 0.631V reference and                                                                                                                                                                                                                                                                                                   |

| 12       | UVLO_B            | Out/Monitoring<br>Input          | are filtered to ignore short (<7µs) transients below programmed UVLO level.                                                                                                                                                                                                                                                                                                                         |

| 17       | UVLO_C            |                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14       | UVLO_D            |                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21       | DLY_ON_A          | Gate On Delay                    | Allows for programming the delay and sequence for V <sub>OUT</sub> turn-on using a capacitor to ground. Each                                                                                                                                                                                                                                                                                        |

| 8        | DLY_ON_B          | Timer Output                     | cap is charged with 1µA, 10ms after turn-on initiated by ENABLE/ENABLE with an internal current source providing delayed enhancement of the associated FETs GATE to turn-on.                                                                                                                                                                                                                        |

| 16       | DLY_ON_C          |                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15       | DLY_ON_D          |                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |

## **Pin Descriptions** (Continued)

| PIN<br># | PIN<br>NAME | FUNCTION                                                                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                    |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18       | DLY_OFF_A   | Gate Off Delay                                                                                                                                                                           | Allows for programming the delay and sequence for V <sub>OUT</sub> turn-off through ENABLE/ENABLE via a                                                                                                                                                                        |

| 13       | DLY_OFF_B   | Timer Output capacitor to ground. Each cap is charged with a 1µA internal current source to an intern voltage causing the corresponding gate to be pulled down thus turning-off the FET. | capacitor to ground. Each cap is charged with a $1\mu$ A internal current source to an internal reference voltage causing the corresponding gate to be pulled down thus turning-off the FET.                                                                                   |

| 3        | DLY_OFF_C   |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                |

| 4        | DLY_OFF_D   |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                |

| 2        | GATE_A      | FET Gate Drive                                                                                                                                                                           | Drives the external FETs with a $10\mu$ A current source to soft start ramp into the load. During sequence                                                                                                                                                                     |

| 5        | GATE_B      | Output                                                                                                                                                                                   | off, 10μA is sunk from this pin to control the FET turn-off. During a turn-off due to a fault, the gate will sink ~75mA to ensure a rapid turn-off.                                                                                                                            |

| 6        | GATE_C      |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                |

| 7        | GATE_D      |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                |

| 22       | SYSRST      | System Reset I/O                                                                                                                                                                         | As an input, allows for immediate and unconditional latch-off of all GATE outputs when driven low. This pin can also be used to initiate the programmed sequence with 'zero' wait (no 10ms stabilization delay) from input signal on this pin being driven high to first GATE. |

|          |             |                                                                                                                                                                                          | As an output when there is a UV condition this pin pulls low. If common to other SYSRST pins in a multiple IC configuration it will cause immediate and unconditional latch-off of all other GATEs on all other ISL872x sequencers.                                            |

|          |             |                                                                                                                                                                                          | This pin is released to go high once all UVLO and enable conditions are satisfied and is pulled low concurrent with the last GATE being turned off after EN disabled.                                                                                                          |

| 9, 11    | No Connect  | No Connect                                                                                                                                                                               | No Connect                                                                                                                                                                                                                                                                     |

#### **Absolute Maximum Ratings**

| V <sub>DD</sub> +6.0V                                     |

|-----------------------------------------------------------|

| GATE                                                      |

| UVLO, ENABLE, ENABLE, SYSRST0.3V to V <sub>DD</sub> +0.3V |

| RESET, DLY_ON, DLYOFF0.3V to V <sub>DD</sub> +0.3V        |

#### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range | +2.5V to +5.0V |

|--------------------------------------|----------------|

| Temperature Range (T <sub>A</sub> )  | 40°C to +85°C  |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 1, 2) | $\theta_{JA}$ (°C/W) | $\theta_{\text{JC}} (^{\circ}\text{C/W})$ |

|------------------------------------------|----------------------|-------------------------------------------|

| 24 Ld 4x4 QFN Package                    | 48                   | 9                                         |

| Maximum Junction Temperature             |                      | +125°C                                    |

| Maximum Storage Temperature Range        | 65°                  | °C to +150°C                              |

| Pb-Free Reflow Profile                   |                      | ee link below                             |

| http://www.intersil.com/pbfree/Pb-FreeF  | leflow.asp           |                                           |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 3. All voltages are relative to GND, unless otherwise specified.

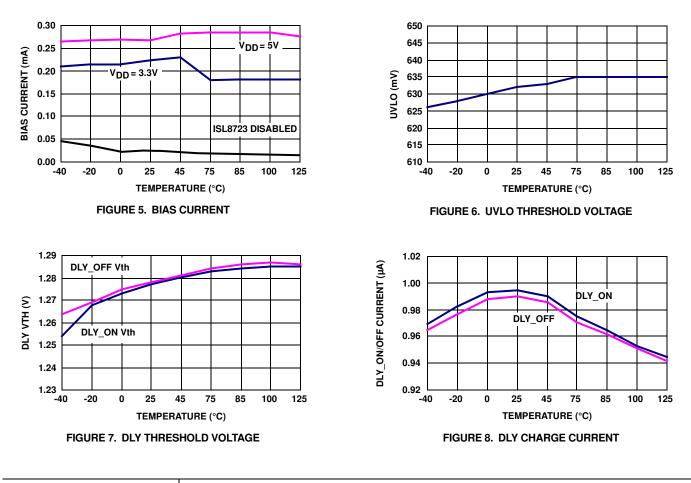

**Electrical Specifications**  $V_{DD} = 3.3V$  to +5V,  $T_A = T_J = -40^{\circ}C$  to +85°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| PARAMETER                              | SYMBOL                              | TEST CONDITIONS                                        | MIN  | ТҮР                    | MAX   | UNIT |

|----------------------------------------|-------------------------------------|--------------------------------------------------------|------|------------------------|-------|------|

| UVLO                                   |                                     |                                                        |      |                        |       |      |

| Undervoltage Lockout Falling Threshold | V <sub>UVLOvth</sub>                | $T_A = T_J = +25^{\circ}C$                             | 619  | 631                    | 647   | mV   |

| Undervoltage Lockout Falling Threshold | V <sub>UVLOvth</sub>                |                                                        | 604  | 631                    | 656   | mV   |

| Undervoltage Lockout Hysteresis        | V <sub>UVLOhys</sub>                |                                                        | -    | 9                      | -     | mV   |

| Undervoltage Lockout Threshold Range   | RUVLOvth                            | Max V <sub>UVLOvth</sub> - Min V <sub>UVLOvth</sub>    | -    | 6                      | 18    | mV   |

| Undervoltage Lockout Delay             | t <sub>UVLOdel</sub>                | ENABLE satisfied                                       | -    | 10                     | -     | ms   |

| Transient Filter Duration              | tFIL                                | V <sub>DD</sub> , UVLO, ENABLE glitch filter           | -    | 7                      | -     | μs   |

| DELAY ON/OFF                           |                                     |                                                        |      |                        |       | 1    |

| Delay Charging Current                 | DLY_ichg                            | $V_{DLY} = 0V$                                         | 0.9  | 1                      | 1.115 | μA   |

| Delay Charging Current Range           | DLY_ichg_r                          | DLY_ichg(max) - DLY_ichg(min)                          | -    | 0.01                   | 0.05  | μA   |

| Delay Threshold Voltage                | DLY_Vth                             |                                                        | 1.21 | 1.273                  | 1.32  | V    |

| ENABLE/ENABLE, RESET AND SYSRST        | I/O                                 |                                                        |      | 1 1                    |       |      |

| ENABLE Threshold                       | V <sub>ENh</sub>                    | Measured at V <sub>DD</sub> = 5V                       | -    | 1.28                   | 1.35  | V    |

| ENABLE Threshold                       | V <sub>ENh</sub>                    |                                                        | -    | 0.5 V <sub>DD</sub>    | -     | V    |

| ENABLE/ENABLE Hysteresis               | V <sub>ENh -</sub> V <sub>ENI</sub> | Measured at $V_{DD} = 5V$                              | -    | 0.1                    | 0.2   | V    |

| ENABLE/ENABLE Lockout Delay            | <sup>t</sup> delEN_LO               | UVLO satisfied, EN to DLY_ON                           | -    | 10                     | -     | ms   |

| ENABLE/ENABLE Input Capacitance        | C <sub>IN_EN</sub>                  |                                                        | -    | 5                      | -     | pF   |

| RESET Pull-up Voltage                  | V <sub>PU_RST</sub>                 |                                                        | -    | V <sub>DD</sub>        | -     | V    |

| RESET Pull-Down Current                | IRSTpd5                             | V <sub>DD</sub> = 5V, <del>RST</del> = 0.1V            | -    | 13                     | -     | mA   |

| RESET Delay after GATE High            | T <sub>RSTdel</sub>                 | GATE = V <sub>DD</sub> + 5V                            | -    | 160                    | -     | ms   |

| RESET Output Low                       | VRSTI                               | Measured at V <sub>DD</sub> = 5V, 1mA sourcing current | -    | -                      | 0.1   | V    |

| RESET Output Capacitance               | C <sub>OUT_RST</sub>                |                                                        | -    | 10                     | -     | pF   |

| SYSRST Pull-up Voltage                 | V <sub>PU_SRST</sub>                |                                                        | -    | V <sub>DD</sub> - 0.5V | -     | V    |

| SYSRST Pull-up Current                 | IPU_SRST                            | V <sub>DD</sub> = 3.3V, <u>SYSRST</u> = 0.5V           | -    | 12                     | -     | μA   |

| SYSRST Pull Down Current               | I <sub>PU_5</sub>                   | $V_{DD} = 5V$                                          | -    | 2.7                    | -     | μA   |

#### **Electrical Specifications**

$V_{DD} = 3.3V$  to +5V,  $T_A = T_J = -40^{\circ}$ C to +85°C, Unless Otherwise Specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (**Continued**)

| PARAMETER                          | SYMBOL                  | TEST CONDITIONS                                | MIN                    | ТҮР                    | MAX  | UNIT |

|------------------------------------|-------------------------|------------------------------------------------|------------------------|------------------------|------|------|

| SYSRST Low Output Voltage          | V <sub>OL_SRST</sub>    | V <sub>DD</sub> = 5V, I <sub>OUT</sub> = 100µA | -                      |                        | 0.1  | V    |

| SYSRST Output Capacitance          | C <sub>OUT_SRST</sub>   |                                                | -                      | 10                     | -    | pF   |

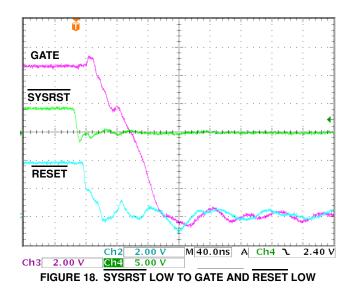

| SYSRST Low to GATE Turn-off        | <sup>t</sup> delSYS_G_1 | GATE = 80% of $V_{DD}$ +5V                     | -                      | 40                     | -    | ns   |

| SYSRST High to GATE Turn-on        | <sup>t</sup> delSYS_G_2 | GATE = 50% of $V_{DD}$ +5V                     | -                      | 0.4                    | -    | ms   |

| GATE                               |                         |                                                |                        |                        |      | 1    |

| GATE Turn-On Current               | IGATEon                 | GATE = 0V                                      | 8.3                    | 10.2                   | 12.5 | μA   |

| GATE Turn-Off Current              | IGATEoff_I              | GATE = V <sub>DD</sub> , Disabled              | -12.5                  | -10.2                  | -8.3 | μA   |

| GATE Current Range                 | IGATE_range             | Within IC IGATE max-min                        | -                      | 0.6                    | 3    | μA   |

| GATE Pull-Down High Current        | IGATEoff_h              | $GATE = V_{DD}, UVLO = 0V$                     | -                      | 75                     | -    | mA   |

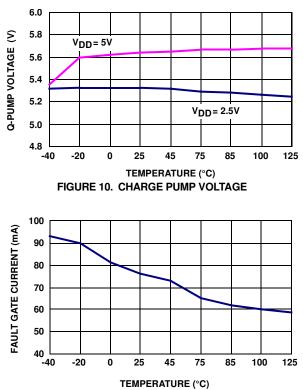

| GATE High Voltage                  | V <sub>GATEh5</sub>     | $V_{DD} = 5V$                                  | V <sub>DD</sub> + 5.3V | V <sub>DD</sub> + 5.6V | -    | V    |

| GATE Low Voltage                   | V <sub>GATEI</sub>      | Gate Low Voltage, V <sub>DD</sub> = 1V         | -                      | 0.01                   | 0.1  | V    |

| BIAS                               |                         |                                                | ·                      |                        |      |      |

| IC Supply Current                  | I <sub>VDD_5V</sub>     | $V_{DD}$ = 5V, Enabled and static              | -                      | 0.48                   | 0.6  | mA   |

| ISL8723 Stand By IC Supply Current | I <sub>VDD_sb</sub>     | V <sub>DD</sub> = 5V, ENABLE = 0V              | -                      | 30                     | 40   | μA   |

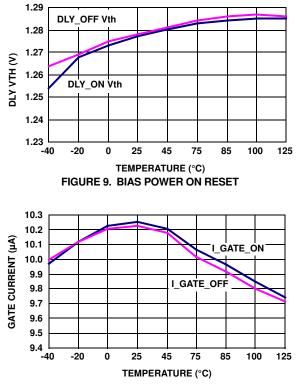

| V <sub>DD</sub> Power On Reset     | V <sub>DD</sub> _POR    | V <sub>DD</sub> rising                         | -                      | 2.2                    | 2.41 | V    |

# ISL8723, ISL8724 Descriptions and Operation

The ISL8723 and ISL8724 sequencers are quad voltage sequencing controllers designed for use in multiple-voltage systems requiring power sequencing of various supply voltages. Individual voltage rails are gated on and off by external N-Channel MOSFETs, the gates of which are driven by an internal charge pump to  $\sim V_{DD}$  +5.6V (VQP) in a user programmed sequence.

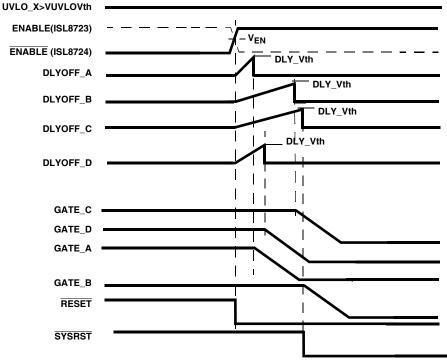

With the ISL8723, the ENABLE must be asserted high and all four voltages to be sequenced must be above their respective user programmed Undervoltage Lock Out (UVLO) levels before programmed output turn on sequencing can begin. Sequencing and delay determination is accomplished by the choice of external capacitor values on the DLY ON and DLY OFF pins. The SYSRST goes high once all 4 UVLO inputs and ENABLE are satisfied. Once all 4 UVLO inputs and ENABLE are satisfied for 10ms, the four DLY ON capacitors are simultaneously charged with 1µA current sources to the DLY Vth level of 1.28V. As each DLY ON pin reaches the DLY Vth level, its associated GATE will then turn-on with a  $10\mu$ A source current to the VQP voltage of V<sub>DD</sub> + 5.6V. Thus, all four GATEs will sequentially turn on. Once at DLY Vth the DLY ON pins will discharge to be ready when next needed. After the entire turn on sequence has been completed and all GATEs have reached the charge pumped voltage (VQP), a 160ms delay is started to ensure stability after which the RESET output will be released to go high. Subsequent to turn-on, if any input falls below its

UVLO point for longer than the glitch filter period, tFII (~7µs) this is considered a fault. RESET, SYSRST and all GATEs are simultaneously pulled low. In this mode the GATEs are pulled low with ~75mA. Normal shutdown mode is entered when no UVLO is violated and the ENABLE is deasserted. When ENABLE is deasserted, RESET is asserted and pulled low. Next, all four shutdown ramp capacitors on the DLY OFF pins are charged with a 1µA source and when any ramp-capacitor reaches DLY Vth, a latch is set and a 10µA current is sunk on the respective GATE pin to turn off its external MOSFET. When the falling GATE voltage is approximately 1.5V, the GATE is pulled down the rest of the way at a higher current level to ensure a hard turn-off. Each individual external FET is thus turned off removing the voltages from the load in the programmed sequence. The SYSRST will pull low concurrent with the last GATE being pulled low.

The ISL8723 and ISL8724 have the same functionality except for the complimentary ENABLE active polarity with the ISL8724 having an ENABLE input. Additionally, the ISL8723 also has a low power sleep state when disabled.

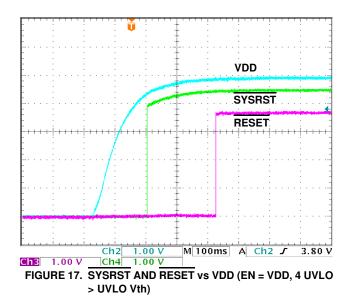

Upon bias, the  $\overline{SYSRST}$  and  $\overline{RESET}$  pins are held low before bias voltage = 1V.

The SYSRST has both an input and output function. As an output, the SYSRST pin is useful when implementing multiple sequencers in a design needing simultaneous shutdown as with a kill switch across all sequencers. Once any UVLO is unsatisfied for longer than  $t_{FIL}$ , the related SYSRST will pull low and pull all other SYSRST pins low

that are on a common connection thus unconditionally shutting down all outputs across multiple sequencers. As an input, if it is pulled low all GATEs will be unconditionally shut off and RESET pulled low (see Figure 18). This pin can also be used as a 'no wait' enabling input if all inputs (ENABLE and UVLO) are satisfied; it does not wait through the ~10ms enable delay to initiate the DLY\_ON capacitor charging when released to go high. This feature can be used where 4 voltages can be monitored in addition to a on-off switch position or, in the case of the ISL8724, a present pin pull-down.

Restart of the turn on sequence is automatic once all requirements are met. This allows for no interaction between the sequencer and a controller IC if so desired. If no capacitors are connected between DLY\_ON or DLY\_OFF pins and ground then all such related GATEs start to turn on immediately after the 10ms (t<sub>UVLOdel</sub>) ENABLE stabilization time out has expired and the GATEs start to immediately turn off when ENABLE is deasserted.

Table 1 illustrates the nominal time delay from the start of charging to the 1.27V reference for various capacitor values on the DLY\_X pins. This table does not include the 10ms of enable lock out delay during a start-up sequence but represents the time from the end of the enable lock out

delay to the start of GATE transition. There is no enable lock out delay for a sequence off, so this table illustrates the delay to GATE transition from a disable signal.

| TABLE 1.                              |       |  |  |  |

|---------------------------------------|-------|--|--|--|

| NOMINAL DELAY TO SEQUENCING THRESHOLD |       |  |  |  |

| DLY PIN TIME<br>CAPACITANCE (ms)      |       |  |  |  |

| Open 0.02                             |       |  |  |  |

| 100pF                                 | 0.135 |  |  |  |

| 1000pF                                | 1.35  |  |  |  |

| 0.01µF                                | 13.5  |  |  |  |

| 0.1µF 135                             |       |  |  |  |

| 1µF 1350                              |       |  |  |  |

|                                       |       |  |  |  |

NOTE: Nom. T<sub>DEL</sub> SEQ = dly\_cap ( $\mu$ F)x1.35M $\Omega$

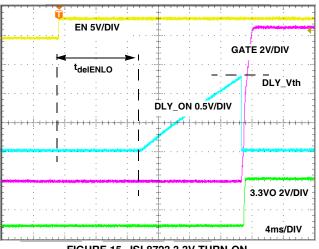

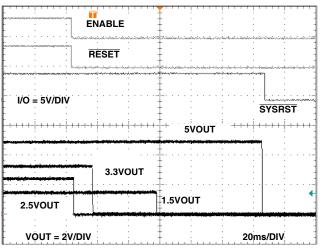

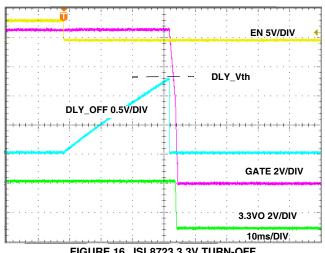

Figure 3 illustrates the turn-on and Figure 4 the nominal turnoff timing diagrams of the **ISL8723** and **ISL8724** product.

Note the delay and flexible sequencing possibilities. Multiple series, parallel or adjustable capacitors can be used to easily fine tune timing between that offered by standard value capacitors.

FIGURE 3. ISL8723, ISL8724 TURN-ON AND GLITCH RESPONSE TIMING DIAGRAM

FIGURE 4. ISL8723, ISL8724 TURN-OFF TIMING DIAGRAM

7

## Typical Performance Curves (Continued)

FIGURE 11. GATE TURN-OFF/ON (DIS)CHARGE CURRENT

## Using the ISL8723EVAL1 Platform

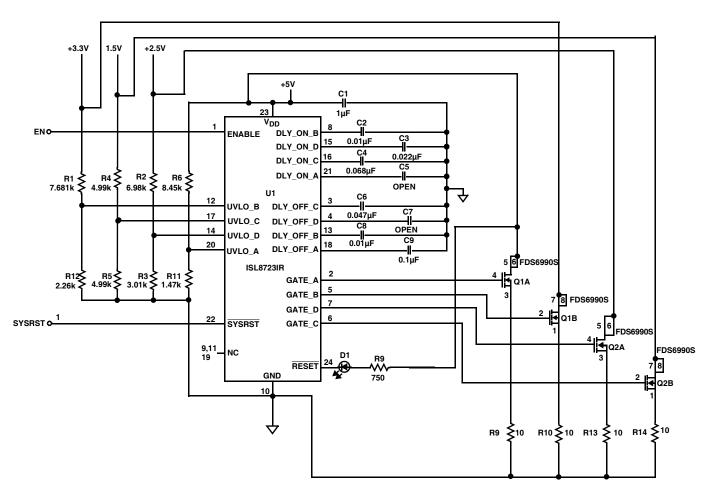

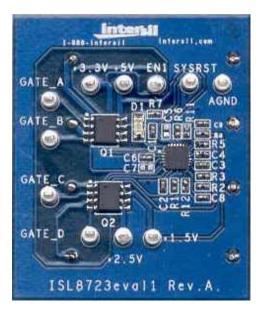

The **ISL8723EVAL1** platform allows evaluation of the ISL8723, easily providing access to the critical nodes (see Figure 22 for schematic and Figure 23 for a photograph of the evaluation platform).

The board has a SMD layout with a **ISL8723** illustrating the possible small implementation size for a typical four rail sequencing application. There are bias and function labeled test points to give access to the IC pins for evaluation. Remember that significant current or capacitive loading of particular I/O pins will affect functionality and performance.

The default configuration of the **ISL8723EVAL1** circuit was built around the following design assumptions:

- 1. Using the ISL8723IR

- The four supplies being sequenced are 5V (IN\_A), 3.3V (IN\_B), 2.5V (IN\_D) and 1.5V (IN\_C), the UVLO levels are ~80% of nominal voltages. Resistors chosen such that the total resistance of each divider is ~ 10k using standard value resistors to approximate 80% of nominal voltage supply = 0.63V on UVLO input.

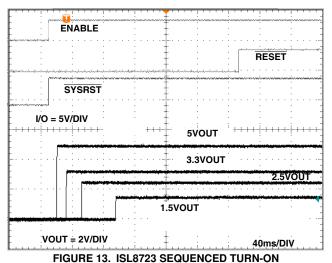

- The desired order turn-on sequence is 5V first, then 3.3V about 12ms later then the 2.5V supply about 19ms later and lastly the 1.5V supply about 40ms later.

- The desired turn-off sequence is first the 2.5V, the 3.3V 12ms later, then the 1.5V supply about 36ms later and lastly the 5V supply about 72ms after that.

FIGURE 12. FAULT GATE TURN-OFF SINK CURRENT

5. LED off indicates sequence has completed and RESET has released and pulled high.

All scope shots are taken from ISL8723EVAL1 board. Figures 13 and 14 illustrate the desired turn-on and turn-off sequences respectively. The sequencing order and delay between voltages sequencing is set by external capacitance values so other than that illustrated can be accomplished.

Figures 15 and 16 illustrate the timing relationships between the EN input, RESET, DLY and GATE outputs and the VOUT voltage for a single channel being turned on and off respectively.

RESET and SYSRST functionality and relationships are shown in Figures 17 through 21.

Figure 17 illustrates that with a rising VDD, EN tied to VDD, and all UVLO configured to be satisfied, both the RESET and SYSRST are held low before  $V_{DD} = 1V$ . SYSRST is released to go high once the last UVLO is satisfied and RESET is released to go high at  $t_{RSTdel}$  after the last GATE is high.

Figure 18 shows GATE and RESET response to SYSRST being pulled low.

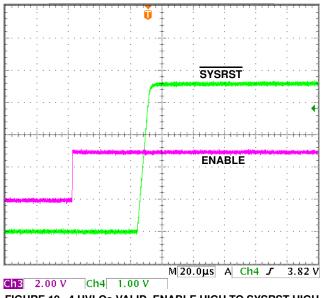

Figure 19 shows EN high to SYSRST delay with all UVLO inputs satisfied.

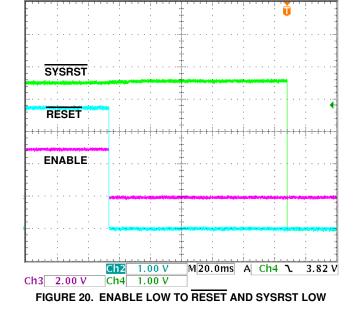

Figure 20 shows RESET and SYSRST delay to EN pulled low.

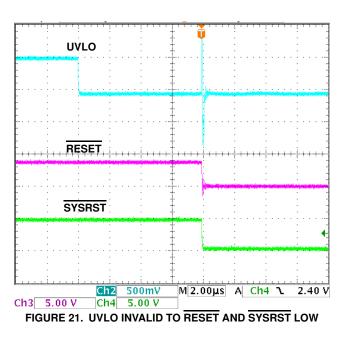

Figure 21 shows ~8 $\mu s$  of glitch filter duration,  $t_{FIL}$  during which the RESET and SYSRST do not react.

## **Typical Performance Waveforms**

FIGURE 15. ISL8723 3.3V TURN-ON

FIGURE 14. ISL8723 SEQUENCED TURN-OFF

FIGURE 16. ISL8723 3.3V TURN-OFF

Typical Performance Waveforms (Continued)

FIGURE 19. 4 UVLOS VALID, ENABLE HIGH TO SYSRST HIGH

FIGURE 23. EVAL BOARD PHOTOGRAPH

#### COMPONENT DESIGNATOR **COMPONENT FUNCTION** COMPONENT DESCRIPTION 111 ISL8723, 4 Supply Sequencer Intersil, ISL8723IR 4 Supply Sequencer Q1. Q2 FDS6990S or equivalent, Dual N-Channel MOSFET Voltage Rail Switches R6 5V to UVLO A Resistor for Divider String 8.45kΩ 1%, 0402 R11 UVLO A to GND Resistor for Divider String 1.47kΩ 1%, 0402 R1 3.3V to UVLO\_B Resistor for Divider String 7.68kΩ 1%, 0402 **R12** UVLO B to GND Resistor for Divider String 2.26kΩ 1%, 0402 R2 6.98kΩ 1%, 0402 2.5V to UVLO D Resistor for Divider String R3 UVLO D to GND Resistor for Divider String 3.01kΩ 1%, 0402 R4 1.5V to UVLO C Resistor for Divider String 4.99kΩ 1%, 0402 R5 UVLO D to GND Resistor for Divider String 4.99kΩ 1%, 0402 R9 **RESET LED Current Limiting Resistor** 750Ω 10%, 0805 C5 5V turn-on Delay Capacitor A (~10ms) DNP, 0402 C9 5V turn-off Delay Capacitor A (~140ms) 0.1µF 10%, 6.3V, 0402 C2 3.3V turn-on Delay Capacitor B (~13ms) 0.01µF 10%, 6.3V, 0402 C8 3.3V turn-off Delay Capacitor B (~13ms) 0.01µF 10%, 6.3V, 0402 C3 2.5V turn-on Delay Capacitor D (~25ms) 0.022µF 10%, 6.3V, 0402 C7 2.5V turn-off Delay Capacitor D (0ms) DNP, 0402 C4 1.5V turn-on Delay Capacitor C (~100ms) 0.068µF 10%, 6.3V, 0402 0.047µF 10%, 6.3V, 0402 C6 1.5V turn-off Delay Capacitor C (~60ms) C1 **Decoupling Capacitor** 1µF, 0805 D1 **RESET Indicating LED** 0805, SMD LEDs Red R9 5V Load Resistor 10Ω 20%, 3W Carbon **R10** 3.3V Load Resistor 10Ω 20%, 3W Carbon R13 2.5V Load Resistor 10Ω 20%, 3W Carbon R14 1.5V Load Resistor 10Ω 20%, 3W Carbon Test Points Labeled as to Function

#### TABLE 2. ISL872XSEQEVAL1 BOARD COMPONENT LISTING

## Application Implementations

#### Multiple Sequencer Implementations

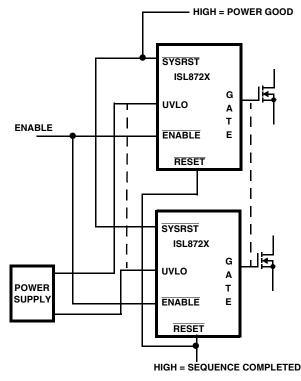

In order to control the sequencing of more than 4 voltages in applications where the integrity of these critical voltages must be assured prior to sequencing, several of the ISL8723 or ISL8724 devices can configured together to accomplish this.

Figure 24 shows a typical multi sequencer implementation; note the common SYSRST signal that asserts once all monitored voltages are valid allowing the sequence to initiate. The sequencing is straight forward across multiple sequencers as all DLY\_ON capacitors will simultaneously start charging once all monitored voltages area valid and ~10ms after the common ENABLE input signal is delivered. This allows the choice of capacitors to be related to each other no different than using a single sequencer. When the common enabling signal is deasserted, this configuration will then execute the turn-off sequence across all sequencers as programmed by the DLY\_OFF capacitor values. With all the SYSRST pins bused together, once the on sequence is complete, simultaneous shutdown upon any UVLO input failure is assured as the SYSRST output will pull low, simultaneously turning off all GATE outputs.

FIGURE 24. MULTIPLE ISL872X CONFIGURATION

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

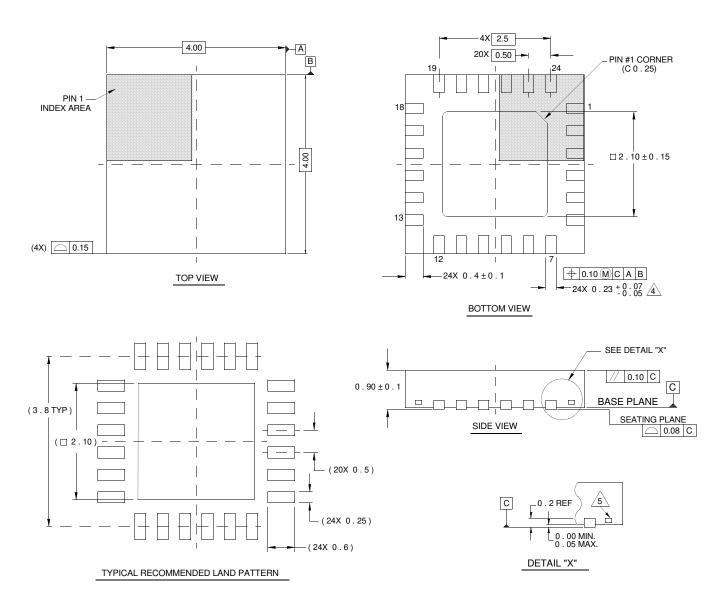

## **Package Outline Drawing**

#### L24.4x4

24 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 4, 10/06

NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 indentifier may be either a mold or mark feature.