# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Lattice<sup>®</sup> Semiconductor Corporation

# ispClock<sup>®</sup>5600A Family

In-System Programmable, Enhanced Zero-Delay Clock Generator with Universal Fan-Out Buffer

Data Sheet DS1019

## June 2008

## Features

- 8MHz to 400MHz Input/Output Operation

- Low Output to Output Skew (<50ps)

- Low Jitter Peak-to-Peak

- Up to 20 Programmable Fan-out Buffers

- Programmable output standards and individual enable controls

- LVTTL, LVCMOS, HSTL, eHSTL, SSTL, LVDS, LVPECL, Differential HSTL, SSTL

- Programmable output impedance

40 to 70Ω in 5Ω increments

- Programmable slew rate

- Up to 10 banks with individual V<sub>CCO</sub> and GND

1.5V, 1.8V, 2.5V, 3.3V

- Fully Integrated High-Performance PLL

- Programmable lock detect

- · Multiply and divide ratio controlled by

- Input divider (1 to 40)

- Feedback divider (1 to 40)

- Five output dividers (2 to 80)

- Programmable on-chip loop filter

- Compatible with spread spectrum clocks

### Precision Programmable Phase Adjustment (Skew) Per Output

- 16 settings; minimum step size 156ps

- Locked to VCO frequency

- Up to +/- 12ns skew range

- Coarse and fine adjustment modes

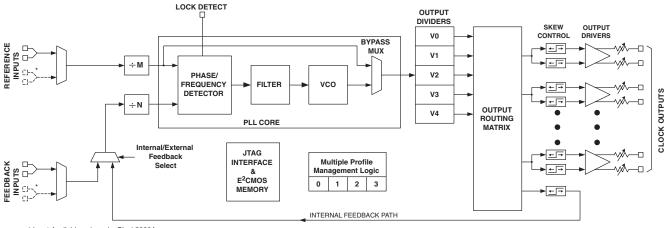

## **Product Family Block Diagram**

- Up to Five Clock Frequency Domains

- Flexible Clock Reference and External Feedback Inputs

- Programmable input standards

LVTTL, LVCMOS, SSTL, HSTL, LVDS, LVPECL, Differential HSTL, SSTL

- Clock A/B selection multiplexer

- Feedback A/B selection multiplexer

- Programmable termination

- All Inputs and Outputs are Hot Socket Compliant

- Four User-programmable Profiles Stored in E<sup>2</sup>CMOS<sup>®</sup> Memory

- Supports both test and multiple operating configurations

- Full JTAG Boundary Scan Test In-System Programming Support

- Exceptional Power Supply Noise Immunity

- Commercial (0 to 70°C) and Industrial (-40 to 85°C) Temperature Ranges

- 100-pin and 48-pin TQFP Packages

- Applications

- Circuit board common clock generation and distribution

- PLL-based frequency generation

- · High fan-out clock buffer

- Zero-delay clock buffer

\* Input Available only on ispClock5620A

© 2008 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

## **General Description and Overview**

The ispClock5610A and ispClock5620A are in-system-programmable high-fanout enhanced zero delay clock generators designed for use in high performance communications and computing applications. The ispClock5610A provides up to 10 single-ended or five differential clock outputs, while the ispClock5620A provides up to 20 singleended or 10 differential clock outputs. Each pair of outputs may be independently configured to support separate I/O standards (LVDS, LVPECL, LVTTL, LVCMOS, SSTL, HSTL) and output frequency. In addition, each output provides independent programmable control of termination, slew-rate, and timing skew. All configuration information is stored on-chip in non-volatile E<sup>2</sup>CMOS memory.

The ispClock5600A's PLL and divider systems supports the synthesis of multiple clock frequencies derived from the reference input through the provision of programmable input and feedback dividers. A set of five post-PLL V-dividers provides additional flexibility by supporting the generation of five separate output frequencies. Loop feedback may be taken internally from the output of any of the five V-dividers, or externally through FBKA+/- or FBKB+/-pins.

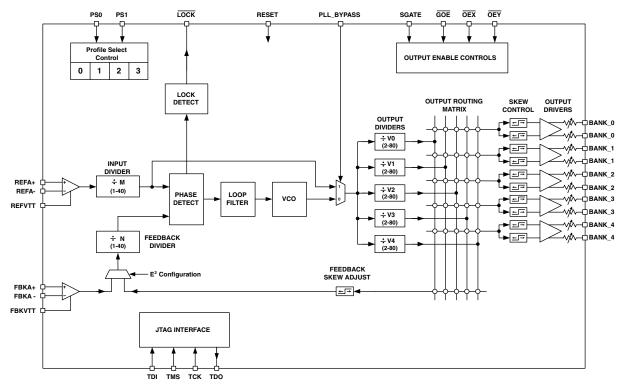

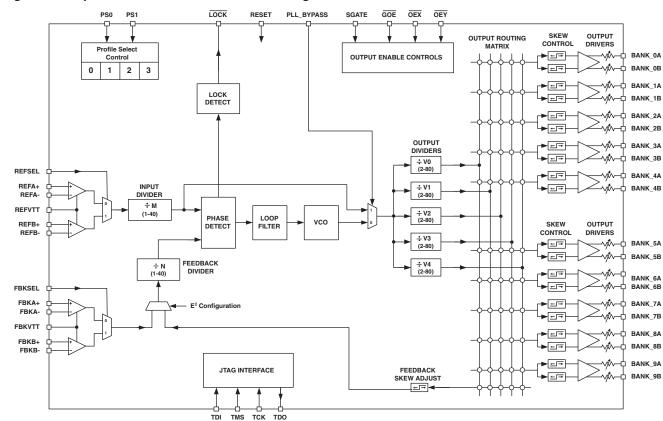

The core functions of all members of the ispClock5600A family are identical, the differences between devices being restricted to the number of inputs and outputs, as shown in the following table. Figures 1 and 2 show functional block diagrams of the ispClock5610A and ispClock5620A.

#### Table 1-1. ispClock5600A Family Members

| Device        | Ref. Input Pairs | Feedback Input Pairs | Clock Outputs |

|---------------|------------------|----------------------|---------------|

| ispClock5610A | 1                | 1                    | 10            |

| ispClock5620A | 2                | 2                    | 20            |

Figure 1-1. ispClock5610A Functional Block Diagram

Figure 1-2. ispClock5620A Functional Block Diagram

1-3

# **Absolute Maximum Ratings**

|                                                                           | ispClock5600A |

|---------------------------------------------------------------------------|---------------|

| Core Supply Voltage V <sub>CCD</sub>                                      | 0.5 to 5.5V   |

| PLL Supply Voltage V <sub>CCA</sub>                                       | 0.5 to 5.5V   |

| JTAG Supply Voltage V <sub>CCJ</sub>                                      | 0.5 to 5.5V   |

| Output Driver Supply Voltage V <sub>CCO</sub>                             | 0.5 to 4.5V   |

| Input Voltage                                                             | 0.5 to 4.5V   |

| Output Voltage <sup>1</sup>                                               | 0.5 to 4.5V   |

| Storage Temperature                                                       | 65 to 150°C   |

| Junction Temperature with power supplied                                  | 40 to 130°C   |

| 4 Million and the later and a standard and the later. The second state of |               |

1. When applied to an output when in high-Z condition

# **Recommended Operating Conditions**

|                      |                                   |                 | ispCloc | k5600A          |       |  |

|----------------------|-----------------------------------|-----------------|---------|-----------------|-------|--|

| Symbol               | Parameter                         | Conditions      | Min.    | Max.            | Units |  |

| V <sub>CCD</sub>     | Core Supply Voltage               |                 | 3.0     | 3.6             | V     |  |

| V <sub>CCJ</sub>     | JTAG I/O Supply Voltage           |                 | 2.25    | 3.6             | V     |  |

| V <sub>CCA</sub>     | Analog Supply Voltage             |                 | 3.0     | 3.6             | V     |  |

| V <sub>CCXSLEW</sub> | V <sub>CC</sub> Turn-on Ramp Rate | All supply pins | —       | 0.33            | V/µs  |  |

| т                    | Operating Junction Tomporature    | Commercial      | 0       | 130             | °C    |  |

| I JOP                | Operating Junction Temperature    | Industrial      | -40     | 130             |       |  |

| T <sub>A</sub>       | Ambient Operating Temperature     | Commercial      | 0       | 70 <sup>1</sup> | °C    |  |

|                      | Ambient Operating Temperature     | Industrial      | -40     | 85¹             |       |  |

1. Device power dissipation may also limit maximum ambient operating temperature.

# **Recommended Operating Conditions – V<sub>CCO</sub> vs. Logic Standard**

|        |                       |       | V <sub>CCO</sub> (V) |       |      | V <sub>REF</sub> (V) |      |                         | V <sub>TT</sub> (V)    |                         |

|--------|-----------------------|-------|----------------------|-------|------|----------------------|------|-------------------------|------------------------|-------------------------|

| Log    | ic Standard           | Min.  | Тур.                 | Max.  | Min. | Тур.                 | Max. | Min.                    | Тур.                   | Max.                    |

| LVTTL  |                       | 3.0   | 3.3                  | 3.6   | _    | —                    | _    | —                       | _                      | _                       |

| LVCMC  | DS 1.8V               | 1.71  | 1.8                  | 1.89  | _    | —                    |      | —                       | _                      | _                       |

| LVCMC  | DS 2.5V               | 2.375 | 2.5                  | 2.625 | —    | —                    | _    | —                       | _                      | _                       |

| LVCMC  | DS 3.3V               | 3.0   | 3.3                  | 3.6   | _    | —                    | _    | —                       | _                      | _                       |

| SSTL1. | .8                    | 1.71  | 1.8                  | 1.89  | 0.84 | 0.90                 | 0.95 | —                       | 0.5 x V <sub>CCO</sub> | _                       |

| SSTL2  | Class 1               | 2.375 | 2.5                  | 2.625 | 1.15 | 1.25                 | 1.35 | V <sub>REF</sub> - 0.04 | V <sub>REF</sub>       | V <sub>REF</sub> + 0.04 |

| SSTL3  | Class 1               | 3.0   | 3.3                  | 3.6   | 1.30 | 1.50                 | 1.70 | V <sub>REF</sub> - 0.05 | V <sub>REF</sub>       | V <sub>REF</sub> + 0.05 |

| HSTL C | Class 1               | 1.425 | 1.5                  | 1.575 | 0.68 | 0.75                 | 0.90 | —                       | 0.5 x V <sub>CCO</sub> | —                       |

| eHSTL  | Class 1               | 1.71  | 1.8                  | 1.89  | 0.84 | 0.90                 | 0.95 | —                       | 0.5 x V <sub>CCO</sub> | _                       |

| LVPEC  | L (Differential)      | 3.0V  | 3.3V                 | 3.6V  | _    | —                    | _    | —                       | _                      | _                       |

| LVDS   | $V_{\rm CCO} = 2.5 V$ | 2.375 | 2.5V                 | 2.625 | —    | —                    | —    | —                       | —                      | —                       |

|        | $V_{\rm CCO} = 3.3V$  | 3.0   | 3.3                  | 3.6   | —    | —                    | —    | —                       | _                      | —                       |

Note: '—' denotes  $V_{\mathsf{REF}}$  or  $V_{\mathsf{TT}}$  not applicable to this logic standard

## E<sup>2</sup>CMOS Memory Write/Erase Characteristics

| Parameter              | Conditions | Min. | Тур. | Max. | Units |

|------------------------|------------|------|------|------|-------|

| Erase/Reprogram Cycles |            | 1000 | —    | _    |       |

## **Performance Characteristics – Power Supply**

| Symbol           | Parameter                          | Conditions                                                               | Тур. | Max. | Units |

|------------------|------------------------------------|--------------------------------------------------------------------------|------|------|-------|

| 1                | Core Supply Current <sup>3</sup>   | ispClock5610A f <sub>VCO</sub> = 800MHz                                  | 110  | 125  | mA    |

| ICCD             |                                    | ispClock5620A f <sub>VCO</sub> = 800MHz                                  | 130  | 150  | mA    |

| I <sub>CCA</sub> | Analog Supply Current <sup>3</sup> | f <sub>VCO</sub> = 800MHz                                                | 5.5  | 7    | mA    |

|                  |                                    | V <sub>CCO</sub> = 1.8V <sup>1</sup> , LVCMOS, f <sub>OUT</sub> = 266MHz | 16   | 18   | mA    |

| 1                |                                    | $V_{CCO} = 2.5V^1$ , LVCMOS, $f_{OUT} = 266MHz$                          | 21   | 27   | mA    |

| ICCO             | (per Bank)                         | $V_{CCO} = 3.3V^1$ , LVCMOS, $f_{OUT} = 266MHz$                          | 27   | 38   | mA    |

|                  |                                    | $V_{CCO} = 3.3V^2$ , LVDS, f <sub>OUT</sub> = 400MHz                     | 8    | 10   | mA    |

|                  |                                    | $V_{CCJ} = 1.8V$                                                         |      | 300  | μΑ    |

| I <sub>CCJ</sub> | -                                  | $V_{CCJ} = 2.5V$                                                         |      | 400  | μΑ    |

|                  |                                    | $V_{CCJ} = 3.3V$                                                         |      | 400  | μA    |

1. Supply current consumed by each bank, both outputs active, 5pF load.

2. Supply current consumed by each bank,  $100\Omega,$  5pf differential load.

3. All unused REFCLK and feedbacks connected to ground.

# **DC Electrical Characteristics – Single-ended Logic**

|                   | V    | <sub>L</sub> (V)        | V <sub>IH</sub> (       | V)   |                          |                                      |                      |                      |

|-------------------|------|-------------------------|-------------------------|------|--------------------------|--------------------------------------|----------------------|----------------------|

| Logic Standard    | Min. | Max.                    | Min.                    | Max. | V <sub>OL</sub> Max. (V) | V <sub>OH</sub> Min. (V)             | l <sub>OL</sub> (mA) | l <sub>OH</sub> (mA) |

| LVTTL/LVCMOS 3.3V | -0.3 | 0.8                     | 2                       | 3.6  | 0.4                      | V <sub>CCO</sub> - 0.4               | 12 <sup>2, 3</sup>   | -12 <sup>2, 3</sup>  |

| LVCMOS 1.8V       | -0.3 | 0.68                    | 1.07                    | 3.6  | 0.4                      | V <sub>CCO</sub> - 0.4               | 12 <sup>2, 3</sup>   | -12 <sup>2, 3</sup>  |

| LVCMOS 2.5V       | -0.3 | 0.7                     | 1.7                     | 3.6  | 0.4                      | V <sub>CCO</sub> - 0.4               | 12 <sup>2, 3</sup>   | -12 <sup>2, 3</sup>  |

| SSTL2 Class 1     | -0.3 | V <sub>REF</sub> - 0.18 | V <sub>REF</sub> + 0.18 | 3.6  | 0.54 <sup>2</sup>        | V <sub>CCO</sub> - 0.81 <sup>1</sup> | 7.6                  | -7.6                 |

| SSTL3 Class 1     | -0.3 | V <sub>REF</sub> - 0.2  | V <sub>REF</sub> + 0.2  | 3.6  | 0.9 <sup>2</sup>         | V <sub>CCO</sub> - 1.3 <sup>1</sup>  | 8                    | -8                   |

| HSTL Class 1      | -0.3 | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6  | 0.43                     | V <sub>CCO</sub> - 0.4 <sup>2</sup>  | 8                    | -8                   |

| eHSTL Class 1     | -0.3 | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | 3.6  | 0.4 <sup>3</sup>         | V <sub>CCO</sub> - 0.4 <sup>2</sup>  | 8                    | -8                   |

1. Specified for  $40 \Omega$  internal series output termination.

2. Specified for  $\approx 20\Omega$  internal series output termination, fast slew rate setting.

3. For slower slew rate setting  $I_{OH}$ ,  $I_{OL}$  = 8mA.

# **DC Electrical Characteristics – LVDS**

| Symbol           | Parameter                                 | Conditions                                          | Min.                | Тур.  | Max.  | Units |

|------------------|-------------------------------------------|-----------------------------------------------------|---------------------|-------|-------|-------|

| V.               | Common Mode Input Voltage                 | V <sub>THD</sub> ≤ 100mV                            | V <sub>THD</sub> /2 | _     | 2.0   | V     |

| V <sub>ICM</sub> | ICM Common mode input voltage             | V <sub>THD</sub> ≤ 150mV                            | $V_{THD}/2$         |       | 2.325 | V     |

| V <sub>THD</sub> | Differential Input Threshold              |                                                     | ±100                | _     | _     | mV    |

| V <sub>IN</sub>  | Input Voltage                             |                                                     | 0                   | _     | 2.4   | V     |

| V <sub>OH</sub>  | Output High Voltage                       | R <sub>T</sub> = 100Ω                               | _                   | 1.375 | 1.60  | V     |

| V <sub>OL</sub>  | Output Low Voltage                        | R <sub>T</sub> = 100Ω                               | 0.9                 | 1.03  | —     | V     |

| V <sub>OD</sub>  | Output Voltage Differential               | R <sub>T</sub> = 100Ω                               | 250                 | 400   | 480   | mV    |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> Between H and L |                                                     | _                   | _     | 50    | mV    |

| V <sub>OS</sub>  | Output Voltage Offset                     | Common Mode Output Voltage                          | 1.10                | 1.20  | 1.375 | V     |

| $\Delta V_{OS}$  | Change in V <sub>OS</sub> Between H and L |                                                     | _                   | _     | 50    | mV    |

| I <sub>SA</sub>  | Output Short Circuit Current              | V <sub>OD</sub> = 0V, Outputs Shorted to GND        | _                   | _     | 24    | mA    |

| I <sub>SAB</sub> | Output Short Circuit Current              | V <sub>OD</sub> = 0V, Outputs Shorted to Each Other | _                   | —     | 12    | mA    |

|                  |                                           |                                                     |                     |       |       |       |

# **DC Electrical Characteristics – Differential LVPECL**

| Symbol                                          | Parameter                         | Test Conditions                | Min.                    | Тур. | Max.                    | Units |

|-------------------------------------------------|-----------------------------------|--------------------------------|-------------------------|------|-------------------------|-------|

| VIH                                             | Input Voltage High                | V <sub>CCD</sub> = 3.0 to 3.6V | V <sub>CCD</sub> - 1.17 |      | V <sub>CCD</sub> - 0.88 | v     |

| <sup>v</sup> IH                                 |                                   | V <sub>CCD</sub> = 3.3V        | 2.14                    |      | 2.42                    | v     |

| V.                                              | Input Voltage Low                 | V <sub>CCD</sub> = 3.0 to 3.6V | V <sub>CCD</sub> - 1.81 |      | V <sub>CCD</sub> - 1.48 | v     |

| <sup>v</sup> IL                                 | V <sub>IL</sub> Input Voltage Low | $V_{CCD} = 3.3V$               | 1.49                    |      | 1.83                    | v     |

| V.                                              | Output High Voltage <sup>1</sup>  | V <sub>CCO</sub> = 3.0 to 3.6V | V <sub>CCO</sub> - 1.07 |      | V <sub>CCO</sub> - 0.88 | v     |

| V <sub>OH</sub>                                 |                                   | $V_{CCO} = 3.3V$               | 2.23                    |      | 2.42                    | v     |

| V <sub>OI</sub> Output Low Voltage <sup>1</sup> |                                   | V <sub>CCO</sub> = 3.0 to 3.6V | V <sub>CCO</sub> - 1.81 |      | V <sub>CCO</sub> - 1.62 | v     |

| V <sub>OL</sub>                                 |                                   | $V_{\rm CCO} = 3.3 V$          | 1.49                    | _    | 1.68                    |       |

1.  $100\Omega$  differential termination.

# **Electrical Characteristics – Differential SSTL18**

| Symbol             | Parameter                                  | Conditions                      | Min.                    | Тур. | Max.                    | Units |

|--------------------|--------------------------------------------|---------------------------------|-------------------------|------|-------------------------|-------|

| V <sub>CCO</sub>   | Output Supply Voltage                      |                                 | 1.71                    | 1.8  | 1.89                    | V     |

| V <sub>IL</sub>    | Low-Logic Level Input Voltage              |                                 |                         |      | 0.61                    | V     |

| V <sub>IH</sub>    | Hi Logic Level Input Voltage               |                                 | 1.17                    |      |                         | V     |

| V <sub>SWING</sub> | AC Differential Output Voltage             |                                 | 0.64                    |      |                         | V     |

| V <sub>IX</sub>    | Input Pair Differential Crosspoint Voltage |                                 | V <sub>REF</sub> -175mV |      | V <sub>REF</sub> +175mV | V     |

| ТСКД               | Clock Duty Cycle                           | Load Conditions<br>(Figure 1-6) | 45                      |      | 55                      | %     |

# **Electrical Characteristics – Differential SSTL2**

| Symbol                 | Parameter                                  | Conditions                      | Min.                      | Тур. | Max.                      | Units |

|------------------------|--------------------------------------------|---------------------------------|---------------------------|------|---------------------------|-------|

| V <sub>CCO</sub>       | Output Supply Voltage                      |                                 | 2.375                     | 2.5  | 2.625                     | V     |

| V <sub>SWING(DC)</sub> | DC Differential Input Voltage Swing        |                                 | -0.03                     |      | 3.225                     | V     |

| V <sub>SWING(AC)</sub> | AC Input Differential Voltage              |                                 | 0.62                      |      | 3.225                     | V     |

| V <sub>IX</sub>        | Input Pair Differential Crosspoint Voltage |                                 | V <sub>REF</sub> - 200 mV |      | V <sub>REF</sub> + 200 mV | V     |

| ТСКД                   | Clock Duty Cycle                           | Load Conditions<br>(Figure 1-6) | 45                        |      | 55                        | %     |

# **Electrical Characteristics – Differential HSTL**

| Symbol                 | Parameter                                     | Conditions                      | Min   | Тур | Max              | Units |

|------------------------|-----------------------------------------------|---------------------------------|-------|-----|------------------|-------|

| V <sub>CCO</sub>       | Output Supply Voltage                         |                                 | 1.425 | 1.5 | 1.575            | V     |

| V <sub>SWING(DC)</sub> | DC Differential Input Voltage Swing           |                                 | -0.03 |     | V <sub>CCD</sub> | V     |

| V <sub>SWING(AC)</sub> | AC Input Differential Voltage                 |                                 | 0.4   |     | V <sub>CCD</sub> | V     |

| V <sub>IX</sub>        | Input Pair Differential Crosspoint<br>Voltage |                                 | 0.68  |     | 0.9              | V     |

| ТСКД                   | Clock Duty Cycle                              | Load Conditions<br>(Figure 1-6) | 45    |     | 55               | %     |

# **Electrical Characteristics – Differential eHSTL**

| Symbol                 | Parameter                                  | Conditions                      | Min   | Тур | Max              | Units |

|------------------------|--------------------------------------------|---------------------------------|-------|-----|------------------|-------|

| V <sub>CCO</sub>       | Output Supply Voltage                      |                                 | 1.7   | 1.8 | 1.9              | V     |

| V <sub>SWING(DC)</sub> | DC Differential Input Voltage Swing        |                                 | -0.03 |     | V <sub>CCD</sub> | V     |

| V <sub>SWING(AC)</sub> | AC Input Differential Voltage              |                                 | 0.4   |     | V <sub>CCD</sub> | V     |

| V <sub>IX</sub>        | Input Pair Differential Crosspoint Voltage |                                 | 0.68  |     | 0.9              | V     |

| ТСКД                   | Clock Duty Cycle                           | Load Conditions<br>(Figure 1-6) | 45    |     | 55               | %     |

# **DC Electrical Characteristics – Input/Output Loading**

| Symbol           | Parameter               | Conditions    | Min. | Тур. | Max. | Units |

|------------------|-------------------------|---------------|------|------|------|-------|

| I <sub>LK</sub>  | Input Leakage           | Note 1        |      | _    | ±10  | μA    |

| I <sub>PU</sub>  | Input Pull-up Current   | Note 2        | _    | 80   | 120  | μA    |

| I <sub>PD</sub>  | Input Pull-down Current | Note 3        | _    | 120  | 150  | μA    |

| I <sub>OLK</sub> | Tristate Leakage Output | Note 4        |      | _    | ±10  | μA    |

| C <sub>IN</sub>  | Input Capacitance       | Notes 2, 3, 5 |      | 8    | 10   | pF    |

|                  |                         | Note 6        |      | 13.5 | 15   | pF    |

1. Applies to clock reference inputs when termination 'open'.

2. Applies to TDI, TMS inputs.

3. Applies to REFSEL, PS0, PS1, GOE, SGATE and PLL\_BYPASS, FBKSEL, OEX, OEY.

4. Applies to all logic types when in tristated mode.

5. Applies to OEX, OEY, TCK, RESET inputs.

6. Applies to REFA+, REFA-, REFB+, REFB-, FBKA+, FBKA-, FBKB+, FBKB-.

# Switching Characteristics – Timing Adders for I/O Modes

| Adder Type                                 | Description                                       | Min. | Тур. | Max. | Units |

|--------------------------------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>IOI</sub> Input Adders <sup>2</sup> |                                                   |      |      |      |       |

| LVTTL_in                                   | Using LVTTL Standard                              | 0    | 0    | 0    | ps    |

| LVCMOS18_in                                | Using LVCMOS 1.8V Standard                        | -99  | 80   | 315  | ps    |

| LVCMOS25_in                                | Using LVCMOS 2.5V Standard                        | 0    | 0    | 0    | ps    |

| LVCMOS33_in                                | Using LVCMOS 3.3V Standard                        | 0    | 0    | 0    | ps    |

| SSTL18_in                                  | Using SSTL18 Standard                             | 10   | 360  | 642  | ps    |

| SSTL2_in                                   | Using SSTL2 Standard                              | 64   | 420  | 679  | ps    |

| SSTL3_in                                   | Using SSTL3 Standard                              | 34   | 380  | 630  | ps    |

| HSTL_in                                    | Using HSTL Standard                               | 231  | 672  | 1064 | ps    |

| eHSTL_in                                   | Using eHSTL Standard                              | 128  | 514  | 846  | ps    |

| LVDS_in                                    | Using LVDS Standard                               | 118  | 426  | 651  | ps    |

| LVPECL_in                                  | Using LVPECL Standard                             | 201  | 593  | 937  | ps    |

| t <sub>IOO</sub> Output Adders             | 1, 3                                              |      |      |      |       |

| LVTTL_out                                  | Output Configured as LVTTL Buffer                 | 116  | 395  | 553  | ps    |

| LVCMOS18_out                               | Output Configured as LVCMOS 1.8V Buffer           | 155  | 510  | 730  | ps    |

| LVCMOS25_out                               | Output Configured as LVCMOS 2.5V Buffer           | 124  | 387  | 592  | ps    |

| LVCMOS33_out                               | Output Configured as LVCMOS 3.3V Buffer           | 116  | 395  | 553  | ps    |

| SSTL2_out                                  | Output Configured as SSTL2 Buffer                 | -109 | 66   | 209  | ps    |

| SSTL3_out                                  | Output Configured as SSTL3 Buffer                 | -97  | 78   | 242  | ps    |

| SSTL18_out_diff                            | Output Configured as SSTL18 Buffer (Differential) | -153 | 41   | 228  | ps    |

| HSTL_out_diff                              | Output Configured as HSTL Buffer (Differential)   | -4   | 180  | 402  | ps    |

| eHSTL_out_diff                             | Output Configured as eHSTL Buffer (Differential)  | -16  | 173  | 375  | ps    |

| SSTL_out_diff                              | Output Configured as SSTL2 Buffer (Differential)  | -146 | 83   | 305  | ps    |

| LVDS_out                                   | Output Configured as LVDS Buffer                  | 0    | 0    | 0    | ps    |

| LVPECL_out                                 | Output Configured as LVPECL Buffer                | -187 | -17  | 57   | ps    |

| t <sub>IOS</sub> Output Slew Ra            | te Adders <sup>1</sup>                            |      |      |      |       |

| Slew_1                                     | Output Slew_1 (Fastest)                           | _    | 0    |      | ps    |

| Slew_2                                     | Output Slew_2                                     | —    | 330  | —    | ps    |

| Slew_3                                     | Output Slew_3                                     | — —  | 660  | —    | ps    |

| Slew_4                                     | Output Slew_4 (Slowest)                           | _    | 1320 | _    | ps    |

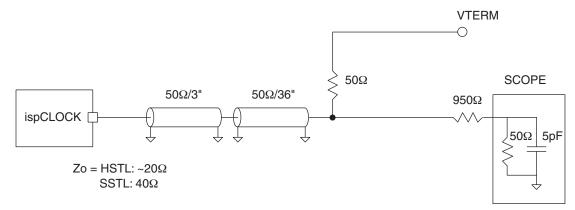

1. Measured under standard output load conditions. See Figures 1-3-1-5.

2. All input adders referenced to LVCMOS33.

3. All output adders referenced to LVDS.

# Output Rise and Fall Times – Typical Values<sup>1, 2</sup>

|                     | Slew 1 (       | (Fastest)      | Sle            | w 2            | Slew 3         |                | Slew 4 (Slowest) |                |       |

|---------------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------|----------------|-------|

| Output Type         | t <sub>R</sub> | t <sub>F</sub> | t <sub>R</sub> | t <sub>F</sub> | t <sub>R</sub> | t <sub>F</sub> | t <sub>R</sub>   | t <sub>F</sub> | Units |

| LVTTL               | 0.54           | 0.76           | 0.60           | 0.87           | 0.78           | 1.26           | 1.05             | 1.88           | ns    |

| LVCMOS 1.8V         | 0.75           | 0.69           | 0.88           | 0.78           | 0.83           | 1.11           | 1.20             | 1.68           | ns    |

| LVCMOS 2.5V         | 0.57           | 0.69           | 0.65           | 0.78           | 0.99           | 0.98           | 1.65             | 1.51           | ns    |

| LVCMOS 3.3V         | 0.55           | 0.77           | 0.60           | 0.87           | 0.78           | 1.26           | 1.05             | 1.88           | ns    |

| SSTL18              | 0.55           | 0.40           | —              | —              | _              | —              | —                | —              | ns    |

| SSTL2               | 0.50           | 0.40           | —              | _              | _              | —              | —                |                | ns    |

| SSTL3               | 0.50           | 0.45           | —              | _              | _              | —              | —                |                | ns    |

| HSTL                | 0.60           | 0.45           | —              | —              | _              | —              | —                | —              | ns    |

| eHSTL               | 0.55           | 0.40           | —              | —              | —              | —              | —                | —              | ns    |

| LVDS <sup>3</sup>   | 0.25           | 0.20           | —              | —              | —              | —              | —                | —              | ns    |

| LVPECL <sup>3</sup> | 0.20           | 0.20           | —              | —              | —              | —              | —                | —              | ns    |

1. See Figures 1-3-1-5 for test conditions.

2. Measured between 20% and 80% points.

3. Only the 'fastest' slew rate is available in LVDS and LVPECL modes.

# **Output Test Loads**

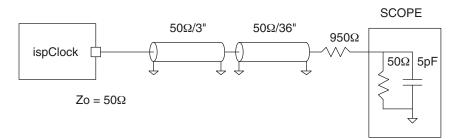

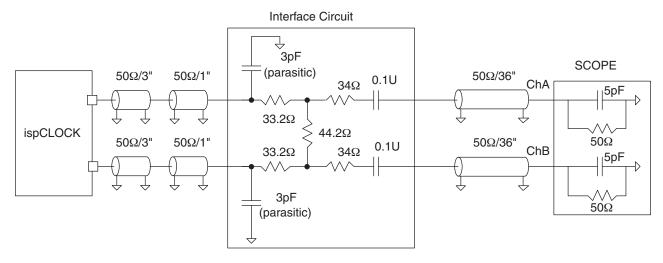

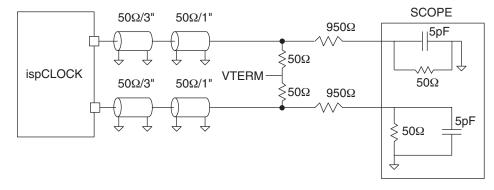

Figures 1-3-1-5 show the equivalent termination loads used to measure rise/fall times, output timing adders and other selected parameters as noted in the various tables of this data sheet.

## Figure 1-3. CMOS Termination Load

Figure 1-6. Differential HSTL/SSTL Termination Load

# Programmable Input and Output Termination Characteristics

| Symbol          | Parameter                      | Conditions              | V <sub>CCO</sub> Voltage | Min. | Тур. | Max. | Units |

|-----------------|--------------------------------|-------------------------|--------------------------|------|------|------|-------|

|                 |                                | Rin=40 $\Omega$ setting |                          | 36   | _    | 44   |       |

|                 |                                | Rin=45 $\Omega$ setting |                          | 40.5 | —    | 49.5 |       |

|                 |                                | Rin=50 $\Omega$ setting |                          | 45   | —    | 55   |       |

| R <sub>IN</sub> | Input Resistance               | Rin=55 $\Omega$ setting |                          | 49.5 | —    | 60.5 | Ω     |

|                 |                                | Rin=60 $\Omega$ setting |                          | 54   | —    | 66   |       |

|                 |                                | Rin=65 $\Omega$ setting |                          | 59   | —    | 71.5 |       |

|                 |                                | Rin=70 $\Omega$ setting |                          | 61   | —    | 77   |       |

|                 |                                |                         | VCCO=3.3V                | _    | 15   | —    |       |

|                 |                                | Rout≈20Ω setting        | VCCO=2.5V                | _    | 15   | —    |       |

|                 |                                | noui≈∠os₂ seiiiny       | VCCO=1.8V                | _    | 16   | —    |       |

|                 |                                |                         | VCCO=1.5V                | _    | 14   | —    |       |

|                 |                                |                         | VCCO=3.3V                | -9%  | 40   | 9%   |       |

|                 |                                | Rout≈40Ω setting        | VCCO=2.5V                | -11% | 40   | 11%  |       |

|                 |                                |                         | VCCO=1.8V                | -13% | 41   | 13%  |       |

|                 |                                |                         | VCCO=3.3V                | -10% | 45   | 10%  |       |

|                 |                                | Rout≈45Ω setting        | VCCO=2.5V                | -12% | 45   | 12%  | Ω     |

|                 |                                |                         | VCCO=1.8V                | -14% | 48   | 14%  |       |

|                 |                                |                         | VCCO=3.3V                | -8%  | 50   | 8%   |       |

|                 |                                | Rout≈50Ω setting        | VCCO=2.5V                | -9%  | 50   | 9%   |       |

| Rout            | Output Resistance <sup>1</sup> |                         | VCCO=1.8V                | -13% | 54   | 13%  |       |

|                 |                                |                         | VCCO=3.3V                | -9%  | 55   | 9%   |       |

|                 |                                | Rout≈55Ω setting        | VCCO=2.5V                | -11% | 55   | 11%  |       |

|                 |                                |                         | VCCO=1.8V                | -13% | 59   | 13%  |       |

|                 |                                |                         | VCCO=3.3V                | -8%  | 59   | 8%   |       |

|                 |                                | Rout≈60Ω setting        | VCCO=2.5V                | -9%  | 59   | 9%   |       |

|                 |                                |                         | VCCO=1.8V                | -14% | 63   | 14%  |       |

|                 |                                | Rout≈65Ω setting        | VCCO=3.3V                | -8%  | 65   | 8%   | 1     |

|                 |                                |                         | VCCO=2.5V                | -9%  | 64   | 9%   |       |

|                 |                                |                         | VCCO=1.8V                | -13% | 69   | 13%  | -     |

|                 |                                |                         | VCCO=3.3V                | -9%  | 72   | 9%   |       |

|                 |                                | Rout≈70Ω setting        | VCCO=2.5V                | -10% | 70   | 10%  |       |

|                 |                                |                         | VCCO=1.8V                | -12% | 74   | 12%  |       |

1. Guaranteed by characterization.

# **Performance Characteristics – PLL**

| Symbol                                        | Parameter                                                         | Cond                                                                                                      | litions                         | Min. | Тур. | Max. | Units              |

|-----------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------|------|------|------|--------------------|

| f <sub>REF,</sub> f <sub>FBK</sub>            | Reference and feedback input frequency range                      |                                                                                                           |                                 | 8    |      | 400  | MHz                |

| t <sub>CLOCKHI,</sub><br>t <sub>CLOCKLO</sub> | Reference and feedback input<br>clock HIGH and LOW times          | M-Divider and N-D bypassed.                                                                               | ivider not                      | 1.25 |      |      | ns                 |

| t <sub>rinp,</sub><br>t <sub>finp</sub>       | Reference and feedback input rise and fall times                  | Measured between levels                                                                                   | 1 20% and 80%                   |      |      | 5    | ns                 |

| M <sub>DIV</sub>                              | M-divider range                                                   |                                                                                                           |                                 | 1    |      | 40   |                    |

| N <sub>DIV</sub>                              | N-Divider range                                                   |                                                                                                           |                                 | 1    |      | 40   |                    |

| f <sub>PFD</sub>                              | Phase detector input frequency range <sup>2</sup>                 |                                                                                                           |                                 | 8    |      | 400  | MHz                |

| f <sub>VCO</sub>                              | VCO operating frequency                                           |                                                                                                           |                                 | 320  |      | 800  | MHz                |

| V <sub>DIV</sub>                              | Output Divider range                                              | Even integer values                                                                                       | s only                          | 2    |      | 80   |                    |

|                                               |                                                                   | Fine Skew Mode,                                                                                           | All differential options        | 4    |      | 400  | MHz                |

| f <sub>оит</sub>                              | Output frequency range <sup>1</sup>                               | f <sub>VCO</sub> = 800MHz                                                                                 | All single-ended options        | 4    |      | 266  | MHz                |

|                                               |                                                                   | Coarse Skew Mode,<br>f <sub>VCO</sub> = 800MHz                                                            |                                 | 2.5  |      | 200  | MHz                |

| t <sub>JIT</sub> (cc)                         | Output adjacent-cycle jitter <sup>6</sup><br>(1000 cycle sample)  | f <sub>PFD</sub> ≥ 100MHz                                                                                 |                                 |      |      | 70   | ps (p-p)           |

| t <sub>JIT</sub> (per)                        | Output period jitter <sup>6</sup><br>(10000 cycle sample)         | f <sub>PFD</sub> ≥ 100MHz                                                                                 |                                 |      |      | 12   | ps (RMS)           |

| t <sub>JIT(</sub> ∳)                          | Reference clock to output jitter <sup>6</sup> (2000 cycle sample) | f <sub>PFD</sub> ≥ 100MHz                                                                                 |                                 |      |      | 50   | ps (RMS)           |

| tφ                                            | Static phase offset <sup>5</sup>                                  |                                                                                                           |                                 | -100 |      | 200  | ps                 |

| t <sub>DELAY</sub>                            | Reference clock to output delay                                   | Internal feedback n                                                                                       | node <sup>4</sup>               |      | 2.25 |      | ns                 |

| DC                                            | Output duty cycle                                                 | Output type LVCM0<br>f <sub>OUT</sub> >100 MHz                                                            | OS 3.3V³                        | 45   |      | 55   | %                  |

| t <sub>PDBY-</sub>                            | Reference clock to output                                         | MINO                                                                                                      | Input: LVPECL<br>Output: LVPECL | 6.2  |      | 8.8  | ns                 |

| PASS                                          | propagation delay                                                 | M=1, V=2                                                                                                  | Input: LVCMOS<br>Output: LVCMOS | 6    |      | 8.25 | ns                 |

|                                               |                                                                   | From Power-up event                                                                                       |                                 |      | 150  |      | μs                 |

| LOCK                                          | PLL lock time                                                     | From Reset event                                                                                          |                                 |      | 15   |      | μs                 |

|                                               | DLL releak time                                                   | To same reference frequency                                                                               |                                 |      | 15   |      | μs                 |

| RELOCK                                        | PLL relock time                                                   | To different frequer                                                                                      | псу                             |      | 150  |      | μs                 |

| PSR                                           | Power supply rejection, period jitter vs. power supply noise      | $f_{IN} = f_{OUT} = 100MHz$<br>$V_{CCA} = V_{CCD} = V_{CCO}$ modulated with<br>100kHz sinusoidal stimulus |                                 |      | 0.05 |      | ps(RMS)<br>mV(p-p) |

1. In PLL Bypass mode (PLL\_BYPASS = HIGH), output will support frequencies down to 0Hz (divider chain is a fully static design).

2. Dividers should be set so that they provide the phase detector with signals of 8MHz or greater for loop stability.

3. See Figures 1-3-1-5 for output loads.

4. Input and outputs LVPECL mode

5. Inserted feedback loop delay < 7ns

6. Measured with  $f_{OUT}$  = 100MHz,  $f_{VCO}$  = 600MHz, input and output interface set to LVPECL.

## **Timing Specifications**

## **Skew Matching**

| Symbol            | Parameter          | Conditions                                                                    |   | Тур. | Max. | Units |

|-------------------|--------------------|-------------------------------------------------------------------------------|---|------|------|-------|

| t <sub>SKEW</sub> | Output-output Skew | Between any two identically configured and loaded outputs regardless of bank. | _ | _    | 50   | ps    |

## **Programmable Skew Control**

| Symbol               | Parameter                              | Conditions                                   | Min. | Тур.  | Max. | Units |

|----------------------|----------------------------------------|----------------------------------------------|------|-------|------|-------|

|                      |                                        | Fine Skew Mode, f <sub>VCO</sub> = 320 MHz   | _    | 5.86  | _    |       |

|                      | Skow Control Pango <sup>1</sup>        | Fine Skew Mode, f <sub>VCO</sub> = 800 MHz   | _    | 2.34  | —    | ns    |

| <sup>t</sup> SKRANGE | KRANGE Skew Control Range <sup>1</sup> | Coarse Skew Mode, f <sub>VCO</sub> = 320 MHz | _    | 11.72 | _    | 115   |

|                      |                                        | Coarse Skew Mode, f <sub>VCO</sub> = 800 MHz | _    | 4.68  | —    |       |

| SK <sub>STEPS</sub>  | Skew Steps per range                   |                                              | —    | 16    | —    |       |

|                      |                                        | Fine Skew Mode, f <sub>VCO</sub> = 320 MHz   | _    | 390   | _    |       |

| +                    | Skew Step Size <sup>2</sup>            | Fine Skew Mode, f <sub>VCO</sub> = 800 MHz   | _    | 156   | —    | ne    |

| ISKSTEP              | Skew Step Size                         | Coarse Skew Mode, f <sub>VCO</sub> = 320 MHz | _    | 780   | _    | ps    |

|                      |                                        | Coarse Skew Mode, f <sub>VCO</sub> = 800 MHz | _    | 312   | _    |       |

| t                    | Skew Time Error <sup>3</sup>           | Fine skew mode                               | _    | 30    | —    | ps    |

| <sup>t</sup> SKERR   |                                        | Coarse skew mode                             |      | 50    | _    | ps ps |

1. Skew control range is a function of VCO frequency ( $f_{VCO}$ ). In fine skew mode  $T_{SKRANGE} = 15/(8 \times f_{VCO})$ . In coarse skew mode  $T_{SKRANGE} = 15/(4 \times f_{VCO})$ .

2. Skew step size is a function of VCO frequency ( $f_{VCO}$ ). In fine skew mode  $T_{SKSTEP} = 1/(8 \text{ x } f_{VCO})$ . In coarse skew mode  $T_{SKSTEP} = 1/(4 \text{ x } f_{VCO})$ .

3. Only applicable to outputs with non-zero skew settings.

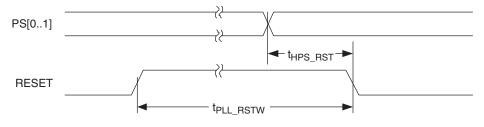

## **Control Functions**

| Symbol                | Parameter                                             | Conditions | Min. | Тур. | Max. | Units               |

|-----------------------|-------------------------------------------------------|------------|------|------|------|---------------------|

| t <sub>DIS/OE</sub>   | Delay Time, OEX or OEY to Output Disabled/<br>Enabled |            |      | 10   | 20   | ns                  |

| t <sub>DIS/GOE</sub>  | Delay Time, GOE to Output Disabled/Enabled            |            |      | 10   | 20   | ns                  |

| t <sub>SUSGATE</sub>  | Setup Time, SGATE to Output Clock Start/<br>Stop      |            | 3    | _    | _    | cycles <sup>1</sup> |

| t <sub>PLL_RSTW</sub> | PLL Reset Pulse Width <sup>2</sup>                    |            | 1    | —    |      | ms                  |

| t <sub>RSTW</sub>     | Logic Reset Pulse Width <sup>3</sup>                  |            | 20   | _    |      | ns                  |

| t <sub>HPS_RST</sub>  | Hold time for RESET past change in PS[01]             |            | 20   | —    | —    | ns                  |

1. Output clock cycles for the particular output being controlled.

2. Will completely reset PLL.

3. Will only reset digital logic.

## Figure 1-7. RESET and Profile Select Timing

# Timing Specifications (Cont.)

## **Boundary Scan Logic**

| Symbol               | Parameter                                                           | Min. | Max. | Units |

|----------------------|---------------------------------------------------------------------|------|------|-------|

| t <sub>BTCP</sub>    | TCK (BSCAN Test) Clock Cycle                                        | 40   | _    | ns    |

| t <sub>BTCH</sub>    | TCK (BSCAN Test) Pulse Width High                                   | 20   | _    | ns    |

| t <sub>BTCL</sub>    | TCK (BSCAN Test) Pulse Width Low                                    | 20   | —    | ns    |

| t <sub>BTSU</sub>    | TCK (BSCAN Test) Setup Time                                         | 8    | —    | ns    |

| t <sub>BTH</sub>     | TCK (BSCAN Test) Hold Time                                          | 10   | —    | ns    |

| t <sub>BRF</sub>     | TCK (BSCAN Test) Rise and Fall Rate                                 | 50   | —    | mV/ns |

| t <sub>BTCO</sub>    | TAP Controller Falling Edge of Clock to Valid Output                | _    | 10   | ns    |

| t <sub>BTOZ</sub>    | TAP Controller Falling Edge of Clock to Data Output Disable         | _    | 10   | ns    |

| t <sub>BTVO</sub>    | TAP Controller Falling Edge of Clock to Data Output Enable          | _    | 10   | ns    |

| t <sub>BVTCPSU</sub> | BSCAN Test Capture Register Setup Time                              | 8    | _    | ns    |

| t <sub>втсрн</sub>   | BSCAN Test Capture Register Hold Time                               | 10   | —    | ns    |

| t <sub>BTUCO</sub>   | BSCAN Test Update Register, Falling Edge of Clock to Valid Output   | _    | 25   | ns    |

| t <sub>BTUOZ</sub>   | BSCAN Test Update Register, Falling Edge of Clock to Output Disable | —    | 25   | ns    |

| t <sub>BTUOV</sub>   | BSCAN Test Update Register, Falling Edge of Clock to Output Enable  | _    | 25   | ns    |

## JTAG Interface and Programming Mode

| Symbol              | Parameter                            | Condition | Min. | Тур. | Max. | Units |

|---------------------|--------------------------------------|-----------|------|------|------|-------|

| f <sub>MAX</sub>    | Maximum TCK Clock Frequency          |           | —    | _    | 25   | MHz   |

| t <sub>СКН</sub>    | TCK Clock Pulse Width, High          |           | 20   | _    | _    | ns    |

| t <sub>CKL</sub>    | TCK Clock Pulse Width, Low           |           | 20   | _    | _    | ns    |

| t <sub>ISPEN</sub>  | Program Enable Delay Time            |           | 15   |      |      | μs    |

| t <sub>ISPDIS</sub> | Program Disable Delay Time           |           | 30   | _    |      | μs    |

| t <sub>HVDIS</sub>  | High Voltage Discharge Time, Program |           | 30   | _    | _    | μs    |

| t <sub>HVDIS</sub>  | High Voltage Discharge Time, Erase   |           | 200  |      |      | μs    |

| t <sub>CEN</sub>    | Falling Edge of TCK to TDO Active    |           | —    | _    | 15   | ns    |

| t <sub>CDIS</sub>   | Falling Edge of TCK to TDO Disable   |           | —    |      | 15   | ns    |

| t <sub>SU1</sub>    | Setup Time                           |           | 8    |      |      | ns    |

| t <sub>H</sub>      | Hold Time                            |           | 10   | _    |      | ns    |

| t <sub>CO</sub>     | Falling Edge of TCK to Valid Output  |           | —    | _    | 15   | ns    |

| t <sub>PWV</sub>    | Verify Pulse Width                   |           | 30   |      |      | μs    |

| t <sub>PWP</sub>    | Programming Pulse Width              |           | 20   | _    | _    | ms    |

| t <sub>BEW</sub>    | Bulk Erase Pulse Width               |           | 200  |      |      | ms    |

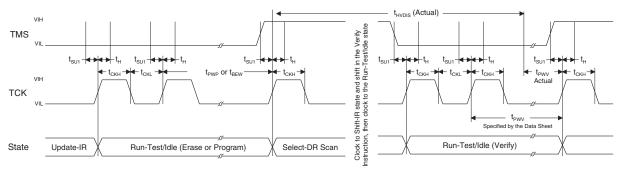

## **Timing Diagrams**

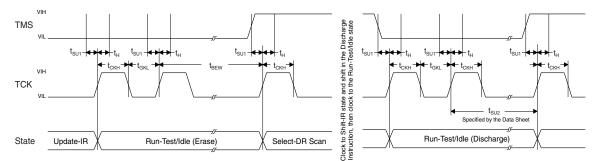

Figure 1-8. Erase (User Erase or Erase All) Timing Diagram

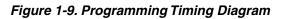

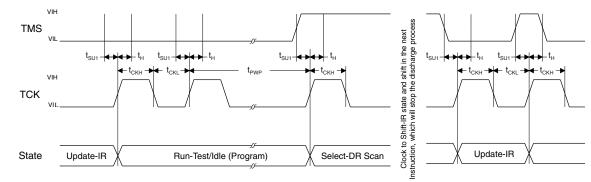

Figure 1-10. Verify Timing Diagram

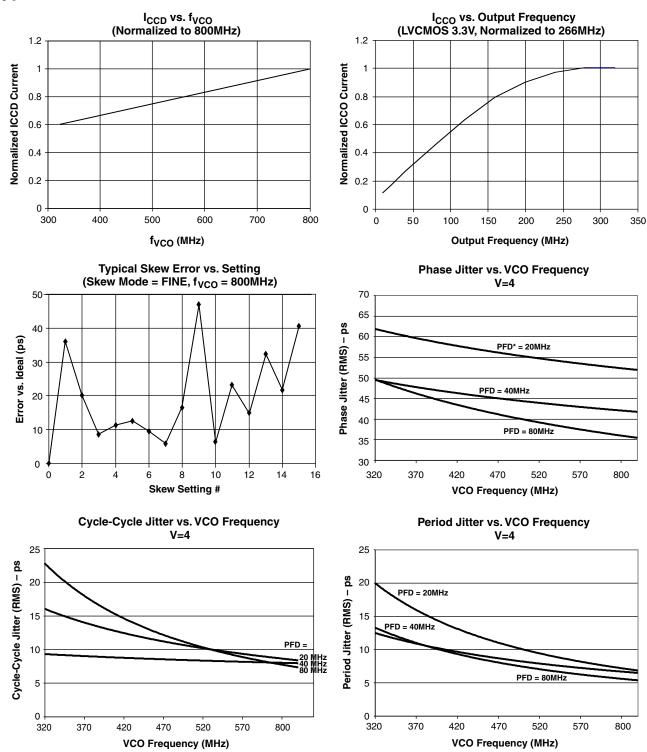

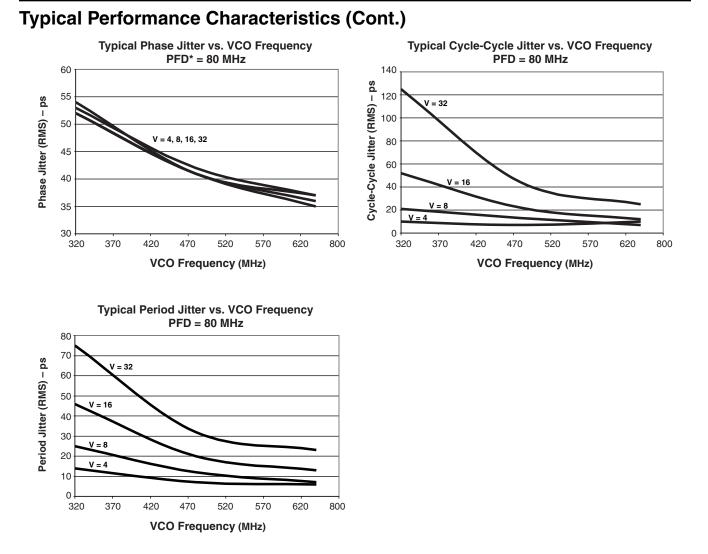

## **Typical Performance Characteristics**

\*PFD = Phase/Frequency Detector

\*PFD = Phase/Frequency Detector

# **Detailed Description**

## PLL Subsystem

The ispClock5600A provides an integral phase-locked-loop (PLL) which may be used to generate output clock signals at lower, higher, or the same frequency as a user-supplied input reference signal. The core functions of the PLL are an edge-sensitive phase detector, a programmable loop filter, and a high-speed voltage-controlled oscillator (VCO). Additionally, a set of programmable input, output and feedback dividers (M, N, V[1..5]) is provided to support the synthesis of different output frequencies.

## Phase/Frequency Detector

The ispClock5600A provides an edge-sensitive phase/frequency detector (PFD), which means that the device will function properly over a wide range of input clock reference duty cycles. It is only necessary that the input reference clock meet specified minimum HIGH and LOW times ( $t_{CLOCKHI}$ ,  $t_{CLOCKLO}$ ) for it to be properly recognized by the PFD. The PFD's output is of a classical charge-pump type, outputting charge packets which are then integrated by the PLL's loop filter.

A lock-detection feature is also associated with the PFD. When the ispClock5600A is in a LOCKED state, the LOCK output pin goes LOW. The lock detector has two operating modes: Phase Lock Detect mode and Frequency

## Lattice Semiconductor

Lock Detect mode. In Phase Lock Detect mode, the LOCK signal is asserted if the phases of the reference and feedback signals match, whereas in Frequency Lock Detect mode the LOCK signal is asserted when the frequencies of the feedback and reference signals match. The option for which mode to use is programmable and may be set using PAC-Designer software (available from the Lattice website at <u>www.latticesemi.com</u>).

In Phase Lock Detect mode the lock detector asserts the LOCK signal as soon as a lock condition is determined.

In Frequency Lock Detect mode, however, the PLL must be in a locked condition for a set number of phase detector cycles before the LOCK signal will be asserted. The number of cycles required before asserting the LOCK signal in frequency-lock mode can be set from 16 to 256.

When the lock condition is lost the LOCK signal will be de-asserted immediately in both Phase Lock Detect and Frequency Lock Detect modes.

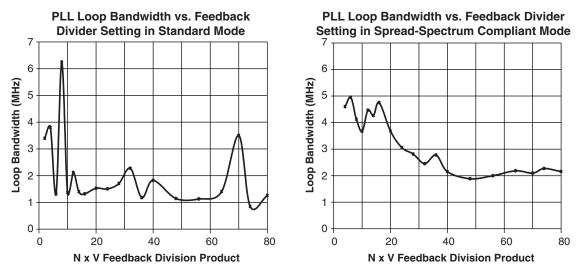

**Loop Filter:** The loop filter parameters for each profile are automatically selected by the PAC-Designer software depending on the following:

- Individual profile VCO operating frequency

- Individual profile NxV product

- · Maximum VCO operating frequency across all used profiles

**Spread Spectrum Support:** The reference clock inputs of the ispClock5600A device are spread spectrum clock tolerant. The tolerance limits are:

- Center spread ±0.125% to ±2%

- Down spread -0.25% to -4%

- 30-33kHz modulation frequency

#### Figure 1-12. PLL Loop Bandwidth vs. Feedback Divider Setting (Nominal)

#### vco

The ispClock5600A provides an internal VCO which provides an output frequency ranging from 320MHz to 800MHz. The VCO is implemented using differential circuit design techniques which minimize the influence of power supply noise on measured output jitter. The VCO is also used to generate output clock skew as a function of the total VCO period. Using the VCO as the basis for controlling output skew allows for highly precise and consistent skew generation, both from device-to-device, as well as channel-to-channel within the same device.

#### M-, N-, and V-Dividers

The ispClock5600A incorporates a set of programmable dividers which provide the ability to synthesize output frequencies differing from that of the reference clock input.

## Lattice Semiconductor

The input, or M-Divider prescales the input reference frequency, and can be programmed with integer values over the range of 1 to 40. To achieve low levels of output jitter, it is best to use the smallest M-Divider value possible.

The feedback, or N-Divider prescales the feedback frequency and like the M-Divider, can also be programmed with integer values ranging from 1 to 40.

Each one of the five output, or V-Dividers can be independently programmed to provide even division ratios ranging from 2 to 80.

When the PLL is selected (PLL\_BYPASS=LOW) and locked, the output frequency of each V-Divider ( $f_k$ ) may be calculated as:

$$f_{k} = f_{ref} \frac{N \times V_{fbk}}{M \times V_{k}}$$

(1)

where

$f_k \text{ is the frequency of V-Divider } k \\ f_{ref} \text{ is the input reference frequency} \\ M \text{ and N are the input and feedback divider settings} \\ V_{fbk} \text{ is the setting of the V-Divider used to close the PLL feedback path} \\ V_k \text{ is the setting of the V-Divider used to provide output k}$

Note that because the feedback may be taken from any V-Divider, V<sub>k</sub> and V<sub>fbk</sub> may refer to the same divider.

Because the VCO has an operating frequency range spanning 320 MHz to 800 MHz, and the V-Dividers provide division ratios from 2 to 80, the ispClock5600A can generate output signals ranging from 5 MHz to 400 MHz. For performance and stability reasons, however, there are several constraints which should be followed when selecting divider values:

- Use the smallest feasible value for the M-Divider

- The output frequency from the M (and N) divider should be greater or equal to 8 MHz.

- The product of the N-Divider and the V-Divider used to close the PLL's feedback loop should be less than or equal to 80 (N x V<sub>fbk</sub> ≤ 80)

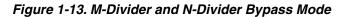

#### M-Divider and N-Divider Bypass Mode

The M-Divider and the N-Divider in the ispClock5600A device can be bypassed using PAC-Designer software. M and N-Dividers should be bypassed in applications that require glitchless switching between reference and feed-back clocks. However, the frequencies of these clocks should be close. If M and N-Dividers are not bypassed, one should ensure that t<sub>CLOCKHI</sub> and t<sub>CLOCKLO</sub> specifications are not violated. Otherwise, activation of the reset signal is necessary to ensure reliable switchover.

Note: Bypassing M- and N-Dividers also results in reducing the number of output frequency combinations generated from a single reference clock input.

#### PLL\_BYPASS Mode

The PLL\_BYPASS mode is provided so that input reference signals can be coupled through to the outputs without using the PLL functions. When PLL\_BYPASS mode is enabled (PLL\_BYPASS=HIGH), the output of the M-Divider is routed directly to the inputs of the V-Dividers. In PLL\_BYPASS mode, the nominal values of the V-Dividers are halved, so that they provide division ratios ranging from 1 to 40. The output frequency for a given V-Divider ( $f_k$ ) will be determined by

$$f_{k} = \frac{f_{\text{ref}} \times 2}{M \times V_{k}}$$

(2)

Please note that PLL\_BYPASS mode is provided primarily for testing purposes. When PLL\_BYPASS mode is enabled, features such as lock detect and skew generation are unavailable.

## **Reference and External Feedback Inputs**

The ispClock5600A provides sets of configurable, internally-terminated inputs for both clock reference and feedback signals. In normal operation, one of the clock reference input pairs (REFA+/- or REFB+/-) is used as a clock input.

The external feedback inputs make it possible to compensate for input to output delay through external means. This makes it possible to provide output clocks which have very low skews in relation to the reference clock regardless of loading effects.

The ispClock5610A provides one input signal pair for reference input and one input pair for external feedback, while the ispClock5620A provides two pairs for reference signals and two pairs for feedback. To select between reference and feedback inputs, the ispClock5620A provides two CMOS-compatible digital inputs called REFSEL and FBKSEL. Table 1-2 shows the behavior of these two control inputs.

#### Table 1-2. REFSEL and FBKSEL Operation for ispClock5620A

| REFSEL | Selected<br>Input Pair | FBKSEL | Selected<br>Input Pair |

|--------|------------------------|--------|------------------------|

| 0      | REFA+/-                | 0      | FBKA+/-                |

| 1      | REFB+/-                | 1      | FBKB+/-                |

- LVTTL (3.3V)

- LVCMOS (1.8V, 2.5V, 3.3V)

- SSTL2

- SSTL3

- HSTL

- eHSTL

- Differential SSTL1.8

- Differential SSTL2

- Differential SSTL3

- Differential HSTL

- LVDS

- LVPECL (differential, 3.3V)

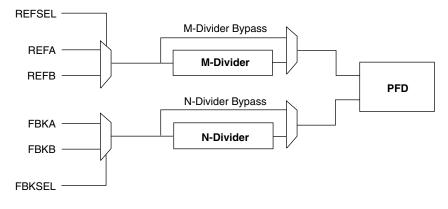

Each input also features internal programmable termination resistors, as shown in Figure 1-14. Note that all reference inputs (REFA+, REFA-, REFB+, REFB-) terminate to the REFVTT pin, while all feedback inputs (FBKA+, FBKA-, FBKB+, FBKB-) terminate to the FBKVTT pin.

The following usage guidelines are suggested for interfacing to supported logic families.

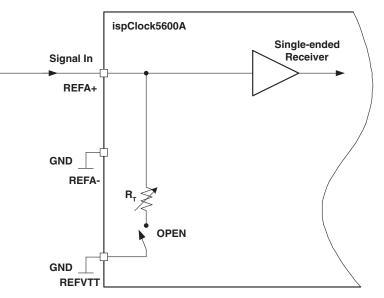

## LVTTL (3.3V), LVCMOS (1.8V, 2.5V, 3.3V)

The receiver should be set to LVCMOS or LVTTL mode, and the input signal should be connected to the '+' terminal of the input pair (e.g. REFA+). The '-' input terminal should be connected to GND. In addition, REFVTT should also be tied to GND. CMOS transmission lines are generally source terminated, so all termination resistors should be set to the OPEN state. Figure 1-15 shows the proper configuration. Please note that because switching thresholds are different for LVCMOS running at 1.8V, there is a separate configuration setting for this particular standard.

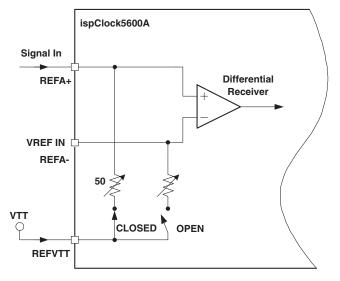

#### HSTL, eHSTL, SSTL2, SSTL3

The receiver should be set to HSTL/SSTL mode, and the input signal should be fed into the '+' terminal of the input pair. The '-' input terminal should be tied to the appropriate  $V_{REF}$  value, and the associated REFVTT or FBKVTT terminal should be tied to a  $V_{TT}$  termination supply. The positive input's terminating resistor should be engaged and set to 50 $\Omega$ . Figure 1-16 shows an appropriate configuration. Refer to the "Recommended Operating Conditions - Supported Logic Standards" table in this data sheet for suitable values of  $V_{REF}$  and  $V_{TT}$ . If one of the REF or FBK

## Lattice Semiconductor

pairs is not used, tie the unused pins REF+ and REF- to GND. In addition, if external feedback is not used, tied FBVTT to GND.

One important point to note is that the termination supplies must have low impedance and be able to both source and sink current without experiencing fluctuations. These requirements generally preclude the use of a resistive divider network, which has an impedance comparable to the resistors used, or of commodity-type linear voltage regulators, which can only source current. The best way to develop the necessary termination voltages is with a regulator specifically designed for this purpose. Because SSTL and HSTL logic is commonly used for high-performance memory busses, a suitable termination voltage supply is often already available in the system.

Figure 1-16. SSTL2, SSTL3, eHSTL, HSTL Receiver Configuration

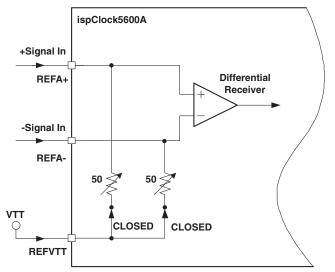

#### **Differential HSTL and SSTL**

HSTL and SSTL are sometimes used in a differential form, especially for distributing clocks in high-speed memory systems. Figure 1-17 shows how ispClock5600A reference input should be configured for accepting these standards. The major difference between differential and single-ended forms of these logic standards is that in the differential case, the REFA- input is used as a signal input, not a reference level, and that both terminating resistors are engaged and set to  $50\Omega$ . If one of the REF or FBK pairs is not used, tie the unused REF+ and REF- pins to GND. If external feedback is not used, tie FBVTT to GND as well.

Figure 1-17. Differential HSTL/SSTL Receiver Configuration

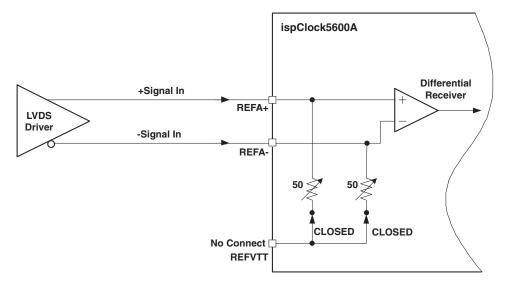

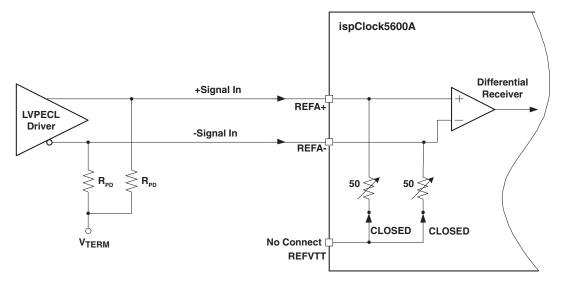

### LVDS/Differential LVPECL

The receiver should be set to LVDS or LVPECL mode as required and both termination resistors should be engaged and set to  $50\Omega$ . The associated REFVTT or FBKVTT pin, however, should be left unconnected. This creates a floating  $100\Omega$  differential termination resistance across the input terminals. The LVDS termination configuration is shown in Figure 1-18.

#### Figure 1-18. LVDS Input Receiver Configuration

Note that while a floating  $100\Omega$  resistor forms a complete termination for an LVDS signal line, additional circuitry may be required to satisfactorily terminate a differential LVPECL signal. This is because a true bipolar LVPECL output driver typically requires an external DC 'pull-down' path to a V<sub>TERM</sub> termination voltage (typically VCC-2V) to properly bias its open emitter output stage. When interfacing to an LVPECL input signal, the ispClock5600A's internal termination resistors should not be used for this pull-down function, as they may be damaged from excessive current. The pull-down should be implemented with external resistors placed close to the LVPECL driver (Figure 1-19)

#### Figure 1-19. LVPECL Input Receiver Configuration

Please note that while the above discussions specify using  $50\Omega$  termination impedances, the actual impedance required to properly terminate the transmission line and maintain good signal integrity may vary from this ideal. The

actual impedance required will be a function of the driver used to generate the signal and the transmission medium used (PCB traces, connectors and cabling). The ispClock5600A's ability to adjust input impedance over a range of 40 $\Omega$  to 70 $\Omega$  allows the user to adapt his circuit to non-ideal behaviors from the rest of the system without having to swap out components.

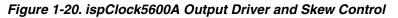

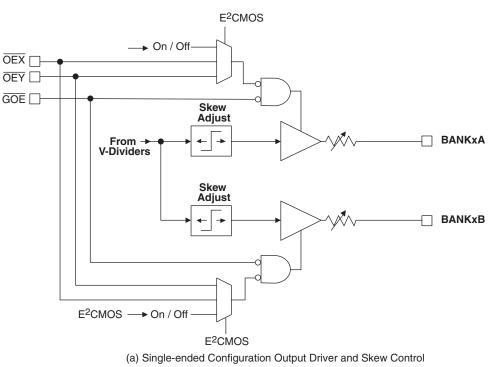

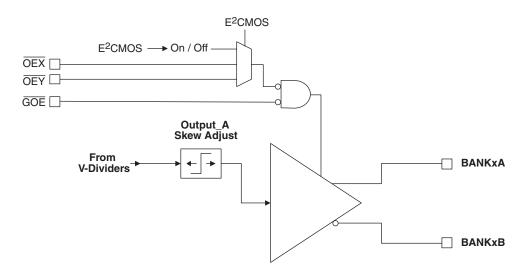

## **Output Drivers**

The ispClock5600A provide banks of configurable, internally-terminated high-speed dual-output line drivers. The ispClock5610A provides five driver banks, while the ispClock5620A provides ten. Each of these driver banks may be configured to provide either a single differential output signal, or a pair of single-ended output signals. Program-mable internal source-series termination allows the ispClock5600A to be matched to transmission lines with impedances ranging from 40 to 70 Ohms. The outputs may be independently enabled or disabled, either from E<sup>2</sup>CMOS configuration or by external control lines. Additionally, each can be independently programmed to provide a fixed amount of signal delay or skew, allowing the user to compensate for the effects of unequal PCB trace lengths or loading effects. Figure 1-20 shows a block diagram of a typical ispClock5600A output driver bank and associated skew control.

Because of the high edge rates which can be generated by the ispClock5600A's clock output drivers, the VCCO power supply pin for each output bank should be individually bypassed. Low ESR capacitors with values ranging from 0.01 to 0.1  $\mu$ F may be used for this purpose. Each bypass capacitor should be placed as close to its respective output bank power pins (VCCO and GNDO) pins as is possible to minimize interconnect length and associated parasitic inductances.

In the case where an output bank is unused, the associated VCCO pin may be either left floating or tied to ground to reduce quiescent power consumption. We recommend, however, that all unused VCCO pins be tied to ground where possible. All GND0 pins must be tied to ground, regardless of whether or not the associated bank is used.

(b) Differential Configuration Output Driver and Skew Control