# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

InvenSense Inc. 1745 Technology Drive, San Jose, CA 95110 U.S.A. Tel: +1 (408) 988-7339 Fax: +1 (408) 988-8104 Website: www.invensense.com

Document Number: PS-ISZ-2510A-00 Revision: 1.0 Release Date: 12/24/2013

# ISZ-2510 Product Specification Revision 1.0

## CONTENTS

| 1.1   REVISION HISTORY   4     1.2   PURPOSE AND SCOPE   5     1.3   PRODUCT OVERVIEW   5     1.4   APPLICATIONS   5     2   FEATURES   6     2.1   SENSORS   6     2.2   DIGITAL OUTPUT   6     2.3   DATA PROCESSING   6     2.4   CLOCKING   6     2.5   POWER   6     2.6   PACACINE   6     2.7   POWER   6     2.8   POWER   6     2.6   POWER   6     3.7   SELECTRICAL CHARACTERISTICS   7     3.1   SELECTRICAL SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS   7     3.3   ELECTRICAL SPECIFICATIONS   7     3.4   I'C TIMING CHARACTERIZATION   10     3.5   SELECTRICAL SPECIFICATIONS   7     3.4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION                                                                                                                                                                                                                                                   | 1 | DOC  | CUMENT INFORMATION                | .4 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----------------------------------|----|

| 1.3   PRODUCT OVERVIEW.   5     1.4   APPLICATIONS.   55     2   FEATURES   6     2.1   SENSORS   6     2.2   DIGITAL OUTPUT   6     2.3   DATA PROCESSING   6     2.4   CLOCKING   6     2.5   POWER   6     2.6   PACKAGE   6     3   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS   7     3.3   ELECTRICAL SPECIFICATIONS   7     3.4   FC TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   10     3.6   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILLO PROVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW                                                                                                                                                      |   |      |                                   |    |

| 1.4   APPLICATIONS.   5     2   FEATURES   6     2.1   SENSORS.   6     2.2   DIATA PROCESSING   6     2.3   DATA PROCESSING   6     2.4   CLOCKING   6     2.5   POWER   6     2.6   PACKAGE   6     3   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS.   7     3.2   ELECTRICAL SPECIFICATIONS.   7     3.4   JÉC TIMING CHARACTERISTICS   7     3.5   SPI TIMING CHARACTERIZATION   10     3.6   ABSOLUTE MAXIMUM RATINGS.   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>C</sup> C AND SPI SERIAL COMMONICATIONS INTERFACE   <                                                                                         |   |      |                                   |    |

| 2.1   SENSORS   6     2.2   DIGITAL OUTPUT   6     2.3   DATA PROCESSING   6     2.4   CLOCKING   6     2.4   CLOCKING   6     2.6   PACKAGE   6     3.6   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.4   I <sup>2</sup> C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   10     3.6   SPI TIMING CHARACTERIZATION   11     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BLIC OF MATERING SIGNAL DESCRIPTION   13     4.4   BLIC OF MATERING SIGNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15 </td <td></td> <td>-</td> <td></td> <td></td>                                                         |   | -    |                                   |    |

| 2.2   Digital Output   6     2.3   Data Processing   6     2.4   CLOCKING   6     2.5   POWER   6     2.6   Package   6     3   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.4   I'C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   10     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   14     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINCLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I'C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.1   BLOCK DIAGRAM   15   15                                                                                    | 2 | FEA  | TURES                             | 6  |

| 2.2   Digital Output   6     2.3   Data Processing   6     2.4   CLOCKING   6     2.5   POWER   6     2.6   Package   6     3   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.4   I'C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   10     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   14     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINCLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I'C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.1   BLOCK DIAGRAM   15   15                                                                                    |   | 2.1  | SENSORS                           | 6  |

| 2.4   CLOCKING.   6     2.5   POWER   6     2.6   PACKAGE   6     3   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS.   7     3.2   ELECTRICAL SPECIFICATIONS.   7     3.3   ELECTRICAL SPECIFICATIONS.   7     3.4   I*C TIMING CHARACTERIZATION.   9     3.4   I*C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   10     3.6   ABSOLUTE MAXIMUM RATINGS.   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I*C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16                                                                         |   |      | DIGITAL OUTPUT                    | 6  |

| 2.5   POWER   6     2.6   PACKAGE   6     3   ELECTRICAL CHARACTERISTICS   7     3.1   SENSOR SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS   8     3.3   ELECTRICAL SPECIFICATIONS   8     3.4   I <sup>2</sup> C   TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   10     3.6   ABSOLUTE MAXIMUM RATINGS   11     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     6.6   SENSOR DATA REGISTERS   16 <td></td> <td></td> <td></td> <td></td> |   |      |                                   |    |

| 2.6   PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                   |    |

| 3.1   SENSOR SPECIFICATIONS   7     3.2   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.3   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.4   I <sup>2</sup> C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   11     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERNAL CLOCK GENERATION   16     6.8   INTERNAL CLOCK GENERATION   16     6.9   DIGITAL INTERFACE<           |   |      |                                   | -  |

| 3.2   ELECTRICAL SPECIFICATIONS.   8     3.3   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.4   I <sup>7</sup> C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   11     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION.   13     4.2   TYPICAL OPERATING CIRCUIT   14     4   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>7</sup> C AND SPI SENIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16   16     5.8   INTERRUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE                                 | 3 | ELE  | CTRICAL CHARACTERISTICS           | .7 |

| 3.3   ELECTRICAL SPECIFICATIONS, CONTINUED   9     3.4   I <sup>2</sup> C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   11     3.6   ABSOLUTE MAXIMUM RATINOS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERNUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     6   DIGITAL INTERFACE   17     7   SERIAL INTERFACE   17     6.10   BIGITAL INTERFACE   17                                       |   | 3.1  | SENSOR SPECIFICATIONS             | .7 |

| 3.4   I <sup>2</sup> C TIMING CHARACTERIZATION   10     3.5   SPI TIMING CHARACTERIZATION   11     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERNAL CLOCK GENERATIONS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     7   SERIAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   22                              |   |      |                                   |    |

| 3.5   SPI TIMING CHARACTERIZATION   11     3.6   ABSOLUTE MAXIMUM RATINGS   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS   16     5.9   Digital-Output TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8                                                              |   |      |                                   |    |

| 3.6   ABSOLUTE MAXIMUM RATINGS.   12     4   APPLICATIONS INFORMATION   13     4.1   PIN OUT AND SIGNAL DESCRIPTION   13     4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SENIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERNAL CLOCK GENERATION   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     7   SERIAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   22     7.1   SUPPORTED INTERFACES   22     7.1   SUPPORTED INTERFACES   22     <                                                  |   | -    |                                   |    |

| 4.1   PIN OUT AND SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                   |    |

| 4.2   TYPICAL OPERATING CIRCUIT   14     4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS   14     5   FUNCTIONAL OVERVIEW   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS.   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.1   ORIENTATION SI   23                                                                                                                     | 4 | APF  | PLICATIONS INFORMATION            | 13 |

| 4.3   BILL OF MATERIALS FOR EXTERNAL COMPONENTS.   14     5   FUNCTIONAL OVERVIEW.   15     5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW.   15     5.3   SINCLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                     |   | 4.1  | PIN OUT AND SIGNAL DESCRIPTION.   | 13 |

| 5   FUNCTIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                   |    |

| 5.1   BLOCK DIAGRAM   15     5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS.   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE CONSIDERATIONS   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                             |   | -    |                                   |    |

| 5.2   OVERVIEW   15     5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                  | 5 | FUN  |                                   |    |

| 5.3   SINGLE-AXIS MEMS GYROSCOPE WITH 16-BIT ADCS AND SIGNAL CONDITIONING   15     5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE CONSIDERATIONS   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                           |   |      |                                   |    |

| 5.4   I <sup>2</sup> C AND SPI SERIAL COMMUNICATIONS INTERFACE   15     5.5   INTERNAL CLOCK GENERATION   16     5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE   17     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                                                                                                                             |   | -    |                                   |    |

| 5.6   SENSOR DATA REGISTERS   16     5.7   FIFO   16     5.8   INTERRUPTS   16     5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE CONSIDERATIONS   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                   |    |

| 5.7   FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | INTERNAL CLOCK GENERATION         | 16 |

| 5.8   INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      |                                   |    |

| 5.9   DIGITAL-OUTPUT TEMPERATURE SENSOR   16     5.10   BIAS AND LDO   16     6   DIGITAL INTERFACE   17     6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE CONSIDERATIONS   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | -    |                                   |    |

| 6   DIGITAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | DIGITAL-OUTPUT TEMPERATURE SENSOR | 16 |

| 6.1   I <sup>2</sup> C SERIAL INTERFACE   17     7   SERIAL INTERFACE CONSIDERATIONS   22     7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5.10 | BIAS AND LDO                      | 16 |

| 7     SERIAL INTERFACE CONSIDERATIONS     22       7.1     SUPPORTED INTERFACES     22       7.2     LOGIC LEVELS     22       8     ASSEMBLY     23       8.1     ORIENTATION OF AXES     23       8.2     PACKAGE DIMENSIONS     24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6 | DIG  | ITAL INTERFACE                    | 17 |

| 7.1   SUPPORTED INTERFACES   22     7.2   LOGIC LEVELS   22     8   ASSEMBLY   23     8.1   ORIENTATION OF AXES   23     8.2   PACKAGE DIMENSIONS   24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 6.1  | I <sup>2</sup> C SERIAL INTERFACE | 17 |

| 7.2   LOGIC LEVELS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7 | SEF  | RIAL INTERFACE CONSIDERATIONS     | 22 |

| 8     ASSEMBLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      |                                   |    |

| 8.1ORIENTATION OF AXES238.2PACKAGE DIMENSIONS24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ |      |                                   |    |

| 8.2 PACKAGE DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8 |      |                                   | -  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | •••• |                                   |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                   |    |

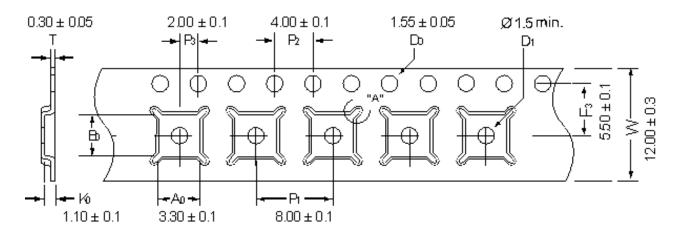

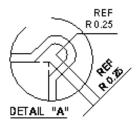

| 8.4<br>8.5                                | TAPE & REEL SPECIFICATION<br>PCB DESIGN GUIDELINES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25<br>27                                                                   |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 9 RE                                      | GISTER MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28                                                                         |

| 10 F                                      | REGISTER DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                                                         |

| 10.11<br>10.12<br>10.13<br>10.14<br>10.15 | REGISTERS 04-05, 07-08, 10-11- GYROSCOPE OFFSET TEMPERATURE COMPENSATION (TC)<br>REGISTER 19 TO 24 – GYROSCOPE OFFSET ADJUSTMENT<br>REGISTER 25 – SAMPLE RATE DIVIDER<br>REGISTER 26 – CONFIGURATION<br>REGISTER 27 – GYROSCOPE CONFIGURATION<br>REGISTER 35 – FIFO ENABLE<br>REGISTER 55 – INT PIN / BYPASS ENABLE CONFIGURATION<br>REGISTER 56 – INTERRUPT ENABLE<br>REGISTER 56 – INTERRUPT ENABLE<br>REGISTER 58 – INTERRUPT STATUS<br>REGISTER 65 AND 66 – TEMPERATURE MEASUREMENT<br>REGISTERS 67 TO 72 – GYROSCOPE MEASUREMENTS<br>REGISTER 106 – USER CONTROL<br>REGISTER 107 – POWER MANAGEMENT 1<br>REGISTER 108 – POWER MANAGEMENT 2<br>REGISTER 114 AND 115 – FIFO COUNT REGISTERS<br>REGISTER 116 – FIFO READ WRITE | 30<br>31<br>32<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43 |

| 10.17                                     | Register 117 – WHO AM I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                         |

## 1 Document Information

## 1.1 Revision History

| Revision<br>Date | Revision | Description     |

|------------------|----------|-----------------|

| 12/24/2013       | 1.0      | Initial Release |

#### 1.2 Purpose and Scope

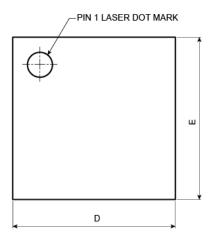

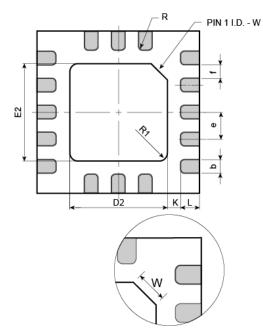

This document is a preliminary product specification, providing a description, specifications, and design related information for the single axis ISZ-2510<sup>™</sup> gyroscope. The device is housed in a small 3x3x0.9mm QFN package.

#### 1.3 Product Overview

The ISZ-2510 is a single-chip, digital output, single axis MEMS gyroscope IC which features a 512-byte FIFO. The FIFO can lower the traffic on the serial bus interface, and reduce power consumption by allowing the system processor to burst read sensor data and then go into a low-power mode.

The gyroscope includes a programmable full-scale range of  $\pm 250$ ,  $\pm 500$ ,  $\pm 1000$ , and  $\pm 2000$  degrees/sec, very low Rate noise at 0.01 dps/ $\sqrt{Hz}$  and extremely low power consumption at 2.8mA. Factory-calibrated initial sensitivity reduces production-line calibration requirements.

Other industry-leading features include on-chip 16-bit ADCs, programmable digital filters, a precision clock with 1% drift from -40°C to 85°C, an embedded temperature sensor, and programmable interrupts. The device features I<sup>2</sup>C and SPI serial interfaces, a VDD operating range of 1.71 to 3.6V, and a separate digital IO supply, VDDIO from 1.71V to 3.6V.

By leveraging its patented and volume-proven CMOS-MEMS fabrication platform, which integrates MEMS wafers with companion CMOS electronics through wafer-level bonding, InvenSense has driven the gyro package size down to a footprint and thickness of 3x3x0.9mm (16-pin QFN), to provide a very small yet high performance low cost package. The device provides high robustness by supporting 10,000 *g* shock reliability.

#### 1.4 Applications

- Toys

- Tools

- Industrial

## 2 Features

The ISZ-2510 MEMS gyroscope includes a wide range of features:

#### 2.1 Sensors

- Monolithic Z- Axis angular rate sensor (gyros) integrated circuit

- Digital-output temperature sensor

- External sync signal connected to the FSYNC pin supports image, video and GPS synchronization

- Factory calibrated scale factor

- High cross-axis isolation via proprietary MEMS design

- 10,000*g* shock tolerant

#### 2.2 Digital Output

- Fast Mode (400kHz) I<sup>2</sup>C serial interface

- 1 MHz SPI serial interface for full read/write capability

- 20 MHz SPI to read gyro sensor & temp sensor data.

- 16-bit ADCs for digitizing sensor outputs

- User-programmable full-scale-range of ±250, ±500, ±1000, and ±2000 °/sec

#### 2.3 Data Processing

- The total data set obtained by the device includes gyroscope data, temperature data, and the one bit external sync signal connected to the FSYNC pin.

- FIFO allows burst read, reduces serial bus traffic and saves power on the system processor.

- FIFO can be accessed through both I<sup>2</sup>C and SPI interfaces.

- Programmable interrupt

- Programmable low-pass filters

#### 2.4 Clocking

• On-chip timing generator clock frequency ±1% drift over full temperature range

#### 2.5 Power

- VDD supply voltage range of 1.71V to 3.6V

- Flexible VDDIO reference voltage allows for multiple I<sup>2</sup>C and SPI interface voltage levels

- Power consumption with both axes active: 2.8mA

- Sleep mode: 8µA

- Each axis can be individually powered down

#### 2.6 Package

- 3x3x0.9mm footprint and maximum thickness 16-pin QFN plastic package

- MEMS structure hermetically sealed at wafer level

- RoHS and Green compliant

## 3 Electrical Characteristics

## 3.1 Sensor Specifications

Typical Operating Circuit of Section 4.2, VDD = 2.5V, VDDIO = 1.8V,  $T_A=25^{\circ}C$ .

| Parameter                                              | Conditions                   | Min | Typical    | Max | Unit      | Notes |

|--------------------------------------------------------|------------------------------|-----|------------|-----|-----------|-------|

| GYRO SENSITIVITY                                       |                              |     |            |     |           |       |

| Full-Scale Range                                       | FS_SEL=0                     |     | ±250       |     | º/s       |       |

|                                                        | FS_SEL=1                     |     | ±500       |     | º/s       |       |

|                                                        | FS_SEL=2                     |     | ±1000      |     | º/s       |       |

|                                                        | FS_SEL=3                     |     | ±2000      |     | º/s       |       |

| Sensitivity Scale Factor                               | FS_SEL=0                     |     | 131        |     | LSB/(⁰/s) |       |

|                                                        | FS_SEL=1                     |     | 65.5       |     | LSB/(º/s) |       |

|                                                        | FS_SEL=2                     |     | 32.8       |     | LSB/(º/s) |       |

|                                                        | FS_SEL=3                     |     | 16.4       |     | LSB/(º/s) |       |

| Gyro ADC Word Length                                   |                              |     | 16         |     | bits      |       |

| Sensitivity Scale Factor Tolerance                     | 25°C                         |     | ±4.5       |     | %         |       |

| Sensitivity Scale Factor Variation Over<br>Temperature | -10°C to +75°                |     | ±4         |     | %         |       |

| Nonlinearity                                           | Best fit straight line; 25°C |     | ±0.2       |     | %         |       |

| Cross-Axis Sensitivity                                 |                              |     | ±2         |     | %         |       |

| GYRO ZERO-RATE OUTPUT (ZRO)                            |                              |     |            |     |           |       |

| Initial ZRO Tolerance                                  | 25°C                         |     | ±15        |     | º/s       |       |

| ZRO Variation Over Temperature                         | -10°C to +75°C               |     | ±15        |     | º/s       |       |

| GYRO NOISE PERFORMANCE                                 | FS_SEL=0                     |     |            |     |           |       |

| Total RMS Noise                                        | DLPFCFG=2 (92 Hz)            |     | 0.1        |     | ⁰/s-rms   |       |

| Rate Noise Spectral Density                            | At 10Hz                      |     | 0.01       |     | °/s/√Hz   |       |

| GYRO MECHANICAL                                        |                              |     |            |     |           |       |

| Mechanical Frequency                                   |                              | 25  | 27         | 29  | kHz       |       |

| GYRO START-UP TIME                                     | DLPFCFG=0, to ±1º/s of Final |     |            |     |           |       |

| ZRO Settling                                           | From Sleep Mode to ready     |     | 35         |     | ms        |       |

|                                                        | From Power On to ready       |     | 50         |     | ms        |       |

| TEMPERATURE SENSOR                                     |                              |     |            |     |           |       |

| Range                                                  | Untrimmed                    |     | -10 to +75 |     | °C        |       |

| Sensitivity                                            |                              |     | 321.4      |     | LSB/ºC    |       |

| Room-Temperature Offset                                | 21°C                         |     | 0          |     | LSB       |       |

| Linearity                                              |                              |     | ±0.2       |     | °C        |       |

| TEMPERATURE RANGE                                      |                              |     |            |     |           |       |

| Specification Temperature Range                        |                              | -10 |            | +75 | °C        |       |

#### 3.2 Electrical Specifications

Typical Operating Circuit of Section 4.2, VDD = 2.5V, VDDIO = 1.8V, T<sub>A</sub> =  $25^{\circ}$ C.

| Parameters                                                                                         | Conditions                                                                                                     | Min       | Typical            | Max       | Units        | Notes |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------|--------------------|-----------|--------------|-------|

| VDD POWER SUPPLY                                                                                   |                                                                                                                |           |                    |           |              |       |

| Operating Voltage Range                                                                            |                                                                                                                | 1.71      |                    | 3.6       | V            |       |

| Power-Supply Ramp Rate                                                                             | Monotonic ramp. Ramp<br>rate is 10% to 90% of the<br>final value                                               | 1         |                    | 100       | ms           |       |

| Normal Operating Current                                                                           | Z Axis Active                                                                                                  |           | 2.8                |           | mA           |       |

| Sleep Mode Current                                                                                 |                                                                                                                |           | 8                  |           | μA           |       |

| VDDIO REFERENCE VOLTAGE<br>(must be regulated)                                                     |                                                                                                                |           |                    |           |              |       |

| Voltage Range                                                                                      |                                                                                                                | 1.71      |                    | 3.6       | V            |       |

| Power-Supply Ramp Rate                                                                             | Monotonic ramp. Ramp<br>rate is 10% to 90% of the<br>final value                                               | 0.1       |                    | 100       | ms           |       |

| Normal Operating Current                                                                           | 10pF load, 5MHz data rate.<br>Does not include pull up<br>resistor current draw as<br>that is system dependent |           | 300                |           | μA           |       |

| START-UP TIME FOR REGISTER<br>READ/WRITE                                                           |                                                                                                                |           | 12                 |           | ms           |       |

| I <sup>2</sup> C ADDRESS                                                                           | AD0 = 0<br>AD0 = 1                                                                                             |           | 1101000<br>1101001 |           |              |       |

| DIGITAL INPUTS (FSYNC, AD0,<br>SCLK, SDI, /CS)                                                     |                                                                                                                |           |                    |           |              |       |

| $V_{IH}$ , High Level Input Voltage $V_{IL}$ , Low Level Input Voltage $C_{I}$ , Input Capacitance |                                                                                                                | 0.7*VDDIO | < 5                | 0.3*VDDIO | V<br>V<br>pF |       |

| DIGITAL OUTPUT (INT, SDO)                                                                          |                                                                                                                |           |                    |           |              |       |

| V <sub>OH</sub> , High Level Output Voltage                                                        | $R_{LOAD}$ =1M $\Omega$                                                                                        | 0.9*VDDIO |                    |           | V            |       |

| V <sub>OL1</sub> , LOW-Level Output Voltage                                                        | R <sub>LOAD</sub> =1MΩ                                                                                         |           |                    | 0.1*VDDIO | V            |       |

| V <sub>OL.INT1</sub> , INT Low-Level Output Voltage                                                | OPEN=1, 0.3mA sink                                                                                             |           |                    | 0.1       | V            |       |

|                                                                                                    | current                                                                                                        |           | 100                |           |              |       |

| Output Leakage Current                                                                             | OPEN=1                                                                                                         |           | 100                |           | nA           |       |

| t <sub>INT</sub> , INT Pulse Width                                                                 | LATCH_INT_EN=0                                                                                                 |           | 50                 |           | μs           |       |

Note: Power-Supply Ramp Rates are defined as the time it takes for the voltage to rise from 10% to 90% of the final value. VDD and VDDIO must be monotonic ramps.

## 3.3 Electrical Specifications, continued

Typical Operating Circuit of Section 4.2, VDD = 2.5V, VDDIO = 1.8V, T<sub>A</sub> =  $25^{\circ}$ C.

| Parameters                                                                      | Conditions                                               | Min | Typical                      | Max | Units    | Notes |

|---------------------------------------------------------------------------------|----------------------------------------------------------|-----|------------------------------|-----|----------|-------|

| I <sup>2</sup> C I/O (SCL, SDA)                                                 |                                                          |     |                              |     |          |       |

| V⊾, LOW Level Input Voltage                                                     |                                                          |     | -0.5V to 0.3*VDDIO           |     | V        |       |

| V⊮, HIGH-Level Input Voltage                                                    |                                                          |     | 0.7*VDDIO to VDDIO +<br>0.5V |     | V        |       |

| V <sub>hys</sub> , Hysteresis                                                   |                                                          |     | 0.1*VDDIO                    |     | V        |       |

| VoL1, LOW-Level Output Voltage                                                  | 3mA sink current                                         |     | 0 to 0.4                     |     | V        |       |

| I <sub>OL</sub> , LOW-Level Output Current                                      | $\begin{array}{l} V_{OL}=0.4V\\ V_{OL}=0.6V \end{array}$ |     | 3<br>6                       |     | mA<br>mA |       |

| Output Leakage Current                                                          |                                                          |     | 100                          |     | nA       |       |

| $t_{\text{of}},$ Output Fall Time from $V_{\text{IHmax}}$ to $V_{\text{ILmax}}$ | C <sub>b</sub> bus capacitance in pf                     |     | 20+0.1Cb to 250              |     | ns       |       |

| C <sub>I</sub> , Capacitance for Each I/O pin                                   |                                                          |     | < 10                         |     | pF       |       |

| INTERNAL CLOCK SOURCE                                                           |                                                          |     |                              |     |          |       |

|                                                                                 | Fchoice=0,1,2<br>SMPLRT_DIV=0                            |     | 32                           |     | kHz      |       |

| Sample Rate                                                                     | Fchoice=3;<br>DLPFCFG=0 or 7<br>SMPLRT_DIV=0             |     | 8                            |     | kHz      |       |

|                                                                                 | Fchoice=3;<br>DLPFCFG=1,2,3,4,5,6;<br>SMPLRT_DIV=0       |     | 1                            |     | kHz      |       |

| Clock Frequency Initial Tolerance                                               | CLK_SEL=0, 6; 25°C                                       | -2  |                              | +2  | %        |       |

|                                                                                 | CLK_SEL=1,2,3,4,5; 25°C                                  | -1  |                              | +1  | %        |       |

| Frequency Variation over Temperature                                            | CLK_SEL=0,6                                              |     | -10 to +10                   |     | %        |       |

|                                                                                 | CLK_SEL=1,2,3,4,5                                        |     | ±1                           |     | %        |       |

| PLL Settling Time                                                               | CLK_SEL=1,2,3,4,5                                        |     | 4                            |     | ms       |       |

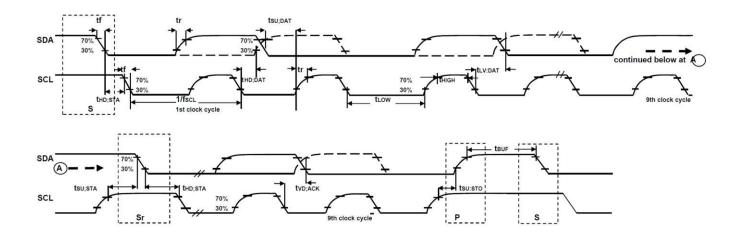

## 3.4 I<sup>2</sup>C Timing Characterization

Typical Operating Circuit of Section 4.2, VDD = 2.5V, VDDIO = 1.8V,  $T_A=25^{\circ}C$ .

| Parameters                                                                   | Conditions                                  | Min                      | Typical | Max | Units | Notes |

|------------------------------------------------------------------------------|---------------------------------------------|--------------------------|---------|-----|-------|-------|

| I <sup>2</sup> C TIMING                                                      | I <sup>2</sup> C FAST-MODE                  |                          |         |     |       |       |

| f <sub>SCL</sub> , SCL Clock Frequency                                       |                                             | 0                        |         | 400 | kHz   |       |

| t <sub>HD.STA</sub> , (Repeated) START Condition<br>Hold Time                |                                             | 0.6                      |         |     | μs    |       |

| tLOW, SCL Low Period                                                         |                                             | 1.3                      |         |     | μs    |       |

| t <sub>HIGH</sub> , SCL High Period                                          |                                             | 0.6                      |         |     | μs    |       |

| t <sub>SU.STA</sub> , Repeated START Condition<br>Setup Time                 |                                             | 0.6                      |         |     | μs    |       |

| t <sub>HD.DAT</sub> , SDA Data Hold Time                                     |                                             | 0                        |         |     | μs    |       |

| t <sub>SU.DAT</sub> , SDA Data Setup Time                                    |                                             | 100                      |         |     | ns    |       |

| tr, SDA and SCL Rise Time                                                    | C <sub>b</sub> bus cap. from 10 to<br>400pF | 20+0.1<br>C <sub>b</sub> |         | 300 | ns    |       |

| $t_{\rm f},$ SDA and SCL Fall Time                                           | C <sub>b</sub> bus cap. from 10 to<br>400pF | 20+0.1<br>C <sub>b</sub> |         | 300 | ns    |       |

| $t_{\text{SU.STO}}$ , STOP Condition Setup Time                              |                                             | 0.6                      |         |     | μs    |       |

| $t_{\mbox{\scriptsize BUF}},$ Bus Free Time Between STOP and START Condition |                                             | 1.3                      |         |     | μs    |       |

| $C_b$ , Capacitive Load for each Bus Line                                    |                                             |                          | < 400   |     | pF    |       |

| t <sub>VD.DAT</sub> , Data Valid Time                                        |                                             |                          |         | 0.9 | μs    |       |

| tvd.ack, Data Valid Acknowledge Time                                         |                                             |                          |         | 0.9 | μs    |       |

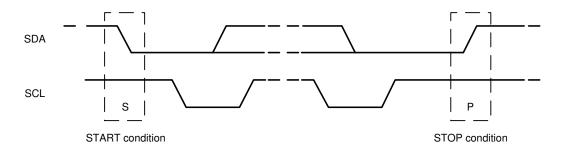

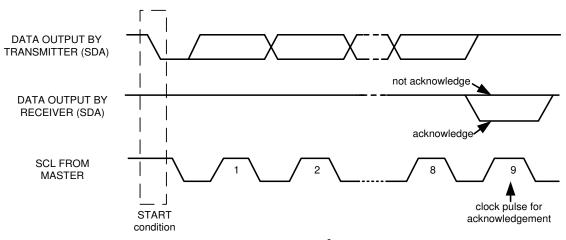

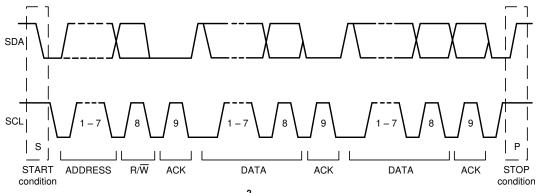

I<sup>2</sup>C Bus Timing Diagram

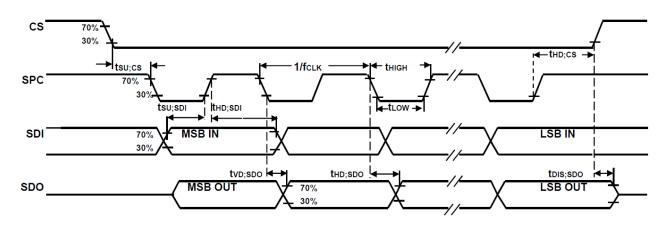

## 3.5 SPI Timing Characterization

Typical Operating Circuit of Section 4.2, VDD = 2.5V, VDDIO = 1.8V, T<sub>A</sub> =  $25^{\circ}$ C,

| Parameters                                     | Conditions                               | Min | Typical | Max             | Units |

|------------------------------------------------|------------------------------------------|-----|---------|-----------------|-------|

| SPI TIMING                                     |                                          |     |         |                 |       |

| f <sub>SCLK</sub> , SCLK Clock Frequency       |                                          |     |         | 1 <sup>1</sup>  | MHz   |

|                                                |                                          |     |         | 20 <sup>2</sup> | MHz   |

| t <sub>LOW</sub> , SCLK Low Period             |                                          | 400 |         |                 | ns    |

| t <sub>HIGH</sub> , SCLK High Period           |                                          | 400 |         |                 | ns    |

| t <sub>SU.CS</sub> , CS Setup Time             |                                          | 8   |         |                 | ns    |

| t <sub>HD.CS</sub> , CS Hold Time              |                                          | 500 |         |                 | ns    |

| t <sub>SU.SDI</sub> , SDI Setup Time           |                                          | 11  |         |                 | ns    |

| t <sub>HD.SDI</sub> , SDI Hold Time            |                                          | 7   |         |                 | ns    |

| t <sub>vD.SDO</sub> , SDO Valid Time           | $C_{load} = 20 pF$                       |     |         | 100             | ns    |

| t <sub>HD.SDO</sub> , SDO Hold Time            | $C_{load} = 20 pF$<br>$C_{load} = 20 pF$ | 4   |         |                 | ns    |

| t <sub>DIS.SDO</sub> , SDO Output Disable Time |                                          |     |         | 10              | ns    |

#### Notes:

- 1. R/W of all Registers

- 2. Read of Sensor Registers only

**SPI Bus Timing Diagram**

#### 3.6 Absolute Maximum Ratings

Stress above those listed as "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to the absolute maximum ratings conditions for extended periods may affect device reliability.

| Parameter                                | Rating                           |

|------------------------------------------|----------------------------------|

| Supply Voltage, VDD                      | -0.5V to +4.0V                   |

| VDDIO Input Voltage Level                | -0.5V to 4.0V                    |

| REGOUT                                   | -0.5V to 2V                      |

| Input Voltage Level (AD0, FSYNC)         | -0.5V to VDD                     |

| SCL, SDA, INT (SPI enable)               | -0.5V to VDD                     |

| SCL, SDA, INT (SPI disable)              | -0.5V to VDD                     |

| Acceleration (Any Axis, unpowered)       | 10,000 <i>g</i> for 0.2ms        |

| Operating Temperature Range              | -40°C to +85°                    |

| Storage Temperature Range                | -40°C to +125°C                  |

| Electrostatic Discharge (ESD) Protection | 2kV (HBM); 200V (MM)             |

| Latch-up                                 | JEDEC Class II (2),125°C, ±100mA |

#### **Absolute Maximum Ratings**

## 4 Applications Information

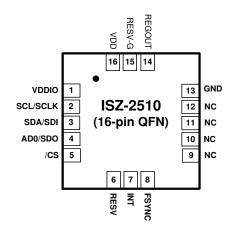

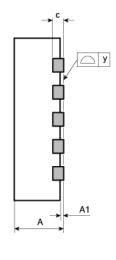

## 4.1 Pin Out and Signal Description

| Pin Number<br>3x3x0.9mm | Pin Name   Pin Description |                                                                        |

|-------------------------|----------------------------|------------------------------------------------------------------------|

| 1                       | VDDIO                      | Digital I/O supply voltage                                             |

| 2                       | SCL/SCLK                   | I <sup>2</sup> C serial clock (SCL); SPI serial clock (SCLK)           |

| 3                       | SDA/SDI                    | I <sup>2</sup> C serial data (SDA); SPI serial data input (SDI)        |

| 4                       | AD0 / SDO                  | I <sup>2</sup> C Slave Address LSB (AD0); SPI serial data output (SDO) |

| 5                       | /CS                        | SPI chip select (0=SPI mode, 1= I <sup>2</sup> C mode)                 |

| 6                       | RESV                       | Reserved. Connect to Ground.                                           |

| 7                       | INT                        | Interrupt digital output (totem pole or open-drain)                    |

| 8                       | FSYNC                      | Frame synchronization digital input. Connect to GND if not used.       |

| 13                      | GND                        | Power supply ground                                                    |

| 14                      | REGOUT                     | Regulator filter capacitor connection                                  |

| 15                      | RESV-G                     | Reserved. Connect to Ground.                                           |

| 16                      | VDD                        | Power supply voltage                                                   |

| 9, 10, 11, 12 NC        |                            | Not internally connected. May be used for PCB trace routing.           |

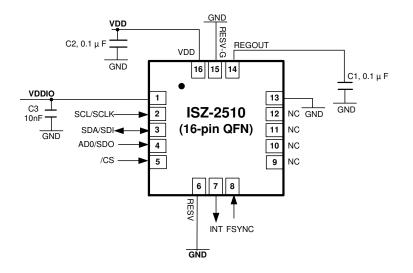

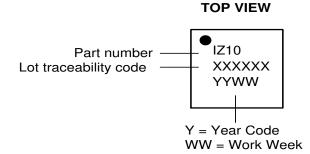

QFN Package (Top View) 16-pin, 3mm x 3mm x 0.90mm Footprint and maximum thickness

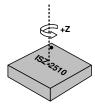

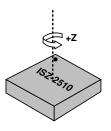

Orientation of Axes of Sensitivity and Polarity of Rotation

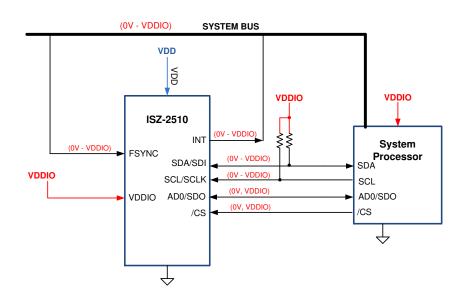

## 4.2 Typical Operating Circuit

## **Typical Operating Circuit**

#### 4.3 Bill of Materials for External Components

| Component                  | Label | Specification                | Quantity |

|----------------------------|-------|------------------------------|----------|

| Regulator Filter Capacitor | C1    | Ceramic, X7R, 0.1µF ±10%, 2V | 1        |

| VDD Bypass Capacitor       | C2    | Ceramic, X7R, 0.1µF ±10%, 4V | 1        |

| VDDIO Bypass Capacitor     | C3    | Ceramic, X7R, 10nF ±10%, 4V  | 1        |

## 5 Functional Overview

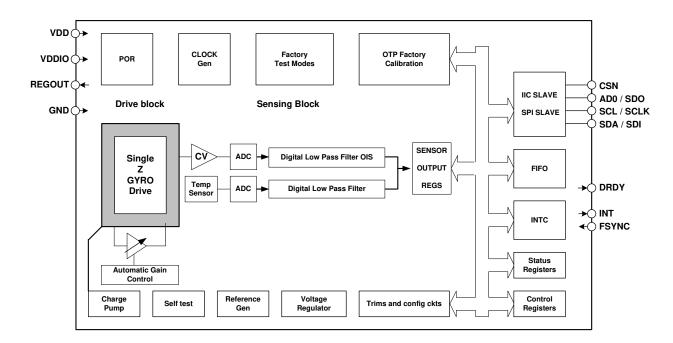

### 5.1 Block Diagram

#### 5.2 Overview

The ISZ-2510 is comprised of the following key blocks / functions:

- Single-axis MEMS rate gyroscope sensor with 16-bit ADCs and signal conditioning

- I<sup>2</sup>C and SPI serial communications interfaces

- Clocking

- Sensor Data Registers

- FIFO

- Interrupts

- Digital-Output Temperature Sensor

- Bias and LDO

#### 5.3 Single-Axis MEMS Gyroscope with 16-bit ADCs and Signal Conditioning

The ISZ-2510 consists of a single structure vibratory MEMS rate gyroscope, which detects rotation about the Z axis. When the gyro is rotated about any of the sense axes, the Coriolis Effect causes a vibration that is detected by a capacitive pick off. The resulting signal is amplified, demodulated, and filtered to produce a voltage that is proportional to the angular rate. This voltage is digitized using individual on-chip 16-bit Analog-to-Digital Converters (ADCs) to sample each axis. The chip features a programmable full-scale range of the gyro sensors of ±250, ±500, ±1000, and ±2000 dps. User-selectable low-pass filters enable a wide range of cut-off frequencies. The ADC sample rate can be programmed to 32 kHz, 8 kHz, 1 kHz, 500 Hz, 333.3 Hz, 250 Hz, 200 Hz, 166.7 Hz, 142.9 Hz, or 125 Hz.

#### 5.4 I<sup>2</sup>C and SPI Serial Communications Interface

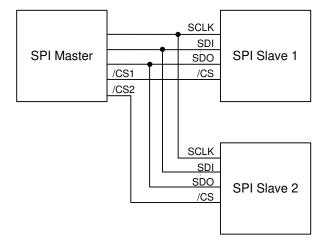

The ISZ-2510 has both  $I^2C$  and SPI serial interfaces. The device always acts as a slave when communicating to the system processor. The logic level for communications to the master is set by the voltage on the VDDIO pin. The LSB of the of the  $I^2C$  slave address is set by the AD0 pin. The  $I^2C$  and SPI protocols are described in more detail in Section 6.

#### 5.5 Internal Clock Generation

The ISZ-2510 has a flexible clocking scheme, allowing for a variety of internal clock sources for the internal synchronous circuitry. This synchronous circuitry includes the signal conditioning and ADCs, various control circuits, and registers.

Allowable internal sources for generating the internal clock are:

- An internal relaxation oscillator

- PLL (gyroscope based clock)

In order for the gyroscope to perform to spec, the PLL must be selected as the clock source. When the internal 20MHz oscillator is chosen as the clock source, the device can operate while having the gyroscopes disabled. However, this is only recommended if the user wishes to use the internal temperature sensor in this mode.

#### 5.6 Sensor Data Registers

The sensor data registers contain the latest gyro and temperature data. They are read-only registers, and are accessed via the Serial Interface. Data from these registers may be read anytime, however, the interrupt function may be used to determine when new data is available.

#### 5.7 FIFO

The ISZ-2510 contains a 512-byte FIFO register that is accessible via the both the I<sup>2</sup>C and SPI Serial Interfaces. The FIFO configuration register determines what data goes into it, with possible choices being gyro data, temperature readings and FSYNC input. A FIFO counter keeps track of how many bytes of valid data are contained in the FIFO. The FIFO register supports burst reads. The interrupt function may be used to determine when new data is available.

#### 5.8 Interrupts

Interrupt functionality is configured via the Interrupt Configuration register. Items that are configurable include the INT pin configuration, the interrupt latching and clearing method, and triggers for the interrupt. Items that can trigger an interrupt are (1) Clock generator locked to new reference oscillator (used when switching clock sources), (2) new data is available to be read (from the FIFO and Data registers), and (3) FIFO overflow. The interrupt status can be read from the Interrupt Status register.

#### 5.9 Digital-Output Temperature Sensor

An on-chip temperature sensor and ADC are used to measure the device's die temperature. The readings from the ADC can be read from the FIFO or the Sensor Data registers.

#### 5.10 Bias and LDO

The bias and LDO section generates the internal supply and the reference voltages and currents required by the ISZ-2510. Its two inputs are unregulated VDD of 1.71V to 3.6V and a VDDIO logic reference supply voltage of 1.71V to 3.6V. The LDO output is bypassed by a  $0.1\mu$ F capacitor at REGOUT.

## 6 Digital Interface

### 6.1 I<sup>2</sup>C Serial Interface

The internal registers and memory of the ISZ-2510 can be accessed using the I<sup>2</sup>C interface.

#### Serial Interface

| Pin Number | Pin Name   | Pin Description                                                        |

|------------|------------|------------------------------------------------------------------------|

| 1          | VDDIO      | Digital I/O supply voltage.                                            |

| 4          | AD0 / SDO  | I <sup>2</sup> C Slave Address LSB (AD0); SPI serial data output (SDO) |

| 2          | SCL / SCLK | I <sup>2</sup> C serial clock (SCL); SPI serial clock (SCLK)           |

| 3          | SDA / SDI  | I <sup>2</sup> C serial data (SDA); SPI serial data input (SDI)        |

## 6.1.1 I<sup>2</sup>C Interface

$I^2C$  is a two-wire interface comprised of the signals serial data (SDA) and serial clock (SCL). In general, the lines are open-drain and bi-directional. In a generalized  $I^2C$  interface implementation, attached devices can be a master or a slave. The master device puts the slave address on the bus, and the slave device with the matching address acknowledges the master.

The ISZ-2510 always operates as a slave device when communicating to the system processor, which thus acts as the master. SDA and SCL lines typically need pull-up resistors to VDD. The maximum bus speed is 400 kHz.

The slave address of the device is b110100X which is 7 bits long. The LSB bit of the 7 bit address is determined by the logic level on pin AD0. This allows two ISZ-2510 devices to be connected to the same  $I^2C$  bus. When used in this configuration, the address of the one of the devices should be b1101000 (pin AD0 is logic low) and the address of the other should be b1101001 (pin AD0 is logic high). The  $I^2C$  address is stored in WHO\_AM\_I register.