Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

ITS4200S-SJ-D

Smart High-Side NMOS-Power Switch

Data Sheet

Rev 1.0, 2012-09-01

Standard Power

## **Smart High-Side NMOS-Power Switch**

ITS4200S-SJ-D

## 1 Overview

#### **Features**

- · CMOS compatible input

- Switching all types of resistive, inductive and capacitive loads

- · Fast demagnetization of inductive loads

- Very low standby current

- Optimized Electromagnetic Compatibility (EMC)

- · Open drain diagnostic output for overtemperature and short circuit

- · Open load detection in OFF-state with external resistor

- Overload protection

- Current limitation

- · Short circuit protection

- · Thermal shutdown with restart

- Overvoltage protection (including load dump)

- Reverse battery protection with external resistor

- Loss of GND and loss of Vbb protection

- Electrostatic Discharge Protection (ESD)

- Green Product (RoHS compliant)

ITS4200S-SJ-D is not qualified and manufactured according to the requirements of Infineon Technologies with regards to automotive and/or transportation applications.

The ITS4200S-SJ-D is a protected 200m  $\Omega$  single channel Smart High-Side NMOS-Power Switch in a PG-DSO-8 package with charge pump, CMOS compatible input and diagnostic feedback.

#### **Product Summary**

Overvoltage protection  $V_{\rm SAZmin}$ = 62V Operating voltage range: 6V <  $V_{\rm S}$ < 52V On-state resistance  $R_{\rm DSON}$  = typ 150m $\Omega$  Nominal load current  $I_{\rm LNOM}$ = 1.2A

Operating Temperature range:  $T_i = -40$ °C to 125°C

Application

- All types of resistive, inductive and capacitive loads

- Power switch for 12V, 24V and 45V DC applications with CMOS compatible control interface

- · Open drain diagnosis feedback for overtemperature and short circuit

- Driver for electromagnetic relays

- Power managment for high-side-switching with low current consumption in OFF-mode

| Туре          | Package  | Marking |

|---------------|----------|---------|

| ITS4200S-SJ-D | PG-DSO-8 | I200SD  |

PG-DSO-8

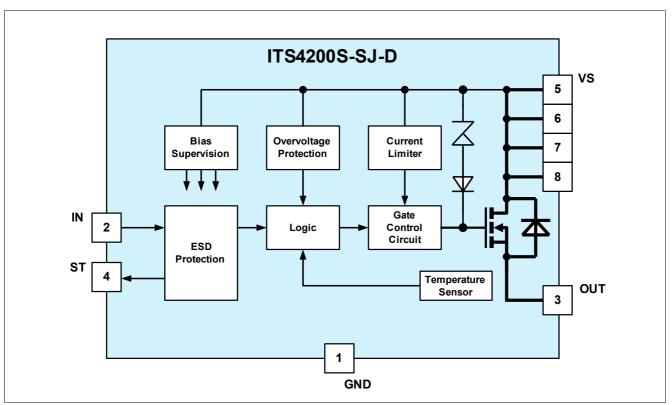

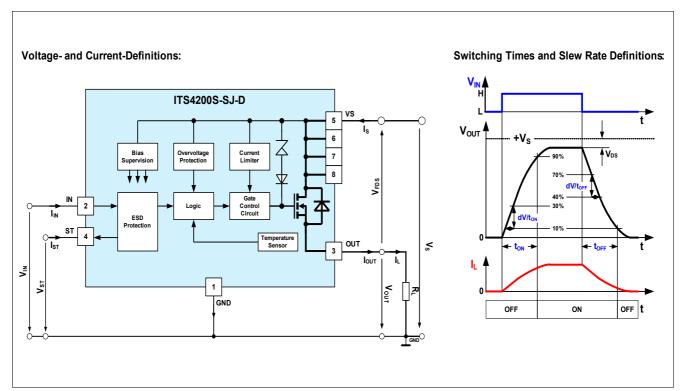

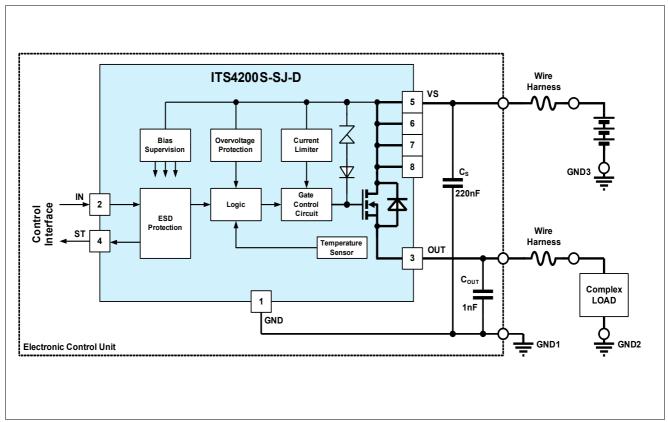

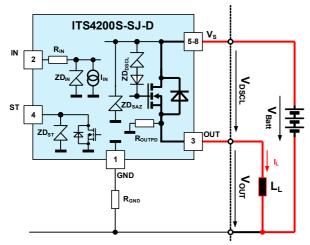

**Block Diagram and Terms**

## 2 Block Diagram and Terms

Figure 1 Block diagram

Figure 2 Terms - parameter definition

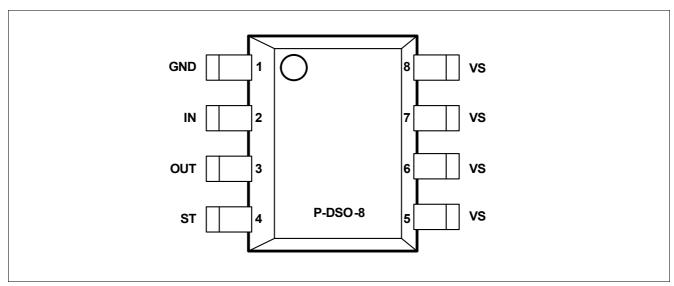

**Pin Configuration**

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 3 Pin configuration top view, PG-DSO-8

## 3.2 Pin Definitions and Functions

| Pin        | Symbol | Function                                                                                                     |

|------------|--------|--------------------------------------------------------------------------------------------------------------|

| 1          | GND    | Logic ground                                                                                                 |

| 2          | IN     | Input, controles the power switch; the powerswitch is ON when high                                           |

| 3          | OUT    | Output to the load                                                                                           |

| 4          | ST     | Status flag; diagnosis feedback; NMOS open drain                                                             |

| 5, 6, 7, 8 | VS     | Supply voltage (design the wiring for the maximum short circuit current and also for low thermal resistance) |

**General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

Table 1 Absolute maximum ratings  $^{1)}$  at  $T_j$  = 25°C unless otherwise specified. Currents flowing into the device unless otherwise specified in chapter "Block Diagram and Terms"

| Parameter                                                              | Symbol             |              | Value | s               | Unit | Note /<br>Test Condit<br>ion | Number   |

|------------------------------------------------------------------------|--------------------|--------------|-------|-----------------|------|------------------------------|----------|

|                                                                        |                    | Min.         | Тур.  | Max.            |      |                              |          |

| Supply voltage VS                                                      |                    |              |       | 1               | 1    | -                            |          |

| Voltage                                                                | $V_{S}$            |              |       | 52              | V    |                              | 4.1.1    |

| Voltage for short circuit protection                                   | $V_{SSC}$          |              |       | 36              | V    |                              | 4.1.2    |

| Output stage OUT                                                       |                    |              |       |                 |      | ,                            |          |

| Output Current; (Short circuit current see electrical characteristics) | $I_{OUT}$          |              |       | self<br>limited | А    |                              | 4.1.3    |

| Input IN                                                               | <u> </u>           | 1            | - 1   |                 |      |                              | 1        |

| Current                                                                | $I_{IN}$           | -5           |       | 5               | mA   |                              | 4.1.4    |

| Status ST                                                              | <del></del> !      | <del>!</del> | •     | •               | *    | •                            | <u>.</u> |

| Current                                                                | $I_{ST}$           | -5           |       | 5               | mA   |                              | 4.1.5    |

| Temperatures                                                           |                    |              |       |                 |      | ,                            |          |

| Junction Temperature                                                   | $T_{\rm j}$        | -40          |       | 125             | °C   |                              | 4.1.6    |

| Storage Temperature                                                    | $T_{\mathrm{stg}}$ | -55          |       | 125             | °C   |                              | 4.1.7    |

| Power dissipation                                                      |                    |              |       |                 |      |                              |          |

| Ta = 25 °C <sup>2)</sup>                                               | $P_{\text{tot}}$   |              |       | 1.4             | W    |                              | 4.1.8    |

| Inductive load switch-off energy dissipa                               | tion               |              |       |                 |      |                              |          |

| Tj = 125 °C; IL= 1A <sup>3)</sup>                                      | $E_{AS}$           |              |       | 125             | mJ   | single pulse                 | 4.1.9    |

| ESD Susceptibility                                                     | <u> </u>           |              |       | •               | •    |                              | •        |

| ESD susceptibility (input pin)                                         | $V_{ESD}$          | -1           |       | 1               | kV   | HBM <sup>4)</sup>            | 4.1.10   |

| ESD susceptibility (all other pins)                                    | $V_{ESD}$          | -5           |       | 5               | kV   | HBM <sup>5)</sup>            | 4.1.11   |

<sup>1)</sup> Not subject to production test, specified by design

Note: Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" the normal operating range. Protection functions are neither designed for continuous nor repetitive operation.

Data Sheet 5 Rev 1.0, 2012-09-01

<sup>2)</sup> Device on 50mm\*50mm\*1.5mm epoxy PCB FR4 with 6 cm2 (one layer, 70mm thick) copper area for Vbb connection. PCB is vertical without blown air

<sup>3)</sup> Not subject to production test, specified by design

<sup>4)</sup> ESD susceptibility HBM according to EIA/JESD 22-A 114.

<sup>5)</sup> ESD susceptibility HBM according to EIA/JESD 22-A 114.

## **General Product Characteristics**

## 4.2 Functional Range

Table 2 Funtional Range

| Parameter                 | Symbol  |      | Values |      | Unit | Note /                 | Number |

|---------------------------|---------|------|--------|------|------|------------------------|--------|

|                           |         | Min. | Тур.   | Max. |      | Test Condition         |        |

| Nominal Operating Voltage | $V_{S}$ | 6    |        | 52   | V    | $V_{\rm S}$ increasing | 4.2.1  |

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

Table 3 Thermal Resistance<sup>1)</sup>

| Parameter                                                           | Symbol                       |      | Values | ;    | Unit | Note /<br>Test Condition | Number |

|---------------------------------------------------------------------|------------------------------|------|--------|------|------|--------------------------|--------|

|                                                                     |                              | Min. | Тур.   | Max. |      |                          |        |

| Thermal Resistance - Junction to pin5                               | $R_{ m thj-pin5}$            |      | 23.3   |      | K/W  |                          | 4.3.1  |

| Thermal Resistance - Junction to Ambient - 1s0p, minimal footprint  | $R_{ m thJA\_1s0p}$          |      | 128.7  |      | K/W  | 2)                       | 4.3.2  |

| Thermal Resistance - Junction to Ambient - 1s0p, 300mm <sup>2</sup> | R <sub>thJA_1s0p_300mm</sub> |      | 70.1   |      | K/W  | 3)                       | 4.3.3  |

| Thermal Resistance - Junction to Ambient - 1s0p, 600mm <sup>2</sup> | R <sub>thJA_1s0p_600mm</sub> |      | 65.6   |      | K/W  | 4)                       | 4.3.4  |

| Thermal Resistance - Junction to Ambient - 2s2p                     | $R_{\mathrm{thJA\_2s2p}}$    |      | 55.4   |      | K/W  | 5)                       | 4.3.5  |

| Thermal Resistance - Junction to Ambient with thermal vias - 2s2p   | R <sub>thJA_2s2p</sub>       |      | 53.5   |      | K/W  | 6)                       | 4.3.6  |

- 1) Not subject to production test, specified by design

- 2) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, footprint; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 3) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, Cu, 300mm<sup>2</sup>; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 4) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-3 at natural convection on FR4 1s0p board, 600mm<sup>2</sup>; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 1x 70 $\mu$ m Cu.

- 5) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu).

- 6) Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board with two thermal vias; the Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70μm Cu, 2 x 35μm Cu. The diameter of the two vias are equal 0.3mm and have a plating of 25um with a copper heatsink area of 3mm x 2mm). JEDEC51-7: The two plated-through hole vias should have a solder land of no less than 1.25 mm diameter with a drill hole of no less than 0.85 mm diameter.

Data Sheet 6 Rev 1.0, 2012-09-01

**Electrical Characteristics**

## **5** Electrical Characteristics

Table 4  $V_{\rm S}$  = 12V to 42V;  $T_{\rm j}$  = -40°C to 125°C; all voltages with respect to ground, currents flowing into the device unless otherwise specified in chapter "Block Diagram and Terms". Typical values at  $V_{\rm s}$  = 13.5V,  $T_{\rm i}$  = 25°C

| Parameter                                                                                                  | Symbol              | Values  |      |      | Unit   | Note /                                                                                                                                                          | Number |

|------------------------------------------------------------------------------------------------------------|---------------------|---------|------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                            |                     | Min.    | Тур. | Max. |        | Test Condition                                                                                                                                                  |        |

| Powerstage                                                                                                 |                     | 1       | 1    |      |        |                                                                                                                                                                 |        |

| NMOS ON Resistance                                                                                         | $R_{DSON}$          |         | 150  | 200  | mΩ     | $\begin{split} I_{\rm OUT} &= {\rm 1A;} \ T_{\rm j} = 25^{\circ}{\rm C;} \\ 9{\rm V} &< V_{\rm S} < 52{\rm V;} \\ V_{\rm IN} &= 5{\rm V} \end{split}$           | 5.0.1  |

| NMOS ON Resistance                                                                                         | $R_{DSON}$          |         | 250  | 350  | mΩ     | $\begin{split} I_{\text{OUT}} &= \text{1A; } T_{\text{j}} = \text{125°C;} \\ 9\text{V} &< V_{\text{S}} < \text{52V;} \\ V_{\text{IN}} &= \text{5V} \end{split}$ | 5.0.2  |

| Nominal Load Current; device on PCB <sup>1)</sup>                                                          | $I_{LNOM}$          | 1.2     |      |      | А      | $T_{\text{pin5}}$ = 85°C                                                                                                                                        | 5.0.3  |

| Timings of Power Stages <sup>2)</sup>                                                                      |                     | 1       | ļ.   |      |        |                                                                                                                                                                 | 1      |

| Turn ON Time(to 90% of $V_{\rm out}$ ); $V_{\rm S}$ to GND transition of $V_{\rm IN}$                      | $t_{ON}$            |         | 80   | 180  | μs     | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                                                                                                   | 5.0.4  |

| Turn OFF Time (to 10% of $V_{\rm out}$ ); $V_{\rm S}$ to GND transition of $V_{\rm IN}$                    | $t_{OFF}$           |         | 80   | 200  | μs     | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                                                                                                   | 5.0.5  |

| ON-Slew Rate (10 to 30% of $V_{\rm out}$ ); L to H transition of $V_{\rm IN}$                              | SR <sub>ON</sub>    |         | 0.7  | 2.0  | V/µs   | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                                                                                                   | 5.0.6  |

| OFF-Slew Rate; $dV_{\rm OUT}/dt_{\rm ON}$ (70 to 40% of $V_{\rm out}$ ); H to L transition of $V_{\rm IN}$ | SR <sub>OFF</sub>   |         | 0.9  | 2.0  | V / µs | $V_{\rm S}$ =13.5V; $R_{\rm L}$ = 47 $\Omega$                                                                                                                   | 5.0.7  |

| Under voltage lockout (charge pur                                                                          | np start-sto        | p-resta | art) |      |        |                                                                                                                                                                 |        |

| Supply undervoltage; charge pump stop voltage                                                              | $V_{SUV}$           |         |      | 4    | V      | $V_{\rm S}$ decreasing -40°C < $T_{\rm i}$ < 85°C                                                                                                               | 5.0.8  |

| Supply undervoltage;<br>Charge pump stop voltage                                                           | $V_{SUV}$           |         |      | 5.5  | V      | $V_{\rm S}$ decreasing $T_{\rm i}$ = 125°C                                                                                                                      | 5.0.9  |

| Supply startup voltage; Charge pump restart voltage                                                        | $V_{SSU}$           |         | 4    | 5.5  | V      | $V_{\rm S}$ increasing                                                                                                                                          | 5.0.10 |

| Current consumption                                                                                        |                     |         |      |      |        |                                                                                                                                                                 |        |

| Operating current                                                                                          | $I_{GND}$           |         | 8.0  | 2    | mA     | $V_{IN}$ = 5V                                                                                                                                                   | 5.0.11 |

| Standby current                                                                                            | $I_{SSTB}$          |         |      | 15   | μΑ     | $V_{\text{IN}}$ = 0V; $V_{\text{OUT}}$ = 0V<br>-40°C < $T_{\text{i}}$ < 85°C                                                                                    | 5.0.12 |

| Standby current                                                                                            | $I_{\mathrm{SSTB}}$ |         |      | 18   | μA     | $V_{IN}$ = 0V; $T_{i}$ = 125°C                                                                                                                                  | 5.0.13 |

| Output leakage current                                                                                     | $I_{OUTLK}$         |         |      | 5    | μA     | $V_{\text{IN}}$ = 0V; $V_{\text{OUT}}$ = 0V                                                                                                                     | 5.0.14 |

| Protection functions 3)                                                                                    |                     |         |      |      |        |                                                                                                                                                                 |        |

| Initial peak short circuit current limit                                                                   | $I_{LSCP}$          |         |      | 9    | А      | $T_{\rm j}$ = -40°C; $V_{\rm S}$ = 20V; $V_{\rm IN}$ = 5.0V; $t_{\rm m}$ = 150 $\mu$ s                                                                          | 5.0.15 |

| Initial peak short circuit current limit                                                                   | $I_{LSCP}$          |         | 6.5  |      | Α      | $T_{\rm j}$ = 25°C; $V_{\rm S}$ = 20V; $V_{\rm IN}$ = 5.0V; $t_{\rm m}$ = 150 $\mu$ s                                                                           | 5.0.16 |

**Electrical Characteristics**

Table 4  $V_{\rm S}$  = 12V to 42V;  $T_{\rm j}$  = -40°C to 125°C; all voltages with respect to ground, currents flowing into the device unless otherwise specified in chapter "Block Diagram and Terms". Typical values at  $V_{\rm s}$  = 13.5V,  $T_{\rm j}$  = 25°C

| Parameter                                                                                         | r Symbol Values Min. Typ. Max. |     | S   | Unit                  | Note /   | Number                                                                                |        |

|---------------------------------------------------------------------------------------------------|--------------------------------|-----|-----|-----------------------|----------|---------------------------------------------------------------------------------------|--------|

|                                                                                                   |                                |     |     | <b>Test Condition</b> |          |                                                                                       |        |

| Initial peak short circuit current limit                                                          | $I_{LSCP}$                     | 4   |     |                       | А        | $T_{\rm j}$ =125°C; $V_{\rm S}$ = 20V; $V_{\rm IN}$ = 5.0V; $t_{\rm m}$ = 150 $\mu$ s | 5.0.17 |

| Initial peak short circuit current limit 4)                                                       | $I_{LSCP}$                     |     | 5   |                       | Α        | $V_{\rm S}$ > 40V; $V_{\rm IN}$ = 5.0V;<br>$t_{\rm m}$ = 150 $\mu{\rm s}$             | 5.0.18 |

| Repetitive short circuit current limit $T_{\rm i} = T_{\rm iTrip}$ ; see timing diagrams          | $I_{LSCR}$                     |     | 6   |                       | Α        | $V_{\rm IN}$ = 5.0V; $V_{\rm S}$ < 40V                                                | 5.0.19 |

| Repetitive short circuit current limit $T_{\rm j} = T_{\rm jTrip}$ ; see timing diagrams          | $I_{LSCR}$                     |     | 4.5 |                       | А        | $V_{\rm IN}$ = 5.0V; $V_{\rm S}$ > 40V                                                | 5.0.20 |

| Output clamp at $V_{\text{OUT}}$ = $V_{\text{S}}$ - $V_{\text{DSCL}}$ (inductive load switch off) | $V_{DSCL}$                     | 59  | 63  |                       | V        | $I_{\rm S}$ = 4mA                                                                     | 5.0.22 |

| Overvoltage protection $V_{\text{OUT}} = V_{\text{S}} - V_{\text{ONCL}}$                          | $V_{SAZ}$                      | 62  |     |                       | V        | $I_{\rm S}$ = 4mA                                                                     | 5.0.23 |

| Thermal overload trip temperature                                                                 | $T_{jTrip}$                    | 150 |     |                       | °C       |                                                                                       | 5.0.24 |

| Thermal hysteresis                                                                                | $T_{HYS}$                      |     | 10  |                       | K        |                                                                                       | 5.0.25 |

| Reverse Battery <sup>5)</sup>                                                                     | +                              |     | "   | "                     | -        |                                                                                       | +      |

| Continuous reverse battery voltage                                                                | $V_{SREV}$                     |     |     | 52                    | V        |                                                                                       | 5.0.26 |

| Forward voltage of the drain-source reverse diode                                                 | $V_{FDS}$                      |     | 600 |                       | mV       | $I_{\rm FDS}$ = 200mA;<br>$V_{\rm IN}$ = 0V; $T_{\rm j}$ = 125°C                      | 5.0.27 |

| Input interface; pin IN                                                                           |                                | 1   | "   | "                     |          | ,                                                                                     | 1      |

| Input turn-ON threshold voltage                                                                   | $V_{INON}$                     | 2.2 |     |                       | V        |                                                                                       | 5.0.28 |

| Input turn-OFF threshold voltage                                                                  | $V_{INOFF}$                    |     |     | 8.0                   | V        |                                                                                       | 5.0.29 |

| Input threshold hysteresis                                                                        | $V_{INHYS}$                    |     | 0.4 |                       | V        |                                                                                       | 5.0.30 |

| Off state input current                                                                           | $I_{INOFF}$                    | 1   |     | 25                    | μA       | $V_{IN} = 0.7V$                                                                       | 5.0.31 |

| On state input current                                                                            | $I_{INON}$                     | 3   |     | 25                    | μA       | V <sub>IN</sub> = 5.0V                                                                | 5.0.32 |

| Input resistance                                                                                  | $R_{IN}$                       | 2.0 | 3.5 | 5.0                   | kΩ       |                                                                                       | 5.0.33 |

| Status output (NMOS open drain); pi                                                               | n ST                           |     |     | •                     |          |                                                                                       |        |

| Status output zener voltage                                                                       | $V_{STZ}$                      | 5.4 | 6.1 | 6.8                   | V        | $I_{\rm ST}$ = 1.6mA                                                                  | 5.0.34 |

| Status output low voltage                                                                         | $V_{STLO}$                     |     |     | 0.4                   | V        | $I_{ST}$ = 1.6mA; $T_{j}$ < 25°C                                                      | 5.0.35 |

| Status output low voltage                                                                         | $V_{\mathrm{STLO}}$            |     |     | 0.6                   | V        | $I_{\rm ST}$ = 1.6mA<br>$T_{\rm j}$ < 125°C                                           | 5.0.36 |

| Status leakage current                                                                            | $I_{STLK}$                     |     |     | 2                     | μA       | $V_{\rm ST}$ = 5V; $T_{\rm i}$ < 105°C                                                | 5.0.37 |

| Status invalid time after positive input slope <sup>6)7)</sup>                                    | $t_{\sf dP}$                   |     | 120 | 160                   | μs       | V <sub>S</sub> = 13.5V                                                                | 5.0.38 |

| Status invalid time after negative input slope <sup>8)9)</sup>                                    | $t_{\sf dN}$                   |     | 250 | 400                   | μs       | V <sub>S</sub> = 13.5V                                                                | 5.0.39 |

| Diagnostic characteristics                                                                        | ı                              | 1   |     |                       | <u> </u> | 1                                                                                     | 1      |

| Short circuit detection voltage                                                                   | $V_{OUTSC}$                    |     | 2.8 |                       | V        |                                                                                       | 5.0.40 |

| Open load detection voltage <sup>10)</sup>                                                        | $V_{OUTOL}$                    |     | 3   | 4                     | V        |                                                                                       | 5.0.41 |

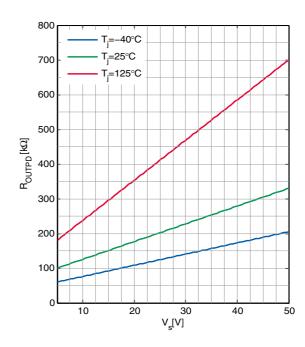

| Internal pull down resistor <sup>11)</sup>                                                        | $R_{OUTPD}$                    |     | 200 |                       | kΩ       | $V_{OUT}$ = 4V                                                                        | 5.0.42 |

|                                                                                                   |                                |     |     |                       |          |                                                                                       |        |

Data Sheet 8 Rev 1.0, 2012-09-01

#### **Electrical Characteristics**

- 1) Device on 50mm x 50mm x 1,5mm epoxy FR4 PCB with 6cm² (one layer copper 70um thick) copper area for supply voltage connection. PCB in vertical position without blown air.

- 2) Timing values only with high slewrate input signal; otherwise slower.

- 3) Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

- 4) No subject to production test; specified by design.

- 5) Requires a 150W resistor in GND connection. The reverse load current trough the intrinsic drain-source diode of the power-MOS has to be limited by the connected load. Power dissipation is higher compared to normal operation due to the votage drop across the drain-source diode. The temperature protection is not functional during reverse current operation! Input current has to be limited (see max ratings).

- 6) No delay time after overtemparature switch off and short circuit in on-state.

- 7) No subject to production test; specified by design.

- 8) No delay time after overtemparature switch off and short circuit in on-state.

- 9) No subject to production test; specified by design.

- 10) External pull up resistor required for open load detection in off state.

- 11) No subject to production test; specified by design.

Data Sheet 9 Rev 1.0, 2012-09-01

## **6** Typical Performance Graphs

## **Typical Characterisitics**

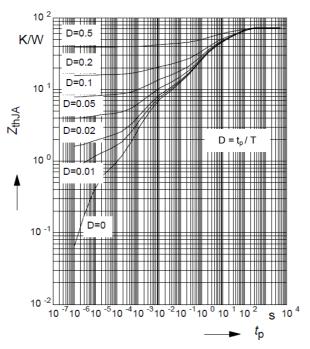

# Transient Thermal Impedance $Z_{\rm thJA}$ versus Pulse Time $t_{\rm p}$ @ 6cm² heatsink area

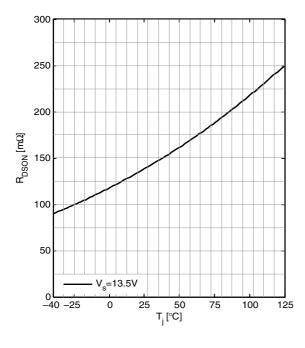

# On-Resistance $R_{\rm DSON}$ versus Junction Temperature $T_{\rm i}$

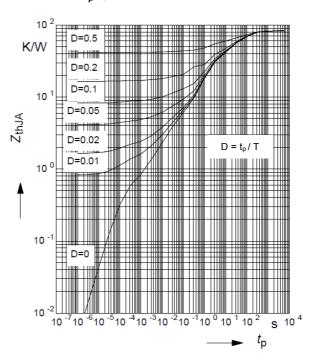

# Transient Thermal Impedance $Z_{thJA}$ versus Pulse Time $t_p$ @ min footprint

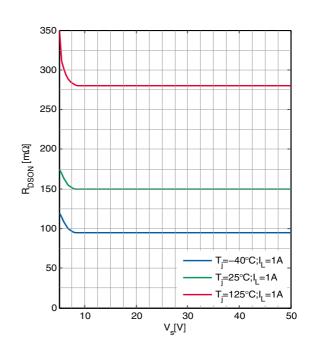

On-Resistance  $R_{\mathrm{DSON}}$  versus Supply Voltage  $V_{\mathrm{S}}$

## **Typical Characterisitics**

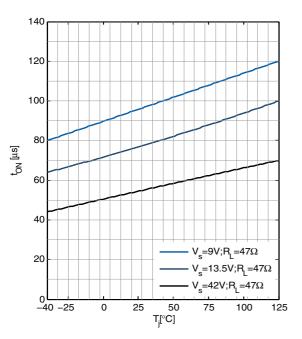

# Switch ON Time $t_{\rm ON}$ versus Junction Temperature $T_{\rm i}$

ON Slewrate  $SR_{ON}$  versus Junction Temperature  $T_{i}$

# Switch OFF Time $t_{\text{OFF}}$ versus Junction Temperature $T_{\text{j}}$

OFF Slewrate  $SR_{OFF}$  versus Junction Temperature  $T_i$

## **Typical Characterisitics**

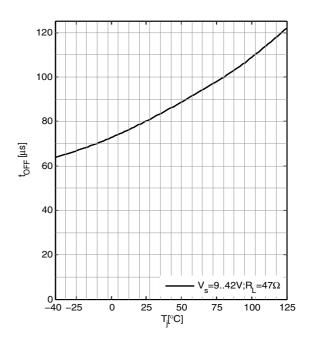

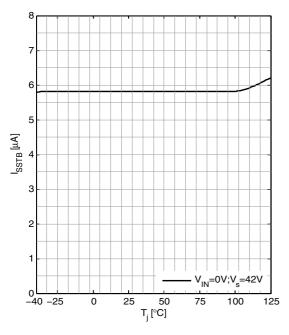

# Standby Current $I_{\rm SSTB}$ versus Junction Temperature $T_{\rm i}$

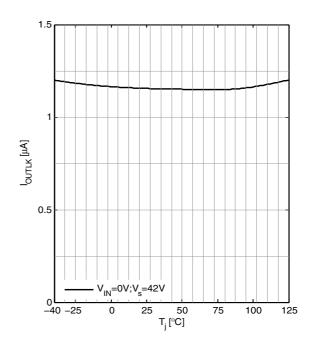

Output Leakage current  $I_{\rm OUTLK}$  versus Junction Temperature  $T_{\rm i}$

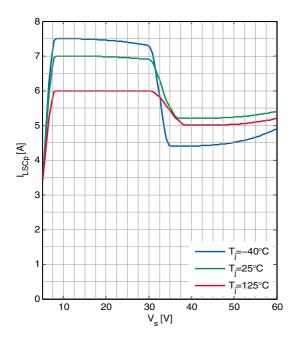

Initial Peak Short Circuit Current Limt  $I_{\rm LSCP}$  versus Junction Temperature  $T_{\rm i}$

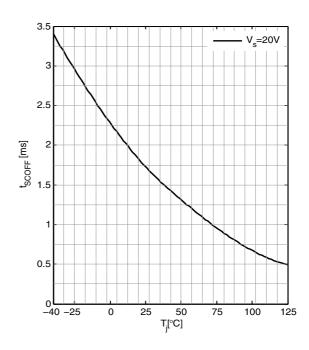

Initial Short Circuit Shutdown time  $t_{\rm SCOFF}$  versus Junction Temperature  $T_{\rm i}$

## **Typical Characterisitics**

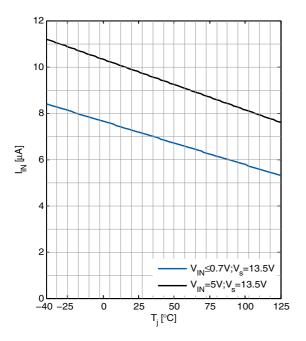

# Input Current Consumption $I_{\rm IN}$ versus Junction Temperature $T_{\rm j}$

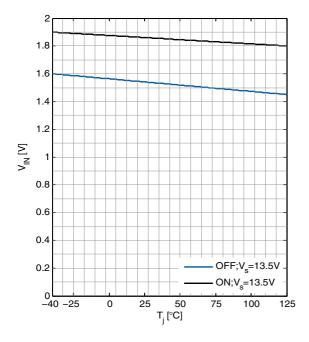

Input Threshold voltage  $V_{\mathrm{INH,L}}$  versus Junction Temperature  $T_{\mathrm{i}}$

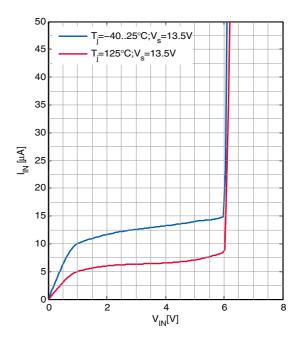

# Input Current Consumption $I_{\mathrm{IN}}$ versus Input voltage $V_{\mathrm{IN}}$

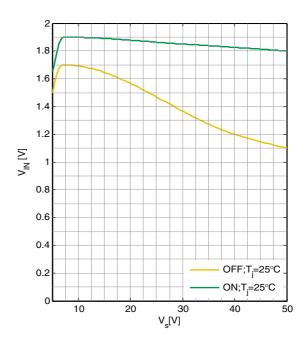

Input Threshold voltage  $V_{\rm INH,L}$  versus Supply Voltage  $V_{\rm S}$

## **Typical Characterisitics**

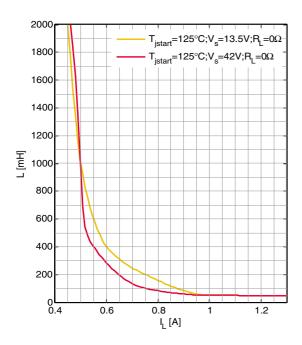

# Max. allowable Load Inductance L versus Load current $I_{\rm L}$

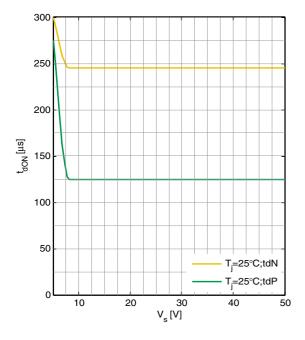

Status Delay Time  $t_{\rm N,\,P}$  versus Supply Voltage  $V_{\rm S}$

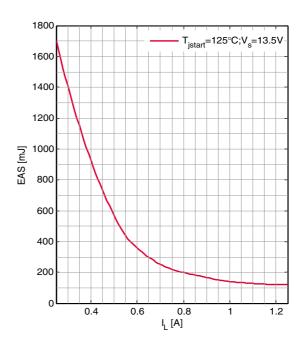

# Max. allowable Inductive single pulse Switch-off Energy $E_{\rm AS}$ versus Load current $I_{\rm L}$

Internal Output pull down Resistor  $R_{\mathrm{OUTOPD}}$  versus Supply Voltage  $V_{\mathrm{S}}$

## 7 Application Information

## 7.1 Application Diagram

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty for a certain functionality, condition or quality of the device.

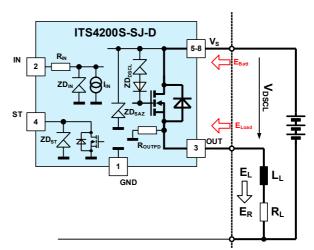

Figure 4 Application Diagram

The ITS4200S-SJ-D can be connected directly to the battery of a supply network. It is recommended to place a ceramic capacitor (e.g.  $C_S = 220$ nF) between supply and GND of the ECU to avoid line disturbances. Wire harness inductors/resistors are sketched in the application circuit above.

The complex load (resistive, capacitive or inductive) must be connected to the output pin OUT.

A built-in current limit protects the device against destruction.

The ITS4200S-SJ-D can be switched on and off with standard logic ground related logic signal at pin IN.

In standby mode (IN=L) the ITS4200S-SJ-D is deactivated with very low current consumption.

The output voltage slope is controlled during on and off transistion to minimize emissions. Only a small ceramic capacitor COUT=1nF is recommended to attenuate RF noise.

In the following chapters the main features, some typical waverforms and the protection behaviour of the ITS4200S-SJ-D is shown. For further details please refer to application notes on the Infineon homepage.

## 7.2 Diagnosis Description

For diagnostic purpose the device provides a digital output pin ST in order to indicate fault conditions.

The status output (ST) of the ITS4200S-SJ-D is a high voltage open drain output.

In "normal" operation mode the NMOS open drain transistor is switched OFF.

The following truth table defines the status output.

Table 5 Truth Table of diagnosis feature

| Device Operation                              | IN | OUT | ST | Comment                                                                               |

|-----------------------------------------------|----|-----|----|---------------------------------------------------------------------------------------|

| Normal Operation                              | L  | L   | Н  |                                                                                       |

| Normal Operation                              | Н  | Н   | Н  |                                                                                       |

| Short circuit to GND                          | L  | L   | Н  |                                                                                       |

| Short circuit to GND                          | Н  | L   | L  | OUT=L: $V_{\rm OUT}$ < $V_{\rm OUTSC}$ ;<br>Short circuit detection voltage; typ 2.8V |

| Short Circuit to V <sub>S</sub> (in OFF state | L  | Н   | L  |                                                                                       |

| Short Circuit to V <sub>S</sub> (in OFF state | Н  | Н   | Н  |                                                                                       |

| Overload                                      | L  | L   | Н  |                                                                                       |

| Overload                                      | Н  | Н   | Н  | OUT=H: $V_{\rm OUT}$ > $V_{\rm OUTSC}$ ;<br>Short circuit detection voltage; typ 2.8V |

| Overtemperature                               | L  | L   | Н  |                                                                                       |

| Overtemperature                               | Н  | L   | L  |                                                                                       |

| Open Load in OFF state                        | L  | Z   | Н  | OUT=Z: high impedance; potential depends on external circuit                          |

| Open Load in OFF state                        | L  | Н   | L  | with external resistor between $V_{\rm S}$ and OUT                                    |

## 7.3 Special Feature Description

## Supply over voltage:

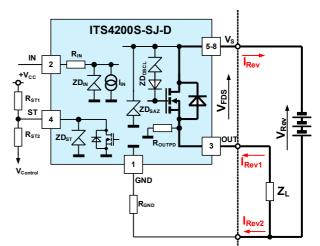

# ITS4200S-SJ-D IN 2 ZD<sub>IN</sub> ZD<sub>ST</sub> ZD<sub>ST</sub> R<sub>OUTPD</sub> 3 OUT R<sub>GND</sub> R<sub>GND</sub> ZL

If over-voltage is applied to the V<sub>S</sub>-Pin:

Voltage is limited to V<sub>ZDSAZ</sub>; current can be calculated:

$I_{ZDSAZ} = (V_S - V_{ZDSAZ}) / R_{GND}$

A typical value for RGND is 150  $\!\Omega.$

In case of ESD pulse on the input pin there is in both polarities a peak current  $I_{INpeak} \sim V_{ESD} / R_{IN}$

#### Supply reverse voltage:

If reverse voltage is applied to the device:

1.) Current via load resistance RL:

$I_{Rev1} = (V_{Rev} - V_{FDS}) / R_L$

2.) Current via Input pin IN and dignostic pin ST:

$$\begin{split} I_{Rev2} &= I_{ST} + I_{IN} \sim (V_{Rev} - V_{CC})/R_{IN} + (V_{Rev} - V_{CC})/R_{ST1,2} \\ \text{Current } I_{ST} \text{ must be limited with the extrernal series} \\ \text{resistor } R_{STS}. \text{ Both currents will sum up to:} \end{split}$$

$$I_{Rev} = I_{Rev1} + I_{Rev2}$$

## Drain-Source power stage clamper V<sub>DSCL</sub>:

When an inductive load is switched off a current path must be established until the current is sloped down to zero (all energy removed from the inductive load). For that purpose the series combination  $Z_{DSCL}$  is connected between Gate and Drain of the power DMOS acting as an active clamp.

When the device is switched off, the voltage at OUT turns negative until V<sub>DSCI</sub> is reached.

The voltage on the inductive load is the difference between  $V_{\text{DSCL}}$  and  $V_{\text{S}}.$

## **Energy calculation:**

Energy stored in the load inductance is given by :  $E_L = I_L^{2*}L/2$

While demagnetizing the load inductance the energy dissipated by the Power-DMOS is:

$$E_{AS} = E_S + E_L - E_R$$

With an approximate solution for  $R_L = 0\Omega$ :  $E_{AS} = \frac{1}{2} * L * I_L^2 * \{(1 - V_S / (V_S - V_{DSCL}))\}$

Figure 5 Special feature description

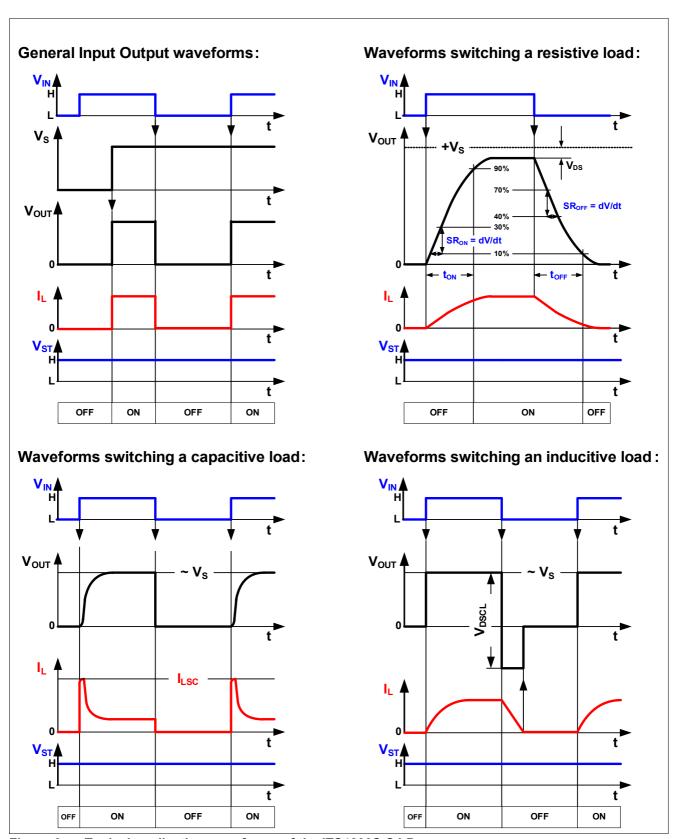

## 7.4 Typical Application Waveforms

Figure 6 Typical application waveforms of the ITS4200S-SJ-D

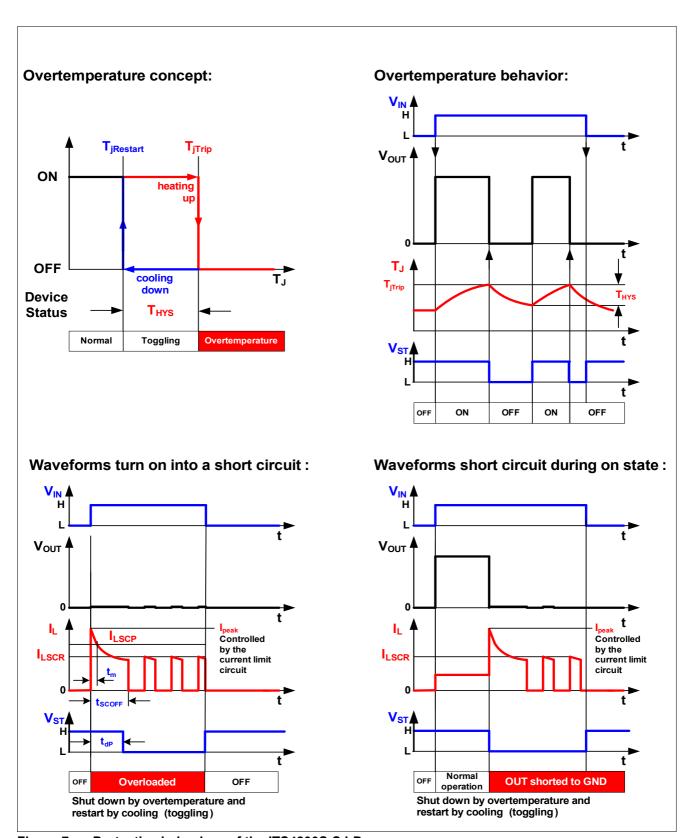

## 7.5 Protection Behavior

Figure 7 Protective behaviour of the ITS4200S-SJ-D

Package outlines and footprint

## 8 Package outlines and footprint

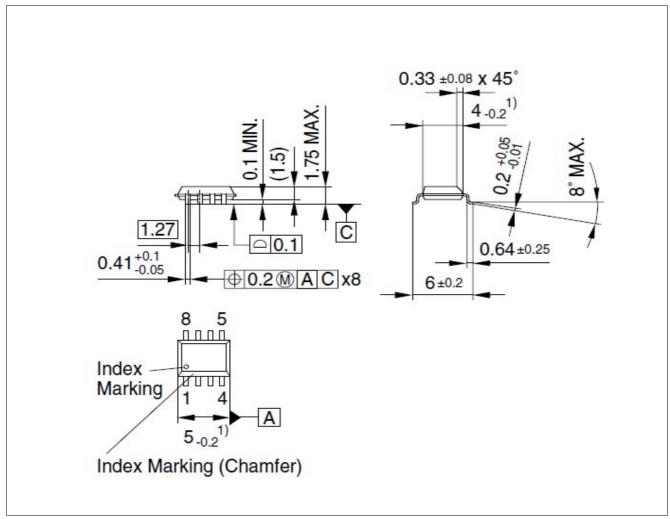

Figure 8 PG-DSO-8 (Plastic Dual Small Outline Package, RoHS-Compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020

**Revision History**

## 9 Revision History

| Revision | Date     | Changes           |

|----------|----------|-------------------|

| V 1.0    | 12-09-01 | Datasheet release |

|          |          |                   |

|          |          |                   |

|          |          |                   |

#### Trademarks of Infineon Technologies AG

AURIXTM, C166TM, Canpaktm, CIPOSTM, CIPURSETM, Econopacktm, CoolMostm, CoolSettm, Corecontroltm, Crossavetm, Davetm, DI-Poltm, EasyPIMTM, Econobridgetm, Econopualtm, Econopimtm, Econopacktm, Eicedrivertm, eupectm, Fcostm, Hitfettm, Hybridpacktm, I²Rftm, Isofacetm, Isopacktm, MIPaqtm, Modstacktm, my-dtm, NovalithIctm, OptiMostm, Origatm, Powercodetm; Primariontm, PrimePacktm, PrimeStacktm, Pro-Siltm, Profettm, Rasictm, Reversavetm, Satrictm, Siegettm, Sindriontm, Sipmostm, Smartlewistm, Solid Flashtm, Tempfettm, thinq!tm, Trenchstoptm, Tricoretm.

#### **Other Trademarks**

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2011-11-11

Edition 2012-09-01

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

The Infineon Technologies component described in this Data Sheet may be used in life-support devices or systems and/or automotive, aviation and aerospace applications or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support automotive, aviation and aerospace device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.