Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

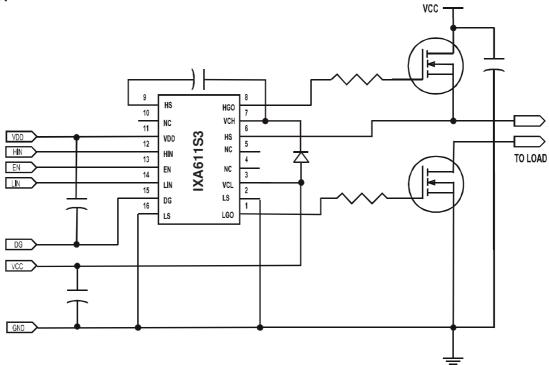

### 600mA Half-Bridge Driver

#### **Features**

- Floating High Side Driver with boot-strap Power supply along with a Low Side Driver.

- · Fully operational to 650V

- ± 50V/ns dV/dt immunity

- Gate drive power supply range: 10 35V

- · Undervoltage lockout for both output drivers

- Separate Logic power supply range: 3.3V to  $\rm V_{\rm cl}$

- Built using the advantages and compatibility of CMOS and IXYS HDMOS™ processes

- Latch-Up protected over entire operating range

- · High peak output current: 600 mA

- · Matched propagation delay for both outputs

- · Low output impedance

- · Low power supply current

- · Immune to negative voltage transients

Warning: The IXA611 is ESD sensitive.

### **General Description**

The IXA611 is a Bridge Driver for N-channel MOSFETs and IGBTs with a high side and low side output, whose input signals reference the low side. The High Side driver can control a MOSFET or IGBT connected to a positive buss voltage up to 650V. The logic input stages are compatible with TTL or CMOS, have built-in hysteresis and are fully immune to latch up over the entire operating range. The IXA611 can withstand dV/dt on the output side up to  $\pm$  50V/ns.

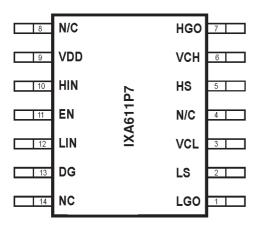

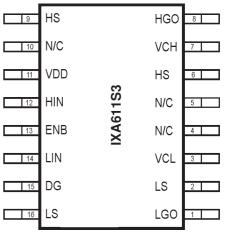

The IXA611 comes in either the 16-PIN SOIC package (IXA611S3) or the 14-PIN DIP through-hole package (IXA611P7)

### **Applications**

- Driving MOSFETs and IGBTs in half-bridge circuits

- · High voltage, high side and low side drivers

- Motor Controls

- Switch Mode Power Supplies (SMPS)

- DC to DC Converters

- · Class D Switching Amplifiers

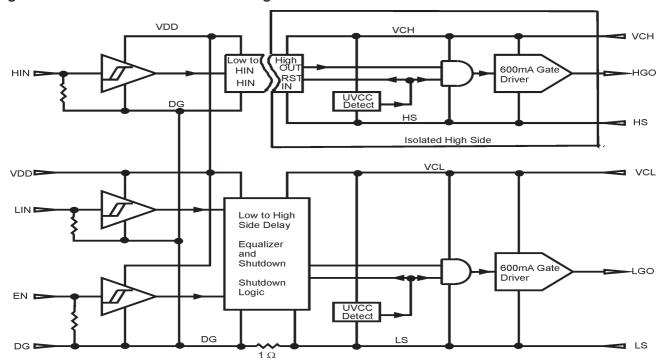

Figure 2 - IXA611 Functional Block Diagram

### **Pin Description And Configuration**

| SYMBOL | FUNCTION       | DESCRIPTION                                                  |

|--------|----------------|--------------------------------------------------------------|

| VDD    | Logic Supply   | Positive power supply for the chip CMOS functions            |

| HIN    | HS Input       | High side Input signal, TTL or CMOS compatible; HGO in phase |

| LIN    | LS Input       | Low side Input signal, TTL or CMOS compatible; LGO in phase  |

| ENB    | Enable         | Chip enable. When driven high, both outputs go low.          |

| DG     | Ground         | Logic Reference Ground                                       |

| VCH    | Supply Voltage | High Side Power Supply                                       |

| HGO    | Output         | High side driver output                                      |

| HS     | Return         | High side voltage return pin                                 |

| VCL    | Supply Voltage | Low side power supply. This power supply provides power for  |

|        |                | both outputs. Voltage range is from 4.5 to 25V.              |

| LGO    | Output         | Low side driver output                                       |

| LS     | Ground         | Low side return                                              |

| ·      |                |                                                              |

IXYS ICs are covered by US Patent No. 6,759,692

## **Absolute Maximum Ratings**

| Symbol            | Definition                                      | Min                  | Max                 | Units |

|-------------------|-------------------------------------------------|----------------------|---------------------|-------|

| V <sub>CH</sub>   | High side floating supply voltage               | -25                  | 650                 | V     |

| $V_{HS}$          | High side floating supply offset voltage        | V <sub>CH</sub> -200 | V <sub>CH</sub> +.3 | V     |

| $V_{HGO}$         | High side floating output voltage               | $V_{HS}$ 3           | $V_{CH}+.3$         | V     |

| $V_{CL}$          | Low side fixed supply voltage                   | -0.3                 | 35                  | V     |

| $V_{LGO}$         | Low side output voltage                         | -0.3                 | $V_{CL}+.3$         | V     |

| $V_{DD}$          | Logic supply voltage                            | -0.3                 | $V_{DG} + 35$       | V     |

| $V_{DG}$          | Logic supply offset voltage                     | $V_{LS}$ -3.8        | $V_{LS}$ +3.8       | V     |

| $V_{IN}$          | Logic input voltage(HIN & LIN)                  | $V_{SS}$ 3           | $V_{DD}+.3$         | V     |

| $dV_s/dt$         | Allowable offset supply voltage transient       |                      | 50                  | V/ns  |

| $P_{D}$           | Package power dissipation@ T <sub>A</sub> ≤ 25C |                      | 1                   | W     |

| $P_{D}$           | Package power dissipation@ T <sub>C</sub> ≤ 25C |                      | 2.1                 | W     |

| R <sub>THJA</sub> | Thermal resistance, junction-to-ambient         |                      | 125                 | K/W   |

| R <sub>THJc</sub> | Thermal resistance, junction-to-case            |                      | 60                  | K/W   |

| T <sub>J</sub>    | Junction Temperature                            |                      | 150                 | °C    |

| T <sub>s</sub>    | Storage temperature                             | -55                  | 150                 | °C    |

| T <sub>L</sub>    | Lead temperature (soldering, 10 s)              |                      | 300                 | °C    |

## **Recommended Operating Conditions**

| Symbol          | Definition                                 | Min                 | Max                  | Units |

|-----------------|--------------------------------------------|---------------------|----------------------|-------|

| V <sub>CH</sub> | High side floating supply absolute voltage | V <sub>HS</sub> +10 | V <sub>HS</sub> +20  | V     |

| V <sub>HS</sub> | High side floating supply offset voltage   | -20                 | 650                  | V     |

| $V_{HGO}$       | High side floating output voltage          | $V_{HS}$            | $V_{CH}+20$          | V     |

| V <sub>CL</sub> | Low side fixed supply voltage              | 10                  | 20                   | V     |

| $V_{LGO}$       | Low side output voltage                    | 0                   | $V_{cc}$             | V     |

| $V_{DD}$        | Logic supply voltage                       | $V_{DG} + 3$        | $V_{DG} + 20$        | V     |

| $V_{DG}$        | Logic supply voffset voltage               | $V_{LS}$ -1         | $V_{LS}+1$           | V     |

| V <sub>IN</sub> | Logic input voltage(HIN, LIN, ENbar)       | $V_{_{ m DG}}$      | $V_{_{\mathrm{DD}}}$ | V     |

| T <sub>A</sub>  | Ambient Temperature                        | -40                 | 125                  | °C    |

| Ordering Information |              |  |  |

|----------------------|--------------|--|--|

| Part Number          | Package Type |  |  |

| IXA611P7             | 14-PIN DIP   |  |  |

| IXA611S3             | 16-PIN SOIC  |  |  |

| ymbol | Definition                          | Test Conditions                    | Min | Тур | Max | Units |

|-------|-------------------------------------|------------------------------------|-----|-----|-----|-------|

|       | Turn-on propagation delay           | $V_{HS} = 0V, C_{load} = 2nF$      |     | 120 |     | ns    |

| ŧ     | Turn-off propagation delay          | $V_{HS} = 600V$ , $C_{load} = 2nF$ |     | 87  |     | ns    |

| 1     | Device enable delay                 |                                    |     | 202 |     | ns    |

|       | Turn-on rise time                   | $C_{load} = 2nF$                   |     | 23  |     | ns    |

|       | Turn-off fall time                  | C <sub>load</sub> = 2nF            |     | 22  |     | ns    |

| n     | Delay matching, HS & LS turn-on/off | C <sub>load</sub> = 2nF            |     | 50  |     | ns    |

| Static El           | lectrical Characteristics  Definition                         | Test Conditions                                 | Min | Тур   | Max | Units |

|---------------------|---------------------------------------------------------------|-------------------------------------------------|-----|-------|-----|-------|

| Cymbol              | Seminion                                                      | rest conditions                                 |     | ı yp  | Mux | Omis  |

| $V_{INH}$           | Logic "1" input voltage                                       | $V_{DD} = V_{CL} = 15V$                         | 7.0 |       |     | V     |

| V <sub>INL</sub>    | Logic "0" input voltage                                       |                                                 |     |       | 6   | V     |

|                     | GO High level output voltage,                                 | I <sub>0</sub> = 0A                             |     | 0.28  |     | V     |

|                     | $V_{CH}^{-}V_{HGO}^{-}$ or $V_{CL}^{-}V_{LGO}^{-}$            |                                                 |     |       |     |       |

| $V_{LLGO}/V_{LHG}$  | o High level output voltage,                                  | I <sub>0</sub> = 0A                             |     | .23   |     | V     |

|                     | $V_{HGO}$ or $V_{LGO}$                                        |                                                 |     |       |     |       |

| I <sub>HL</sub>     | HS to LS bias current.                                        | $V_{HS} = V_{CH} = 600V$                        |     | .17   |     | mA    |

| I <sub>QHS</sub>    | Quiescent V <sub>CH</sub> supply current                      | $V_{IN} = 0V \text{ or } V_{DD}$                |     | .77   |     | mA    |

| I <sub>QLS</sub>    | Quiescent V <sub>CL</sub> supply current                      | $V_{IN} = 0V \text{ or } V_{DD}$                |     | .79   |     | mA    |

| I <sub>QDD</sub>    | Quiescent V <sub>DD</sub> supply current                      | $V_{IN} = 0V \text{ or } V_{DD}$                |     | 36    |     | uA    |

| I <sub>IN</sub> +   | Logic "1" input bias current                                  | $V_{IN} = V_{DD}$                               |     | 2     |     | uA    |

| I <sub>IN</sub> -   | Logic "0" input voltage                                       | V <sub>IN</sub> = 0V                            |     | 1     |     | uA    |

| V <sub>CHUV</sub> + | V <sub>CH</sub> supply undervoltage positive going threshold. |                                                 |     | 8.3   |     | V     |

| V <sub>CHUV</sub> - | V <sub>CH</sub> supply undervoltage negative going threshold. |                                                 |     | 8.2   |     | V     |

| V <sub>CLUV</sub> + | V <sub>CL</sub> supply undervoltage positive going threshold  |                                                 |     | 8.1   |     | V     |

| V <sub>CLUV</sub> - | V <sub>CL</sub> supply undervoltage negative                  | e going threshold.                              |     | 8.0   |     | V     |

| I <sub>GO</sub>     | HS or LS Output low short circuit                             | current; $V_{GO}$ = 15V, $V_{IN}$ = 0V, PW<10us |     | ± 0.6 |     | Α     |

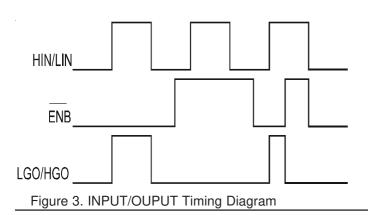

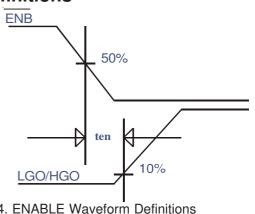

# **Timing Waveform Definitions**

Figure 4. ENABLE Waveform Definitions

### **Timing Waveform Definitions**

Figure 5. Definitions of Switching Time Waforms Figure 6. Definitions of Delay Matching Waveforms 50% 50% tenb HIN/LIN 50% tdoff LIN LG0 tenb **LOW SIDE** HGO/LGO tenb 50% **HGO**

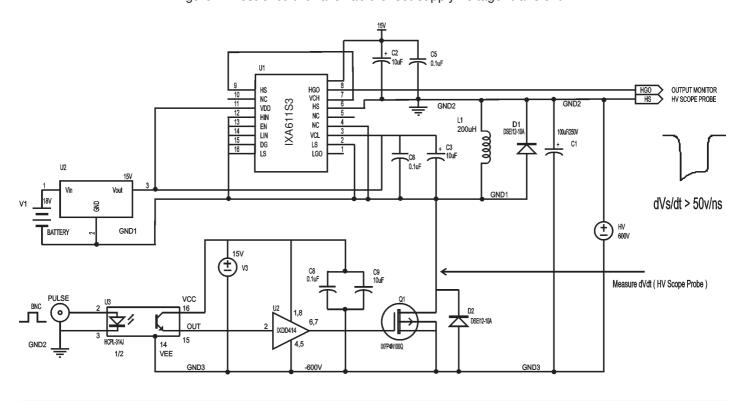

Figure 7. Test circuit for allowable offset supply voltage transient.

tenb

**HIGH SIDE**

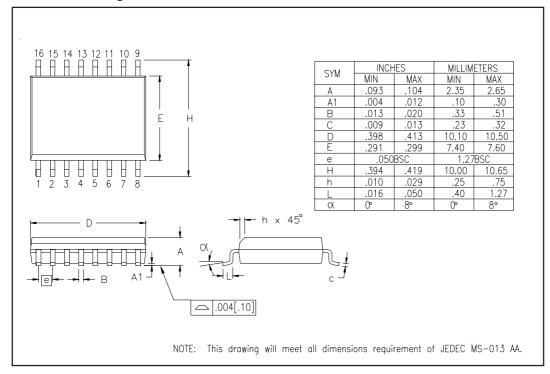

#### **IXA611S3 Package Outline**

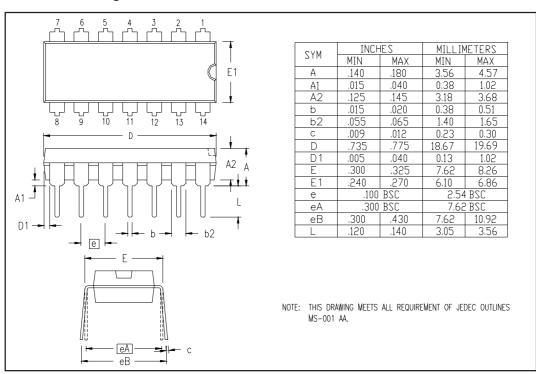

#### IXA611P7 Package Outline

IXYS Corporation 3540 Bassett St; Santa Clara, CA 95054 Tel: 408-982-0700; Fax: 408-496-0670 e-mail: sales@ixys.net

www.ixys.com

IXYS Semiconductor GmbH Edisonstrasse15; D-68623; Lampertheim Tel: +49-6206-503-0; Fax: +49-6206-503627 e-mail: marcom@ixys.de