Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

32-Bit

TC1797

32-Bit Single-Chip Microcontroller

Data Sheet V1.3 2014-08

Microcontrollers

Edition 2014-08

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2014 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

32-Bit

TC1797

32-Bit Single-Chip Microcontroller

Data Sheet V1.3 2014-08

Microcontrollers

#### TC1797 Data Sheet

## Revision History: V1.3, 2014-08

| Previous Version: V1.2, 2009-09 |                                                                                             |  |

|---------------------------------|---------------------------------------------------------------------------------------------|--|

| Page                            | Subjects (major changes since last revision)                                                |  |

| 6                               | add SAK-TC1797-512F180EF and SAK-TC1797-384F150EF.                                          |  |

| 185                             | add figure for new package P/PG-BGA-416-27.                                                 |  |

| all                             | add package P/PG-BGA-416-27 for new variants SAK-TC1797-512F180EF and SAK-TC1797-384F150EF. |  |

#### **Trademarks**

TriCore® is a trademark of Infineon Technologies AG.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

Data Sheet V1.3, 2014-08

## **Table of Contents**

## **Table of Contents**

| 1       | Summary of Features                                  | . 4 |

|---------|------------------------------------------------------|-----|

| 2       | Introduction                                         |     |

| 2.1     | About this Document                                  |     |

| 2.1.1   | Related Documentations                               |     |

| 2.1.2   | Text Conventions                                     | . 7 |

| 2.1.3   | Reserved, Undefined, and Unimplemented Terminology   |     |

| 2.1.4   | Register Access Modes                                |     |

| 2.1.5   | Abbreviations and Acronyms                           |     |

| 2.2     | System Architecture of the TC1797                    |     |

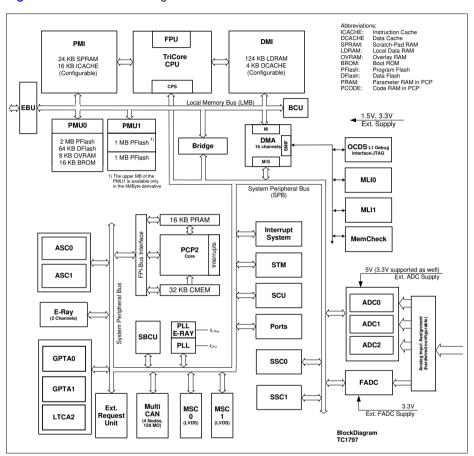

| 2.2.1   | TC1797 Block Diagram                                 |     |

| 2.2.2   | System Features                                      |     |

| 2.2.3   | CPU Cores of the TC1797                              |     |

| 2.2.3.1 | High-performance 32-bit CPU                          |     |

| 2.2.3.2 | High-performance 32-bit Peripheral Control Processor |     |

| 2.3     | On-Chip System Units                                 |     |

| 2.3.1   | Flexible Interrupt System                            |     |

| 2.3.2   | Direct Memory Access Controller                      |     |

| 2.3.3   | System Timer                                         |     |

| 2.3.4   | System Control Unit                                  | 22  |

| 2.3.4.1 | Clock Generation Unit                                |     |

| 2.3.4.2 | Features of the Watchdog Timer                       | 22  |

| 2.3.4.3 | Reset Operation                                      | 22  |

| 2.3.4.4 | External Interface                                   |     |

| 2.3.4.5 | Die Temperature Measurement                          |     |

| 2.3.5   | General Purpose I/O Ports and Peripheral I/O Lines   |     |

| 2.3.6   | Program Memory Unit (PMU)                            | 23  |

| 2.3.6.1 | Boot ROM                                             |     |

| 2.3.6.2 | Overlay RAM and Data Acquisition                     |     |

| 2.3.6.3 | Emulation Memory Interface                           |     |

| 2.3.6.4 | Tuning Protection                                    |     |

| 2.3.6.5 | Program and Data Flash                               |     |

| 2.3.7   | Data Access Overlay                                  |     |

| 2.4     | Development Support                                  |     |

| 2.5     | On-Chip Peripheral Units of the TC1797               |     |

| 2.5.1   | Asynchronous/Synchronous Serial Interfaces           |     |

| 2.5.2   | High-Speed Synchronous Serial Interfaces             |     |

| 2.5.3   | Micro Second Channel Interface                       |     |

| 2.5.4   | FlexRay™ Protocol Controller (Mod_Name)              |     |

| 2.5.4.1 | Mod_Name Kernel Description                          | 39  |

| 2.5.4.2 | Overview                                             |     |

## **Table of Contents**

| 2.5.5                                                                                                                  | MultiCAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                                                     |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 2.5.6                                                                                                                  | Micro Link Serial Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 2.5.7                                                                                                                  | General Purpose Timer Array (GPTA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

| 2.5.7.1                                                                                                                | Functionality of GPTA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 2.5.7.2                                                                                                                | Functionality of LTCA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 2.5.8                                                                                                                  | Analog-to-Digital Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| 2.5.8.1                                                                                                                | ADC Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

| 2.5.8.2                                                                                                                | FADC Short Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 2.5.9                                                                                                                  | External Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| 2.6                                                                                                                    | On-Chip Debug Support (OCDS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| 2.6.1                                                                                                                  | On-Chip Debug Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |

| 2.6.2                                                                                                                  | Real Time Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 2.6.3                                                                                                                  | Calibration Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                     |

| 2.6.4                                                                                                                  | Tool Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58                                                                                     |

| 2.6.5                                                                                                                  | Self-Test Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58                                                                                     |

| 2.6.6                                                                                                                  | FAR Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58                                                                                     |

| 3                                                                                                                      | Pinning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60                                                                                     |

| 3.1                                                                                                                    | TC1797 Pin Definition and Functions: P/PG-BGA-416-10 / P/PG-BGA-416-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|                                                                                                                        | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

| 3.1.1                                                                                                                  | TC1797 P/PG-BGA-416-27P/PG-BGA-416-10 / Package Variant Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

|                                                                                                                        | Configuration 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                        |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| 3.1.2                                                                                                                  | Pull-Up/Pull-Down Reset Behavior of the Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                                                     |

|                                                                                                                        | Pull-Up/Pull-Down Reset Behavior of the Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| 4                                                                                                                      | Identification Registers 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                     |

| 4<br>5                                                                                                                 | Identification Registers     1       Electrical Parameters     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25<br>27                                                                               |

| <b>4</b><br><b>5</b><br>5.1                                                                                            | Identification Registers1Electrical Parameters1General Parameters1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25<br>27<br>27                                                                         |

| <b>4</b><br><b>5</b><br>5.1<br>5.1.1                                                                                   | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>27<br>27                                                                         |

| <b>4</b><br><b>5</b><br>5.1<br>5.1.1<br>5.1.2                                                                          | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>27<br>27<br>27                                                                   |

| <b>4 5 5 5 1 5 1 5 1 5 1 2 5 1 3</b>                                                                                   | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25<br>27<br>27<br>27<br>28                                                             |

| <b>5</b> 5.1 5.1.1 5.1.2 5.1.3 5.1.4                                                                                   | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1                                                                                                                                                                                                                                                                                                                                                                                                                   | 25<br>27<br>27<br>27<br>28<br>29                                                       |

| 3.1.2<br>4<br>5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1                                             | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1                                                                                                                                                                                                                                                                                                                                                                                                     | 25<br>27<br>27<br>27<br>28<br>29                                                       |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2                                                                    | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1                                                                                                                                                                                                                                                                                                                                                                                   | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34                                           |

| 4<br>5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2                                             | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADCO/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1                                                                                                                                                                                                                                                                                             | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34                                     |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1                                                           | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADCO/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1                                                                                                                                                                                                                                                                                             | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34<br>38                               |

| 4<br>5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3                                    | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADCO/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1Oscillator Pins1Temperature Sensor1                                                                                                                                                                                                                                                          | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34<br>38<br>43                         |

| 4<br>5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                           | Identification Registers         1           Electrical Parameters         1           General Parameters         1           Parameter Interpretation         1           Pad Driver and Pad Classes Summary         1           Absolute Maximum Ratings         1           Operating Conditions         1           DC Parameters         1           Input/Output Pins         1           Analog to Digital Converters (ADCO/ADC1/ADC2)         1           Fast Analog to Digital Converter (FADC)         1           Oscillator Pins         1           Temperature Sensor         1 | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34<br>38<br>43<br>46                   |

| 4<br>5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                  | Identification RegistersElectrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADC0/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1Oscillator Pins1Temperature Sensor1Power Supply Current1AC Parameters1                                                                                                                                                                                                                        | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34<br>43<br>46<br>46<br>48             |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1          | Identification RegistersElectrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADC0/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1Oscillator Pins1Temperature Sensor1Power Supply Current1AC Parameters1Testing Waveforms1                                                                                                                                                                                                      | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34<br>46<br>46<br>48<br>50             |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2 | Identification Registers1Electrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADC0/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1Oscillator Pins1Temperature Sensor1Power Supply Current1AC Parameters1Testing Waveforms1Output Rise/Fall Times1                                                                                                                                                                              | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>34<br>46<br>48<br>48<br>50<br>51       |

| 5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                   | Identification RegistersElectrical Parameters1General Parameters1Parameter Interpretation1Pad Driver and Pad Classes Summary1Absolute Maximum Ratings1Operating Conditions1DC Parameters1Input/Output Pins1Analog to Digital Converters (ADC0/ADC1/ADC2)1Fast Analog to Digital Converter (FADC)1Oscillator Pins1Temperature Sensor1Power Supply Current1AC Parameters1Testing Waveforms1                                                                                                                                                                                                      | 25<br>27<br>27<br>27<br>28<br>29<br>30<br>34<br>38<br>43<br>46<br>48<br>50<br>51<br>51 |

## **Table of Contents**

| 5.3.5    | Phase Locked Loop (PLL)                         |

|----------|-------------------------------------------------|

| 5.3.6    | E-Ray Phase Locked Loop (E-Ray PLL)             |

| 5.3.7    | BFCLKO Output Clock Timing                      |

| 5.3.8    | JTAG Interface Timing                           |

| 5.3.9    | DAP Interface Timing                            |

| 5.3.10   | EBU Timings                                     |

| 5.3.10.1 | EBU Asynchronous Timings                        |

| 5.3.10.2 | EBU Burst Mode Access Timing 172                |

| 5.3.10.3 | EBU Arbitration Signal Timing                   |

| 5.3.11   | Peripheral Timings                              |

| 5.3.11.1 | Micro Link Interface (MLI) Timing               |

| 5.3.11.2 | Micro Second Channel (MSC) Interface Timing 178 |

| 5.3.11.3 | SSC Master/Slave Mode Timing 179                |

| 5.3.11.4 | E-Ray Interface Timing 181                      |

| 5.4      | Package and Reliability                         |

| 5.4.1    | Package Parameters                              |

| 5.4.2    | Package Outline 184                             |

| 5.4.3    | Flash Memory Parameters                         |

| 5.4.4    | Quality Declarations                            |

|          |                                                 |

#### **Summary of Features**

## 1 Summary of Features

- High-performance 32-bit super-scalar TriCore V1.3.1 CPU with 4-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Single precision Floating Point Unit (FPU)

- 180 or 150<sup>1)</sup> MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 180 or150<sup>1)</sup> MHz operation at full temperature range

- Multiple on-chip memories

- 4 or 31) Mbyte Program Flash Memory (PFLASH) with ECC

- 64 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 128 Kbyte Data Memory (LDRAM)

- 40 Kbyte Code Scratchpad Memory (SPRAM)

- Instruction Cache: up to 16 Kbyte (ICACHE, configurable)

- Data Cache: up to 4 Kbyte (DCACHE, configurable)

- 8 Kbyte Overlay Memory (OVRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- 32-bit External Bus Interface Unit (EBU) with

- 32-bit demultiplexed / 16-bit multiplexed external bus interface (3.3V, 2.5V)

- Support for Burst Flash memory devices

- Scalable external bus timing up to 75 MHz

- Sophisticated interrupt system with 2 x 255 hardware priority arbitration levels serviced by CPU or PCP2

- High performing on-chip bus structure

- 64-bit Local Memory Buses between CPU, EBU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridges (LFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Two High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Two serial Micro Second Bus interface (MSC) for serial port expansion to external power devices

Data Sheet 4 V1.3, 2014-08

<sup>1)</sup> Derivative dependent.

### **Summary of Features**

- Two High-Speed Micro Link interface (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer

- One FlexRay<sup>TM</sup> module with 2 channels (E-Ray).

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- 44 analog input lines for ADC

- 3 independent kernels (ADC0, ADC1, ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- Performance for 12 bit resolution ( $@f_{ADCI} = 10 \text{ MHz}$ )

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of  $f_{FADC}$  clock (262.5 ns @  $f_{FADC}$  = 80 MHz)

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 221 digital general purpose I/O lines<sup>1)</sup> (GPIO), 4 input lines

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Bus)

- Dedicated Emulation Device chip available (TC1797ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- Clock Generation Unit with PLL

- Core supply voltage of 1.5 V

- I/O voltage of 3.3 V

- Full automotive temperature range: -40° to +125°C

- Package variants: P/PG-BGA-416-10 and P/PG-BGA-416-27

Data Sheet 5 V1.3, 2014-08

<sup>1)</sup> TC1797 package variant P/PG-BGA-416-10 / P/PG-BGA-416-27: 86 GPIO's

#### **Summary of Features**

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- · The package and the type of delivery.

For the available ordering codes for the TC1797 please refer to the "**Product Catalog Microcontrollers**", which summarizes all available microcontroller variants.

This document describes the derivatives of the device. The **Table 1** enumerates these derivatives and summarizes the differences.

Table 1 TC1797 Derivative Synopsis

| Derivative           | Ambient<br>Temperature<br>Range                      | Program<br>Flash | CPU<br>frequency | Package         |

|----------------------|------------------------------------------------------|------------------|------------------|-----------------|

| SAK-TC1797-512F180E  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 4 MBytes         | 180MHz           | P/PG-BGA-416-10 |

| SAK-TC1797-384F150E  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 3 MBytes         | 150MHz           | P/PG-BGA-416-10 |

| SAK-TC1797-512F180EF | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 4 MBytes         | 180MHz           | P/PG-BGA-416-27 |

| SAK-TC1797-384F150EF | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 3 MBytes         | 150MHz           | P/PG-BGA-416-27 |

## 2 Introduction

This Data Sheet describes the Infineon TC1797, a 32-bit microcontroller DSP, based on the Infineon TriCore Architecture.

#### 2.1 About this Document

This document is designed to be read primarily by design engineers and software engineers who need a detailed description of the interactions of the TC1797 functional units, registers, instructions, and exceptions.

This TC1797 Data Sheet describes the features of the TC1797 with respect to the TriCore Architecture. Where the TC1797 directly implements TriCore architectural functions, this manual simply refers to those functions as features of the TC1797. In all cases where this manual describes a TC1797 feature without referring to the TriCore Architecture, this means that the TC1797 is a direct implementation of the TriCore Architecture.

Where the TC1797 implements a subset of TriCore architectural features, this manual describes the TC1797 implementation, and then describes how it differs from the TriCore Architecture. Such differences between the TC1797 and the TriCore Architecture are documented in the section covering each such subject.

#### 2.1.1 Related Documentations

A complete description of the TriCore architecture is found in the document entitled "TriCore Architecture Manual". The architecture of the TC1797 is described separately this way because of the configurable nature of the TriCore specification: Different versions of the architecture may contain a different mix of systems components. The TriCore architecture, however, remains constant across all derivative designs in order to preserve compatibility.

This Data Sheets together with the "TriCore Architecture Manual" are required to understand the complete TC1797 micro controller functionality.

#### 2.1.2 Text Conventions

This document uses the following text conventions for named components of the TC1797:

- Functional units of the TC1797 are given in plain UPPER CASE. For example: "The SSC supports full-duplex and half-duplex synchronous communication".

- Pins using negative logic are indicated by an overline. For example: "The external reset pin, ESRO, has a dual function.".

- Bit fields and bits in registers are in general referenced as "Module\_Register name.Bit field" or "Module\_Register name.Bit". For example: "The Current CPU Priority Number bit field CPU ICR.CCPN is cleared". Most of the

register names contain a module name prefix, separated by an underscore character "\_" from the actual register name (for example, "ASC0\_CON", where "ASC0" is the module name prefix, and "CON" is the kernel register name). In chapters describing the kernels of the peripheral modules, the registers are mainly referenced with their kernel register names. The peripheral module implementation sections mainly refer to the actual register names with module prefixes.

- Variables used to describe sets of processing units or registers appear in mixed upper and lower cases. For example, register name "MSGCFGn" refers to multiple "MSGCFG" registers with variable n. The bounds of the variables are always given where the register expression is first used (for example, "n = 0-31"), and are repeated as needed in the rest of the text.

- The default radix is decimal. Hexadecimal constants are suffixed with a subscript letter "H", as in 100<sub>H</sub>. Binary constants are suffixed with a subscript letter "B", as in: 111<sub>B</sub>.

- When the extent of register fields, groups register bits, or groups of pins are

collectively named in the body of the document, they are represented as

"NAME[A:B]", which defines a range for the named group from B to A. Individual bits,

signals, or pins are given as "NAME[C]" where the range of the variable C is given in

the text. For example: CFG[2:0] and SRPN[0].

- Units are abbreviated as follows:

- MHz = Megahertz

- $\mu s = Microseconds$

- kBaud, kbit = 1000 characters/bits per second

- MBaud, Mbit = 1,000,000 characters/bits per second

- Kbyte, KB = 1024 bytes of memory

- Mbyte, MB= 1048576 bytes of memory

In general, the k prefix scales a unit by 1000 whereas the K prefix scales a unit by 1024. Hence, the Kbyte unit scales the expression preceding it by 1024. The kBaud unit scales the expression preceding it by 1000. The M prefix scales by 1,000,000 or 1048576, and  $\mu$  scales by .000001. For example, 1 Kbyte is 1024 bytes, 1 Mbyte is 1024  $\times$  1024 bytes, 1 kBaud/kbit are 1000 characters/bits per second, 1 MBaud/Mbit are 1000000 characters/bits per second, and 1 MHz is 1,000,000 Hz.

- Data format quantities are defined as follows:

- Byte = 8-bit quantity

- Half-word = 16-bit quantity

- Word = 32-bit quantity

- Double-word = 64-bit quantity

## 2.1.3 Reserved, Undefined, and Unimplemented Terminology

In tables where register bit fields are defined, the following conventions are used to indicate undefined and unimplemented function. Furthermore, types of bits and bit fields are defined using the abbreviations as shown in **Table 2**.

Table 2 Bit Function Terminology

| Table 2 Bit Function Terminology |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Function of Bits                 | Description                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Unimplemented,<br>Reserved       | Register bit fields named 0 indicate unimplemented functions with the following behavior.  Reading these bit fields returns 0.  These bit fields should be written with 0 if the bit field is defined as r or rh.  These bit fields have to be written with 0 if the bit field is defined as rw.  These bit fields are reserved. The detailed description of these bit fields can be found in the register descriptions. |  |  |

| rw                               | The bit or bit field can be read and written.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| rwh                              | As rw, but bit or bit field can be also set or reset by hardware.                                                                                                                                                                                                                                                                                                                                                        |  |  |

| r                                | The bit or bit field can only be read (read-only).                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| w                                | The bit or bit field can only be written (write-only). A read to this register will always give a default value back.                                                                                                                                                                                                                                                                                                    |  |  |

| rh                               | This bit or bit field can be modified by hardware (read-hardware, typical example: status flags). A read of this bit or bit field give the actual status of this bit or bit field back. Writing to this bit or bit field has no effect to the setting of this bit or bit field.                                                                                                                                          |  |  |

| S                                | Bits with this attribute are "sticky" in one direction. If their reset value is once overwritten by software, they can be switched again into their reset state only by a reset operation. Software cannot switch this type of bit into its reset state by writing the register. This attribute can be combined to "rws" or "rwhs".                                                                                      |  |  |

| f                                | Bits with this attribute are readable only when they are accessed<br>by an instruction fetch. Normal data read operations will return<br>other values.                                                                                                                                                                                                                                                                   |  |  |

## 2.1.4 Register Access Modes

Read and write access to registers and memory locations are sometimes restricted. In memory and register access tables, the terms as defined in **Table 3** are used.

| Table 3 | Access Terms                                                                                                                                                                                                                       |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Description                                                                                                                                                                                                                        |

| U       | Access Mode: Access permitted in User Mode 0 or 1.                                                                                                                                                                                 |

|         | Reset Value: Value or bit is not changed by a reset operation.                                                                                                                                                                     |

| SV      | Access permitted in Supervisor Mode.                                                                                                                                                                                               |

| R       | Read-only register.                                                                                                                                                                                                                |

| 32      | Only 32-bit word accesses are permitted to this register/address range.                                                                                                                                                            |

| E       | Endinit-protected register/address.                                                                                                                                                                                                |

| PW      | Password-protected register/address.                                                                                                                                                                                               |

| NC      | No change, indicated register is not changed.                                                                                                                                                                                      |

| BE      | Indicates that an access to this address range generates a Bus Error.                                                                                                                                                              |

| nBE     | Indicates that no Bus Error is generated when accessing this address range, even though it is either an access to an undefined address or the access does not follow the given rules.                                              |

| nE      | Indicates that no Error is generated when accessing this address or address range, even though the access is to an undefined address or address range. True for CPU accesses (MTCR/MFCR) to undefined addresses in the CSFR range. |

## 2.1.5 Abbreviations and Acronyms

The following acronyms and terms are used in this document:

| ADC  | Analog-to-Digital Converter                |

|------|--------------------------------------------|

| AGPR | Address General Purpose Register           |

| ALU  | Arithmetic and Logic Unit                  |

| ASC  | Asynchronous/Synchronous Serial Controller |

| BCU  | Bus Control Unit                           |

| BROM | Boot ROM & Test ROM                        |

| CAN  | Controller Area Network                    |

| CMEM | PCP Code Memory                            |

| CISC | Complex Instruction Set Computing          |

| CPS  | CPU Slave Interface                        |

| CPU  | Central Processing Unit                    |

CSA Context Save Area

CSFR Core Special Function Register

DAP Device Access Port

DAS Device Access Server

DCACHE Data Cache

DFLASH Data Flash Memory

DGPR Data General Purpose Register

DMA Direct Memory Access

DMI Data Memory Interface

EBU External Bus Interface

EMI Electro-Magnetic Interference

FADC Fast Analog-to-Digital Converter

FAM Flash Array Module

FCS Flash Command State Machine

FIM Flash Interface and Control Module

FPI Flexible Peripheral Interconnect (Bus)

FPU Floating Point Unit

GPIO General Purpose Input/Output

GPR General Purpose Register

GPTA General Purpose Timer Array

ICACHE Instruction Cache

I/O Input / Output

JTAG Joint Test Action Group = IEEE1149.1

LBCU Local Memory Bus Control Unit

LDRAM Local Data RAM

LFI Local Memory-to-FPI Bus Interface

LMB Local Memory Bus

LTC Local Timer Cell

MLI Micro Link Interface

MMU Memory Management Unit

MSB Most Significant Bit

MSC Micro Second Channel

NC Not Connected

NMI Non-Maskable Interrupt OCDS On-Chip Debug Support

OVRAM Overlay Memory

PCP Peripheral Control Processor

PMU Program Memory Unit PΠ Phase Locked Loop PCODE PCP Code Memory PFI ASH Program Flash Memory PMI Program Memory Interface **PMU** Program Memory Unit

PRAM PCP Parameter RAM RAM

RISC Reduced Instruction Set Computing SBCU System Peripheral Bus Control Unit

Random Access Memory

SCU System Control Unit

SFR Special Function Register SPB System Peripheral Bus

SPRAM Scratch-Pad RAM SRAM Static Data Memory SRN Service Request Node

Synchronous Serial Controller SSC

STM System Timer WDT Watchdog Timer

## 2.2 System Architecture of the TC1797

The TC1797 combines three powerful technologies within one silicon die, achieving new levels of power, speed, and economy for embedded applications:

- Reduced Instruction Set Computing (RISC) processor architecture

- Digital Signal Processing (DSP) operations and addressing modes

- · On-chip memories and peripherals

DSP operations and addressing modes provide the computational power necessary to efficiently analyze complex real-world signals. The RISC load/store architecture provides high computational bandwidth with low system cost. On-chip memory and peripherals are designed to support even the most demanding high-bandwidth real-time embedded control-systems tasks.

Additional high-level features of the TC1797 include:

- · Efficient memory organization: instruction and data scratch memories, caches

- Serial communication interfaces flexible synchronous and asynchronous modes

- Peripheral Control Processor standalone data operations and interrupt servicing

- DMA Controller DMA operations and interrupt servicing

- · General-purpose timers

- High-performance on-chip buses

- On-chip debugging and emulation facilities

- Flexible interconnections to external components

- Flexible power-management

The TC1797 is a high-performance microcontroller with TriCore CPU, program and data memories, buses, bus arbitration, an interrupt controller, a peripheral control processor and a DMA controller and several on-chip peripherals. The TC1797 is designed to meet the needs of the most demanding embedded control systems applications where the competing issues of price/performance, real-time responsiveness, computational power, data bandwidth, and power consumption are key design elements.

The TC1797 offers several versatile on-chip peripheral units such as serial controllers, timer units, and Analog-to-Digital converters. Within the TC1797, all these peripheral units are connected to the TriCore CPU/system via the Flexible Peripheral Interconnect (FPI) Bus and the Local Memory Bus (LMB). Several I/O lines on the TC1797 ports are reserved for these peripheral units to communicate with the external world.

## 2.2.1 TC1797 Block Diagram

Figure 1 shows the block diagram of the TC1797.

Figure 1 TC1797 Block Diagram

## 2.2.2 System Features

The TC1797 has the following features:

#### **Package**

- P/PG-BGA-416-10 package, 1mm pitch

- P/PG-BGA-416-27 package, 1mm pitch

## Clock Frequencies for the 180 MHz derivative

- Maximum CPU clock frequency: 180 MHz<sup>1)</sup>

- Maximum PCP clock frequency: 180 MHz<sup>2)</sup>

- Maximum system clock frequency: 90 MHz<sup>3)</sup>

#### Clock Frequencies for the 150 MHz derivative

- Maximum CPU clock frequency: 150 MHz<sup>1)</sup>

- Maximum PCP clock frequency: 150 MHz<sup>2)</sup>

- Maximum system clock frequency: 90 MHz<sup>3)</sup>

<sup>1)</sup> For CPU frequencies > 90 MHz, 2:1 mode has to be enabled. CPU 2:1 mode means:  $f_{FPI} = 0.5 * f_{CPU}$

<sup>2)</sup> For PCP frequencies > 90 MHz, 2:1 mode has to be enabled. PCP 2:1 mode means:  $f_{EPl} = 0.5 * f_{PCP}$

<sup>3)</sup> CPU 1:1 Mode means:  $f_{FPI} = f_{CPU}$ . PCP 1:1 mode means:  $f_{FPI} = f_{PCP}$

#### 2.2.3 CPU Cores of the TC1797

The TC1797 includes a high Performance CPU and a Peripheral Control Processor.

#### 2.2.3.1 High-performance 32-bit CPU

This chapter gives an overview about the TriCore 1 architecture.

#### TriCore (TC1.3.1) Architectural Highlights

- Unified RISC MCU/DSP

- 32-bit architecture with 4 Gbytes unified data, program, and input/output address space

- Fast automatic context-switching

- · Multiply-accumulate unit

- Floating point unit

- Saturating integer arithmetic

- High-performance on-chip peripheral bus (FPI Bus)

- · Register based design with multiple variable register banks

- Bit handling

- Packed data operations

- Zero overhead loop

- Precise exceptions

- Flexible power management

#### **High-efficiency TriCore Instruction Set**

- 16/32-bit instructions for reduced code size

- Data types include: Boolean, array of bits, character, signed and unsigned integer, integer with saturation, signed fraction, double-word integers, and IEEE-754 singleprecision floating point

- Data formats include: Bit, 8-bit byte, 16-bit half-word, 32-bit word, and 64-bit doubleword data formats

- Powerful instruction set

- · Flexible and efficient addressing mode for high code density

### **Integrated CPU related On-Chip Memories**

- Instruction memory: 40 KB total. After reset, configured into:<sup>1)</sup>

- 40 Kbyte Scratch-Pad RAM (SPRAM)

- 0 Kbyte Instruction Cache (ICACHE)

- Data memory: 128 KB total. After reset, configured into:<sup>1)</sup>

- 128 Kbyte Local Data RAM (LDRAM)

<sup>1)</sup> Software configurable. Available options are described in the CPU chapter.

- 0 Kbyte Data Cache (DACHE)

- On-chip SRAMs with parity error detection

## 2.2.3.2 High-performance 32-bit Peripheral Control Processor

The PCP is a flexible Peripheral Control Processor optimized for interrupt handling and thus unloading the CPU.

#### **Features**

- Data move between any two memory or I/O locations

- Data move until predefined limit supported

- Read-Modify-Write capabilities

- Full computation capabilities including basic MUL/DIV

- Read/move data and accumulate it to previously read data

- · Read two data values and perform arithmetic or logical operation and store result

- Bit-handling capabilities (testing, setting, clearing)

- Flow control instructions (conditional/unconditional jumps, breakpoint)

- Dedicated Interrupt System

- PCP SRAMs with parity error detection

- PCP/FPI clock mode 1:1 and 2:1 available

#### Integrated PCP related On-Chip Memories

- 32 Kbyte Code Memory (CMEM)

- 16 Kbyte Parameter Memory (PRAM)

## 2.3 On-Chip System Units

The TC1797 microcontroller offers several versatile on-chip system peripheral units such as DMA controller, embedded Flash module, interrupt system and ports.

### 2.3.1 Flexible Interrupt System

The TC1797 includes a programmable interrupt system with the following features:

#### **Features**

- · Fast interrupt response

- Independent interrupt systems for CPU and PCP

- Each SRN can be mapped to the CPU or PCP interrupt system

- Flexible interrupt-prioritizing scheme with 255 interrupt priority levels per interrupt system

## 2.3.2 Direct Memory Access Controller

The TC1797 includes a fast and flexible DMA controller with 16 independant DMA channels (two DMA Move Engines).

#### **Features**

- 8 independent DMA channels

- 8 DMA channels in the DMA Sub-Block

- Up to 16 selectable request inputs per DMA channel

- 2-level programmable priority of DMA channels within the DMA Sub-Block

- Software and hardware DMA request

- Hardware requests by selected on-chip peripherals and external inputs

- 3-level programmable priority of the DMA Sub-Block at the on chip bus interfaces

- Buffer capability for move actions on the buses (at least 1 move per bus is buffered)

- Individually programmable operation modes for each DMA channel

- Single Mode: stops and disables DMA channel after a predefined number of DMA transfers

- Continuous Mode: DMA channel remains enabled after a predefined number of DMA transfers; DMA transaction can be repeated

- Programmable address modification

- Two shadow register modes (with / w/o automatic re-set and direct write access).

- · Full 32-bit addressing capability of each DMA channel

- 4 Gbyte address range

- Data block move supports > 32 Kbyte moves per DMA transaction

- Circular buffer addressing mode with flexible circular buffer sizes

- Programmable data width of DMA transfer/transaction: 8-bit, 16-bit, or 32-bit

- Register set for each DMA channel

- Source and destination address register

- Channel control and status register

- Transfer count register

- Flexible interrupt generation (the service request node logic for the MLI channel is also implemented in the DMA module)

- DMA module is working on SPB frequency, LMB interface on LMB frequency.

- Dependant on the target/destination address, Read/write requests from the Move Engine are directed to the SPB, LMB, MLI or to the the Cerberus.

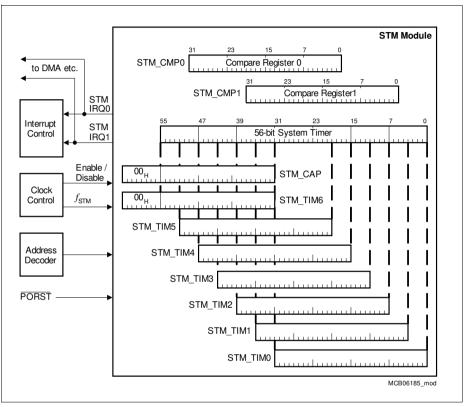

## 2.3.3 System Timer

The TC1797's STM is designed for global system timing applications requiring both high precision and long range.

#### **Features**

- Free-running 56-bit counter

- All 56 bits can be read synchronously

- Different 32-bit portions of the 56-bit counter can be read synchronously

- Flexible interrupt generation based on compare match with partial STM content

- Driven by maximum 90 MHz (=  $f_{SYS}$ , default after reset =  $f_{SYS}$ /2)

- · Counting starts automatically after a reset operation

- STM registers are reset by an application reset if bit ARSTDIS.STMDIS is cleared. If bit ARSTDIS.STMDIS is set, the STM is not reset.

- STM can be halted in debug/suspend mode

Special STM register semantics provide synchronous views of the entire 56-bit counter, or 32-bit subsets at different levels of resolution.

The maximum clock period is  $2^{56} \times f_{\text{STM}}$ . At  $f_{\text{STM}} = 90$  MHz, for example, the STM counts 25.39 years before overflowing. Thus, it is capable of continuously timing the entire expected product life time of a system without overflowing.

In case of a power-on reset, a watchdog reset, or a software reset, the STM is reset. After one of these reset conditions, the STM is enabled and immediately starts counting up. It is not possible to affect the content of the timer during normal operation of the TC1797.

The STM can be optionally disabled for power-saving purposes, or suspended for debugging purposes via its clock control register. In suspend mode of the TC1797 (initiated by writing an appropriate value to STM\_CLC register), the STM clock is stopped but all registers are still readable.

Due to the 56-bit width of the STM, it is not possible to read its entire content with one instruction. It needs to be read with two load instructions. Since the timer would continue to count between the two load operations, there is a chance that the two values read are not consistent (due to possible overflow from the low part of the timer to the high part between the two read operations). To enable a synchronous and consistent reading of the STM content, a capture register (STM\_CAP) is implemented. It latches the content of the high part of the STM each time when one of the registers STM\_TIM0 to STM\_TIM5 is read. Thus, STM\_CAP holds the upper value of the timer at exactly the same time when the lower part is read. The second read operation would then read the content of the STM\_CAP to get the complete timer value.

The content of the 56-bit System Timer can be compared against the content of two compare values stored in the STM\_CMP0 and STM\_CMP1 registers. Interrupts can be generated on a compare match of the STM with the STM\_CMP0 or STM\_CMP1 registers.

Figure 2 provides an overview on the STM module. It shows the options for reading parts of STM content.

Figure 2 General Block Diagram of the STM Module Registers