Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# KS8995M

### Integrated 5-Port 10/100 Managed Switch

### **Rev 1.13**

# **General Description**

The KS8995M is a highly integrated Layer-2 managed switch with optimized BOM (Bill of Materials) cost for low port count, cost-sensitive 10/100Mbps switch systems. It also provides an extensive feature set such as tag/port-based VLAN, QoS (Quality of Service) priority, management, MIB counters, dual MII interfaces and CPU control/data interfaces to effectively address both current and emerging Fast Ethernet applications.

The KS8995M contains five 10/100 transceivers with patented mixed-signal low-power technology, five MAC (Media Access Control) units, a high-speed non-blocking switch fabric, a dedicated address look-up engine, and an on-chip frame buffer memory.

All PHY units support 10BaseT and 100BaseTX. In addition, two of the PHY units support 100BaseFX (Ports 4 and 5).

All support documentation can be found on Micrel's web site at: www.micrel.com.

### **Features**

- Integrated switch with five MACs and five Fast Ethernet transceivers fully compliant to IEEE 802.3u standard

- Shared memory based switch fabric with fully nonblocking configuration

- 1.4Gbps high-performance memory bandwidth

- 10BaseT, 100BaseTX and 100BaseFX modes (FX in Ports 4 and 5)

- Dual MII configuration: MII-Switch (MAC or PHY mode MII) and MII-P5 (PHY mode MII)

- IEEE 802.1q tag-based VLAN (16 VLANs, full-range VID) for DMZ port, WAN/LAN separation or inter-VLAN switch links

- · VLAN ID tag/untag options, per-port basis

- Programmable rate limiting 0Mbps to 100Mbps, ingress and egress port, rate options for high and low priority, per-port-basis

- Flow control or drop packet rate limiting (ingress port)

- Integrated MIB counters for fully compliant statistics gathering, 34 MIB counters per port

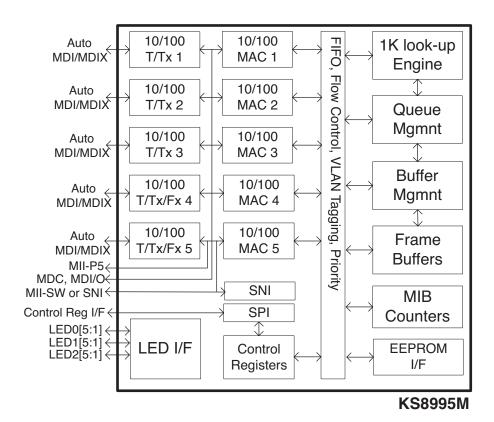

## **Functional Diagram**

### Features (continued)

- Enable/Disable option for huge frame size up to 1916 bytes per frame

- IGMP v1/v2 snooping for multicast packet filtering

- Special tagging mode to send CPU info on ingress packet's port value

- SPI slave (complete) and MDIO (MII PHY only) serial management interface for control of register configuration

- MAC-id based security lock option

- Control registers configurable on-the-fly (port-priority, 802.1p/d/g, AN...)

- CPU read access to MAC forwarding table entries

- 802.1d Spanning Tree Protocol

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port or MII

- Broadcast storm protection with percent control global and per-port basis

- Optimization for fiber-to-copper media conversion

- Full-chip hardware power-down support (register configuration not saved)

- Per-port based software power-save on PHY (idle link detection, register configuration preserved)

- QoS/CoS packets prioritization supports: per port, 802.1p and DiffServ based

- 802.1p/q tag insertion or removal on a per port basis (egress)

- MDC and MDI/O interface support to access the MII PHY control registers (not all control registers)

- · MII local loopback support

- On-chip 64Kbyte memory for frame buffering (not shared with 1K unicast address table)

- · Wire-speed reception and transmission

- Integrated look-up engine with dedicated 1K MAC addresses

- Full duplex IEEE 802.3x and half-duplex back pressure flow control

- · Comprehensive LED support

- 7-wire SNI support for legacy MAC interface

- · Automatic MDI/MDI-X crossover for plug-and-play

- · Disable Automatic MDI/MDI-X option

- · Low power:

Core: 1.8V I/O: 2.5V or 3.3V

0.18µm CMOS technology

• Commercial temperature range: 0°C to +70°C

Industrial temperature range: -40°C to +85°C

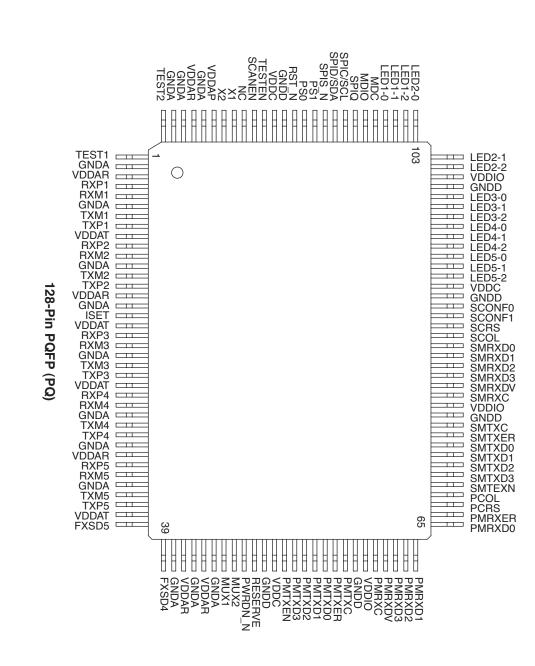

· Available in 128-pin PQFP package

### **Applications**

- Broadband gateway/firewall/VPN

- · Integrated DSL or cable modem multi-port router

- · Wireless LAN access point plus gateway

- Home networking expansion

- · Standalone 10/100 switch

- Hotel/campus/MxU gateway

- · Enterprise VoIP gateway/phone

- FTTx customer premise equipment

- Managed media converter

### **Ordering Information**

| Part Number | Temperature Range | Package                |

|-------------|-------------------|------------------------|

| KS8995M     | 0°C to +70°C      | 128-Pin PQFP           |

| KSZ8995M    | 0°C to +70°C      | 128-Pin PQFP Lead Free |

| KS8995MI    | -40°C to +85°C    | 128-Pin PQFP           |

# **Revision History**

| Revision | Date     | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1.00     | 11/05/01 | Created                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 1.01     | 11/09/01 | Pinout Mux1/2, DVCC-IO 2.5/3.3V, feature list, register spec 11-09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 1.02     | 12/03/01 | Editorial changes, added new register and MIB descriptions. Added paragraph describing TOS registers. Imported functional descriptions. Formatting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 1.03     | 12/12/01 | ncorporate changes per engineering feedback as well as updating functional descriptions and adding ew timing information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 1.04     | 12/13/01 | Changed Rev. and For. Modes to PHY and MAC modes respectively. Added MIIM clarification in "MII Management Interface" section. Reformatted section sequence. Added hex register addresses. Added advertisement ability descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 1.05     | 12/18/01 | Inserted switch forwarding flow charts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 1.06     | 12/20/01 | Added new KS8995M block diagram, editorial changes, register descriptions changes and cross-references from functional descriptions to register and strap in options.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 1.07     | 1/22/01  | Changed FXSD pins to inputs, added new descriptions to "Configuration Interfaces" section. Edited pin descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 1.08     | 3/1/02   | Editorial changes in "Dynamic MAC Address table and "MIB Counters." Updated figure 2 flowchart.  Updated table 2 for MAC mode connections. Separate static MAC bit assignments for read and write.  Edited read and write examples to MAC tables and MIB counters. Changed Table 3 KS8995M signals to "S" suffix. Changed aging description in Register 2, bit 0. Changed "Port Registers" section and listed all port register addresses. Changed port control 11 description for bits [7:5]. Changed MIB counter descriptions.                                                                                                                                              |  |  |  |  |  |  |

| 1.09     | 5/17/02  | Changed MII setting in "Pin Descriptions." Changed pu/pd descriptions for SMRXD2. "Register 18," changed pu/pd description for forced flow control. "Illegal Frames." Edited large packet sizes back in. "Elecrical Characteristics," Added in typical supply current numbers for 100 BaseTX and 10 BaseTX operation. "Register 18," Added in note for illegal half-duplex, force flow control. "Pin Description," Added extra X1 clock input description. "Elecrical Characteristics," Updated to chip only current numbers. Added SPI Timing. Feature Highlights.                                                                                                           |  |  |  |  |  |  |

| 1.10     | 7/29/02  | "Pin Description," changed SMRXC and SMTXC to I/O. Input in MAC mode, output in PHY mode MII. "Elecrical Characteristics," modified current consumption to chip only numbers. "Half-Duplex Back Pressure," added description for no dropped packets in half-duplex mode. Added recommended operating conditions. Added Idle mode current consumption in "Elecrical Characteristics," added "Selection of Isolation Transformers," Added 3.01kΩ resistor instructions for ISET "Pin Description" section. Changed Polarity of transmit pairs in "Pin Description." Changed description for Register 2, bit 1, in "Register Description" section. Added "Reset Timing" section. |  |  |  |  |  |  |

| 1.11     | 12/17/02 | "Register 3" changed 802.1x to 802.3x. "Register 6," changed default column to disable flow control for pull-down, and enable flow control for pull-up. "Register 29" and "Register 0" indicate loop back is at the PHY. Added description to register 4 bit 2 to indicate that STPID packets from CPU to normal ports are not allowed as 1522 byte tag packets. Fixed dynamic MAC address example errors in "Dynamic MAC Address Table." Changed definition of forced MDI, MDIX in section "Register 29," "Register 30" and "Register 0." Added "Part Ordering Information." Added Ambient operating temperature for KS8995MI                                                |  |  |  |  |  |  |

| 1.12     | 3/10/03  | Changed pin 120 description to NC. Changed SPIQ pin description to Otri. Changed logo. Changed contact information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 1.13     | 7/5/06   | Add a note for VLAN table write, improve the timing diagram of MAC mode and PHY mode for MII interface, change VDDIO support 3.3V only, update pin description for PCRS, PCOL, and so on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

# **Table of Contents**

| System Level Applications                       | 7  |

|-------------------------------------------------|----|

| Pin Description (by Number)                     | 9  |

| Pin Description (by Name)                       | 15 |

| Pin Configuration                               | 21 |

| Introduction                                    | 22 |

| Functional Overview: Physical Layer Transceiver | 22 |

| 100BaseTX Transmit                              | 22 |

| 100BaseTX Receive                               | 22 |

| PLL Clock Synthesizer                           | 22 |

| Scrambler/De-scrambler (100BaseTX only)         | 22 |

| 100BaseFX Operation                             | 22 |

| 100BaseFX Signal Detection                      | 22 |

| 100BaseFX Far End Fault                         | 23 |

| 10BaseT Transmit                                | 23 |

| 10BaseT Receive                                 | 23 |

| Power Management                                | 23 |

| MDI/MDI-X Auto Crossover                        | 23 |

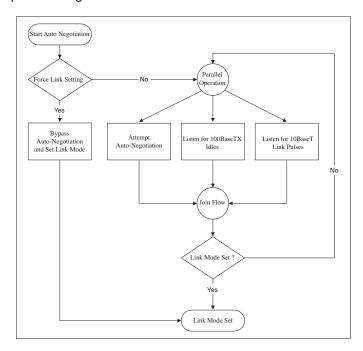

| Auto-Negotiation                                | 23 |

| Functional Overview: Switch Core                | 24 |

| Address Look-Up                                 | 24 |

| Learning                                        | 24 |

| Migration                                       | 24 |

| Aging                                           | 24 |

| Forwarding                                      | 24 |

| Switching Engine                                | 24 |

| MAC Operation                                   | 24 |

| Inter-Packet Gap (IPG)                          | 24 |

| Backoff Algorithm                               | 24 |

| Late Collision                                  | 26 |

| Illegal Frames                                  | 26 |

| Flow Control                                    | 26 |

| Half-Duplex Back Pressure                       | 26 |

| Broadcast Storm Protection                      | 26 |

| MII Interface Operation                         | 26 |

| SNI Interface Operation                         | 28 |

| Advanced Functionality                          | 28 |

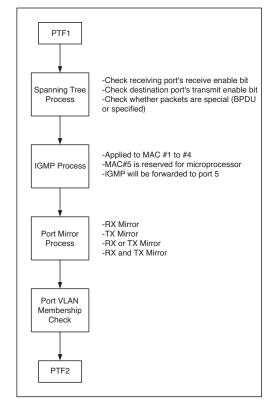

| Spanning Tree Support                           | 28 |

| Special Tagging Mode                            | 29 |

| IGMP Support                                    | 30 |

| Port Mirroring Support                          | 31 |

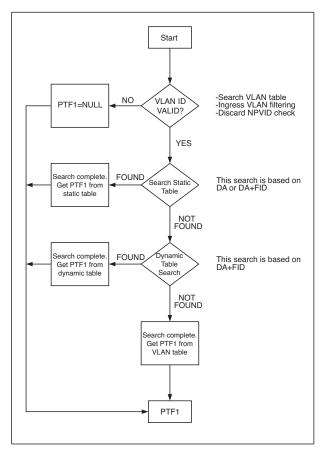

| VLAN Support                                    | 31 |

| Rate Limit Support                              | 32 |

| Configuration Interface                         | 33 |

| I2C Master Serial Bus Configuration             | 35 |

| SPI Slave Serial Bus Configuration              |    |

| MII Management Interface (MIIM)                 | 38 |

| Register Description                                 | 39 |

|------------------------------------------------------|----|

| Global Registers                                     | 39 |

| Register 0 (0x00): Chip ID0                          | 39 |

| Register 1 (0x01): Chip ID1/Start Switch             | 39 |

| Register 2 (0x02): Global Control 0                  | 40 |

| Register 3 (0x03): Global Control 1                  | 40 |

| Register 4 (0x04): Global Control 2                  | 41 |

| Register 5 (0x05): Global Control 3                  | 42 |

| Register 6 (0x06): Global Control 4                  | 42 |

| Register 7 (0x07): Global Control 5                  | 43 |

| Register 8 (0x08): Global Control 6                  | 43 |

| Register 9 (0x09): Global Control 7                  | 43 |

| Register 10 (0x0A): Global Control 8                 |    |

| Register 11 (0x0B): Global Control 9                 | 43 |

| Port Registers                                       | 44 |

| Register 16 (0x10): Port 1 Control 0                 |    |

| Register 17 (0x11): Port 1 Control 1                 |    |

| Register 18 (0x12): Port 1 Control 2                 |    |

| Register 19 (0x13): Port 1 Control 3                 |    |

| Register 20 (0x14): Port 1 Control 4                 | 46 |

| Register 21 (0x15): Port 1 Control 5                 |    |

| Register 22 (0x16): Port 1 Control 6                 |    |

| Register 23 (0x17): Port 1 Control 7                 |    |

| Register 24 (0x18): Port 1 Control 8                 |    |

| Register 25 (0x19): Port 1 Control 9                 |    |

| Register 26 (0x1A): Port 1 Control 10                |    |

| Register 27 (0x1B): Port 1 Control 11                |    |

| Register 28 (0x1C): Port 1 Control 12                |    |

| Register 29 (0x1D): Port 1 Control 13                |    |

| Register 30 (0x1E): Port 1 Status 0                  |    |

| Register 31 (0x1F): Port 1 Status 1                  | 50 |

| Advanced Control Registers                           |    |

| Register 96 (0x60): TOS Priority Control Register 0  |    |

| Register 97 (0x61): TOS Priority Control Register 1  |    |

| Register 98 (0x62): TOS Priority Control Register 2  |    |

| Register 99 (0x63): TOS Priority Control Register 3  |    |

| Register 100 (0x64): TOS Priority Control Register 4 |    |

| Register 101 (0x65): TOS Priority Control Register 5 |    |

| Register 102 (0x66): TOS Priority Control Register 6 |    |

| Register 103 (0x67): TOS Priority Control Register 7 |    |

| Register 104 (0x68): MAC Address Register 0          |    |

| Register 105 (0x69): MAC Address Register 1          |    |

| Register 106 (0x6A): MAC Address Register 2          |    |

| Register 107 (0x6B): MAC Address Register 3          |    |

| Register 108 (0x6C): MAC Address Register 4          |    |

| Register 109 (0X6D): MAC Address Register 5          |    |

| Register 110 (0x6E): Indirect Access Control 0       |    |

| Register 111 (0x6F): Indirect Access Control 1       | 51 |

| Register 112 (0x70): Indirect Data Register 8  | . 51 |

|------------------------------------------------|------|

| Register 113 (0x71): Indirect Data Register 7  | . 51 |

| Register 114 (0x72): Indirect Data Register 6  | . 51 |

| Register 115 (0x73): Indirect Data Register 5  | . 51 |

| Register 116 (0x74): Indirect Data Register 4  | . 51 |

| Register 117 (0x75): Indirect Data Register 3  | . 51 |

| Register 118 (0x76): Indirect Data Register 2  | . 51 |

| Register 119 (0x77): Indirect Data Register 1  | . 51 |

| Register 120 (0x78): Indirect Data Register 0  | . 51 |

| Register 121 (0x79): Digital Testing Status 0  | . 51 |

| Register 122 (0x7A): Digital Testing Status 1  | . 51 |

| Register 123 (0x7B): Digital Testing Control 0 | . 51 |

| Register 124 (0x7C): Digital Testing Control 1 | . 51 |

| Register 125 (0x7D): Analog Testing Control 0  | . 51 |

| Register 126 (0x7E): Analog Testing Control 1  | . 52 |

| Register 127 (0x7F): Analog Testing Status     | . 52 |

| Static MAC Address                             | . 53 |

| VLAN Address                                   | . 55 |

| Dynamic MAC Address                            | . 56 |

| MIB Counters                                   | . 57 |

| MIIM Registers                                 | . 60 |

| Register 0: MII Control                        | . 60 |

| Register 1: MII Status                         | . 61 |

| Register 2: PHYID HIGH                         | . 61 |

| Register 3: PHYID LOW                          | . 61 |

| Register 4: Advertisement Ability              | . 61 |

| Register 5: Link Partner Ability               | . 62 |

| Absolute Maximum Ratings                       | . 63 |

| Operating Ratings                              | . 63 |

| Electrical Characteristics                     | . 63 |

| Timing Diagrams                                | . 65 |

| Selection of Isolation Transformers            | . 72 |

| Qualified Magnetic Lists                       | . 72 |

| Dockogo Information                            | 72   |

# **System Level Applications**

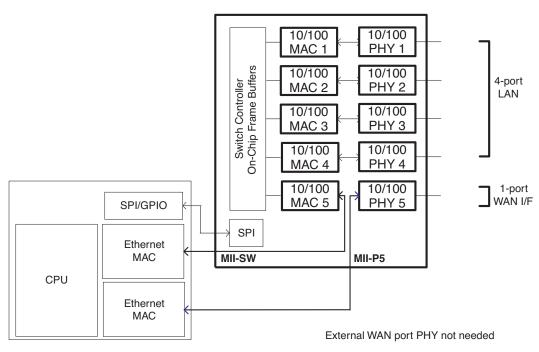

Figure 1. Broadband Gateway

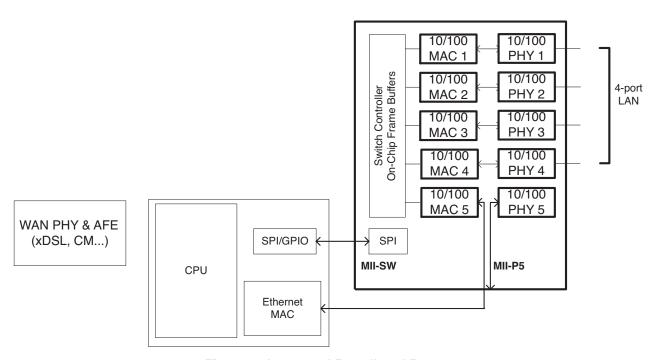

Figure 2. Integrated Broadband Router

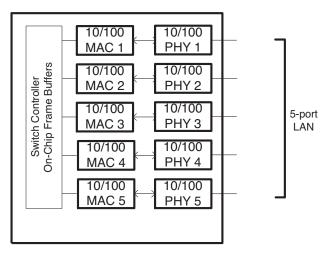

Figure 3. Standalone Switch

# **Pin Description (by Number)**

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                       |  |

|------------|----------|---------------------|------|------------------------------------------------------------------------------------|--|

| 1          | TEST1    | NC                  |      | NC for normal operation. Factory test pin.                                         |  |

| 2          | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 3          | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub>                                                        |  |

| 4          | RXP1     | 1                   | 1    | Physical receive signal + (differential)                                           |  |

| 5          | RXM1     | I                   | 1    | Physical receive signal - (differential)                                           |  |

| 6          | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 7          | TXM1     | 0                   | 1    | Physical transmit signal - (differential)                                          |  |

| 8          | TXP1     | 0                   | 1    | Physical transmit signal + (differential)                                          |  |

| 9          | VDDAT    | Р                   |      | 2.5V analog V <sub>DD</sub>                                                        |  |

| 10         | RXP2     | I                   | 2    | Physical receive signal + (differential)                                           |  |

| 11         | RXM2     | I                   | 2    | Physical receive signal - (differential)                                           |  |

| 12         | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 13         | TXM2     | 0                   | 2    | Physical transmit signal - (differential)                                          |  |

| 14         | TXP2     | 0                   | 2    | Physical transmit signal + (differential)                                          |  |

| 15         | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub>                                                        |  |

| 16         | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 17         | ISET     |                     |      | Set physical transmit output current. Pull-down with a 3.01k $\Omega$ 1% resistor. |  |

| 18         | VDDAT    | Р                   |      | 2.5V analog V <sub>DD</sub>                                                        |  |

| 19         | RXP3     | I                   | 3    | Physical receive signal + (differential)                                           |  |

| 20         | RXM3     | 1                   | 3    | Physical receive signal - (differential)                                           |  |

| 21         | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 22         | TXM3     | 0                   | 3    | Physical transmit signal - (differential)                                          |  |

| 23         | TXP3     | 0                   | 3    | Physical transmit signal + (differential)                                          |  |

| 24         | VDDAT    | Р                   |      | 2.5V analog V <sub>DD</sub>                                                        |  |

| 25         | RXP4     | I                   | 4    | Physical receive signal + (differential)                                           |  |

| 26         | RXM4     | I                   | 4    | Physical receive signal - (differential)                                           |  |

| 27         | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 28         | TXM4     | 0                   | 4    | Physical transmit signal - (differential)                                          |  |

| 29         | TXP4     | 0                   | 4    | Physical transmit signal + (differential)                                          |  |

| 30         | GNDA     | Gnd                 |      | Analog ground                                                                      |  |

| 31         | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub>                                                        |  |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

Ipu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

lpu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                   |                                          |      |

|------------|----------|---------------------|------|----------------------------------------------------------------|------------------------------------------|------|

| 32         | RXP5     | I                   | 5    | Physical receive signal + (differential)                       | Physical receive signal + (differential) |      |

| 33         | RXM5     | I                   | 5    | Physical receive signal - (differential)                       |                                          |      |

| 34         | GNDA     | Gnd                 |      | Analog ground                                                  |                                          |      |

| 35         | TXM5     | 0                   | 5    | Physical transmit signal - (differential)                      |                                          |      |

| 36         | TXP5     | 0                   | 5    | Physical transmit signal + (differential)                      |                                          |      |

| 37         | VDDAT    | Р                   |      | 2.5V analog V <sub>DD</sub>                                    |                                          |      |

| 38         | FXSD5    | I                   | 5    | Fiber signal detect/factory test pin, pull-down for TX         | ( mode                                   |      |

| 39         | FXSD4    | I                   | 4    | Fiber signal detect/factory test pin, pull-down for TX         | ( mode                                   |      |

| 40         | GNDA     | Gnd                 |      | Analog ground                                                  |                                          |      |

| 41         | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub>                                    |                                          |      |

| 42         | GNDA     | Gnd                 |      | Analog ground                                                  |                                          |      |

| 43         | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub>                                    |                                          |      |

| 44         | GNDA     | Gnd                 |      | Analog ground                                                  |                                          |      |

| 45         | MUX1     | NC                  |      | MUX1 and MUX2 should be left unconnected for normal operation. |                                          |      |

| 46         | MUX2     | NC                  |      | They are factory test pins.                                    |                                          |      |

|            |          |                     |      | Mode                                                           | Mux1                                     | Mux2 |

|            |          |                     |      | Normal Operation                                               | NC                                       | NC   |

|            |          |                     |      | Remote Analog Loopback Mode for Testing only                   | 0                                        | 1    |

|            |          |                     |      | Reserved                                                       | 1                                        | 0    |

|            |          |                     |      | Power Save Mode for Testing only                               | 1                                        | 1    |

| 47         | PWRDN_N  | lpu                 |      | Full-chip power down. Active low.                              | ·                                        | •    |

| 48         | RESERVE  | NC                  |      | Reserved pin. No connect.                                      |                                          |      |

| 49         | GNDD     | Gnd                 |      | Digital ground                                                 |                                          |      |

| 50         | VDDC     | Р                   |      | 1.8V digital core V <sub>DD</sub>                              |                                          |      |

| 51         | PMTXEN   | lpd                 | 5    | PHY[5] MII transmit enable                                     |                                          |      |

| 52         | PMTXD3   | lpd                 | 5    | PHY[5] MII transmit bit 3                                      |                                          |      |

| 53         | PMTXD2   | lpd                 | 5    | PHY[5] MII transmit bit 2                                      |                                          |      |

| 54         | PMTXD1   | lpd                 | 5    | PHY[5] MII transmit bit 1                                      |                                          |      |

| 55         | PMTXD0   | lpd                 | 5    | PHY[5] MII transmit bit 0                                      |                                          |      |

| 56         | PMTXER   | lpd                 | 5    | PHY[5] MII transmit error                                      |                                          |      |

| 57         | PMTXC    | 0                   | 5    | PHY[5] MII transmit clock. PHY mode MII.                       |                                          |      |

| 58         | GNDD     | Gnd                 |      | Digital ground                                                 |                                          |      |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

lpu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port                                                                                                                                           | Pin Function                                                                                                                                                                                                        |  |

|------------|----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 59         | VDDIO    | Р                   |                                                                                                                                                | 3.3V digital V <sub>DD</sub> for digital I/O circuitry                                                                                                                                                              |  |

| 60         | PMRXC    | 0                   | 5                                                                                                                                              | PHY[5] MII receive clock. PHY mode MII                                                                                                                                                                              |  |

| 61         | PMRXDV   | lpd/O               | 5                                                                                                                                              | PHY[5] MII receive data valid                                                                                                                                                                                       |  |

| 62         | PMRXD3   | lpd/O               | 5                                                                                                                                              | PHY[5] MII receive bit 3. Strap option: PD (default) = enable flow control; PU = disable flow control.                                                                                                              |  |

| 63         | PMRXD2   | lpd/O               | 5                                                                                                                                              | PHY[5] MII receive bit 2. Strap option: PD (default) = disable back pressure; PU = enable back pressure.                                                                                                            |  |

| 64         | PMRXD1   | lpd/O               | 5                                                                                                                                              | PHY[5] MII receive bit 1. Strap option: PD (default) = drop excessive collision packets; PU = does not drop excessive collision packets.                                                                            |  |

| 65         | PMRXD0   | lpd/O               | 5                                                                                                                                              | PHY[5] MII receive bit 0. Strap option: PD (default) = disable aggressive back-off algorithm in half-duplex mode; PU = enable for performance enhancement.                                                          |  |

| 66         | PMRXER   | lpd/O               | 5                                                                                                                                              | PHY[5] MII receive error. Strap option: PD (default) = 1522/1518 bytes; PU = packet size up to 1536 bytes.                                                                                                          |  |

| 67         | PCRS     | lpd/O               | 5                                                                                                                                              | PHY[5] MII carrier sense. Strap option for port 4 only. See "Register 70 PD (default) = Force half-duplex if auto-negotiation is disabled or fails PU = Force full-duplex if auto-negotiation is disabled or fails. |  |

| 68         | PCOL     | lpd/O               | 5 PHY[5] MII collision detect. Strap option for port 4 only. See "Register 66." PD (default) = No force flow control. PU = Force flow control. |                                                                                                                                                                                                                     |  |

| 69         | SMTXEN   | lpd                 | Switch MII transmit enable                                                                                                                     |                                                                                                                                                                                                                     |  |

| 70         | SMTXD3   | lpd                 |                                                                                                                                                | Switch MII transmit bit 3                                                                                                                                                                                           |  |

| 71         | SMTXD2   | lpd                 |                                                                                                                                                | Switch MII transmit bit 2                                                                                                                                                                                           |  |

| 72         | SMTXD1   | lpd                 |                                                                                                                                                | Switch MII transmit bit 1                                                                                                                                                                                           |  |

| 73         | SMTXD0   | lpd                 |                                                                                                                                                | Switch MII transmit bit 0                                                                                                                                                                                           |  |

| 74         | SMTXER   | lpd                 |                                                                                                                                                | Switch MII transmit error                                                                                                                                                                                           |  |

| 75         | SMTXC    | I/O                 |                                                                                                                                                | Switch MII transmit clock. Input in MAC mode, output in PHY mode MII.                                                                                                                                               |  |

| 76         | GNDD     | Gnd                 |                                                                                                                                                | Digital ground                                                                                                                                                                                                      |  |

| 77         | VDDIO    | Р                   |                                                                                                                                                | 3.3V digital V <sub>DD</sub> for digital I/O circuitry                                                                                                                                                              |  |

| 78         | SMRXC    | I/O                 |                                                                                                                                                | Switch MII receive clock. Input in MAC mode, output in PHY mode MII.                                                                                                                                                |  |

| 79         | SMRXDV   | Ipd/O               |                                                                                                                                                | Switch MII receive data valid                                                                                                                                                                                       |  |

| 80         | SMRXD3   | lpd/O               |                                                                                                                                                | Switch MII receive bit 3. Strap option: PD (default) = Disable Switch MII full-duplex flow control; PU = Enable Switch MII full-duplex flow control.                                                                |  |

| 81         | SMRXD2   | lpd/O               |                                                                                                                                                | Switch MII receive bit 2. Strap option: PD (default) = Switch MII in full-duplex mode; PU = Switch MII in half-duplex mode.                                                                                         |  |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

Ipu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

| Pin Number | Pin Name     | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                   | Pin Function                                   |            |            |

|------------|--------------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|------------|

| 82         | SMRXD1       | lpd/O               |      | Switch MII receive bit 1. Strap option: PD (default) = Switch MII in 100Mbps mode; PU = Switch MII in 10Mbps mode.             |                                                |            |            |

| 83         | SMRXD0 lpd/O |                     |      |                                                                                                                                | 0; Strap option: LED<br>0; PU = Mode 1. See    |            |            |

|            |              |                     |      |                                                                                                                                |                                                | Mode 0     | Mode 1     |

|            |              |                     |      | LEDX_2                                                                                                                         |                                                | Lnk/Act    | 100Lnk/Act |

|            |              |                     |      | LEDX_1                                                                                                                         |                                                | Fulld/Col  | 10Lnk/Act  |

|            |              |                     |      | LEDX_0                                                                                                                         |                                                | Speed      | Fulld      |

| 84         | SCOL         | lpd/O               |      | Switch MII collision de                                                                                                        | etect                                          |            |            |

| 85         | SCRS         | lpd/O               |      | Switch MII carrier sen                                                                                                         | ise                                            |            |            |

| 86         | SCONF1       | lpd                 |      | Dual MII configuration                                                                                                         | n pin                                          |            |            |

|            |              |                     |      | Pin# (91, 86, 87):                                                                                                             | Switch MII                                     | PHY [5] M  | II         |

|            |              |                     |      | 000                                                                                                                            | Disable, Otri                                  | Disable, O | tri        |

|            |              |                     |      | 001                                                                                                                            | PHY Mode MII                                   | Disable, O | tri        |

|            |              |                     |      | 010                                                                                                                            | MAC Mode MII                                   | Disable, O | tri        |

|            |              |                     |      | 011                                                                                                                            | PHY Mode SNI                                   | Disable, O | tri        |

|            |              |                     |      | 100                                                                                                                            | Disable                                        | Disable    |            |

|            |              |                     |      | 101                                                                                                                            | PHY Mode MII                                   | PHY Mode   | MII        |

|            |              |                     |      | 110                                                                                                                            | MAC Mode MII                                   | PHY Mode   | MII        |

|            |              |                     |      | 111                                                                                                                            | PHY Mode SNI                                   | PHY Mode   | MII        |

| 87         | SCONF0       | lpd                 |      | Dual MII configuration                                                                                                         | n pin                                          |            |            |

| 88         | GNDD         | Gnd                 |      | Digital ground                                                                                                                 |                                                |            |            |

| 89         | VDDC         | Р                   |      | 1.8V digital core V <sub>DD</sub>                                                                                              |                                                |            |            |

| 90         | LED5-2       | lpu/O               | 5    |                                                                                                                                | o option: Aging setup.<br>Enable; PD = Aging d |            | section    |

| 91         | LED5-1       | lpu/O               | 5    | LED indicator 1. Strap option: PU (default): enable PHY [5] MII I/F PD: tristate all PHY [5] MII output. See "pin# 86 SCONF1." |                                                |            |            |

| 92         | LED5-0       | lpu/O               | 5    | LED indicator 0                                                                                                                |                                                |            |            |

| 93         | LED4-2       | lpu/O               | 4    | LED indicator 2                                                                                                                |                                                |            |            |

| 94         | LED4-1       | lpu/O               | 4    | LED indicator 1                                                                                                                |                                                |            |            |

| 95         | LED4-0       | lpu/O               | 4    | LED indicator 0                                                                                                                |                                                |            |            |

| 96         | LED3-2       | lpu/O               | 3    | LED indicator 2                                                                                                                |                                                |            |            |

| 97         | LED3-1       | lpu/O               | 3    | LED indicator 1                                                                                                                |                                                |            |            |

|            |              |                     |      |                                                                                                                                |                                                |            |            |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

lpu = Input w/ internal pull-up

lpd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                                                     |                                                             |  |  |

|------------|----------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| 98         | LED3-0   | lpu/O               | 3    | LED indicator 0                                                                                                                                                                                                                                  |                                                             |  |  |

| 99         | GNDD     | Gnd                 |      | Digital ground                                                                                                                                                                                                                                   |                                                             |  |  |

| 100        | VDDIO    | Р                   |      | 3.3V digital V <sub>DD</sub> for digital                                                                                                                                                                                                         | I/O                                                         |  |  |

| 101        | LED2-2   | lpu/O               | 2    | LED indicator 2                                                                                                                                                                                                                                  |                                                             |  |  |

| 102        | LED2-1   | lpu/O               | 2    | LED indicator 1                                                                                                                                                                                                                                  |                                                             |  |  |

| 103        | LED2-0   | lpu/O               | 2    | LED indicator 0                                                                                                                                                                                                                                  |                                                             |  |  |

| 104        | LED1-2   | lpu/O               | 1    | LED indicator 2                                                                                                                                                                                                                                  |                                                             |  |  |

| 105        | LED1-1   | lpu/O               | 1    | LED indicator 1                                                                                                                                                                                                                                  |                                                             |  |  |

| 106        | LED1-0   | lpu/O               | 1    | LED indicator 0                                                                                                                                                                                                                                  |                                                             |  |  |

| 107        | MDC      | lpu                 | All  | Switch or PHY[5] MII mana                                                                                                                                                                                                                        | agement data clock                                          |  |  |

| 108        | MDIO     | I/O                 | All  | Switch or PHY[5] MII mana<br>Features internal pull down                                                                                                                                                                                         | agement data I/O.<br>n to define pin state when not driven. |  |  |

| 109        | SPIQ     | Otri                | All  | (1) SPI serial data output in SPI slave mode; (2) Not used in I2C master mode. See "pin# 113."                                                                                                                                                   |                                                             |  |  |

| 110        | SPIC/SCL | I/O                 | All  | (1) Input clock up to 5MHz in SPI slave mode; (2) Output clock at 81KHz in I2C master mode. See "pin# 113."                                                                                                                                      |                                                             |  |  |

| 111        | SPID/SDA | I/O                 | All  | (1) Serial data input in SPI slave mode; (2) Serial data input/output in I2C master mode See "pin# 113."                                                                                                                                         |                                                             |  |  |

| 112        | SPIS_N   | lpu                 | All  | Active low. (1) SPI data transfer start in SPI slave mode. When SPIS_N is high, the KS8995M is deselected and SPIQ is held in high impedance state, a high-to-low transition to initiate the SPI data transfer; (2) Not used in I2C master mode. |                                                             |  |  |

| 113        | PS1      | lpd                 |      | Serial bus configuration pin<br>If EEPROM is not present,<br>default (00)                                                                                                                                                                        | n<br>the KS8995M will start itself with chip                |  |  |

|            |          |                     |      | Pin Config.                                                                                                                                                                                                                                      | Serial Bus Configuration                                    |  |  |

|            |          |                     |      | PS[1:0]=00                                                                                                                                                                                                                                       | I2C Master Mode for EEPROM                                  |  |  |

|            |          |                     |      | PS[1:0]=01                                                                                                                                                                                                                                       | Reserved                                                    |  |  |

|            |          |                     |      | PS[1:0]=10                                                                                                                                                                                                                                       | SPI Slave Mode for CPU Interface                            |  |  |

|            |          |                     |      | PS[1:0]=11                                                                                                                                                                                                                                       | Factory Test Mode (BIST)                                    |  |  |

| 114        | PS0      | lpd                 |      | Serial bus configuration pi                                                                                                                                                                                                                      | n. See <i>"pin# 113."</i>                                   |  |  |

| 115        | RST_N    | lpu                 |      | Reset the KS8995M. Active low.                                                                                                                                                                                                                   |                                                             |  |  |

| 116        | GNDD     | Gnd                 |      | Digital ground                                                                                                                                                                                                                                   |                                                             |  |  |

| 117        | VDDC     | Р                   |      | 1.8V digital core V <sub>DD</sub>                                                                                                                                                                                                                |                                                             |  |  |

| 118        | TESTEN   | lpd                 |      | NC for normal operation.                                                                                                                                                                                                                         | NC for normal operation. Factory test pin.                  |  |  |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

Ipu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                                    |

|------------|----------|---------------------|------|-------------------------------------------------------------------------------------------------|

| 119        | SCANEN   | lpd                 |      | NC for normal operation. Factory test pin.                                                      |

| 120        | NC       | NC                  |      | No Connect                                                                                      |

| 121        | X1       | I                   |      | 25MHz crystal clock connection/or 3.3V tolerant oscillator input. Oscillator should be ±100ppm. |

| 122        | X2       | 0                   |      | 25MHz crystal clock connection                                                                  |

| 123        | VDDAP    | Р                   |      | 1.8V analog V <sub>DD</sub> for PLL                                                             |

| 124        | GNDA     | Gnd                 |      | Analog ground                                                                                   |

| 125        | VDDAR    | Р                   |      | 1.8V analog V <sub>DD</sub>                                                                     |

| 126        | GNDA     | Gnd                 |      | Analog ground                                                                                   |

| 127        | GNDA     | Gnd                 |      | Analog ground                                                                                   |

| 128        | TEST2    | NC                  |      | NC for normal operation. Factory test pin.                                                      |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

lpu = Input w/ internal pull-up

lpd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

# Pin Description (by Name)

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                         |  |

|------------|----------|---------------------|------|--------------------------------------------------------------------------------------|--|

| 39         | FXSD4    | I                   | 4    | Fiber signal detect/factory test pin. Pull-down for TX mode.                         |  |

| 38         | FXSD5    | I                   | 5    | Fiber signal detect/factory test pin. Pull-down for TX mode                          |  |

| 124        | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 42         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 44         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 2          | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 16         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 30         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 6          | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 12         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 21         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 27         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 34         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 40         | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 120        | NC       | NC                  |      | No connect                                                                           |  |

| 127        | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 126        | GNDA     | Gnd                 |      | Analog ground                                                                        |  |

| 49         | GNDD     | Gnd                 |      | Digital ground                                                                       |  |

| 88         | GNDD     | Gnd                 |      | Digital ground                                                                       |  |

| 116        | GNDD     | Gnd                 |      | Digital ground                                                                       |  |

| 58         | GNDD     | Gnd                 |      | Digital ground                                                                       |  |

| 76         | GNDD     | Gnd                 |      | Digital ground                                                                       |  |

| 99         | GNDD     | Gnd                 |      | Digital ground                                                                       |  |

| 17         | ISET     |                     |      | Set physical transmit output current. Pull-down with a 3.01k $\!\Omega$ 1% resistor. |  |

| 106        | LED1-0   | Ipu/O               | 1    | LED indicator 0                                                                      |  |

| 105        | LED1-1   | lpu/O               | 1    | LED indicator 1                                                                      |  |

| 104        | LED1-2   | lpu/O               | 1    | LED indicator 2                                                                      |  |

| 103        | LED2-0   | lpu/O               | 2    | LED indicator 0                                                                      |  |

| 102        | LED2-1   | lpu/O               | 2    | LED indicator 1                                                                      |  |

| 101        | LED2-2   | lpu/O               | 2    | LED indicator 2                                                                      |  |

| 98         | LED3-0   | Ipu/O               | 3    | LED indicator 0                                                                      |  |

### Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

Ipu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

lpu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function                                                                                                                                                                                                             |                                            |            |  |

|------------|----------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------|--|

| 97         | LED3-1   | lpu/O               | 3    | LED indicator 1                                                                                                                                                                                                          |                                            |            |  |

| 96         | LED3-2   | lpu/O               | 3    | LED indicator 2                                                                                                                                                                                                          |                                            |            |  |

| 95         | LED4-0   | lpu/O               | 4    | LED indicator 0                                                                                                                                                                                                          |                                            |            |  |

| 94         | LED4-1   | lpu/O               | 4    | LED indicator 1                                                                                                                                                                                                          |                                            |            |  |

| 93         | LED4-2   | lpu/O               | 4    | LED indicator 2                                                                                                                                                                                                          |                                            |            |  |

| 92         | LED5-0   | lpu/O               | 5    | LED indicator 0                                                                                                                                                                                                          |                                            |            |  |

| 91         | LED5-1   | lpu/O               | 5    | LED indicator 1. Strap option: PU (default): enable FPD: tristate all PHY MII output. See "pin# 86 SCON                                                                                                                  |                                            |            |  |

| 90         | LED5-2   | lpu/O               | 5    | LED indicator 2. Strap option: Aging setup. See "A (default) = Aging Enable; PD = Aging disable                                                                                                                          | <i>ging"</i> secti                         | on.        |  |

| 107        | MDC      | lpu                 | All  | Switch or PHY[5] MII management data clock.                                                                                                                                                                              |                                            |            |  |