# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### KSZ8692PB, KSZ8692PB-S

#### Integrated Networking and Communications Controller

Rev. 5.0

#### **General Description**

The KSZ8692PB, KSZ8692PB-S is a highly integrated System-on-Chip (SoC) containing an ARM 922T 32-bit processor and a rich set of peripherals to address the cost-sensitive, high-performance needs of a wide variety of high bandwidth networking and communications applications.

The KSZ9692PB-S is a small package version of KSZ9692PB and it supports 16 bit DDR data width.

#### **Features**

#### ARM 922T High-Performance Processor Core

- 250 MHz ARM 922T RISC processor core

- 8KB I-cache and 8KB D-cache

- Configurable Memory Management Unit (MMU) for Linux and WinCE

#### **Memory Controller**

- 8/16-bit external bus interface for FLASH, ROM, SRAM, and external I/O

- NAND FLASH controller

- 200MHz 32-bit DDR controller

- Two JEDEC Specification JESD82-1 compliant differential clock drivers for a glueless DDR interface solution

#### Ethernet Interfaces

- Two Ethernet (10/100 Mbps) MACs

- MII interface

- Fully compliant with IEEE 802.3 Ethernet standards

#### **IP Security Engine**

- Hardware IPSec Engine guarantees 100Mbps VPN

- Secure Socket Layer Support

- DES/3DES/AES/RC4 Cyphers

- MD-5, SHA-1, SHA-256 Hashing Algorithms

- HMAC

- SSLMAC

#### **PCI Interface**

- Version PCI 2.3

- 32-bit 33/66MHz

- Integrated PCI Arbiter supports three external masters

- · Configurable as Host bridge or Guest device

• Glueless Support for mini-PCI or CardBus devices

#### **Dual High Speed USB 2.0 Interfaces**

- Two USB2.0 ports with integrated PHY

- Can be configured as 2-port host, or host + device

#### **SDIO/SD Host Controller**

- Meets SD Host Controller Standard Specification Version 1.0

- Meets SDIO card specification Version 1.0

#### **DMA Controllers**

• Dedicated DMA channels for PCI, USB, IPSec, SDIO and Ethernet ports.

#### Peripherals

- Four high-speed UART ports up to 5 Mbps

- Two programmable 32-bit timers with watchdog timer capability

- Interrupt Controller

- Twenty GPIO ports

- One shared SPI/I2C interface

- One I2S port

#### Debugging

- ARM9 JTAG debug interface

- JTAG Boundary Scan Support

#### **Power Management**

- CPU and system clock speed step-down options

- Ethernet port Wake-on-LAN

- DDR and PCI power down

#### **Operating Voltage**

- 1.3V power for core

- 3.3V power for I/O

- 2.5V or 2.6V power for DDR memory interface

#### **Reference Hardware and Software Evaluation Kit**

- Hardware evaluation Kit

- Software Evaluation Kit includes WinCE BSP, Open WRT BSP, Linux based SOHO Router packages

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

#### Applications

- Enhanced residential gateways

- High-end printer servers

- Voice-over-Internet Protocol (VoIP) systems

- IP-based multimedia systems

- Wireless Access Points or Mesh Nodes

- USB device servers

- Industrial control

- Video surveillance systems

- SMB/SME Network Security Applications, including VPN Routers

### **Ordering Information**

| Part Number | Temp.<br>Range | Package      | Lead<br>Finish |

|-------------|----------------|--------------|----------------|

| KSZ8692PB,  | 0°C to 70°C    | 400-Pin PBGA | Pb-Free        |

| KSZ8692PBI  | -40°C to 85°C  | 400-Pin PBGA | Pb-Free        |

| KSZ8692PB-S | 0°C to 70°C    | 400-Pin PBGA | Pb-Free        |

### **Revision History**

| Revision | Date     | Summary of Changes                                                                           |  |  |  |

|----------|----------|----------------------------------------------------------------------------------------------|--|--|--|

| 1.0      | 9/23/08  | Preliminary Release                                                                          |  |  |  |

| 2.0      | 3/10/09  | Power Sequencing, Added A1 (PMEN) to pin list, 1.3V Supply for Core, Power Consumption table |  |  |  |

| 3.0      | 8/10/09  | DDR Data Width Changed to 16-bit                                                             |  |  |  |

| 4.0      | 01/28/10 | DDR Data Width Changed to 32-bit                                                             |  |  |  |

| 4.1      | 06/10/10 | Remove NAND Boot support                                                                     |  |  |  |

| 5.0      | 04/14/11 | Add small packet device KSZ9692PB-S                                                          |  |  |  |

|          | 09/13/11 | Change the port 0 to port 2 at Figure 12 and 13. Change RSVD to DATA[3116] in Figure 20.     |  |  |  |

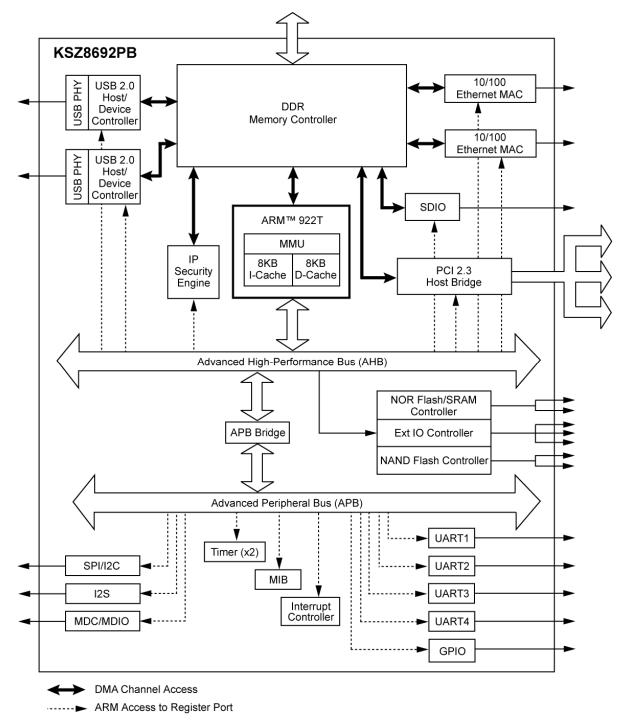

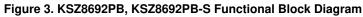

#### **Block Diagram**

Figure 1. KSZ8692PB, KSZ8692PB-S Block Diagram

#### Contents

| System Level Applications                        |    |

|--------------------------------------------------|----|

| Functional Description                           |    |

| ARM High-Performance Processor                   |    |

| FLASH/ROM/SRAM Memory and External I/O Interface |    |

| NAND Flash Memory Interface                      |    |

| DDR Controller                                   |    |

| SDIO/SD Host Controller                          |    |

| IP Security Engine                               |    |

| USB 2.0 Interface                                |    |

| PCI Interface                                    |    |

| Ethernet MAC Ports (Port 0 = WAN, Port 1 = LAN)  |    |

| Wake-on-LAN                                      |    |

| Link Change                                      |    |

| Wake-up Packet                                   |    |

| Magic Packet                                     |    |

| IPv6 Support                                     |    |

| DMA Controller                                   |    |

| UART Interface                                   |    |

| Timers and Watchdog                              |    |

| GPIO                                             |    |

| I2C                                              |    |

| SPI                                              |    |

| I2S                                              |    |

| Interrupt Controller                             |    |

| System Level Interfaces                          |    |

| Power-up Strapping Options                       | 21 |

| Absolute Maximum Ratings                         | 25 |

| Operating Ratings                                | 40 |

| Electrical Characteristics                       | 40 |

| Timing Specifications                            | 41 |

| Signal Location Information                      |    |

| Package Information                              |    |

### List of Figures

| Figure 1. KSZ8692PB, KSZ8692PB-S Block Diagram               | 4  |

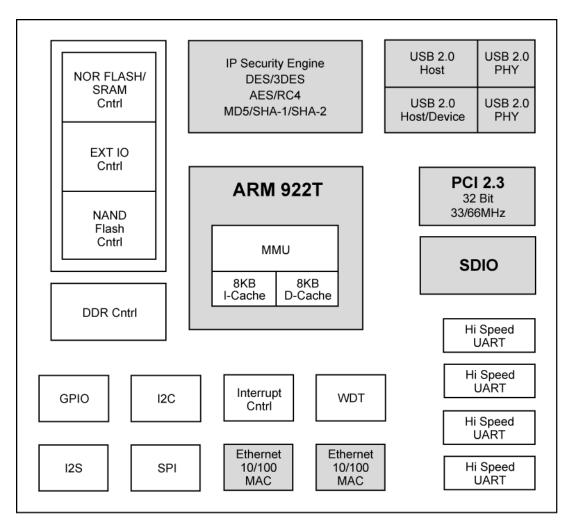

|--------------------------------------------------------------|----|

| Figure 2. Peripheral Options and Examples                    | 8  |

| Figure 3. KSZ8692PB, KSZ8692PB-S Functional Block Diagram    | 25 |

| Figure 4. Static Memory Interface Examples                   | 27 |

| Figure 5. External I/O Interface Examples                    | 27 |

| Figure 6. 8-bit NAND Interface Examples                      | 28 |

| Figure 7. 16-bit NAND Interface Examples                     | 29 |

| Figure 8. Single 16-bit DDR Memory Devices Interface Example | 30 |

| Figure 9. Four8-bit DDR Memory Devices Interface Example     | 31 |

| Figure 10. Burst DDR Read Timing                             | 32 |

| Figure 11. Burst DDR Write Timing                            | 32 |

| Figure 12. USB 2.0 Configuration as Two-Port Host            | 34 |

| Figure 13. USB 2.0 Configuration as Host + Device            | 34 |

| Figure 14. Reset Circuit                                     | 39 |

| Figure 15. Power and Clocks                                  | 39 |

| Figure 16. Reset Timing                                      | 41 |

| Figure 17. Static Memory Read Cycle                          | 41 |

| Figure 18. Static Memory Write Cycle                         | 42 |

| Figure 19. External I/O Read and Write Cycles                | 42 |

| Figure 21. KSZ9692PB 400-Pin PBGA (24X24X2.33 MM)            | 45 |

| Figure 22. KSZ8692PB-S 400-Pin PBGA (17X17X1.4 MM)           | 46 |

#### List of Tables

| Table 1. Reset Timing Parameters                      | 41 |

|-------------------------------------------------------|----|

| Table 2. Programmable Static Memory Timing Parameters | 42 |

| Table 3. External I/O Memory Timing Parameters        | 43 |

| Table 4. Programmable External I/O Timing Parameters  | 43 |

### **System Level Applications**

Figure 2. Peripheral Options and Examples

### Pin Description: Signal Description by Group

| Pin Number                 | Pin Name         | Pin Type | Pin Description                                                                                                                                                                                                                                                                                     |

|----------------------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Interf              | ace              |          |                                                                                                                                                                                                                                                                                                     |

| R5                         | RESETN           | I        | Reset, asserted Low.                                                                                                                                                                                                                                                                                |

|                            |                  |          | RESETN will force the KSZ8692PB, KSZ8692PB-S to reset ARM9 CPU and all functional blocks. Once asserted, RESETN must remain asserted for a minimum duration of 256 system clock cycles. When in the reset state, all the output pins are put into Tri-state and all open drain signals are floated. |

| N5                         | WRSTO            | 0        | Watchdog Timer Reset Output                                                                                                                                                                                                                                                                         |

|                            |                  |          | When the Watchdog Timer expires, this signal will be asserted for at least 200 msec.                                                                                                                                                                                                                |

| W1                         | XCLK2            | I        | System Clock Input 2.                                                                                                                                                                                                                                                                               |

|                            |                  |          | External crystal or clock input 2. The clock frequency should be                                                                                                                                                                                                                                    |

|                            |                  |          | 25MHz ± 50ppm.                                                                                                                                                                                                                                                                                      |

| Y1                         | XCLK1            | I        | System Clock Input 1.                                                                                                                                                                                                                                                                               |

|                            |                  |          | Used with XCLK1 pin when other polarity of crystal is needed. This is unused for a normal clock input.                                                                                                                                                                                              |

| H19                        | CLK25MHz         | 0        | 25MHz output to external PHY                                                                                                                                                                                                                                                                        |

| Y15, Y14                   | DDCLKO[1:0]      | 0        | DDR Clock Out [1:0].                                                                                                                                                                                                                                                                                |

|                            |                  |          | Output of the internal system clock, it is also used as the clock signal for DDR interface.                                                                                                                                                                                                         |

| W15, W14                   | DDCLKON[1:0]     | 0        | The negative of differential pair of DDR Clock Out [1:0].                                                                                                                                                                                                                                           |

|                            |                  |          | Output of the internal system clock, it is also used as the clock signal for DDR interface.                                                                                                                                                                                                         |

| U13                        | SDCLKEO          | 0        | Clock Enable output for SDRAM (for Power Down Mode)                                                                                                                                                                                                                                                 |

| T7, U7                     | VREF             | I        | Reference Voltage for SSTL interface.                                                                                                                                                                                                                                                               |

|                            |                  |          | Must be half of the voltage for the DDR VDD supply. See EIA/JEDEC standard EIA/JESD8-9 (Stub series terminated logic for 2.5V, SSTL_2)                                                                                                                                                              |

| W3                         | SDOCLK           | 0        | DDR Clock Out for loopback from De-skew PLL                                                                                                                                                                                                                                                         |

| Y3                         | SDICLK           | I        | DDR Clock In from loopback to De-skew PLL. This pin must connect to SDOCLK with appropriate de-skew length. See Engineering Evaluation Design Kit for detailed implementation.                                                                                                                      |

| Y17, Y16                   | DDCLKO[3:2]      | 0        | Factory Reserved                                                                                                                                                                                                                                                                                    |

| W17, W16                   | DDCLKON[3:2]     | 0        | Factory Reserved                                                                                                                                                                                                                                                                                    |

| NAND/SRAM/                 | ROM/EXIO Interfa | се       |                                                                                                                                                                                                                                                                                                     |

| L2, K1, K2,                | SADDR[230]       | 0        | SRAM Address Bus.                                                                                                                                                                                                                                                                                   |

| J3, H5, H4,<br>J2, H3, J1, |                  |          | The 24-bit address bus covers 16M word memory space of                                                                                                                                                                                                                                              |

| H2, G5, H1,                |                  |          | ROM/SRAM/FLASH, and 16M byte external I/O banks.                                                                                                                                                                                                                                                    |

| G3, G4, G2,                |                  |          | This address bus is shared between ROM/SRAM/FLASH/EXTIO devices.                                                                                                                                                                                                                                    |

| F1, G1, F2,<br>F3, F5, F4, |                  |          |                                                                                                                                                                                                                                                                                                     |

| E1, E2, E3                 |                  |          |                                                                                                                                                                                                                                                                                                     |

| T2, U1, L5,                | SDATA[150]       | lpu/O    | SRAM DATA Bus.                                                                                                                                                                                                                                                                                      |

| N4, P3, R2,<br>T1, M4, K5, |                  |          | Bidirectional Bus for 16-bit DATA In and DATA Out. The KSZ8692PB,                                                                                                                                                                                                                                   |

| N3, P2, R1,                |                  |          | KSZ8692PB-S also supports 8-bit data bus for ROM/SRAM/FLASH/EXTIO cycles.                                                                                                                                                                                                                           |

| L4, M3, P1,                |                  |          | This data bus is shared between NAND, ROM/SRAM/FLASH/EXTIO devices.                                                                                                                                                                                                                                 |

| K4                         |                  |          |                                                                                                                                                                                                                                                                                                     |

| Pin Number | Pin Name  | Pin Type | Pin Description                                                                                                                                                                       |

|------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L3         | ECS2      | 0        |                                                                                                                                                                                       |

| L3         | EC32      | 0        | External I/O Chip Select 2, asserted Low.                                                                                                                                             |

|            |           |          | Three External I/O banks are provided for external memory-mapped I/O operations. Each I/O bank stores up to 16Kbytes. ECSN signals indicate which of the three I/O banks is selected. |

| N1         | ECS1      | 0        | External I/O Chip Select 1, asserted Low.                                                                                                                                             |

|            |           |          | Three External I/O banks are provided for external memory-mapped I/O operations. Each I/O bank stores up to 16Kbytes. ECSN signals indicate which of the three I/O banks is selected. |

| M2         | ECS0      | 0        | External I/O Chip Select 0, asserted Low.                                                                                                                                             |

|            |           |          | Three External I/O banks are provided for external memory-mapped I/O operations. Each I/O bank stores up to 16Kbytes. ECSN signals indicate which of the three I/O banks is selected. |

| K3         | RCSN1     | 0        | ROM/SRAM/FLASH(NOR) Chip select 1, asserted Low.                                                                                                                                      |

|            |           |          | The KSZ8692PB, KSZ8692PB-S can access up to two external ROM/SRAM/FLASH memory banks. The RCSN pins can be controlled to map the CPU addresses into physical memory banks.            |

| L1         | RCSN0     | 0        | ROM/SRAM/FLASH(NOR) Chip select 0, asserted Low.                                                                                                                                      |

|            |           |          | The KSZ8692PB, KSZ8692PB-S can access up to two external ROM/SRAM/FLASH memory banks. The RCSN pins can be controlled to map the CPU addresses into physical memory banks.            |

|            |           |          | This bank is configurable as boot option                                                                                                                                              |

| N2         | EWAITN    | I        | External Wait asserted Low.                                                                                                                                                           |

|            |           |          | This signal is asserted when an external I/O device or ROM/SRAM/FLASH(NOR) bank needs more access cycles than those defined in the corresponding control register.                    |

| M1         | EROEN     | lpd/O    | ROM/SRAM/FLASH(NOR) and EXTIO Output Enable, asserted Low.                                                                                                                            |

|            | (WRSTPLS) |          | When asserted, this signal controls the output enable port of the specified ROM/SRAM/FLASH memory and EXTIO device.                                                                   |

| J5         | ERWEN1    | 0        | ROM/SRAM/FLASH(NOR) and EXTIO Write Byte Enable, asserted Low.                                                                                                                        |

|            |           |          | When asserted, this signal controls the byte write enable of the memory device SDATA[158] for ROM/SRAM/FLASH and EXTIO access.                                                        |

| J4         | ERWEN0    | lpd/O    | ROM/SRAM/FLASH(NOR) and EXTIO Write Byte Enable, asserted Low.                                                                                                                        |

|            |           |          | When asserted, this signal controls the byte write enable of the memory device SDATA[70 or 150] for ROM/SRAM/FLASH and EXTIO access.                                                  |

| R3         | NCLE      | lpd/O    | NAND command Latch Enable                                                                                                                                                             |

|            |           |          | NCLE controls the activating path for command sent to NAND flash.                                                                                                                     |

| U2         | NALE      | Ipd/O    | NAND Address Latch Enable                                                                                                                                                             |

|            |           |          | NALE controls the activating path for address sent to NAND flash.                                                                                                                     |

| Т3         | NCEN1     | 0        | NAND Bank Chip Enable 1, asserted low                                                                                                                                                 |

|            |           |          | NAND device bank 1 selection control.                                                                                                                                                 |

| V3         | NCEN0     | 0        | NAND Bank Chip Enable 0, asserted low                                                                                                                                                 |

|            |           |          | NAND device bank 0 selection control.                                                                                                                                                 |

| R4         | NREN      | lpu/O    | NAND Read Enable, asserted low                                                                                                                                                        |

| T4         | NWEN      | lpu/O    | NAND Write Enable, asserted low                                                                                                                                                       |

| Pin Number                                                                                                                                                                     | Pin Name   | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U3                                                                                                                                                                             | NWPN       | lpu/O    | NAND Write Protection, asserted low                                                                                                                                                                                                                                                                                                                                                |

| P4, U4                                                                                                                                                                         | NRBN[1:0]  |          | NAND Ready/Busy, asserted low for busy.                                                                                                                                                                                                                                                                                                                                            |

| DDR Interfac                                                                                                                                                                   | e          |          |                                                                                                                                                                                                                                                                                                                                                                                    |

| T17, V18,<br>U17, T16,<br>W20, W19,<br>Y20, Y19,<br>W18, V17,<br>U16, T15,<br>Y18, V16                                                                                         | DADDR[130] | 0        | DDR Address Bus.                                                                                                                                                                                                                                                                                                                                                                   |

| V13, U11,<br>V12, W13,<br>Y13, W12,<br>V11, U10,<br>V10, Y11,<br>W10, U9,<br>Y10, V9, W9,<br>Y9, W8, Y8,<br>Y7, W7, V7,<br>Y6, W6, V6,<br>Y5, V5, W5,<br>U5, T5, Y4,<br>V4, W4 | DDATA[310] | I/O      | DDR Data Bus.                                                                                                                                                                                                                                                                                                                                                                      |

| T13, V14                                                                                                                                                                       | BA[1:0]    | 0        | DDR Bank Address.                                                                                                                                                                                                                                                                                                                                                                  |

| U14                                                                                                                                                                            | CSN        | 0        | DDR Chip Select, asserted Low.<br>Chip select pins for DDR, the KSZ8692PB, KSZ8692PB-S supports only one<br>DDR bank.                                                                                                                                                                                                                                                              |

| T14                                                                                                                                                                            | RASN       | 0        | DDR Row Address Strobe, asserted Low.                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                |            |          | The Row Address Strobe pin for DDR.                                                                                                                                                                                                                                                                                                                                                |

| U15                                                                                                                                                                            | CASN       | 0        | DDR Column Address Strobe, asserted Low.                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                |            |          | The Column Address Strobe pin for DDR.                                                                                                                                                                                                                                                                                                                                             |

| V15                                                                                                                                                                            | WEN        | 0        | DDR Write Enable, asserted Low.                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                |            |          | The write enable signal for DDR.                                                                                                                                                                                                                                                                                                                                                   |

| T12, Y12,<br>U8, T6                                                                                                                                                            | DM[3:0]    | 0        | DDR Data Input/Output Mask<br>Data Input/Output mask signals for DDR. DM is sampled High and is an output<br>mask signal for write accesses and an output enable signal for read accesses.<br>Input data is masked during a Write cycle. DM0 corresponds to DDATA[7:0],<br>DM1 corresponds to DDATA[15:8], DM2 corresponds to DDATA[23:16] and<br>DM3 corresponds to DDATA[31:24]. |

| U12, W11,<br>V8, U6                                                                                                                                                            | DQS[3:0]   | I/O      | DDR only Data Strobe<br>Input with read data, output with write data. DQS0 corresponds to DDATA[7:0],<br>DQS1 corresponds to DDATA[15:8], DQS2 corresponds to DDATA[23:16] and<br>DQS3 corresponds to DDATA[31:24].                                                                                                                                                                |

| 511                                                                                                                                                                            |            |          |                                                                                                                                                                                                                                                                                                                                                                                    |

| Ethernet Por                                                                                                                                                                   |            | 1.1/2    |                                                                                                                                                                                                                                                                                                                                                                                    |

| M16                                                                                                                                                                            | P0_RXC     | Ipd/O    | MAC mode MII: input RX clock                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                |            |          | PHY mode MII: output RX clock                                                                                                                                                                                                                                                                                                                                                      |

|                       |             | -               |                                                 |

|-----------------------|-------------|-----------------|-------------------------------------------------|

| Pin Number            | Pin Name    | Pin Type        | Pin Description                                 |

| P18, N17,<br>P17, N16 | P0_RXD[3:0] | I               | RX data[3:0]                                    |

| N18                   | P0_RXDV     | I               | MII mode: RX data valid                         |

| P19                   | P0_RXER     | I               | MII mode: RX error                              |

| M17                   | P0_CRS      | I               | MAC mode MII: input carrier sense               |

| P20                   | P0_COL      | I               | MAC mode MII: input collision                   |

| M18                   | P0_TXC      | lpd/O           | MAC mode MII: input TX clock                    |

|                       |             |                 | PHY mode MII: output TX clock                   |

| L17, M19,<br>N20, N19 | P0_TXD[3:0] | 0               | TX data[3:0]                                    |

| L16                   | P0_TXEN     | 0               | MII: TX enable                                  |

| Ethernet Port         | 1           |                 |                                                 |

| K19                   | P1_RXC      | Ipd/O           | MAC mode MII: input RX clock                    |

|                       |             |                 | PHY mode MII: output RX clock                   |

| L20, L19,<br>L18, M20 | P1_RXD[3:0] | I               | RX data[3:0]                                    |

| K16                   | P1_RXDV     | I               | MII mode: RX data valid                         |

| K17                   | P1_RXER     | I               | MII mode: RX error                              |

| K18                   | P1_CRS      | I               | MAC mode MII: input carrier sense               |

| K20                   | P1_COL      | I               | MAC mode MII: input collision                   |

| J17                   | P1_TXC      | Ipd/O           | MAC mode MII: input TX clock                    |

|                       |             |                 | PHY mode MII: output TX clock                   |

| H20, J19,<br>J18, J20 | P1_TXD[3:0] | 0               | TX data[3:0] output.                            |

| J16                   | P1_TXEN     | 0               | MII: TX enable                                  |

| USB Interfac          | e           |                 |                                                 |

| G19                   | U1P         | I/O<br>(analog) | USB port 1 differential + signal                |

| G20                   | U1M         | I/O<br>(analog) | USB port 1 differential - signal                |

| F19                   | U2P         | I/O<br>(analog) | USB port 2 differential + signal                |

| F20                   | U2M         | I/O<br>(analog) | USB port 2 differential - signal                |

| G17                   | USBXI       | l (analog)      | Crystal in for USB PLL                          |

| G18                   | USBXO       | O<br>(analog)   | Crystal out for USB PLL                         |

| H16                   | USBREXT     | l (analog)      | Connect to an external resistor 3.4K ohm to GND |

| G16                   | USBTEST     | O<br>(Analog)   | USB analog test output (factory reserved)       |

|                                    | i v                      | · · · ·                  | tion by Group (Continued)                                                                                      |

|------------------------------------|--------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|

| Pin Number                         | Pin Name                 | Pin Type                 | Pin Description                                                                                                |

| G15                                | USBCFG                   | I                        | USB port 2 configuration                                                                                       |

|                                    |                          |                          | "1" = port 2 is host                                                                                           |

|                                    |                          |                          | "0" = port 2 is device                                                                                         |

|                                    |                          |                          | ( port 1 is always host)                                                                                       |

| F18                                | USBHOVC0                 | I                        | Over current sensing input for Host Controller downstream port 1                                               |

| F15                                | USBHOVC1                 | I                        | Over current sensing input for Host Controller downstream port 2                                               |

| F17                                | USBHPWR0                 | lpu/O<br>(open<br>drain) | Power switching control output for downstream port 1; open drain output                                        |

| F16                                | USBHPWR1                 | lpu/O<br>(open<br>drain) | Power switching control output for downstream port 2; open drain output                                        |

| SDIO Interfac                      | 9                        |                          |                                                                                                                |

| D14                                | KCMD                     | lpd/O                    | SD 4-bit mode: Command line                                                                                    |

|                                    |                          |                          | SD 1-bit mode: Command line                                                                                    |

| C18                                | KCLK                     | Ipd/O                    | SDIO/SD Clock                                                                                                  |

| C15                                | KDATA3                   | I/O                      | SD 4-bit mode : data line 3                                                                                    |

|                                    |                          |                          | SD 1-bit mode : not used                                                                                       |

| C16                                | KDATA2                   | I/O                      | SD 4-bit mode : data line 2 or read wait (optional)                                                            |

|                                    |                          |                          | SD 1-bit mode : read wait (optional)                                                                           |

| E13                                | KDATA1                   | I/O                      | SD 4-bit mode : data line 1 or interrupt (optional)                                                            |

|                                    |                          |                          | SD 1-bit mode : interrupt                                                                                      |

| C17                                | KDATA0                   | I/O                      | SD 4-bit mode : data line 0                                                                                    |

|                                    |                          |                          | SD 1-bit mode : data line                                                                                      |

| C14                                | KSDCDN                   | I                        | Active low used for Card Detection                                                                             |

| D13                                | KSDWP                    | I                        | Active high used for Card write protection                                                                     |

| General Purpo                      | ose I/O                  |                          |                                                                                                                |

| B14                                | SLED/GPIO[19]            | I/O                      | SDIO Line Status LED output or General Purpose I/O Pin[19]                                                     |

| B15                                | CPUINTN/                 | I/O                      | Internal CPU interrupt request or General Purpose I/O Pin[18]                                                  |

|                                    | GPIO[18]                 |                          | As CPUINTN, any interrupt generated to ARM CPU asserts logic low on this pin. Useful for software development. |

| B16, B17,<br>B18, D18,<br>E15, D19 | GPIO[17:12]              | I/O                      | General Purpose I/O Pin[17:12]                                                                                 |

| F14                                | UART 4 RTSN<br>/GPIO[11] | I/O                      | UART 4 RTS or general purpose I/O Pin[11]                                                                      |

| E16                                | UART 4 CTSN<br>/GPIO[10] | I/O                      | UART 4 CTS or general purpose I/O Pin[10]                                                                      |

| E17                                | UART 3 RTSN<br>/GPIO[9]  | I/O                      | UART 3 RTS or general purpose I/O Pin[9]                                                                       |

| E19                                | UART 3 CTSN<br>/GPIO[8]  | I/O                      | UART 3 CTS or general purpose I/O Pin[8]                                                                       |

| E20                                | UART 2 RTSN<br>/GPIO[7]  | I/O                      | UART 2 RTS or general purpose I/O Pin[7]                                                                       |

| Pin Number            | Pin Name                | Pin Type | Pin Description                                                                                                                                                                                                                                               |

|-----------------------|-------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E18                   | UART 2 CTSN<br>/GPIO[6] | I/O      | UART 2 CTS or general purpose I/O Pin[6]                                                                                                                                                                                                                      |

| U20, U19              | TOUT[1:0]/<br>GPIO[5:4] | I/O      | Timer 1/0 out or General Purpose I/O Pin[5:4]                                                                                                                                                                                                                 |

| V20, T18,<br>V19, U18 | EINT[3:0]/<br>GPIO[3:0] | I/O      | External Interrupt Request or General Purpose I/O Pin[3:0]                                                                                                                                                                                                    |

| I2S Interface         | L                       |          | •                                                                                                                                                                                                                                                             |

| C20                   | SCKIN                   | I        | External crystal or clock input for I2S clock                                                                                                                                                                                                                 |

|                       |                         |          | The maximum supported frequency is 49.2 MHz                                                                                                                                                                                                                   |

| D20                   | SCKOUT                  | 0        | External crystal out for I2S clock                                                                                                                                                                                                                            |

| C19                   | I2S_MCLK                | 0        | I2S master clock out                                                                                                                                                                                                                                          |

|                       |                         |          | This clock is of same frequency as SCKIN                                                                                                                                                                                                                      |

| B20                   | I2S_BCLK                | 0        | I2S bit clock out                                                                                                                                                                                                                                             |

| B19                   | I2S_LRCLK               | 0        | Left/right select                                                                                                                                                                                                                                             |

| A19                   | I2S_SDO                 | 0        | Serial data out                                                                                                                                                                                                                                               |

| A20                   | I2S_SDI                 | Ι        | Serial data in                                                                                                                                                                                                                                                |

| MDIO/MDC Int          | erface                  |          |                                                                                                                                                                                                                                                               |

| H18                   | MDC                     | lpu/O    | Clock for station management                                                                                                                                                                                                                                  |

| H17                   | MDIO                    | lpu/O    | Serial data for station management                                                                                                                                                                                                                            |

| I2C/SPI Interfa       | ice                     |          | •                                                                                                                                                                                                                                                             |

| E14                   | SPCK_SCL                | lpu/O    | SPI mode: master clock Output                                                                                                                                                                                                                                 |

|                       |                         |          | I2C mode: serial clock output                                                                                                                                                                                                                                 |

| D17                   | SPMOSI_SDA              | lpu/O    | SPI mode: master data out, slave data in                                                                                                                                                                                                                      |

|                       |                         |          | I2C mode: serial data                                                                                                                                                                                                                                         |

| D16                   | SPMISO                  | I        | SPI master data in, slave data out                                                                                                                                                                                                                            |

| D15                   | SPICS                   | lpu/O    | SPI chip select                                                                                                                                                                                                                                               |

| F13                   | SPI_RDY                 | I        | Micrel SPI mode ready signal                                                                                                                                                                                                                                  |

| PCI Interface         | Signals                 |          | ·                                                                                                                                                                                                                                                             |

| C3                    | PRSTN                   | Ι        | PCI Reset, asserted Low                                                                                                                                                                                                                                       |

|                       |                         |          | In Host Bridge Mode, the PCI Reset pin is an input. This pin as well as the reset pin of all the devices on the PCI bus could be driven by WRSTO.                                                                                                             |

|                       |                         |          | In Guest Bridge Mode, this pin is input. The system reset to drive this pin.                                                                                                                                                                                  |

| B2                    | PCLK                    | I        | PCI Bus Clock input.                                                                                                                                                                                                                                          |

|                       |                         |          | This signal provides the timing for the PCI bus transactions. This signal is used to drive the PCI bus interface and the internal PCI logic. All PCI bus signals are sampled on the rising edges of the PCLK. PCLK can operate from 20MHz to 33MHz, or 66MHz. |

| E4                    | GNT3N                   | 0        | PCI Bus Grant 3                                                                                                                                                                                                                                               |

|                       |                         |          | Assert Low.                                                                                                                                                                                                                                                   |

|                       |                         |          | In Host Bridge Mode, this is an output signal from the internal PCI arbiter to grant PCI bus access to the master driving REQ3N.                                                                                                                              |

|                       |                         |          | In Guest Bridge Mode, this is unused.                                                                                                                                                                                                                         |

| Pin Number                                                                                                                                                          | Pin Name | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D4                                                                                                                                                                  | GNT2N    | 0        | PCI Bus Grant 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                     |          |          | Assert Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                     |          |          | In Host Bridge Mode, this is an output signal from the internal PCI arbiter to grant PCI bus access to the master driving REQ2N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                     |          |          | In Guest Bridge Mode, this is unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B1                                                                                                                                                                  | GNT1N    | 0        | PCI Bus Grant 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                     |          |          | Assert Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                     |          |          | In Host Bridge Mode, this is an output signal from the internal PCI arbiter to grant PCI bus access to the master driving REQ1N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                     |          |          | In Guest Bridge Mode, this is an output signal to indicate to the external PCI bus arbiter that KSZ8692PB, KSZ8692PB-S is requesting access to the PCI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D3                                                                                                                                                                  | REQ3N    | I        | PCI Bus Request 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                     |          |          | Assert Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                     |          |          | In Host Bridge Mode, this is an input signal from the external PCI device to request for PCI bus access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |