# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Integrated 5-Port 10/100 Managed Ethernet Switch with MII/RMII Interface

### Features

### Advanced Switch Features

- IEEE 802.1q VLAN Support for up to 128 Active VLAN Groups (Full-Range 4096 of VLAN IDs)

- Static MAC Table Supports up to 32 Entries

- VLAN ID Tag/Untagged Options, Per Port Basis

- IEEE 802.1p/q Tag Insertion or Removal on a Per Port Basis Based on Ingress Port (Egress)

- Programmable Rate Limiting at the Ingress and Egress on a Per Port Basis

- Jitter-Free Per Packet Based Rate Limiting Support

- Broadcast Storm Protection with Percentage Control (Global and Per Port Basis)

- IEEE 802.1d Rapid Spanning Tree Protocol RSTP Support

- Tail Tag Mode (1 Byte Added Before FCS) Support at Port 5 to Inform the Processor Which Ingress Port Receives the Packet

- 1.4 Gbps High-Performance Memory Bandwidth and Shared Memory Based Switch Fabric with Fully Non-Blocking Configuration

- Dual MII with MAC 5 and PHY 5 on Port 5, SW5-MII/RMII for MAC 5 and P5-MII/RMII for PHY 5

- Enable/Disable Option for Huge Frame Size up to 2000 Bytes Per Frame

- IGMP v1/v2 Snooping (IPv4) Support for Multicast Packet Filtering

- IPv4/IPv6 QoS Support

- Support Unknown Unicast/Multicast Address and Unknown VID Packet Filtering

- Self-Address Filtering

#### **Comprehensive Configuration Register Access**

- Serial Management Interface (MDC/MDIO) to All PHYs Registers and SMI Interface (MDC/MDIO) to All Registers

- High-Speed SPI (up to 25 MHz) and I<sup>2</sup>C Master Interface to all Internal Registers

- I/O Pins Strapping and EEPROM to Program Selective Registers in Unmanaged Switch Mode

- Control Registers Configurable on the Fly (Port-Priority, 802.1p/d/q, AN...)

### **QoS/CoS Packet Prioritization Support**

- · Per Port, 802.1p and DiffServ-Based

- 1/2/4-Queue QoS Prioritization Selection

- Programmable Weighted Fair Queuing for Ratio Control

- Re-Mapping of 802.1p Priority Field Per Port Basis

#### Integrated 5-Port 10/100 Ethernet Switch

- New Generation Switch with Five MACs and Five PHYs that are Fully Compliant with the IEEE 802.3u Standard

- PHYs Designed with Patented Enhanced Mixed-Signal Technology

- Non-Blocking Switch Fabric Ensures Fast Packet Delivery by Utilizing a 1K MAC Address Lookup Table and a Store-and-Forward Architecture

- On-Chip 64Kbyte Memory for Frame Buffering (Not Shared with 1K Unicast Address Table)

- Full-Duplex IEEE 802.3x Flow Control (PAUSE) with Force Mode Option

- Half-Duplex Back Pressure Flow Control

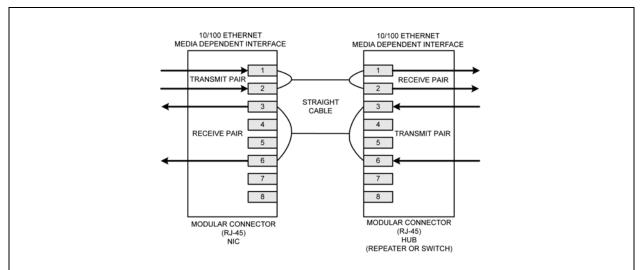

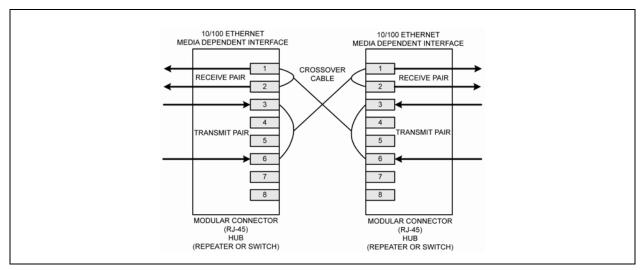

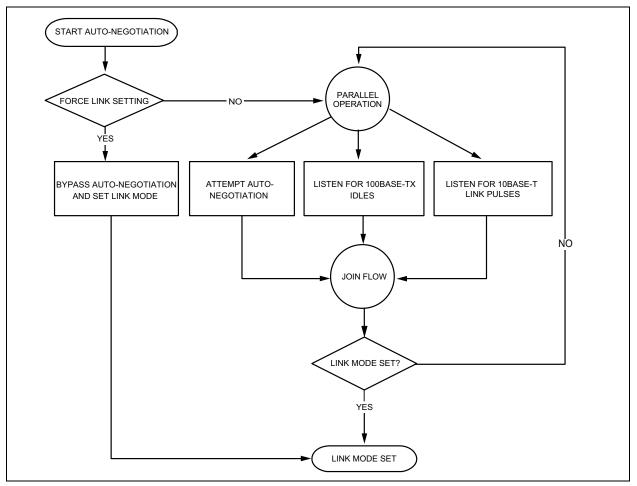

- HP Auto MDI/MDI-X and IEEE Auto Crossover Support

- SW-MII Interface Supports Both MAC Mode and PHY Mode

- 7-Wire Serial Network Interface (SNI) Support for Legacy MAC

- Per Port LED Indicators for Link, Activity, and 10/ 100 Speed

- Register Port Status Support for Link, Activity, Full-/Half-Duplex and 10/100 Speed

- LinkMD<sup>®</sup> Cable Diagnostic Capabilities

- On-Chip Terminations and Internal Biasing Technology for Cost Down and Lowest Power Consumption

#### Switch Monitoring Features

- Port Mirroring/Monitoring/Sniffing: Ingress and/or Egress Traffic to Any Port or MII

- MIB Counters for Fully Compliant Statistics Gathering; 34 MIB Counters Per Port

- Loopback Support for MAC, PHY, and Remote Diagnostic of Failure

- Interrupt for the Link Change on Any Ports

#### Low-Power Dissipation

- · Full-Chip Hardware Power-Down

- Full-Chip Software Power-Down and Per Port Software Power-Down

- Energy-Detect Mode Support <100 mW Full-Chip Power Consumption When All Ports Have No

#### Activity

- Very-Low Full-Chip Power Consumption (<0.5W) in Standalone 5-Port, without Extra Power Consumption on Transformers

- Dynamic Clock Tree Shutdown Feature

- Voltages: Single 3.3V Supply with 3.3V V<sub>DDIO</sub> and Internal 1.2V LDO Controller Enabled, or External 1.2V LDO Solution

- Analog V<sub>DDAT</sub> 3.3V Only

- V<sub>DDIO</sub> Support 3.3V, 2.5V, and 1.8V

- Low 1.2V Core Power

- Commercial Temperature Range: 0°C to +70°C

- Industrial Temperature Range: -40°C to +85°C

- Available in 128-pin PQFP and 128-pin LQFP,

- Lead-Free Packages

### **Target Applications**

- Typical

- VoIP Phone

- · Set-Top/Game Box

- Industrial Control

- IPTV POF

- SOHO Residential Gateway

- Broadband Gateway/Firewall/VPN

- Integrated DSL/Cable Modem

- Wireless LAN Access Point + Gateway

- Standalone 10/100 5-Port Switch

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### **Table of Contents**

| 1.0 Introduction                                                  | 5   |

|-------------------------------------------------------------------|-----|

| 2.0 Pin Description and Configuration                             | 6   |

| 3.0 Functional Description                                        |     |

| 4.0 Register Descriptions                                         |     |

| 5.0 Operational Characteristics                                   | 87  |

| 6.0 Electrical Characteristics                                    | 88  |

| 7.0 Timing Diagrams                                               |     |

| 8.0 Reset Circuit                                                 | 100 |

| 9.0 Selection of Isolation Transformer                            | 101 |

| 10.0 Package Outline                                              | 102 |

| Appendix A: Data Sheet Revision History<br>The Microchip Web Site | 104 |

| The Microchip Web Site                                            | 105 |

| Customer Change Notification Service                              | 105 |

| Customer Support                                                  | 105 |

| Product Identification System                                     | 106 |

### 1.0 INTRODUCTION

### 1.1 General Description

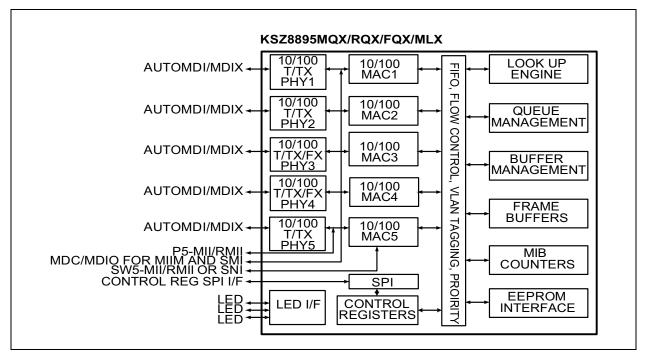

The KSZ8895MQX/RQX/FQX/MLX is a highly-integrated, Layer 2 managed, five-port switch with numerous features designed to reduce system cost. Intended for cost-sensitive 10/100Mbps five-port switch systems with low power consumption, on-chip termination, and internal core power controllers, it supports high-performance memory bandwidth and shared memory-based switch fabric with non-blocking configuration. Its extensive feature set includes power management, programmable rate limit and priority ratio, tag/port-based VLAN, packets filtering, four-queue QoS prioritization, management interfaces, and MIB counters. The KSZ8895 family provides multiple CPU data interfaces to effectively address both current and emerging fast Ethernet applications when Port 5 is configured to separate MAC5 with SW5-MII/RMII and PHY5 with P5-MII/RMII interfaces.

The KSZ8895 family offers three configurations, providing the flexibility to meet different requirements:

- KSZ8895MQX/MLX: Five 10/100Base-T/TX transceivers, One SW5-MII, and One P5-MII interface

- KSZ8895RQX: Five 10/100Base-T/TX transceivers, One SW5-RMII, and One P5-RMII interface

- KSZ8895FQX: Four 10/100Base-T/TX transceivers on Ports 1, 2, 3, and 5 (port 3 can be set to fiber mode). One 100Base-FX transceiver on Port 4. One SW5-MII and One P5-MII interface

All registers of MACs and PHYs units can be managed by the SPI or the SMI interface. MIIM registers can be accessed through the MDC/MDIO interface. EEPROM can set all control registers for the unmanaged mode.

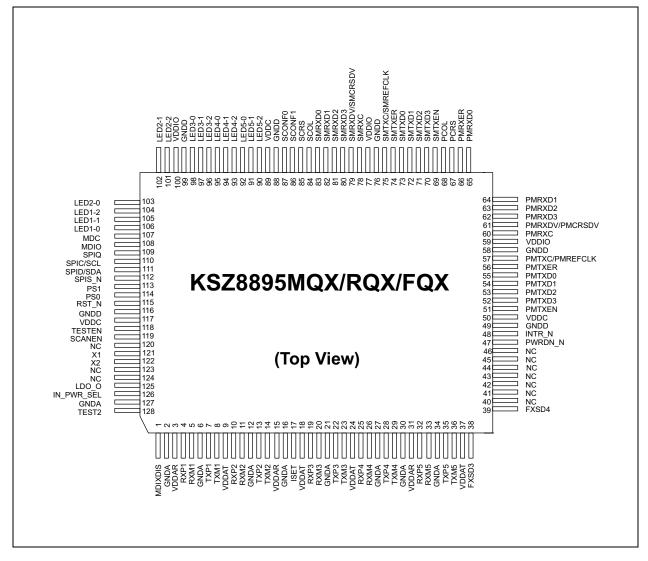

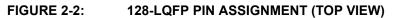

KSZ8895MQX/RQX/FQX are available in the 128-pin PQFP package. KSZ8895MLX is available as a 128-pin LQFP package.

### FIGURE 1-1: FUNCTIONAL DIAGRAM

### 2.0 PIN DESCRIPTION AND CONFIGURATION

### TABLE 2-1: SIGNALS - KSZ8895MQX/RQX/FQX/MLX

| Pin<br>Number | Pin<br>Name | Type,<br>Note<br>2-1 | Port  | Pin Function, Note 2-2                                                                                   |

|---------------|-------------|----------------------|-------|----------------------------------------------------------------------------------------------------------|

| 1             | MDI-XDIS    | IPD                  | 1 - 5 | Disable auto MDI/MDI-X.<br>PD (default) = normal operation.<br>PU = disable auto MDI/MDI-X on all ports. |

| 2             | GNDA        | GND                  | _     | Analog ground.                                                                                           |

© 2016 Microchip Technology Inc.

| Pin<br>Number | Pin<br>Name | Type,<br>Note<br>2-1 | Port | Pin Function, Note 2-2                                                             |  |

|---------------|-------------|----------------------|------|------------------------------------------------------------------------------------|--|

| 3             | VDDAR       | Р                    |      | 1.2V analog V <sub>DD</sub> .                                                      |  |

| 4             | RXP1        | I                    | 1    | Physical receive signal + (differential).                                          |  |

| 5             | RXM1        | I                    | 1    | Physical receive signal - (differential).                                          |  |

| 6             | GNDA        | GND                  |      | Analog ground.                                                                     |  |

| 7             | TXP1        | 0                    | 1    | Physical transmit signal + (differential).                                         |  |

| 8             | TXM1        | 0                    | 1    | Physical transmit signal - (differential).                                         |  |

| 9             | VDDAT       | Р                    |      | 3.3V analog V <sub>DD</sub> .                                                      |  |

| 10            | RXP2        | I                    | 2    | Physical receive signal + (differential).                                          |  |

| 11            | RXM2        | I                    | 2    | Physical receive signal - (differential).                                          |  |

| 12            | GNDA        | GND                  |      | Analog ground.                                                                     |  |

| 13            | TXP2        | 0                    | 2    | Physical transmit signal + (differential).                                         |  |

| 14            | TXM2        | 0                    | 2    | Physical transmit signal - (differential).                                         |  |

| 15            | VDDAR       | Р                    | _    | 1.2V analog V <sub>DD</sub> .                                                      |  |

| 16            | GNDA        | GND                  | _    | Analog ground.                                                                     |  |

| 17            | ISET        | _                    | _    | Set physical transmit output current. Pull-down with a 12.4 $k\Omega$ 1% resistor. |  |

| 18            | VDDAT       | Р                    | _    | 3.3V analog V <sub>DD</sub> .                                                      |  |

| 19            | RXP3        | I                    | 3    | Physical receive signal + (differential).                                          |  |

| 20            | RXM3        | I                    | 3    | Physical receive signal - (differential).                                          |  |

| 21            | GNDA        | GND                  | _    | Analog ground.                                                                     |  |

| 22            | TXP3        | 0                    | 3    | Physical transmit signal + (differential).                                         |  |

| 23            | TXM3        | 0                    | 3    | Physical transmit signal - (differential).                                         |  |

| 24            | VDDAT       | Р                    | _    | 3.3V analog V <sub>DD</sub> .                                                      |  |

| 25            | RXP4        | I                    | 4    | Physical receive signal + (differential).                                          |  |

| 26            | RXM4        | I                    | 4    | Physical receive signal - (differential).                                          |  |

| 27            | GNDA        | GND                  |      | Analog ground.                                                                     |  |

| 28            | TXP4        | 0                    | 4    | Physical transmit signal + (differential).                                         |  |

| 29            | TXM4        | 0                    | 4    | Physical transmit signal - (differential).                                         |  |

| 30            | GNDA        | GND                  |      | Analog ground.                                                                     |  |

| 31            | VDDAR       | Р                    |      | 1.2V analog V <sub>DD</sub> .                                                      |  |

| 32            | RXP5        | I                    | 5    | Physical receive signal + (differential).                                          |  |

### TABLE 2-1: SIGNALS - KSZ8895MQX/RQX/FQX/MLX (CONTINUED)

| Pin<br>Number | Pin<br>Name        | Type,<br>Note<br>2-1 | Port | Pin Function, Note 2-2                                                                                                                                                                                                                          |  |

|---------------|--------------------|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 33            | RXM5               | I                    | 5    | Physical receive signal - (differential).                                                                                                                                                                                                       |  |

| 34            | GNDA               | GND                  |      | Analog ground.                                                                                                                                                                                                                                  |  |

| 35            | TXP5               | 0                    | 5    | Physical transmit signal + (differential).                                                                                                                                                                                                      |  |

| 36            | TXM5               | 0                    | 5    | Physical transmit signal - (differential).                                                                                                                                                                                                      |  |

| 37            | VDDAT              | Р                    | _    | 3.3V analog V <sub>DD</sub> .                                                                                                                                                                                                                   |  |

| 38            | NC/FXSD3           | IPD                  | 3    | FQX: This pin can be floating when port 3 is used as copper port<br>(default). Port 3 can be set to fiber mode by Register 239 bit [7], this<br>pin is used for fiber signal detect pin on Port 3 in Fiber mode.<br>MQX/RQX/MLX: no connection. |  |

| 39            | FXSD4              | IPD                  | 4    | FQX: Fiber signal detect pin for Port 4.<br>MQX/RQX/MLX: no connection.                                                                                                                                                                         |  |

| 40            | NC                 | NC                   | —    | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 41            | NC                 | NC                   | _    | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 42            | NC                 | NC                   |      | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 43            | NC                 | NC                   |      | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 44            | NC                 | NC                   | _    | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 45            | NC                 | NC                   | _    | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 46            | NC                 | NC                   | _    | No connection. Leave NC pin floating.                                                                                                                                                                                                           |  |

| 47            | PWRDN_N            | IPU                  | —    | Full-chip power down. Active low.                                                                                                                                                                                                               |  |

| 48            | INTR_N             | OPU                  | —    | Interrupt. This pin is Open-Drain output pin.                                                                                                                                                                                                   |  |

| 49            | GNDD               | GND                  | —    | Digital ground.                                                                                                                                                                                                                                 |  |

| 50            | VDDC               | Р                    | —    | 1.2V digital core V <sub>DD</sub> .                                                                                                                                                                                                             |  |

| 51            | PMTXEN             | IPD                  | 5    | PHY [5] MII/RMII transmit enable.                                                                                                                                                                                                               |  |

| 52            | PMTXD3             | IPD                  | 5    | MQX/FQX/MLX: PHY [5] MII transmit bit 3.<br>RQX: no connection for RMII.                                                                                                                                                                        |  |

| 53            | PMTXD2             | IPD                  | 5    | MQX/FQX/MLX: PHY [5] MII transmit bit 2.<br>RQX: no connection for RMII.                                                                                                                                                                        |  |

| 54            | PMTXD1             | IPD                  | 5    | PHY [5] MII/RMII transmit bit 1.                                                                                                                                                                                                                |  |

| 55            | PMTXD0             | IPD                  | 5    | PHY [5] MII/RMII transmit bit 0.                                                                                                                                                                                                                |  |

| 56            | PMTXER             | IPD                  | 5    | MQX/FQX/MLX: PHY [5] MII transmit error.<br>RQX: no connection for RMII.                                                                                                                                                                        |  |

| 57            | PMTXC/<br>PMREFCLK | I/O                  | 5    | MQX/FQX/MLX: Output PHY [5] MII transmit clock<br>RQX: Input PHY [5] RMII reference clock, 50 MHz ±50 ppm, the<br>50 MHz clock comes from PMRXC Pin 60.                                                                                         |  |

| 58            | GNDD               | GND                  |      | Digital ground.                                                                                                                                                                                                                                 |  |

© 2016 Microchip Technology Inc.

| Pin<br>Number | Pin<br>Name        | Type,<br>Note<br>2-1 | Port | Pin Function, Note 2-2                                                                                                                                                                                                                                                                 |  |

|---------------|--------------------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 59            | VDDIO              | Р                    | _    | 3.3V, 2.5V, or 1.8V digital V <sub>DD</sub> for digital I/O circuitry.                                                                                                                                                                                                                 |  |

| 60            | PMRXC              | I/O                  | 5    | MQX/FQX/MLX: Output PHY [5] MII receive clock.<br>RQX: Output PHY [5] RMII reference clock, this clock is used when<br>opposite doesn't provide RMII 50 MHz clock or the system doesn't<br>provide an external 50 MHz clock for the P5-RMII interface.                                 |  |

| 61            | PMRXDV/<br>PMCRSDV | IPD/O                | 5    | MQX/FQX/MLX: PMRXDV is for PHY [5] MII receive data valid.<br>RQX: PMCRSDV is for PHY [5] RMII Carrier Sense/Receive Data<br>Valid Output.                                                                                                                                             |  |

| 62            | PMRXD3             | IPD/O                | 5    | MQX/FQX/MLX: PHY [5] MII receive bit 3.<br>RQX: no connection for RMII.<br>Strap option:<br>PD (default) = enable flow control.<br>PU = disable flow control.                                                                                                                          |  |

| 63            | PMRXD2             | IPD/O                | 5    | MQX/FQX/MLX: PHY [5] MII receive bit 2.<br>RQX: no connection for RMII.<br>Strap option:<br>PD (default) = disable back pressure.<br>PU = enable back pressure.                                                                                                                        |  |

| 64            | PMRXD1             | IPD/O                | 5    | MQX/FQX/MLX: PHY [5] MII receive bit 1.<br>RQX: PHY [5] RMII receive bit 1.<br>Strap option:<br>PD (default) = drop excessive collision packets.<br>PU = does not drop excessive collision packets.                                                                                    |  |

| 65            | PMRXD0             | IPD/O                | 5    | MQX/FQX/MLX: PHY [5] MII receive bit 0.<br>RQX: PHY [5] RMII receive bit 0.<br>Strap option:<br>PD (default) = disable aggressive back-off algorithm in half-duplex<br>mode.<br>PU = enable for performance enhancement.                                                               |  |

| 66            | PMRXER             | IPD/O                | 5    | MQX/FQX/MLX:PHY [5] MII receive error<br>RQX: PHY [5] RMII receive error<br>Strap option:<br>PD (default) = packet size 1518/1522 bytes.<br>PU = 1536 bytes.                                                                                                                           |  |

| 67            | PCRS               | IPD/O                | 5    | MQX/FQX/MLX: PHY [5] MII carrier sense.<br>RQX: no connection for RMII.<br>Strap option for port 4 only.<br>PD (default) = force half-duplex if auto-negotiation is disabled or<br>fails.<br>PU = force full-duplex if auto negotiation is disabled or fails. Refer to<br>Register 76. |  |

| 68            | PCOL               | IPD/O                | 5    | MQX/FQX/MLX: PHY [5] MII collision detect.<br>RQX: no connection.<br>Strap option for port 4 only.<br>PD (default) = no force flow control, normal operation.<br>PU = force flow control. Refer to Register 66.                                                                        |  |

| <b>TABLE 2-1:</b> | SIGNALS - KSZ8895MQX/RQX/FQX/MLX (CONTINUED) |

|-------------------|----------------------------------------------|

|-------------------|----------------------------------------------|

| Pin<br>Number | Pin<br>Name        | Type,<br>Note<br>2-1 | Port | Pin Function, Note 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------|--------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 69            | SMTXEN             | IPD                  | _    | Port 5 Switch MII/RMII transmit enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 70            | SMTXD3             | IPD                  |      | MQX/FQX/MLX: Port 5 Switch MII transmit bit 3.<br>RQX: no connection for RMII.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 71            | SMTXD2             | IPD                  | _    | MQX/FQX/MLX: Port 5 Switch MII transmit bit 2.<br>RQX: no connection for RMII.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 72            | SMTXD1             | IPD                  | _    | Port 5 Switch MII/RMII transmit bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 73            | SMTXD0             | IPD                  | _    | Port 5 Switch MII/RMII transmit bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 74            | SMTXER             | IPD                  | _    | MQX/FQX/MLX: Port 5 Switch MII transmit error<br>RQX: Port 5 Switch RMII transmit error                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 75            | SMTXC/<br>SMREFCLK | I/O                  | _    | MQX/FQX/MLX: Port 5 Switch MII transmit clock,<br>Input: SW5-MII MAC mode, Output: SW5-MII PHY modes.<br>RQX: Input SW5-RMII 50MHz ±50 ppm reference clock. The<br>50 MHz clock comes from SMRXC Pin 78 when the device is the<br>clock mode which the device's clock comes from 25 MHz crystal/<br>oscillator from Pins X1/X2. Or the 50 MHz clock comes from exter-<br>nal 50 MHz clock source when the device is the normal mode which<br>the device's clock source comes from SMTXC pin not from X1/X2<br>pins. |  |

| 76            | GNDD               | GND                  | _    | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 77            | VDDIO              | Р                    | -    | 3.3V, 2.5V, or 1.8V digital $V_{DD}$ for digital I/O circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 78            | SMRXC              | I/O                  |      | MQX/FQX/MLX: Port 5 Switch MII receive clock,<br>Input: SW5-MII MAC mode, Output: SW5-MII PHY mode.<br>RQX: Output SW5-RMII 50 MHz clock, this clock is used when<br>opposite doesn't provide RMII reference clock or the system<br>doesn't provide an external 50 MHz clock for the RMII interface.                                                                                                                                                                                                                |  |

| 79            | SMRXDV/<br>SMCRSDV | IPD/O                | _    | MQX/FQX/MLX: SMRXDV is for Switch MAC5 MII receive data valid.<br>RQX: SMCRSDV is for MAC5 RMII Carrier Sense/Receive Data Valid Output.                                                                                                                                                                                                                                                                                                                                                                            |  |

| 80            | SMRXD3             | IPD/O                | _    | MQX/FQX/MLX: Port 5 Switch MII receive bit 3.<br>RQX: no connection for RMII<br>Strap option:<br>PD (default) = Disable Switch SW5-MII/RMII full-duplex flow control<br>PU = Enable Switch SW5-MII/RMII full-duplex flow control.                                                                                                                                                                                                                                                                                   |  |

| 81            | SMRXD2             | IPD/O                | _    | MQX/FQX/MLX: Port 5 Switch MII receive bit 2.<br>RQX: no connection for RMII<br>Strap option:<br>PD (default) = Switch SW5-MII/RMII in full-duplex mode;<br>PU = Switch SW5-MII/RMII in half-duplex mode.                                                                                                                                                                                                                                                                                                           |  |

| 82            | SMRXD1             | IPD/O                | _    | MQX/FQX/MLX: Port 5 Switch MII receive bit 1.<br>RQX: Port 5 Switch RMII receive bit 1.<br>Strap option:<br>PD (default) = Port 5 Switch SW5-MII/RMII in 100 Mbps mode.<br>PU = Switch SW5-MII/RMII in 10 Mbps mode.                                                                                                                                                                                                                                                                                                |  |

| Pin<br>Number | Pin<br>Name | Type,<br>Note<br>2-1 | Port |                                                                                                                                      | Pin Function, Note 2-2 |                  |

|---------------|-------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|

| 83            | SMRXD0      | IPD/O                |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                 |                        |                  |

|               |             |                      |      | —                                                                                                                                    | Mode 0                 | Mode 1           |

|               |             |                      |      | LEDx_2                                                                                                                               | Link/Activity          | 100Link/Activity |

|               |             |                      |      |                                                                                                                                      | LEDx_1                 | Full-Duplex/Col  |

|               |             |                      |      | LEDx_0                                                                                                                               | Speed                  | Full-Duplex      |

| 84            | SCOL        | IPD/O                | _    | MQX/FQX/MLX: Port switch MII collision detect,<br>Input: SW5-MII MAC modes, Output: SW5-MII PHY modes<br>RQX: no connection for RMII |                        |                  |

| 85            | SCRS        | IPD/O                |      | MQX/FQX/MLX: Port switch MII collision detect,<br>Input: SW5-MII MAC modes, Output: SW5-MII PHY modes<br>RQX: no connection for RMII |                        |                  |

| <b>TABLE 2-1</b> : | SIGNALS - KSZ8895MQX/RQX/FQX/MLX (CONTINUED) |

|--------------------|----------------------------------------------|

|--------------------|----------------------------------------------|

| Pin<br>Number | Pin<br>Name | Type,<br>Note<br>2-1 | Port                | Pin Function, Note 2-2                                                                                                                                      |                                               |                            |

|---------------|-------------|----------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------|

|               |             |                      | 5 MAC5 MII/RMII and | re dual MII/RMII configur<br>I PHY [5] MII/RMII. SW5<br>modes. P5-MII supports<br>ow:                                                                       | -MII supports both                            |                            |

|               |             |                      |                     | Pin# (91, 86, 87)                                                                                                                                           | Port 5 Switch<br>MAC5 SW5- MII/<br>RMII       | Port5 PHY5<br>P5- MII/RMII |

|               |             |                      |                     | 000                                                                                                                                                         | Disable, Otri                                 | Disable, Otri              |

|               |             |                      |                     | 001                                                                                                                                                         | PHY Mode MII, or<br>RMII                      | Disable, Otri              |

| 86            | SCONF1      | IPD                  | _                   | 010                                                                                                                                                         | MAC Mode MII, or<br>RMII                      | Disable, Otri              |

|               |             |                      |                     | 011                                                                                                                                                         | PHY Mode SNI                                  | Disable, Otri              |

|               |             |                      | 100                 | Disable (default)                                                                                                                                           | Disable (default)                             |                            |

|               |             |                      | 101                 | PHY Mode MII or<br>RMII                                                                                                                                     | P5-MII/RMII                                   |                            |

|               |             |                      |                     | 110                                                                                                                                                         | MAC Mode MII or<br>RMII                       | P5-MII/RMII                |

|               |             |                      |                     | 111                                                                                                                                                         | PHY Mode SNI                                  | P5-MII/RMII                |

| 87            | SCONF0      | IPD                  | _                   | Dual MII/RMII configu                                                                                                                                       | iration pin. See Pin 86 de                    | escriptions.               |

| 88            | GNDD        | GND                  | _                   | Digital ground.                                                                                                                                             |                                               |                            |

| 89            | VDDC        | Р                    | _                   | 1.2V digital core V <sub>DD</sub> .                                                                                                                         |                                               |                            |

| 90            | LED5-2      | IPU/O                | 5                   | LED indicator 2.<br>Strap option:<br>Aging setup. See "Agi<br>PU (default) = aging e<br>PD = aging disable.                                                 |                                               |                            |

| 91            | LED5-1      | IPU/O                | 5                   | LED indicator 1.<br>Strap option:<br>PU (default): enable F<br>PD: tri-state all PHY [                                                                      | PHY [5] MII I/F.<br>5] MII output. See "Pin 8 | 6 SCONF1."                 |

| 92            | LED5-0      | IPU/O                | 5                   | LED indicator 0.<br>Strap option for port 4 only.<br>PU (default) = Enable auto-negotiation.<br>PD = Disable auto-negotiation. Strap to Register76 bit [7]. |                                               |                            |

| 93            | LED4-2      | IPU/O                | 4                   | LED indicator 2                                                                                                                                             |                                               |                            |

| 94            | LED4-1      | IPU/O                | 4                   | LED indicator 1                                                                                                                                             |                                               |                            |

| Pin<br>Number | Pin<br>Name | Type,<br>Note<br>2-1 | Port | Pin Function, Note 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------------|-------------|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 95            | LED4-0      | IPU/O                | 4    | LED indicator 0.<br>Strap option:<br>PU (default) = Normal mode.<br>PD = Energy Detection mode (EDPD mode)<br>Strap to Register 14 bits [4:3]                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 96            | LED3-2      | IPU/O                | 3    | LED indicator 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 97            | LED3-1      | IPU/O                | 3    | LED indicator 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 98            | LED3-0      | IPU/O                | 3    | LED indicator 0.<br>Strap option:<br>PU (default) = Select I/O drive strength (8 mA);<br>PD = Select I/O drive strength (12 mA).<br>Strap to Register132 bit [7-6].                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 99            | GNDD        | GND                  | —    | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 100           | VDDIO       | Р                    | _    | 3.3V, 2.5V, or 1.8V digital $V_{\text{DD}}$ for digital I/O circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 101           | LED2-2      | IPU/O                | 2    | LED indicator 2.<br>Strap option for RQX only:<br>PU (default) = Select the device as clock mode in SW5- RMII,<br>25MHz crystal/oscillator to X1/X2 pins of the device and pins of<br>SMRXC and PMRXC output 50 MHz clock.<br>PD = Select the device as normal mode in SW5-RMII. Switch<br>MAC5 used only. The input clock from X1/X2 pins is not used, the<br>device's clock source comes from SMTXC/SMREFCLK pin which<br>the 50 MHz reference clock comes from external 50 MHz clock<br>source, PMRXC can output 50 MHz clock for P5-RMII interface in<br>the normal mode. |  |

| 102           | LED2-1      | IPU/O                | 2    | LED indicator 1.<br>Strap option: for Port 3 only.<br>PU (default) = Enable auto-negotiation.<br>PD = Disable auto-negotiation. Strap to Register60 bit [7].                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 103           | LED2-0      | IPU/O                | 2    | LED indicator 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 104           | LED1-2      | IPU/O                | 1    | LED indicator 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 105           | LED1-1      | IPU/O                | 1    | LED indicator 1.<br>Strap option: for port 3 only.<br>PU (default) = no force flow control, normal operation.<br>PD = force flow control. Strap to Register60 bit [4].                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 106           | LED1-0      | IPU/O                | 1    | LED indicator 0.<br>Strap option for port 3 only.<br>PU (default) = force half-duplex if auto-negotiation is disabled or<br>fails.<br>PD = force full-duplex if auto negotiation is disabled or fails.<br>Strap to Register60 bit [5].                                                                                                                                                                                                                                                                                                                                        |  |

| 107           | MDC         | IPU                  | All  | PHYs MII management (MIIM registers) data clock. Or SMI inter-<br>face clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| <b>TABLE 2-1</b> : | SIGNALS - KSZ8895MQX/RQX/FQX/MLX (CONTINUED) |

|--------------------|----------------------------------------------|

|--------------------|----------------------------------------------|

| Pin<br>Number | Pin<br>Name | Type,<br>Note<br>2-1 | Port | Pin Function, Note 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

|---------------|-------------|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 108           | MDIO        | IPU/O                | All  | PHYs MII management (MIIM registers) data I/O. Or SMI interface<br>data I/O<br>Note: Need an external pull-up when driven.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                       |

| 109           | SPIQ        | IPU/O                | All  | SPI serial data output in SPI slave<br>Note: Need an external pull-up w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |

| 110           | SPIC/SCL    | IPU/O                | All  | <ul> <li>(1) Input clock up to 25 MHz in SF</li> <li>(2) Output clock at 61 kHz in I<sup>2</sup>C in Note: Need an external pull-up whether the set of the</li></ul> | master mode. See "Pin 113."                                           |

| 111           | SSPID/SDA   | IPU/O                | All  | <ul> <li>(1) Serial data input in SPI slave r</li> <li>(2) Serial data input/output in I<sup>2</sup>C</li> <li>Note: Need an external pull-up whether the state of the stat</li></ul>    | master mode. See "Pin 113."                                           |

| 112           | SPIS_N      | IPU                  | All  | Active low.<br>(1) SPI data transfer start in SPI slave mode. When SPIS_N is high,<br>the KSZ8895MQX/RQX/FQX/MLX is deselected and SPIQ is held<br>in high impedance state, a high-to-low transition to initiate the SPI<br>data transfer.<br>(2) not used in I <sup>2</sup> C master mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                       |

|               |             | IPD                  |      | Serial bus configuration pin.<br>For this case, if the EEPROM is n<br>RQX/FQX/MLX will start itself with<br>values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | not present, the KSZ8895MQX/<br>In the PS [1:0] = 00 default register |

|               |             |                      | _    | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Serial Bus Configuration                                              |

| 113           | PS1         |                      |      | PS[1:0] = 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I <sup>2</sup> C Master Mode for EEPROM                               |

|               |             |                      |      | PS[1:0] = 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SMI Interface Mode                                                    |