Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## IO-Link communication master transceiver IC

Datasheet - production data

#### **Features**

- Supply voltage from 18 V to 32.5 V

- Programmable output stages: high-side, low-side or push-pull ( $< 2 \Omega$ )

- Up to 500 mA L+ protected high-side driver

- COM1, COM2 and COM3 mode supported

- Additional IEC61131-2 type 1 input

- Short-circuit and overcurrent output protection through current limitation and programmable cut-off current

- 3.3 V / 5 V, 50 mA linear regulator

- 5 mA IO-Link digital input

- Fast mode I<sup>2</sup>C for IC control, configuration and diagnostic

- Diagnostic dual LED sequence generator and driver

- 5 V and 3.3 V compatible I/Os

- Overvoltage protection (> 36 V)

- Overtemperature protection

- ESD protection

- Miniaturized VFQFPN 26L (3.5x5x1 mm) package

## **Applications**

- Industrial sensors

- Factory automation

Process control

## Description

The L6360 is a monolithic IO-Link master port compliant with PHY2 (3-wire) supporting COM1 (4.8 kbaud), COM2 (38.4 kbaud) and COM3 (230.4 kbaud) modes. The C/Qo output stage is programmable: high-side, low-side or push-pull; also cut-off current, cut-off current delay time. and restart delay are programmable. Cut-off current and cut-off current delay time, combined with thermal shutdown and automatic restart. protect the device against overload and shortcircuit. C/Qo and L+ output stages are able to drive resistive, inductive and capacitive loads. Inductive loads up to 10 mJ can be driven. Supply voltage is monitored and low voltage conditions are detected. The L6360 transfers, through the PHY2(C/Qo pin), data received from a host microcontroller through the USART (IN C/Qo pin), or to the USART (OUT C/Q<sub>I</sub> pin) data received from PHY2 (C/Q<sub>I</sub> pin). To enable full IC control, configuration and monitoring (i.e. fault conditions stored in the status register), the communication between the system microcontroller and the L6360 is based on a fast mode 2-wire I<sup>2</sup>C. The L6360 has nine registers to manage the programmable parameters and the status of the IC. Monitored fault conditions are: L+ line, overtemperature, C/Q overload, linear regulator undervoltage, and parity check. Internal LED driver circuitries, in open drain configuration, provide two programmable sequences to drive two LEDs.

Contents L6360

| Co | nte  | nts |

|----|------|-----|

| CU | HILE | H   |

| 1    | Block di               | iagram                                 | 6  |

|------|------------------------|----------------------------------------|----|

| 2    | Pin desc               | cription                               | 7  |

| 3    | Absolut                | e maximum ratings                      | 9  |

| 4    |                        | nended operating conditions            |    |

| 5    |                        | al characteristics                     |    |

| 6    |                        | configuration                          |    |

|      | 6.1                    | Introduction                           |    |

|      | 6.2                    | Main features                          |    |

|      | 6.3                    | General description                    | 18 |

|      | 6.4                    | SDA/SCL line control                   |    |

|      | 6.5                    | Mode selection                         | 18 |

|      | 6.6                    | Functional description                 | 20 |

|      | 6.7                    | Communication flow                     | 20 |

|      | 6.8                    | I <sup>2</sup> C address               | 21 |

|      | 6.9                    | Internal register                      | 21 |

|      | 6.10                   | Start-up default configuration         | 31 |

|      | 6.11                   | Interrupt                              | 33 |

|      | 6.12                   | Demagnetization                        | 33 |

|      |                        | 6.12.1 Fast demagnetization            |    |

|      |                        | 6.12.2 Slow demagnetization            |    |

| 7    | I <sup>2</sup> C proto | ocol                                   |    |

|      | 7.1                    | Protocol configuration                 |    |

|      | 7.2                    | Operating modes                        | 37 |

| 8    | Physica                | I layer communication                  | 47 |

|      | 8.1                    | Transceiver                            | 47 |

|      | 8.2                    | IEC 61131-2 type 1 digital inputs      | 48 |

| 9    | Diagnos                | stic LED sequence generator and driver | 49 |

| 10   | Line reg               | julator                                | 50 |

| 11   | Applicat               | tion example                           | 51 |

| 12   | EMC pro                | otection considerations                | 52 |

|      | 12.1                   | Supply voltage protection              |    |

|      | 12.2                   | I/O line protection                    |    |

| 2/60 |                        | DocID022817 Rev 5                      |    |

| L6360 | Contents |

|-------|----------|

| L0300 | Contents |

| 13 | Ordering | g information                               | 56 |

|----|----------|---------------------------------------------|----|

| 14 | Package  | information                                 | 57 |

|    | 14.1     | VFQFPN 26L (3.5x5x1 mm) package information | 57 |

|    | 14.2     | Packing information                         | 58 |

| 15 | Revision | n history                                   | 59 |

List of tables L6360

# List of tables

| Table 1: Pin description                                                        | 7  |

|---------------------------------------------------------------------------------|----|

| Table 2: Absolute maximum ratings                                               | 9  |

| Table 3: Recommended operating conditions                                       | 10 |

| Table 4: Thermal data                                                           | 10 |

| Table 5: Supply                                                                 |    |

| Table 6: Electrical characteristics - linear regulator                          | 14 |

| Table 7: Electrical characteristics - logic inputs and outputs                  | 14 |

| Table 8: Electrical characteristics - LED driving                               |    |

| Table 9: Electrical characteristics - I <sup>2</sup> C (fast mode)              | 15 |

| Table 10: Main parameter typical variations vs. +/- 1% variation of Rbias value | 16 |

| Table 11: Register addresses                                                    | 21 |

| Table 12: ENcgo: C/Q pull-down enable                                           | 24 |

| Table 13: Icoq: C/QO HS and LS cut-off current                                  | 24 |

| Table 14: tdcoq: C/QO HS and LS cut-off current delay time                      | 25 |

| Table 15: trcoq: C/QO restart delay time                                        |    |

| Table 16: t <sub>dbq</sub> : C/QI debounce time                                 |    |

| Table 17: ENcal: I/Q pull-down enable                                           | 26 |

| Table 18: CQ <sub>PDG</sub> : C/Q pull-down generator switching                 |    |

| Table 19: L+cod: L+ cut-off disable                                             |    |

| Table 20: t <sub>DCOL</sub> : L+ HS cut-off current delay time                  |    |

| Table 21: trcol: L+ restart delay                                               | 27 |

| Table 22: Bit 1:0 = t <sub>dbi</sub> [1:0]: I/Q debounce time                   | 27 |

| Table 23: C/Q output stage configuration                                        |    |

| Table 24: Parameter default configuration                                       |    |

| Table 25: Register default configuration                                        |    |

| Table 26: Current write mode direction bit                                      |    |

| Table 27: Sequential write mode direction bit                                   |    |

| Table 28: Read mode: register address                                           |    |

| Table 29: Address register                                                      |    |

| Table 30: Linear regulator selection pin                                        |    |

| Table 31: Supply voltage protection component description                       |    |

| Table 32: Refined supply voltage protection component description               |    |

| Table 33: V <sub>H</sub> protection component description                       |    |

| Table 34: Typical protection in IO-Link application component description       |    |

| Table 35: IO-Link and SIO application extended protection component description |    |

| Table 36: Ordering information                                                  | 56 |

| Table 37: VFQFPN 26L (3.5x5x1.0 mm) package mechanical data                     |    |

| Table 38: Document revision history                                             | 59 |

L6360 List of figures

# **List of figures**

| Figure 1: Block diagram                                                                            |     |

|----------------------------------------------------------------------------------------------------|-----|

| Figure 2: Pin connection (top through view)                                                        |     |

| Figure 3: Rise/fall time test setup                                                                |     |

| Figure 4: Normalized rise and fall time vs. output capacitor value (typ. values in push-pull confi | •   |

| Figure 5: A master transmitter addressing a slave receiver with a 7-bit address (the transfer is   | not |

| changed)                                                                                           | 19  |

| Figure 6: A master reads data from the slave immediately after the first byte                      | 19  |

| Figure 7: Transfer sequencing                                                                      |     |

| Figure 8: I <sup>2</sup> C communication                                                           | 20  |

| Figure 9: Status register                                                                          |     |

| Figure 10: Power-on bit behavior                                                                   | 22  |

| Figure 11: Overtemperature (OVT) bit behavior                                                      | 23  |

| Figure 12: Cut-off behavior                                                                        |     |

| Figure 13: Control register 1                                                                      |     |

| Figure 14: Control register 2                                                                      | 26  |

| Figure 15: Configuration register                                                                  | 27  |

| Figure 16: LED1 registers                                                                          | 30  |

| Figure 17: LED2 registers                                                                          | 30  |

| Figure 18: Parity register                                                                         |     |

| Figure 19: Power stage, Q2 is not present on L+ output                                             |     |

| Figure 20: Fast demagnetization principle schematic. Load connected to L                           |     |

| Figure 21: Fast demagnetization waveform. Load connected to L                                      | 35  |

| Figure 22: Slow demagnetization block. Load connected to L                                         | 35  |

| Figure 23: Slow demagnetization waveform. Load connected to GND                                    | 36  |

| Figure 24: Device initialization                                                                   |     |

| Figure 25: Current write mode flow chart procedure                                                 | 38  |

| Figure 26: Current write mode frames                                                               |     |

| Figure 27: Sequential write mode flow chart procedure                                              | 40  |

| Figure 28: Sequential write mode frames                                                            |     |

| Figure 29: Microcontroller parity check calculus                                                   |     |

| Figure 30: Register sequence in sequential write mode                                              | 42  |

| Figure 31: Current read mode flow chart procedure                                                  |     |

| Figure 32: Current read mode frames                                                                |     |

| Figure 33: Current read communication flow                                                         |     |

| Figure 34: Sequential/random read mode                                                             | 44  |

| Figure 35: Sequential/random read communication flow                                               |     |

| Figure 36: Block diagram communication mode                                                        |     |

| Figure 37: System communication mode                                                               |     |

| Figure 38: C/Q or L+ channel cut-off protection                                                    | 48  |

| Figure 39: C/Q or L+ channel current limitation and cut-off protection with latched restart        |     |

| Figure 40: LED drivers                                                                             |     |

| Figure 41: Linear regulator                                                                        |     |

| Figure 42: Linear regulator principle schematic                                                    |     |

| Figure 43: Application example                                                                     |     |

| Figure 44: Supply voltage protection with uni-directional Transil                                  |     |

| Figure 45: Refined supply voltage protection                                                       |     |

| Figure 46: V <sub>H</sub> protection vs. V <sub>CC</sub>                                           |     |

| Figure 47: Typical protection in IO-Link applications                                              |     |

| Figure 48: IO-Link and SIO application extended protection                                         |     |

| Figure 49: VFQFPN 26L (3.5x5x1.0 mm) package outline                                               |     |

| Figure 50: VFQFPN 26L (3.5x5x1.0 mm) carrier tape outline                                          | 58  |

|                                                                                                    |     |

Block diagram L6360

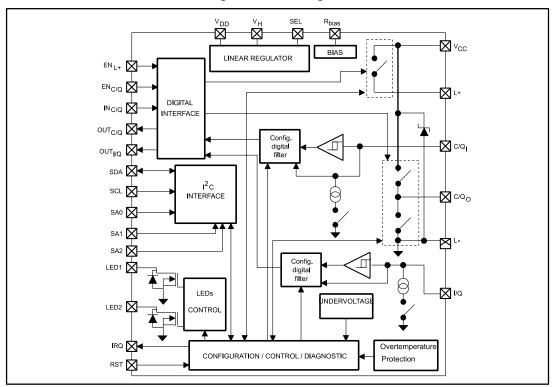

# 1 Block diagram

Figure 1: Block diagram

L6360 Pin description

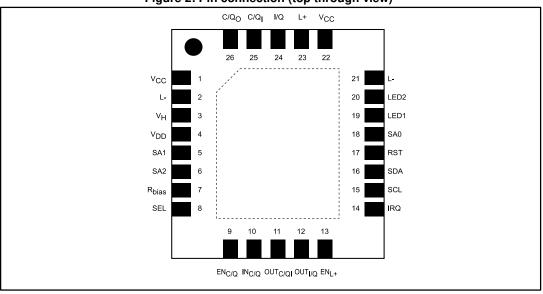

# 2 Pin description

Figure 2: Pin connection (top through view)

Table 1: Pin description

| Number | Name                | Function                                                                                  | Туре         |

|--------|---------------------|-------------------------------------------------------------------------------------------|--------------|

| 1      | Vcc                 | IC power supply                                                                           | Supply       |

| 2      | L-                  | L- line (IC ground)                                                                       | Supply       |

| 3      | V <sub>H</sub>      | Linear regulator supply voltage                                                           | Supply       |

| 4      | $V_{DD}$            | Linear regulator output voltage                                                           | Output       |

| 5      | SA1                 | Serial address 1                                                                          | Input        |

| 6      | SA2                 | Serial address 2                                                                          | Input        |

| 7      | R <sub>bias</sub>   | External resistor for internal reference generation                                       | Input        |

| 8      | SEL                 | Linear regulator 3.3 V/5 V voltage selection. Output is 5 V when SEL pin is pulled to GND | Input        |

| 9      | EN <sub>C/Q</sub>   | C/Q output enable                                                                         | Input        |

| 10     | IN <sub>C/Q</sub>   | C/Q channel logic input                                                                   | Input        |

| 11     | OUTH <sub>C/Q</sub> | C/Q channel logic output                                                                  | Output       |

| 12     | OUTH <sub>I/Q</sub> | I/Q channel logic output                                                                  | Output       |

| 13     | EN <sub>L+</sub>    | L+ switch enable. When EN <sub>L+</sub> is high the switch is closed                      | Input        |

| 14     | IRQ                 | Interrupt request signal (open drain)                                                     | Output       |

| 15     | SCL                 | Serial clock line                                                                         | Input        |

| 16     | SDA                 | Serial data line                                                                          | Input/output |

| 17     | RST                 | Reset - active low                                                                        | Input        |

| 18     | SA0                 | Serial address 0                                                                          | Input        |

| 19     | LED1                | Status/diagnostic LED (open drain)                                                        | Output       |

| 20     | LED2                | Status/diagnostic LED (open drain)                                                        | Output       |

Pin description L6360

| Number | Name             | Function                       | Туре   |

|--------|------------------|--------------------------------|--------|

| 21     | L-               | L- line (IC ground)            | Supply |

| 22     | Vcc              | IC power supply                | Supply |

| 23     | L+               | L+ line                        | Supply |

| 24     | I/Q              | I/Q channel line               | Input  |

| 25     | C/Q <sub>I</sub> | Transceiver (C/Q channel) line | Input  |

| 26     | C/Q <sub>O</sub> | Transceiver (C/Q channel) line | Output |

# 3 Absolute maximum ratings

Table 2: Absolute maximum ratings

| Symbol                                       | Parameter                                                                        | Value                         | Unit |

|----------------------------------------------|----------------------------------------------------------------------------------|-------------------------------|------|

| Vcc                                          | Supply voltage                                                                   | VCLAMP                        |      |

| V <sub>SEL</sub>                             | Linear regulator selection pin voltage                                           | -0.3 to 4                     |      |

| $V_{DD}$                                     | Linear regulator output voltage                                                  | 5.5                           |      |

| VH                                           | Linear regulator input voltage                                                   | Vcc                           |      |

| V <sub>SDA</sub> , SCL, SA0, 1, 2            | I <sup>2</sup> C voltage                                                         | -0.3 to V <sub>DD</sub> + 0.3 |      |

| V <sub>LED1,2</sub>                          | LED1,2 voltage                                                                   | $-0.3$ to $V_{DD} + 0.3$      | V    |

| $V_{C/QI},V_{I/Q}$                           | C/Q <sub>I</sub> , I/Q voltage                                                   | -0.3 to $V_{\text{CC}}$ + 0.3 |      |

| V <sub>RST</sub>                             | Reset voltage                                                                    | $-0.3$ to $V_{DD} + 0.3$      |      |

| $V_{IRQ}$                                    | IRQ voltage                                                                      | $-0.3$ to $V_{DD} + 0.3$      |      |

| V <sub>Rbias</sub>                           | External precision resistance voltage                                            | -03 to 4                      |      |

| V <sub>ESD</sub>                             | Electrostatic discharge (human body model)                                       | 2000                          |      |

| ICLAMP                                       | Current through $V_{\text{CLAMP}}$ in surge test (1 kV, 500 $\Omega$ ) condition | 2                             | Α    |

| Ic/Qo, I <sub>L+</sub>                       | C/Qo, L+ current (continuous)                                                    | Internally limited            | Α    |

| IOUT <sub>C/Q</sub> ,<br>IOUT <sub>I/Q</sub> | OUT <sub>C/Q</sub> , OUT <sub>I/Q</sub> output current                           | ±5                            | mA   |

| I <sub>SDA</sub>                             | I <sup>2</sup> C transmission data current (open drain pin)                      | 10                            | mA   |

| I <sub>RQ</sub>                              | Interrupt request signal current                                                 | 2 <sup>(1)</sup>              | Α    |

| I <sub>LED1,2</sub>                          | LED1, 2 current                                                                  | 10                            | mA   |

| Eload                                        | L+ demagnetization energy                                                        | 10                            | mJ   |

| Ртот                                         | Power dissipation at T <sub>C</sub> = 25 °C                                      | Internally limited            | W    |

| P <sub>LR</sub>                              | Linear regulator power dissipation                                               | 200                           | mW   |

| TJ                                           | Junction operating temperature                                                   | Internally limited            | °C   |

| T <sub>STG</sub>                             | Storage temperature range                                                        | -55 to 150                    | C    |

#### Notes:

<sup>&</sup>lt;sup>(1)</sup>Peak value during fast transient test only.

# 4 Recommended operating conditions

Table 3: Recommended operating conditions

| Symbol            | Parameter                      | Min.  | Тур. | Max. | Unit |

|-------------------|--------------------------------|-------|------|------|------|

| Vcc               | Supply voltage                 | 18    |      | 32.5 | ٧    |

| V <sub>H</sub>    | Linear regulator input voltage | 7     |      | Vcc  | ٧    |

| fscL              | SCL clock frequency            |       |      | 400  | kHz  |

| R <sub>bias</sub> | Precision resistance           | -0.1% | 124  | 0.1% | kΩ   |

| TJ                | Junction temperature           | 40    |      | 125  | °C   |

Table 4: Thermal data

| Symbol                | Parameter                                  | Тур. | Unit |

|-----------------------|--------------------------------------------|------|------|

| R <sub>thj-case</sub> | Thermal resistance, junction-to-case       | 6    | °C/W |

| R <sub>thj-amb</sub>  | Thermal resistance, junction-to-ambient(1) | 50   | °C/W |

#### Notes:

<sup>&</sup>lt;sup>(1)</sup>Mounted on FR4 PCB with 2 signal Cu layers and 2 power Cu layers interconnected through vias.

# 5 Electrical characteristics

(18 V <  $V_{CC}$  < 30 V; -25 °C <  $T_{J}$  < 125 °C;  $V_{DD}$  = 5 V; unless otherwise specified).

Table 5: Supply

| Symbol                | Parameter                                                 | Test conditions | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------------------------------------------------|-----------------|------|------|------|------|

| VCLAMP                | Voltage clamp                                             | I = 5 mA        | 36   |      |      | V    |

| Vuv                   | Undervoltage on threshold                                 |                 | 16   | 17   | 18   | V    |

| V <sub>UVH</sub>      | Undervoltage hysteresis                                   |                 | 0.3  | 1    |      | V    |

| V <sub>REGLN5H</sub>  | Linear regulator<br>undervoltage<br>high threshold        | SEL = L         | 4.3  |      | 4.7  |      |

| V <sub>REGLN5L</sub>  | Linear regulator<br>undervoltage<br>low threshold         | SEL = L         | 3.6  |      | 4.2  | V    |

| V <sub>REG5HYS</sub>  | Linear regulator<br>undervoltage<br>hysteresis            | SEL = L         | 0.1  |      |      | V    |

| V <sub>REGLN33H</sub> | Linear regulator<br>undervoltage<br>high threshold        | SEL = H         | 2.8  |      | 3.1  |      |

| VREGLN33L             | Linear regulator<br>undervoltage<br>low threshold         | SEL = H         | 2.5  |      | 2.7  | V    |

| V <sub>REG33HYS</sub> | Linear regulator<br>undervoltage<br>hysteresis            | SEL = H         | 0.1  |      |      | V    |

| V <sub>QТНН</sub>     | C/Q <sub>I</sub> and I/Q<br>upper voltage<br>threshold    |                 | 10.5 |      | 12.9 | >    |

| V <sub>QTHL</sub>     | C/Q <sub>I</sub> and I/Q<br>lower voltage<br>threshold    |                 | 8    |      | 11.4 | V    |

| V <sub>QHY</sub>      | C/Q and I/Q<br>hysteresis<br>voltage                      |                 | 1    |      |      | V    |

| V <sub>demag</sub>    | L+<br>demagnetization<br>voltage                          | I = 5 mA        | -8.5 | -6.5 | -4.8 | V    |

| V <sub>fHS</sub>      | C/Q high-side<br>freewheeling<br>diode forward<br>voltage | I = 10 mA       |      | 0.5  |      | V    |

| V <sub>fLS</sub>      | C/Q low-side<br>freewheeling<br>diode forward<br>voltage  | I = 10 mA       |      | 0.5  |      | V    |

| Symbol              | Parameter                                        | Test conditions                                          | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------|----------------------------------------------------------|------|------|------|------|

| VLTHOFF             | L+ line<br>diagnostic lower<br>threshold         |                                                          | 9    | 10   | 11   | V    |

| V <sub>LTHY</sub>   | L+ line<br>diagnostic<br>hysteresis              |                                                          | 0.1  | 1    |      | V    |

| VLTHON              | L+ line<br>diagnostic upper<br>threshold         |                                                          | 10   | 11   | 12   | V    |

| Is                  | Supply current                                   | OFF-state                                                |      | 100  |      | μA   |

|                     |                                                  | ON-state Vcc at 32.5 V                                   |      | 4    |      | mA   |

| loffcq              | OFF-state C/Qo current                           | $EN_{C/Q} = 0, \ V_{C/Q} = 0 \ V$                        |      |      | 1    | μA   |

|                     |                                                  |                                                          | 70   | 115  | 190  |      |

| Icoq                | C/Qo low- and high-side cut-off                  | Programmable                                             | 150  | 220  | 300  | mA   |

| ICOQ                | current                                          | 1 Togrammable                                            | 290  | 350  | 440  | ША   |

|                     |                                                  |                                                          | 430  | 580  | 720  |      |

| I <sub>LIMQ</sub>   | C/Qo low- and<br>high-side<br>limitation current |                                                          | 500  |      | 1600 | mA   |

| loffl               | L+ OFF-state current                             | $EN_{L+} = 0, V_{L+} = 0 V$                              | 0    |      | 200  | μA   |

| Icol                | L+ cut-off<br>current                            |                                                          | 480  | 580  | 730  | mA   |

| ILIML               | L+ limitation current                            |                                                          | 500  |      | 1600 | mA   |

| I <sub>INC/Qi</sub> | C/Qı pull-down                                   | Programmable                                             | 5    |      | 6.5  | mA   |

| TINC/QI             | current                                          | Trogrammable                                             | 2    |      | 3.3  | mA   |

| l <sub>INI/Q</sub>  | I/Q pull-down<br>current                         |                                                          | 2    |      | 3    | mA   |

|                     | L+ high-side                                     | IOUT = 0.2 A at T <sub>J</sub> = 25 °C                   |      | 1    |      | Ω    |

| Ronl                | ON-state resistance                              | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 125 °C      |      |      | 2    | Ω    |

|                     | C/Q <sub>O</sub> high-side                       | $I_{OUT} = 0.2 \text{ A}$ at $T_J = 25 ^{\circ}\text{C}$ |      | 1    |      | Ω    |

| Roncah              | ON-state resistance                              | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 125 °C      |      |      | 2    | Ω    |

|                     | C/Q <sub>O</sub> low-side                        | $I_{OUT} = 0.2 \text{ A at T}_{J} = 25 ^{\circ}\text{C}$ |      | 0.6  |      | Ω    |

| Roncal              | ON-state resistance                              | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 125 °C      |      |      | 1.2  | Ω    |

|                     | IN <sub>C/Q</sub> to C/Q <sub>O</sub>            | Push-pull (CQ <sub>O</sub> rising edge)                  |      | 140  |      | ns   |

| tdINC/Q             | propagation delay time                           | Push-pull (CQ <sub>O</sub> falling edge)                 |      | 160  |      | ns   |

|                     | EN <sub>C/Q</sub> to C/Q <sub>O</sub>            | Push-pull (CQ <sub>O</sub> rising edge)                  |      | 110  |      | ns   |

| tenc/Q              | propagation delay time                           | Push-pull (CQ <sub>O</sub> falling edge)                 |      | 225  |      | ns   |

| Symbol             | Parameter                                                                        | Test conditions | Min. | Тур.                    | Max. | Unit |

|--------------------|----------------------------------------------------------------------------------|-----------------|------|-------------------------|------|------|

| trPP               | C/Q rise time in push-pull configuration                                         | 10% to 90%      | 250  |                         | 860  | ns   |

| t <sub>fPP</sub>   | C/Q fall time in<br>push-pull<br>configuration                                   | 10% to 90%      | 290  |                         | 860  | ns   |

| t <sub>rHS</sub>   | C/Q rise time in<br>high-side<br>configuration                                   |                 |      | 410                     |      | ns   |

| t <sub>fHS</sub>   | C/Q fall time in<br>high-side<br>configuration                                   |                 |      | 700                     |      | ns   |

| trLS               | C/Q rise time in low-side configuration                                          |                 |      | 750                     |      | ns   |

| t <sub>fLS</sub>   | C/Q fall time in<br>low-side<br>configuration                                    |                 |      | 530                     |      | ns   |

| tenl               | ENL to L+<br>propagation<br>delay time                                           |                 |      | 1                       |      | μs   |

| t <sub>rL+</sub>   | L+ rise time                                                                     |                 |      | 3                       |      | μs   |

| t <sub>fL+</sub>   | L+ fall time                                                                     |                 |      | 25                      |      | μs   |

|                    | C/Q <sub>i</sub> to OUT <sub>C/Q</sub><br>(falling)<br>propagation<br>delay time |                 |      | 40                      |      | ns   |

| t <sub>dC/Qi</sub> | C/Q <sub>I</sub> to OUT <sub>C/Q</sub> (rising) propagation delay time           |                 |      | 100                     |      | ns   |

| t                  | I/Q to OUT <sub>I/Q</sub><br>(falling)<br>propagation<br>delay time              |                 |      | 40                      |      | ns   |

| t <sub>dI/Q</sub>  | I/Q to OUT <sub>I/Q</sub><br>(rising)<br>propagation<br>delay time               |                 |      | 100                     |      | ns   |

|                    | C/Qo low- and                                                                    |                 |      | 100                     |      | μs   |

| t.                 | high-side cut-off                                                                | Programmable    |      | 150                     |      | μs   |

| t <sub>dcoq</sub>  | current delay                                                                    | Programmable    |      | 200                     |      | μs   |

|                    | time                                                                             |                 | 250  |                         | μs   |      |

| t <sub>rcoq</sub>  | C/Qo restart delay time Programmable                                             | Programmable    |      | 255 × t <sub>dcoq</sub> |      | μs   |

| rcoq               |                                                                                  | delay time      |      | Latched <sup>(1)</sup>  |      | μδ   |

| t <sub>dbq</sub>   | C/Q <sub>I</sub> debounce Programmable                                           |                 | 0    |                         | μs   |      |

|                    | time                                                                             |                 |      | 5                       |      | μδ   |

| Symbol            | Parameter                                        | Test conditions | Min. | Тур.        | Max. | Unit |

|-------------------|--------------------------------------------------|-----------------|------|-------------|------|------|

|                   |                                                  |                 |      | 20          |      |      |

|                   |                                                  |                 |      | 100         |      |      |

|                   |                                                  |                 |      | 0           |      |      |

| +                 | I/Q debounce                                     | Drogrammable    |      | 5           |      |      |

| t <sub>dbl</sub>  | time                                             | Programmable    |      | 20          |      | μs   |

|                   |                                                  |                 |      | 100         |      |      |

|                   | L+ cut-off                                       |                 |      | 500         |      |      |

| t <sub>dcol</sub> | current delay time Programmable                  | Programmable    |      | 0           |      | μs   |

| + .               | L+ restart delay                                 | Programmable    |      | 64          |      | ms   |

| t <sub>rcol</sub> | time                                             | Frogrammable    |      | Latched (1) |      |      |

| T <sub>JSD</sub>  | Junction<br>temperature<br>shutdown              |                 |      | 150         |      | °C   |

| Тлнүзт            | Junction<br>temperature<br>thermal<br>hysteresis |                 |      | 20          |      | °C   |

| T <sub>JRST</sub> | Junction<br>temperature<br>restart threshold     |                 |      | 130         |      | °C   |

#### Notes:

Table 6: Electrical characteristics - linear regulator

| Symbol            | Parameter                                  | Test conditions | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------------------|-----------------|------|------|------|------|

| \/                | Linear regulator output voltage            | SEL = L         | 4.84 | 5    | 5.13 | V    |

| V <sub>DD</sub>   | Linear regulator output voltage            | SEL = H         | 3.22 | 3.3  | 3.37 | V    |

| I <sub>LIMR</sub> | Linear regulator output current limitation |                 | 65   |      |      | mA   |

Table 7: Electrical characteristics - logic inputs and outputs

| Symbol            | Parameter                               | Test conditions          | Min.                    | Тур. | Max. | Unit |

|-------------------|-----------------------------------------|--------------------------|-------------------------|------|------|------|

| VIL               | Input low-level voltage                 |                          |                         |      | 0.8  | V    |

| V <sub>IH</sub>   | Input high-level voltage                |                          | 2.2                     |      |      | V    |

| VIHIS             | Input hysteresis voltage                |                          |                         | 0.2  |      | V    |

| lin               | Input current                           | V <sub>IN</sub> = 5 V    |                         |      | 1    | μΑ   |

| Vol               | Output low-level voltage                | I <sub>OUT</sub> = -2 mA |                         |      | 0.5  | V    |

| Vон               | Output high-level voltage               | I <sub>OUT</sub> = 2 mA  | V <sub>DD</sub> - 0.5 V |      |      | V    |

| V <sub>LIRQ</sub> | Open drain output low-<br>level voltage | I <sub>OUT</sub> = 2 mA  |                         |      | 0.5  | V    |

$<sup>^{(1)}</sup>$ Unlatch through  $I^2$ C communication.

Table 8: Electrical characteristics - LED driving

|                     |                                     |                                             | 9    |      |      |      |

|---------------------|-------------------------------------|---------------------------------------------|------|------|------|------|

| Symbol              | Parameter                           | Test conditions                             | Min. | Тур. | Max. | Unit |

| V <sub>LED1,2</sub> | Open drain output low-level voltage | I <sub>LED</sub> = 2 mA                     |      |      | 0.5  | V    |

| I <sub>LED</sub>    | LED1, 2 leakage current             | V <sub>LED1</sub> = V <sub>LED2</sub> = 5 V |      | 3    |      | nA   |

Table 9: Electrical characteristics - I<sup>2</sup>C (fast mode)

| Symbol               | Parameter Parameter                     | Test conditions                                            | Min.                    | Max.   | Unit     |

|----------------------|-----------------------------------------|------------------------------------------------------------|-------------------------|--------|----------|

| Cymbol               |                                         | Tool ouriding                                              | IVIII.                  | IIIUA. | Oiiit    |

| V <sub>IL(SDA)</sub> | SDA high level input voltage            |                                                            |                         | 0.3    | V        |

| V <sub>IH(SDA)</sub> | SDA high level input voltage            |                                                            | 0.7 x V <sub>DD</sub>   |        | ٧        |

| V <sub>IL(SCL)</sub> | SCL low level input voltage             |                                                            |                         | 0.3    | ٧        |

| V <sub>IH(SCL)</sub> | SCL high level input voltage            |                                                            | 0.7 x V <sub>DD</sub>   |        | <b>V</b> |

| I <sub>IN</sub>      | I <sup>2</sup> C SDA, SCL input current | $(0.1 \text{ x V}_{DD}) < V_{IN} < (0.9 \text{ x V}_{DD})$ | -10                     | 10     | μΑ       |

| t <sub>r(SDA)</sub>  | I <sup>2</sup> C SDA rise time          |                                                            | 20 + 0.1 C <sub>b</sub> | 300    | ns       |

| t <sub>r(SCL)</sub>  | I <sup>2</sup> C SCL rise time          |                                                            | 20 + 0.1 C <sub>b</sub> | 300    | ns       |

| t <sub>f(SDA)</sub>  | I <sup>2</sup> SDA fall time            |                                                            | 20 + 0.1 C <sub>b</sub> | 300    | ns       |

| t <sub>f(SCL)</sub>  | I <sup>2</sup> C SCL fall time          |                                                            | 20 + 0.1 C <sub>b</sub> | 300    | ns       |

| t <sub>su(SDA)</sub> | SDA set-up time                         |                                                            | 100                     |        | ns       |

| th(SDA)              | SDA hold time                           |                                                            |                         | 0.9    | μs       |

| t <sub>su(STA)</sub> | Repeated start condition setup          |                                                            | 0.6                     |        | μs       |

| tsu(STO)             | Top condition set-up time               |                                                            | 0.6                     |        | μs       |

| tw(START/STOP)       | Stop to start condition time (bus free) |                                                            | 1.3                     |        | μs       |

| tw(SCLL)             | SCL clock low time                      |                                                            | 1.3                     |        | μs       |

| t <sub>w(SCLH)</sub> | SCL clock high time                     |                                                            | 0.6                     |        | μs       |

| Сь                   | Capacitance for each bus line           |                                                            |                         | 400    | pF       |

| Cı                   | Capacitance for each I/O pin            |                                                            |                         | 10     | pF       |

Values based on standard I<sup>2</sup>C protocol requirement.

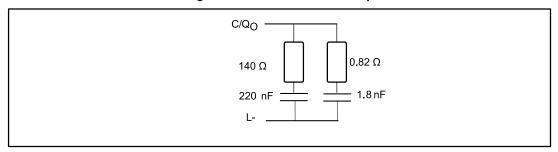

Figure 3: Rise/fall time test setup

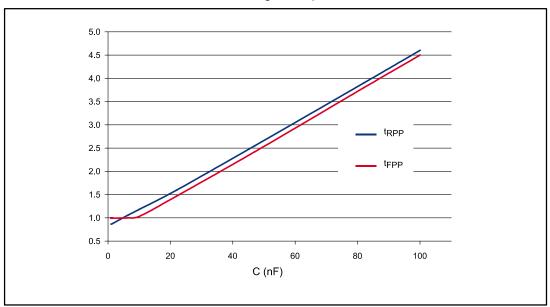

Figure 4: Normalized rise and fall time vs. output capacitor value (typ. values in push-pull configuration)

Table 10: Main parameter typical variations vs. +/- 1% variation of Rbias value

|                     | Parameter                                          | Typ. variation vs. Rbia |     | vs. R <sub>bias</sub> |

|---------------------|----------------------------------------------------|-------------------------|-----|-----------------------|

| Symbol              |                                                    | R <sub>bias</sub> [kΩ]  |     | 2]                    |

|                     |                                                    | 122.74                  | 124 | 125.24                |

| Is                  | Supply current                                     | 0.76%                   | 0   | -0.50%                |

| I <sub>INC/Qi</sub> | Input current C/Q <sub>1</sub> pin (5.5 mA)        | 0.93%                   | 0   | -0.93%                |

| I <sub>INC/Qi</sub> | Input current C/Q <sub>1</sub> pin (2.5 mA)        | 0.75%                   | 0   | -1.13%                |

| I <sub>INI/Q</sub>  | Input current I/Q pin (2.5 mA)                     | 0.85%                   | 0   | -0.85%                |

| t <sub>dcoq</sub>   | C/Qo low- and high-side cut-off current delay time | -2.44%                  | 0   | 2.00%                 |

| Icoq                | C/Qo low- and high-side cut-off current (115 mA)   | 1.19%                   | 0   | -1.28%                |

| t <sub>dcol</sub>   | L+ cut-off current delay time (500 μs)             | -0.95%                  | 0   | 0.47%                 |

| I <sub>COL</sub>    | L+ cut-off current                                 | 1.36%                   | 0   | -0.91%                |

| t <sub>rcol</sub>   | L+ restart delay time                              | -0.93%                  | 0   | 0.97%                 |

| Vuv                 | Undervoltage ON-threshold                          | 0.00%                   | 0   | 0.00%                 |

47/

|                     | Parameter                                                     | Typ. vai | iation              | vs. R <sub>bias</sub> |

|---------------------|---------------------------------------------------------------|----------|---------------------|-----------------------|

| Symbol              |                                                               | R        | <sub>bias</sub> [kΩ | 2]                    |

|                     |                                                               | 122.74   | 124                 | 125.24                |

| $V_{DD}$            | Linear regulator output voltage (3.3 V)                       | -0.03%   | 0                   | 0.03%                 |

| $V_{DD}$            | Linear regulator output voltage (5 V)                         | -0.02%   | 0                   | 0.02%                 |

| $I_{LIMQ}$          | C/Qo high-side limitation current                             | 0.64%    | 0                   | -0.71%                |

| I <sub>LIMQ</sub>   | C/Qo low-side limitation current                              | 0.28%    | 0                   | -1.47%                |

| I <sub>LIML</sub>   | L+ limitation current                                         | 0.47%    | 0                   | -2.09%                |

| $V_{QTHH}$          | C/Q <sub>I</sub> and I/Q upper voltage threshold              | 0.00%    | 0                   | 0.00%                 |

| V <sub>QTHL</sub>   | C/Q <sub>I</sub> and I/Q lower voltage threshold              | 0.00%    | 0                   | 0.00%                 |

| V <sub>QHY</sub>    | C/Q and I/Q hysteresis voltage                                | 0.00%    | 0                   | 0.00%                 |

| trPP                | C/Q rise time in push-pull configuration                      | -1.59%   | 0                   | 1.18%                 |

| t <sub>fPP</sub>    | C/Q fall time in push-pull configuration                      | -2.14%   | 0                   | 0.94%                 |

| t <sub>dINC/Q</sub> | IN <sub>C/Q</sub> to C/Q <sub>O</sub> propagation delay time  | -1.44%   | 0                   | 0.75%                 |

| t <sub>dINC/Q</sub> | IN <sub>C/Q</sub> to C/Q <sub>O</sub> propagation delay time  | -2.36%   | 0                   | 0.18%                 |

| t <sub>dC/Qi</sub>  | C/Q <sub>I</sub> to OUT <sub>C/Q</sub> propagation delay time | 0.49%    | 0                   | 1.13%                 |

| t <sub>dC/Qi</sub>  | C/Q <sub>I</sub> to OUT <sub>C/Q</sub> propagation delay time | 1.82%    | 0                   | 0.03%                 |

| t <sub>dbq</sub>    | C/Q <sub>I</sub> debounce time (100 μs)                       | -1.76%   | 0                   | 1.50%                 |

| t <sub>dcoq</sub>   | C/Qo low- and high-side cut-off current delay time (200 μs)   | -1.27%   | 0                   | 2.00%                 |

| Icoq                | C/Qo low-side cut-off current (220 mA)                        | 0.39%    | 0                   | -1.56%                |

| Icoq                | C/Qo low-side cut-off current (350 mA)                        | 0.36%    | 0                   | -1.43%                |

| Icoq                | C/Qo low-side cut-off current (580 mA)                        | 0.65%    | 0                   | -1.72%                |

| trcoq               | C/Qo restart delay time                                       | -0.90%   | 0                   | 0.97%                 |

| Icoq                | C/Qo high-side cut-off current (220 mA)                       | 0.84%    | 0                   | -0.84%                |

| Icoq                | C/Qo high-side cut-off current (350 mA)                       | 1.38%    | 0                   | -0.69%                |

| Icoq                | C/Qo high-side cut-off current (580 mA)                       | 1.08%    | 0                   | -1.08%                |

Device configuration L6360

## 6 Device configuration

SDA and SCL configure the L6360 device through I2C.

#### 6.1 Introduction

The I<sup>2</sup>C bus interface serves as an interface between the microcontroller and the serial I<sup>2</sup>C bus. It provides single master functions, and controls all I<sup>2</sup>C bus-specific sequencing, protocol and timing. It supports fast I<sup>2</sup>C mode (400 kHz).

### 6.2 Main features

- Parallel bus/I<sup>2</sup>C protocol converter

- Interrupt generation

- Fast I<sup>2</sup>C mode

- 7-bit addressing

## 6.3 General description

In addition to receiving and transmitting data, this interface converts it from serial to parallel format and vice versa. The interface is connected to the I<sup>2</sup>C bus by a data pin (SDA) and a clock pin (SCL).

### 6.4 SDA/SCL line control

SDA is a bi-directional line, SCL is the clock input. SDA should be connected to a positive supply voltage via a current-source or pull-up resistor. When the bus is free, both lines are HIGH. The output stages of the devices connected to the bus must have an open drain or open collector output to perform the wired AND function. Data on the I²C bus can be transferred to rates up to 400 Kbit/s in fast mode. The number of interfaces connected to the bus is limited by the bus capacitance. For a single master application, the master's SCL output can be a push-pull driver provided that there are no devices on the bus which would stretch the clock. Transmitter mode: the microcontroller interface holds the clock line low before transmission. Receiver mode: the microcontroller interface holds the clock line low after reception. When the I²C microcontroller cell is enabled, the SDA and SCL ports must be configured as floating inputs. In this case, the value of the external pull-up resistors used depends on the application. When the I²C microcontroller cell is disabled, the SDA and SCL ports revert to being standard I/O port pins. On the L6360, the SDA output is an open drain pin.

### 6.5 Mode selection

Possible data transfer formats are:

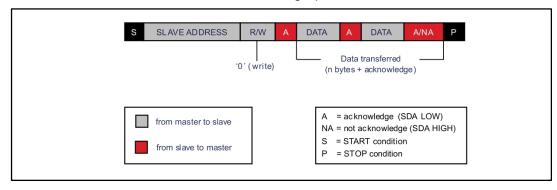

- The master transmitter transmits to the slave receiver. The transfer direction is not changed

- The slave receiver acknowledges each byte

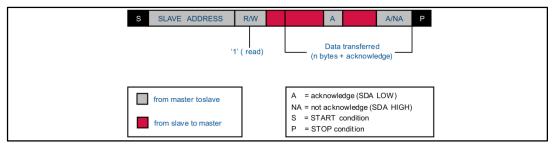

- The master reads data from the slave immediately after the first byte (see Figure 6: "A

master reads data from the slave immediately after the first byte"). At the moment of

the first acknowledge, the master transmitter becomes a master receiver and the slave

receiver becomes a slave transmitter

This first acknowledge is still generated by the slave. Subsequent acknowledges are generated by the master. The STOP condition is generated by the master which sends a not-acknowledge (A) just prior to the STOP condition.

L6360 Device configuration

Figure 5: A master transmitter addressing a slave receiver with a 7-bit address (the transfer is not changed)

Figure 6: A master reads data from the slave immediately after the first byte

On the microcontroller, the interface can operate in the two following modes:

- Master transmitter/receiver

- Idle mode (default state)

The microcontroller interface automatically switches from idle to master receiver after it detects a START condition and from master receiver to idle after it detects a STOP condition. On the L6360 the interface can operate in the two following modes:

- Slave transmitter/receiver

- Idle mode (default state)

The interface automatically switches from idle to slave transmitter after it detects a START condition and from slave transmitter to idle after it detects a STOP condition.

Device configuration L6360

# 6.6 Functional description

By default, the I<sup>2</sup>C microcontroller interface operates in idle; to switch from default idle mode to master mode a START condition generation is needed. The transfer sequencing is shown in the picture below.

7-bit master transmitter (microcontroller)/ slave receiver (L6360)

S SLAVE ADDRESS R/W DATA1 .... DATA N A/NA P

7-bit master receiver (microcontroller) / slave transmitter (L6360)

S SLAVE ADDRESS R/W A .... A/NA P

A DATA1 DATA N

Figure 7: Transfer sequencing

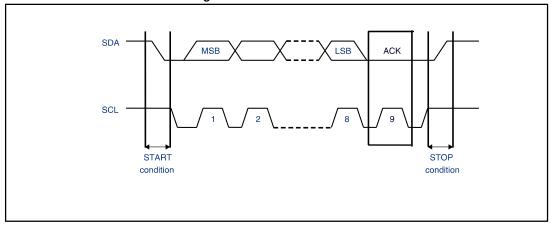

### 6.7 Communication flow

from master to slave

The communication is managed by the microcontroller that generates the clock signal. A serial data transfer always begins with a START condition and ends with a STOP condition. Data is transferred as 8-bit bytes, MSB first. The first byte following the START condition contains the address (7 bits). The 9<sup>th</sup> clock pulse follows the 8<sup>th</sup> clock cycle of a byte transfer, during which the receiver must send an acknowledge bit to the transmitter.

Figure 8: I<sup>2</sup>C communication

Each byte is followed by an acknowledgment bit as indicated by the A or A blocks in the sequence. A START condition immediately followed by a STOP condition (void message) is a prohibited format.

L6360 Device configuration

### 6.8 I<sup>2</sup>C address

Each  $I^2C$  connected to the bus is addressable by a unique address. The  $I^2C$  address is 7 bits long, and there is a simple master/slave relationship. The LSB of the L6360 address can be programmed by means of dedicated IC pins (SA0, SA1 and SA2, which can be hard wired to  $V_{DD}$  or GND, or handled by  $\mu C$  outputs): the microcontroller can interface up to 8 L6360 ICs. The  $I^2C$  inside the device has 5 pins:

- SDA: data

- SCL: clock

- SA0: LSB of the L6360 address

- SA1: bit 1 of the L6360 address

- SA2: bit 2 of the L6360 address

The I2C L6360 IC address is:

- Fixed part (4 MSBits): set to "1100"

- Programmable part (3 LSBits) by hardware: from "000 to 111" connecting SAx pins to GND or VDD

In the L6360 the SDA is an open drain pin.

## 6.9 Internal register

The L6360 has some internal registers to perform control, configuration, and diagnostic operations. These registers are listed below:

- · Status register

- Configuration register

- Control register 1

- Control register 2

- LED1 register MSB

- LED1 register LSB

- LED2 register MSB

- LED2 register LSB

- Parity register

Each register is addressable as follows:

Table 11: Register addresses

| Address | Register name          |

|---------|------------------------|

| 0000    | Status register        |

| 0001    | Configuration register |

| 0010    | Control register 1     |

| 0011    | Control register 2     |

| 0100    | LED1 MSB               |

| 0101    | LED1 LSB               |

| 0110    | LED2 MSB               |

| 0111    | LED2 LSB               |

| 1000    | Parity register        |

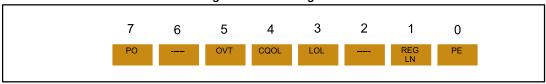

#### Status register

Read only

Reset value: [00000000]

Figure 9: Status register

The status register stores diagnostic information. It can be read to check the status of the run-time of the device (faults, warning, transmission corrupted, etc.). When a fault condition occurs, a bit (corresponding to the fault condition) in the status register is set and an interrupt (via the IRQ pin) is generated. If there is no persistent fault condition, the status register is cleared after a successful current read.

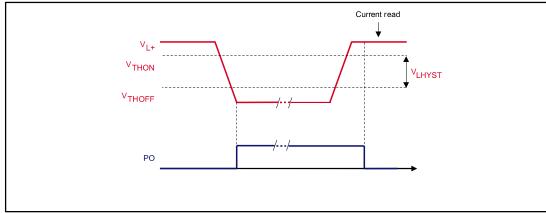

Bit 7 = PO: Power-on (L+ line)

This bit indicates the status of L+ line voltage. If the voltage goes under the lower threshold ( $V_{LTHOFF}$ ) and  $EN_{L+}$  is high, the PO bit is set. It is reset after a successful current read if the L+ voltage has returned above the upper threshold  $V_{LTHON}$  and the read operation has begun after the bit has been set. When the PO bit is high, IRQ is generated. During  $EN_{L+}$  transition (from low-level to high-level) and during L+ line voltage transition, a fault condition is reported setting the PO bit and activating the IRQ pin. To reset the fault a successful current read is necessary.

Figure 10: Power-on bit behavior

Bit 6 = not used: always at zero

Bit 5 = OVT: overtemperature fault

This bit indicates the status of the IC internal temperature. If the temperature goes above the thermal shutdown threshold (T >  $T_{JSD}$ ) the OVT bit is set. It is reset after a successful current read if the temperature has returned below the thermal restart threshold ( $T_{JDS}$  -  $T_{JHIST}$ ) and the read operation has begun after the bit has been set. When OVT bit is high, the power outputs are disabled and IRQ is generated.

T<sub>JSD</sub>

T<sub>JRST</sub>

T<sub>JRST</sub>

OVT

Figure 11: Overtemperature (OVT) bit behavior

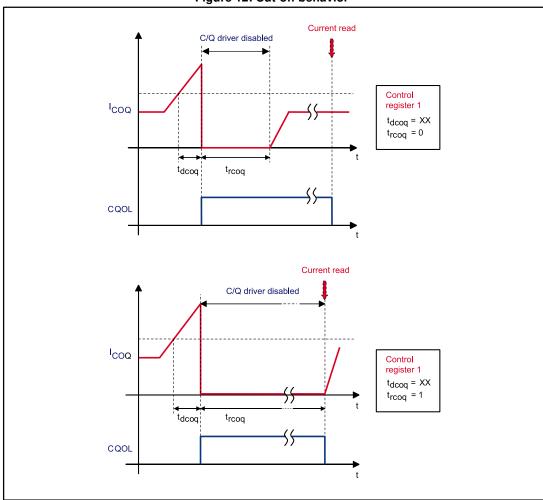

Bit 4 = CQOL: C/Q overload

This bit is set if a cut-off occurs on the C/Q channel. It is reset after a successful current read if the restart delay time ( $t_{rcoq}$ ) has elapsed or the protection is latched (bit  $t_{rcoq} = 1$ ). The read operation should begin after the CQOL bit has been set. When CQOL bit is high, IRQ is generated. When CQOL bit is high and the protection is latched (bit  $t_{rcoq} = 1$  in control register 1), the C/Q power output is disabled. See next figure.

Figure 12: Cut-off behavior

Bit 3 = LOL: L+ overload

This bit is set if a cut-off occurs on the L+ driver. It is reset after a successful current read if the restart delay time ( $t_{rcol}$ ) has elapsed or the protection is latched (bit  $t_{rcol} = 1$  in control register 2). The read operation should begin after the LOL bit has been set. When LOL bit is high, IRQ is generated. When LOL bit is high and the protection is latched (bit  $t_{rcol} = 1$  in control register 2), the L+ power output is disabled. The behavior is the same as the C/Q driver (see *Figure 12: "Cut-off behavior"*).

Bit 2 = not used: always at zero

Bit 1 = REG LN: linear regulator undervoltage fault

This bit is set in case of undervoltage of the linear regulator output ( $V_{REGLNL}$ ). It is reset after a successful current read if the linear regulator output has returned to normal operation and the read operation has begun after the bit has been set. When REGLN bit is high, IRQ is generated.

Bit 0 = PE: parity check error

This flag is set if parity error occurs.

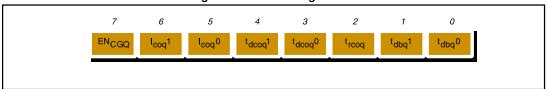

#### **Control register 1**

Read/write

Reset value: [00100001]

Figure 13: Control register 1

The control register holds the parameters to control the L6360.

Bit 7 = ENcgq: C/Q<sub>I</sub> pull-down enable

Table 12: ENCGQ: C/Q pull-down enable

| ENcgq | Pull-down generator status |     |  |

|-------|----------------------------|-----|--|

| 0     | Always OFF                 |     |  |

| 1     | If EN <sub>G/Q</sub> = 0   | ON  |  |

|       | If EN <sub>G/Q</sub> = 1   | OFF |  |

Bit 6:5 = Icoq [1:0]: C/Qo HS and LS cut-off current

This bit is used to configure the cut-off current value on the C/Q channel, as shown in the following table.

Table 13: Icog: C/QO HS and LS cut-off current

| I <sub>coq</sub> [1] | I <sub>coq</sub> [0] | Тур.   |

|----------------------|----------------------|--------|

| 0                    | 0                    | 115 mA |

| 0                    | 1                    | 220 mA |

| 1                    | 0                    | 350 mA |

| 1                    | 1                    | 580 mA |

24/60

L6360 Device configuration

Bit  $4:3 = t_{dcoq}$  [1:0]: C/Q<sub>O</sub> HS and LS cut-off current delay time

The channel output driver is turned off after a delay  $(t_{dcoq})$  programmable by means of these two bits.

Table 14:  $t_{\text{dcoq}}$ : C/QO HS and LS cut-off current delay time

| t <sub>dcoq</sub> [1] | t <sub>dcoq</sub> [0] | Тур.                  |

|-----------------------|-----------------------|-----------------------|

| 0                     | 0                     | 100 μs                |

| 0                     | 1                     | 150 μs                |

| 1                     | 0                     | 200 μs                |

| 1                     | 1                     | 250 μs <sup>(1)</sup> |

#### Notes:

Bit  $2 = t_{rcoq}$ : C/Q<sub>O</sub> restart delay time

After a cut-off event, the channel driver automatically restarts after a delay ( $t_{rcoq}$ ) programmable by means of this bit.

Table 15: trcoq: C/QO restart delay time

| t <sub>rcoq</sub> | Тур.                   |  |

|-------------------|------------------------|--|

| 0                 | 255x t <sub>dcoq</sub> |  |

| 1                 | Latched <sup>(1)</sup> |  |

#### Notes:

### Bit $1:0 = t_{dbq} [1:0]$ : C/Q<sub>I</sub> debounce time

Debounce time is the minimum time that data must be in a given state after a transition. It is a programmable time, and can be configured as shown in the following table.

Table 16: t<sub>dbq</sub>: C/QI debounce time

| t <sub>dbq</sub> [1] | t <sub>dbq</sub> [0] | Тур.   |

|----------------------|----------------------|--------|

| 0                    | 0                    | 0 μs   |

| 0                    | 1                    | 5 μs   |

| 1                    | 0                    | 20 μs  |

| 1                    | 1                    | 100 μs |

#### **Control register 2**

Read/write

Reset value: [0x100001]

<sup>(1)</sup>According to power dissipation at 2 kHz switching, C < 1 μF and power dissipation 0.7 W.

<sup>&</sup>lt;sup>(1)</sup>Unlatch through I<sup>2</sup>C communication (reading or writing any internal register).