Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 3+1 dual controller for VR12 with PMBus

Datasheet - production data

#### **Features**

- VR12 compliant with 25 MHz SVID bus Rev1.5

- SerialVID with programmable IMAX, TMAX, VBOOT, ADDRESS

- Second generation LTB Technology<sup>™</sup>

- Flexible driver/DrMOS support

- JMode support

- Fully configurable through PMBus

- Dual controller:

- 3-phase for VDDQ

- 1-phase for VTT

- Single NTC design for TM, LL and Imon thermal compensation

- VFDE and GDC gate drive control for efficiency optimization

- DPM dynamic phase management

- Dual remote sense

- 0.5% output voltage accuracy

- Full-differential current sense across DCR

- AVP adaptive voltage positioning

- Dual independent adjustable oscillator

- Dual current monitor

- Pre-biased output management

- Average and per-phase OC protection

- OV, UV and FB disconnection protection

- Dual VR\_RDY

- VFQFPN48 6x6 mm package

### **Application**

■ DDR3 memory supply for VR12 servers

### **Description**

The L6759D is a dual controller designed to power Intel's VR12 processor memories: all required parameters are programmable through dedicated pin-strapping and PMBus interface.

The device features 3-phase programmable operation for the multi-phase section and a single-phase with independent control loops. Single-phase (VTT) reference is always tracking multi-phases (VDDQ) scaled by a factor of 2.

The L6759D supports power state transitions featuring VFDE, programmable DPM and GDC maintaining the best efficiency over all loading conditions without compromising transient response.

The device assures fast and independent protection against load overcurrent, under/overvoltage and feedback disconnections.

The device is available in a VFQFPN48 6x6 mm package.

Table 1. Device summary

| Order code | Package                | Packing       |

|------------|------------------------|---------------|

| L6759D     | VFQFPN48 6x6mm         | Tray          |

| L6759DTR   | VI QI I 1440 0X0IIIIII | Tape and reel |

Contents L6759D

# **Contents**

| 1 | Турі  | cal application circuit and block diagram                      | 5    |

|---|-------|----------------------------------------------------------------|------|

|   | 1.1   | Application circuit                                            | 5    |

|   | 1.2   | Block diagram                                                  | 7    |

| 2 | Pin ( | description and connection diagrams                            | 8    |

|   | 2.1   | Pin description                                                | 8    |

|   | 2.2   | Thermal data                                                   | . 12 |

| 3 | Elec  | trical specifications                                          | . 13 |

|   | 3.1   | Absolute maximum ratings                                       | . 13 |

|   | 3.2   | Electrical characteristics                                     | . 13 |

| 4 | Devi  | ice configuration and pin-strapping tables                     | . 17 |

|   | 4.1   | JMode                                                          | . 17 |

|   | 4.2   | Programming HiZ level                                          | . 18 |

| 5 | Devi  | ice description and operation                                  | . 20 |

|   | 5.1   | Device initialization                                          | . 20 |

| 6 | Outp  | out voltage positioning                                        | . 22 |

|   | 6.1   | Multi-phase section - phase # programming                      | . 22 |

|   | 6.2   | Multi-phase section - current reading and current sharing loop | . 22 |

|   | 6.3   | Multi-phase section - defining load-line                       | . 23 |

|   | 6.4   | Multi-phase section - IMON information                         | . 24 |

|   | 6.5   | Single-phase section - disable                                 | . 25 |

|   | 6.6   | Single-phase section - current reading                         | . 25 |

|   | 6.7   | Single-phase section - defining load-line                      | . 25 |

|   | 6.8   | Dynamic VID transition support                                 | . 25 |

|   | 6.9   | DVID optimization: REF                                         | . 26 |

| 7 | Outp  | out voltage monitoring and protection                          | . 28 |

|   | 7.1   | Overvoltage                                                    | . 28 |

|   | 7.2   | Overcurrent                                                    | . 28 |

|   |       |                                                                |      |

| 9.1<br>9.2<br>9.3<br><b>Main</b><br>10.1<br><b>Syst</b><br>11.1<br>11.2 | iency of Dynan Variab Gate of oscilla LSLES em con Compo LTB Te us sup Enabli Contro | ptimization  ptimization  pic phase management (DPM)  le frequency diode emulation (VFDE)  lrive control (GDC)  tor  SS startup and pre-bias output  trol loop compensation  ensation network guidelines  echnology  port  ing the device through PMBus  roltage monitoring (READ_VIN)  ycle monitoring (READ_DUTY) | 34 35 35 37 38 40 41 45 45 46    |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 8.3  Effication 9.1 9.2 9.3  Main 10.1  Syst 11.1 11.2  PMB 12.1        | iency of Dynan Variab Gate of oscilla LSLES em con Compo LTB Te us sup Enabli Contro | ptimization  nic phase management (DPM)  le frequency diode emulation (VFDE)  lrive control (GDC)  tor  SS startup and pre-bias output  trol loop compensation ensation network guidelines echnology  port  ng the device through PMBus  silling Vout through PMBus                                                 | 34 35 35 37 38 40 41 45 45       |

| 8.3  Effication 9.1 9.2 9.3  Main 10.1  Syst 11.1 11.2  PMB             | iency o  Dynan  Variab  Gate o  oscilla  LSLES  em con  Compe                        | ptimization  nic phase management (DPM)  le frequency diode emulation (VFDE)  lrive control (GDC)  tor  SS startup and pre-bias output  trol loop compensation ensation network guidelines echnology                                                                                                                | 34 35 35 37 38 40 41 42          |

| 8.3  Effic  9.1  9.2  9.3  Main  10.1  Syst  11.1                       | Dynan Variab Gate c  oscilla LSLES em con                                            | ptimization  nic phase management (DPM)  le frequency diode emulation (VFDE)  lrive control (GDC)  tor  SS startup and pre-bias output  trol loop compensation ensation network guidelines                                                                                                                          | 34<br>35<br>35<br>37<br>38<br>39 |

| 8.3  Effication 9.1 9.2 9.3  Main 10.1  Syst                            | Dynan Variab Gate c  oscilla LSLES                                                   | ptimization  nic phase management (DPM)  le frequency diode emulation (VFDE)  lrive control (GDC)  tor  SS startup and pre-bias output  trol loop compensation                                                                                                                                                      | 34<br>35<br>35<br>37<br>38       |

| 8.3<br>Effic<br>9.1<br>9.2<br>9.3<br>Main                               | iency o  Dynan  Variab  Gate o                                                       | ptimization  nic phase management (DPM)  le frequency diode emulation (VFDE)  lrive control (GDC)                                                                                                                                                                                                                   | 34<br>35<br>35<br>37             |

| 8.3<br>Effic<br>9.1<br>9.2<br>9.3                                       | iency o<br>Dynan<br>Variab<br>Gate o                                                 | ptimization                                                                                                                                                                                                                                                                                                         | 34<br>34<br>35<br>35             |

| 8.3<br><b>Effic</b><br>9.1<br>9.2                                       | <b>iency o</b><br>Dynan<br>Variab                                                    | ptimization                                                                                                                                                                                                                                                                                                         | . <b>34</b><br>. 34<br>. 35      |

| 8.3 <b>Effic</b> 9.1                                                    | <b>iency o</b><br>Dynan                                                              | ptimization                                                                                                                                                                                                                                                                                                         | . <b>34</b>                      |

| 8.3                                                                     | iency o                                                                              | d TCOMP design                                                                                                                                                                                                                                                                                                      | . 34                             |

|                                                                         | i ivi aii                                                                            | •                                                                                                                                                                                                                                                                                                                   | . 33                             |

| 8.2                                                                     | TM on                                                                                | ai compensation                                                                                                                                                                                                                                                                                                     |                                  |

|                                                                         | Therm                                                                                | al compensation                                                                                                                                                                                                                                                                                                     | . 33                             |

| <b>Sing</b> 8.1                                                         |                                                                                      | thermal monitor and compensation                                                                                                                                                                                                                                                                                    |                                  |

|                                                                         |                                                                                      |                                                                                                                                                                                                                                                                                                                     |                                  |

|                                                                         | 722                                                                                  | Single-phase section                                                                                                                                                                                                                                                                                                | 21                               |

|                                                                         | 7.2.2                                                                                | Overcurrent and power states                                                                                                                                                                                                                                                                                        | . 30                             |

|                                                                         |                                                                                      | 7.2.3                                                                                                                                                                                                                                                                                                               | 7.2.3 Single-phase section       |

List of Tables L6759D

# **List of Tables**

| Table 1.  | Device summary                                  | 1  |

|-----------|-------------------------------------------------|----|

| Table 2.  | Pin description                                 |    |

| Table 3.  | Thermal data                                    |    |

| Table 4.  | Absolute maximum ratings                        | 14 |

| Table 5.  | Electrical characteristics                      | 14 |

| Table 6.  | Pin-strapping                                   | 18 |

| Table 7.  | PMBus address definition                        | 19 |

| Table 8.  | L6759D protection at a glance                   | 28 |

| Table 9.  | Multi-phase section OC scaling and power states | 30 |

| Table 10. | Efficiency optimization                         |    |

| Table 11. | Supported commands                              | 42 |

| Table 12. | OV threshold setting                            | 47 |

| Table 13. | VFQFPN48 (6x6 mm) mechanical data               | 48 |

| Table 14  | Document revision history                       | 50 |

L6759D List of figures

# **List of figures**

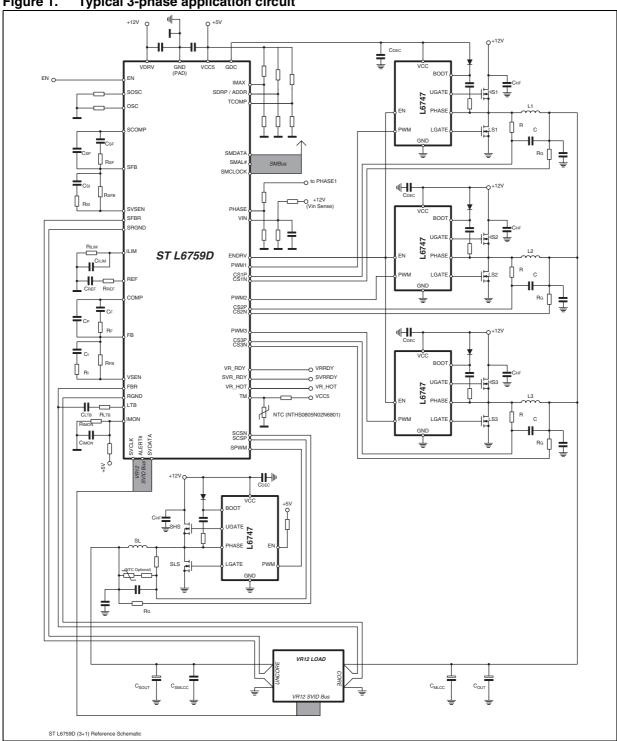

| Figure 1.  | Typical 3-phase application circuit                                                                   | 6  |

|------------|-------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Typical 2-phase application circuit                                                                   | 7  |

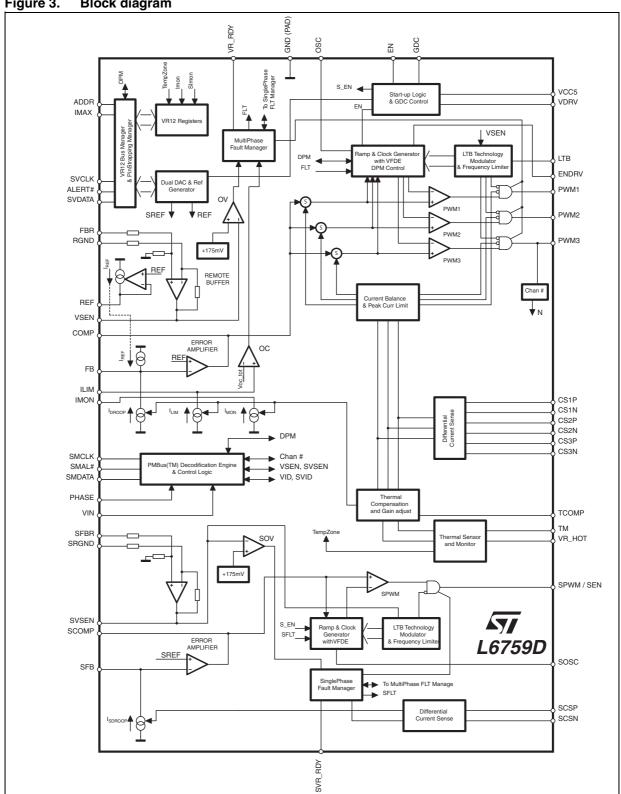

| Figure 3.  | Block diagram                                                                                         | 8  |

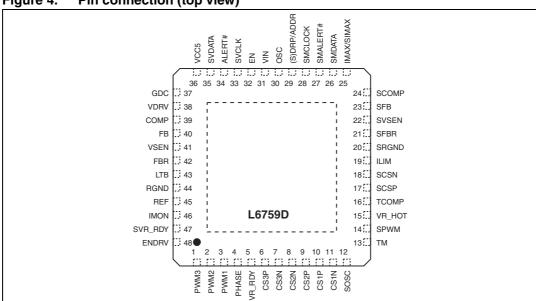

| Figure 4.  | Pin connection (top view)                                                                             | 9  |

| Figure 5.  | JMode: voltage positioning                                                                            | 17 |

| Figure 6.  | Device initialization: default                                                                        | 20 |

| Figure 7.  | Device initialization: alternative sequence                                                           | 21 |

| Figure 8.  | Voltage positioning                                                                                   | 22 |

| Figure 9.  | Current reading                                                                                       | 23 |

| Figure 10. | DVID optimization circuit                                                                             | 27 |

| Figure 11. | Thermal monitor connections                                                                           |    |

| Figure 12. | Output current vs. switching frequency in PSK mode                                                    | 35 |

| Figure 13. | Efficiency performances with and without enhancements (DPM, GDC)                                      | 36 |

| Figure 14. | ROSC vs. F <sub>SW</sub> per phase (R <sub>OSC</sub> to GND - left; R <sub>OSC</sub> to 3.3V - right) | 38 |

| Figure 15. | LSLESS startup: enabled (left) and disabled (right)                                                   | 38 |

| Figure 16. | Equivalent control loop                                                                               | 39 |

| Figure 17. | Control loop Bode diagram and fine tuning                                                             | 40 |

| Figure 18. | Device initialization: PMBus controlling Vout                                                         | 45 |

| Figure 19. | VFQFPN48 (6x6 mm) package drawing                                                                     |    |

# Typical application circuit and block diagram

#### **Application circuit** 1.1

Figure 1. Typical 3-phase application circuit

H CDEC EN UGATE PHASE sosc SDRP / ADDF тсом osc SCOMP LGATE SMDATA SMAL# SMCLOCK o to PHASE1 **HH** SVSEN PHASE SFBR VIN 1 UGATE PHASE ST L6759D ENDRV CS1P CS1N ₹ CS2P CS2N CS3P CS3N VR\_RDY SVR\_RDY SVRRDY VR\_HOT O VR\_HOT RGND TM O VCC5 NTC (NTHS0805N02N6801) SCSN CDEC PHASE PHASE ST L6759D (2+1) Reference Schematic

Figure 2. Typical 2-phase application circuit

#### **Block diagram** 1.2

Figure 3. **Block diagram**

#### Pin description and connection diagrams 2

Figure 4. Pin connection (top view)

#### Pin description 2.1

Table 2. Pin description

| Pin#   | Name            |               | Function                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 3 | PWM3 to<br>PWM1 |               | PWM outputs.  Connect to multi-phase external drivers PWM input. These pins are also used to configure HiZ levels for compatibility with drivers and DrMOS. During normal operations the device is able to manage the HiZ status by setting and holding the PWMx pin to a pre-defined fixed voltage.  Connect PWM3 to 5 V through 1 kW resistor to program 2-phase operation. |

| 4      | PHASE           | section       | Connect through resistor divider to Channel1 multi-phase switching node.                                                                                                                                                                                                                                                                                                      |

| 5      | VR_RDY          | Multi-phase s | VR ready. Open drain output set free after SS has finished in multi-<br>phase and pulled low when triggering any protection on the multi-phase<br>section. Pull up to a voltage lower than 3.3 V (typ.), if not used it can be<br>left floating.                                                                                                                              |

| 6      | CS3P            | _             | Channel 3 current sense positive input. Connect through an R-C filter to the phase-side of the channel 3 inductor. When working at 2-phase, short to the regulated voltage.                                                                                                                                                                                                   |

| 7      | CS3N            |               | Channel 3 current sense negative input. Connect through an Rg resistor to the output-side of the channel inductor. When working at 2-phase, still connect through Rg to CS3P and then to the regulated voltage. Filter the output-side of Rg with 100 nF (typ.) to GND.                                                                                                       |

Pin description (continued) Table 2.

| Pin# | Name          |                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|---------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8    | CS2N          | no                     | Channel 2 current sense negative input. Connect through an Rg resistor to the output-side of the channel inductor. Filter the output-side of Rg with 100 nF (typ.) to GND.                                                                                                                                                                                                                                                                                                                                                      |

| 9    | CS2P          | Multi-phase section    | Channel 2 current sense positive input. Connect through an R-C filter to the phase-side of the channel 2 inductor.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10   | CS1P          | llti-phas              | Channel 1 current sense positive input. Connect through an R-C filter to the phase-side of the channel 1 inductor.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11   | CS1N          | M                      | Channel 1 current sense negative input. Connect through an Rg resistor to the output-side of the channel inductor. Filter the output-side of Rg with 100 nF (typ.) to GND.                                                                                                                                                                                                                                                                                                                                                      |

| 12   | SOSC          | SIngle-phase section   | Oscillator pin.  It allows the programming of the switching frequency F <sub>SSW</sub> for the single-phase section. The pin is internally set to 1.02 V, frequency for single-phase is programmed according to the resistor connected to GND or VCC with a gain of 11.5 kHz/µA. Leaving the pin floating programs a switching frequency of 230 kHz. See <i>Section 10</i> for details.                                                                                                                                         |

| 13   | ТМ            | Multi-phase<br>section | Thermal monitor sensor. Connect with the proper network embedding NTC to the multi-phase power section. The IC senses the power section temperature and uses the information to define the VR_HOT signal and temperature zone register. By programming proper TCOMP gain, the IC also implements load-line thermal compensation for the multi-phase section. In JMode, the pin disables the single-phase section if shorted to GND. Pull up to VCC5 with 1 k $\Omega$ to disable the thermal sensor. See Section 6 for details. |

| 14   | SPWM /<br>SEN | Single-phase section   | PWM output. Connect to single-phase external driver PWM input. During normal operations the device is able to manage HiZ status by setting and holding the SPWM pin to a fixed voltage defined by PWMx strapping. Connect to VCC5 with 1 k $\Omega$ to disable the single-phase section.                                                                                                                                                                                                                                        |

| 15   | VR_HOT        |                        | Voltage regulator HOT.  Open drain output, this is an alarm signal asserted by the controller when the temperature sensed through the TM pin exceeds TMAX (active low). See <i>Section 6</i> for details.                                                                                                                                                                                                                                                                                                                       |

| 16   | TCOMP         | Multi-phase section    | Thermal monitor sensor gain.  Connect the proper resistor divider between VCC5 and GND to define the gain to apply to the signal sensed by TM to implement thermal compensation for the multi-phase section. Short to GND to disable temperature compensation (but not thermal monitor). See Section 6 for details.                                                                                                                                                                                                             |

| 17   | SCSP          | ohase                  | Single-phase section current sense positive input. Connect through an R-C filter to the phase-side of the channel 1 inductor.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18   | SCSN          | Single-phase section   | Single-phase section current sense negative input. Connect through an Rg resistor to the output-side of the channel inductor. Filter the output-side of Rg with 100 nF (typ.) to GND.                                                                                                                                                                                                                                                                                                                                           |

10/51 Doc ID 023240 Rev 1

Table 2. Pin description (continued)

| Pin# | Name             |                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                  |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 19   | I <sub>LIM</sub> |                        | Multi-phase section current limit.  A current proportional to the multi-phase load current is sourced from this pin. Connect through a resistor R <sub>LIM</sub> to GND. When the pin voltage reaches 2.5 V, the overcurrent protection is set and the IC latches. Filter through C <sub>LIM</sub> to GND to delay OC intervention.                                                                                                                                                                     |

| 20   | SRGND            | on                     | Remote buffer ground sense.  Connect to the negative side of the single-phase load to perform remote sense.                                                                                                                                                                                                                                                                                                                                                                                             |

| 21   | SFBR             | Single-phase section   | Remote buffer positive sense.  Connect to the positive side of the single-phase load to perform remote sense.                                                                                                                                                                                                                                                                                                                                                                                           |

| 22   | SVSEN            | Single-p               | Remote buffer output. Output voltage monitor, manages OV and UV protection. Connect with a resistor $R_{SFB}$ // $(R_{SI}$ - $C_{SI})$ to SFB.                                                                                                                                                                                                                                                                                                                                                          |

| 23   | SFB              |                        | Error amplifier inverting input. Connect with a resistor $R_{SFB}$ // $(R_{SI} - C_{SI})$ to SVSEN and with an $(R_{SF} - C_{SF})$ // $C_{SH}$ to SCOMP.                                                                                                                                                                                                                                                                                                                                                |

| 24   | SCOMP            |                        | Error amplifier output. Connect with an (R $_{\rm SF}$ - C $_{\rm SF}$ )// C $_{\rm SH}$ to SFB. The device cannot be disabled by pulling low this pin.                                                                                                                                                                                                                                                                                                                                                 |

| 25   | IMAX             | Pin-strapping          | Connect a resistor divider to GND/VCC5 in order to define the IMAX register. JMode and BOOT voltage can be controlled through this pin. See <i>Table 6</i> and <i>Section 6</i> for details.                                                                                                                                                                                                                                                                                                            |

| 26   | SMDATA           | (S                     | PMBus data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 27   | SMAL#            | PMBus                  | PMBus alert.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 28   | SMCLOCK          | ď                      | PMBus clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 29   | ADDR             | Pin-strapping          | Connect a resistor divider to GND/VCC5 in order to define the IC address, to define the GDC and DPM thresholds and to control the droop function on multi-phase. See <i>Table 6</i> and <i>Section 6</i> for details.                                                                                                                                                                                                                                                                                   |

| 30   | osc              | Multi-phase<br>section | Oscillator pin. It allows the programming of the switching frequency F <sub>SW</sub> for the multiphase section. The pin is internally set to 1.02 V, the frequency for multiphase is programmed according to the resistor connected to GND or VCC with a gain of 10 kHz/µA. Leaving the pin floating programs a switching frequency of 200 kHz per phase. The effective frequency observable on the load results being multiplied by the number of active phases N. See <i>Section 10</i> for details. |

| 31   | VIN              |                        | Input voltage monitor. Connect to input voltage monitor point through a divider $R_{UP}$ / $R_{DOWN}$ to perform VIN sense through PMBus ( $R_{UP}$ = 118.5 k $\Omega$ ; $R_{DOWN}$ = 10 k $\Omega$ typ.). See $Section~12.3$ for details.                                                                                                                                                                                                                                                              |

Table 2. Pin description (continued)

| Pin# | Name           |                     | Function                                                                                                                                                                                                                                                                                           |

|------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32   | EN             |                     | VTT level sensitive enable pin (3.3 V compatible). Pull low to disable the device, pull up above the turn-on threshold to enable the controller.                                                                                                                                                   |

| 33   | SVCLK          | Sſ                  | Serial clock.                                                                                                                                                                                                                                                                                      |

| 34   | ALERT#         | SVI BUS             | Alert.                                                                                                                                                                                                                                                                                             |

| 35   | SVDATA         | S)                  | Serial data.                                                                                                                                                                                                                                                                                       |

| 36   | VCC5           |                     | Main IC power supply. Operative voltage is 5 V ±5%. Filter with 1 μF MLCC to GND (typ.).                                                                                                                                                                                                           |

| 37   | GDC            |                     | Gate drive control pin. Used for efficiency optimization, see <i>Section 9</i> for details. If not used, it can be left floating. Always filter with 1 $\mu$ F MLCC to GND.                                                                                                                        |

| 38   | VDRV           |                     | Driving voltage for external drivers.  Connect to the selected voltage rail to drive the external MOSFET when in maximum power conditions. IC switches GDC voltage between VDRV and VCC5 to implement efficiency optimization according to selected strategies.                                    |

| 39   | COMP /<br>ADDR |                     | Error amplifier output. Connect with an $(R_F - C_F)$ // $C_P$ to FB. The device cannot be disabled by pulling low this pin. Connect $R_{COMP}$ to GND to extend PMBus addressing range (see <i>Table 6</i> ).                                                                                     |

| 40   | FB             |                     | Error amplifier inverting input. Connect with a resistor $R_{FB}$ // $(R_I$ - $C_I$ ) to VSEN and with an $(R_F$ - $C_F$ )// $C_P$ to COMP.                                                                                                                                                        |

| 41   | VSEN           |                     | Output voltage monitor, manages OV and UV protection. Connect to the positive side of the load to perform remote sense.                                                                                                                                                                            |

| 42   | FBR            | Multi-phase section | Remote buffer positive sense.  Connect to the positive side of the multi-phase load to perform remote sense.                                                                                                                                                                                       |

| 43   | LTB            | pha                 | Load transient boost technology® input pin. See Section 11.2 for details.                                                                                                                                                                                                                          |

| 44   | RGND           | Multi-              | Remote ground sense. Connect to the negative side of the multi-phase load to perform remote sense.                                                                                                                                                                                                 |

| 45   | REF            |                     | The reference used for the multi-phase section regulation is available on this pin with -125 mV offset. Connect through an $\rm R_{REF}\text{-}C_{REF}$ to GND to optimize DVID transitions. Connect through $\rm R_{OS}$ resistor to FB pin to implement small positive offset to the regulation. |

| 46   | IMON           |                     | Current monitor output. A current proportional to the multi-phase load current is sourced from this pin. Connect through a resistor $R_{MON}$ to GND. The information available on this pin is used for the current reporting and DPM. The pin can be filtered through $C_{IMON}$ to GND.          |

12/51 Doc ID 023240 Rev 1

Table 2. Pin description (continued)

| Pin# | Name    |                        | Function                                                                                                                                                                                                                                          |

|------|---------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47   | SVR_RDY | Single-phase section   | VR ready.  Open drain output set free after SS has finished in single-phase section and pulled low when triggering any protection for the single-phase section.Pull up to a voltage lower than 3.3 V (typ.), if not used it can be left floating. |

| 48   | ENDRV   | Multi-phase<br>section | Enable driver.  CMOS output driven high when the IC commands the drivers. Used in conjunction with the HiZ window on the PWMx pins to optimize the multi-phase section overall efficiency. Connect directly to external driver enable pin.        |

| PAD  | GND     |                        | GND connection. All internal references and logic are referenced to this pin. Filter to VCC with proper MLCC capacitor and connect to the PCB GND plane.                                                                                          |

# 2.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                                                 | Value      | Unit |

|-------------------|---------------------------------------------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient (device soldered on 2s2p PC board) | 40         | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction to case                                       | 1          | °C/W |

| T <sub>MAX</sub>  | Maximum junction temperature                                              | 150        | °C   |

| T <sub>STG</sub>  | Storage temperature range                                                 | -40 to 150 | °C   |

| T <sub>J</sub>    | Junction temperature range                                                | 0 to 125   | °C   |

# 3 Electrical specifications

# 3.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol                                                                            | Parameter | Value       | Unit |

|-----------------------------------------------------------------------------------|-----------|-------------|------|

| VDRV, GDC                                                                         | to GND    | -0.3 to 14  | V    |

| VCC5, TM, STM, SPWM, PWMx,<br>SENDRV, ENDRV, SCOMP, COMP,<br>SMDATA, SMAL#, SMCLK | to GND    | -0.3 to 7   | V    |

| All other pins                                                                    | to GND    | -0.3 to 3.6 | V    |

### 3.2 Electrical characteristics

$V_{CC5}$  = 5 V ± 5%,  $T_J$  = 0 °C to 70 °C unless otherwise specified.

Table 5. Electrical characteristics

| Symbol               | Parameter                         | Min.                                                                            | Тур. | Max. | Unit |     |

|----------------------|-----------------------------------|---------------------------------------------------------------------------------|------|------|------|-----|

| Supply curre         | ent and power-on                  |                                                                                 |      |      |      |     |

| 1                    | VCCE cumply current               | EN = high                                                                       |      | 28   |      | mA  |

| I <sub>VCC5</sub>    | VCC5 supply current               | EN = low                                                                        |      | 22   |      | mA  |

| 11//1.0              | VCC5 turn-ON                      | VCC5 rising                                                                     |      |      | 4.1  | V   |

| UVLO <sub>VCC5</sub> | VCC5 turn-OFF                     | VCC5 falling                                                                    | 3    |      |      | V   |

| 11//1.0              | VDRV turn-ON                      | VDRV rising                                                                     |      |      | 6    | V   |

| UVLO <sub>VDRV</sub> | VDRV turn-OFF                     | VDRV falling                                                                    | 3    |      | 4.1  | V   |

| UVLO <sub>VIN</sub>  | VIN turn-ON                       | VIN rising, $R_{UP} = 118.5 \text{ k}\Omega$ ; $R_{DOWN} = 10 \text{ k}\Omega$  |      |      | 6    | V   |

|                      | VIN turn-OFF                      | VIN falling, $R_{UP} = 118.5 \text{ k}\Omega$ ; $R_{DOWN} = 10 \text{ k}\Omega$ | 3    |      | 4.1  | ٧   |

| Oscillator, S        | oft-start and enable              |                                                                                 |      |      |      |     |

|                      | Main oscillator accuracy          | OSC = open                                                                      | 170  | 200  | 230  | kHz |

| F <sub>SW</sub>      | Oscillator adjustability          | $R_{OSC} = 47 \text{ k}\Omega \text{ to GND}$                                   | 378  | 420  | 462  | kHz |

| F                    | Main oscillator accuracy          | SOSC = open                                                                     | 195  | 230  | 265  | kHz |

| F <sub>SSW</sub>     | Oscillator adjustability          | $R_{SOSC} = 47 \text{ k}\Omega \text{ to GND}$                                  | 432  | 480  | 528  | kHz |

| $\Delta V_{OSC}$     | PWM ramp amplitude <sup>(1)</sup> |                                                                                 |      | 1.5  |      | V   |

| FAULT                | Voltage at pin OSC,<br>SSOSC      | Latch active for related section                                                | 3    |      |      | V   |

Table 5. Electrical characteristics (continued)

| Symbol            | ol Parameter Test conditions       |                                                                                                                                    | Min.  | Тур. | Max. | Unit  |

|-------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

|                   |                                    | Vboot > 0, from pin-strapping; multi-<br>phase section                                                                             | 2.5   |      |      | mV/μS |

| SOFT-<br>START    | SS time                            | Vboot > 0, from pin-strapping; single-phase section                                                                                | 1.25  |      |      | mV/μS |

|                   |                                    | Vboot > 0, from pin-strapping;<br>single-phase section, JMode ON                                                                   | 2.5   |      |      | mV/μS |

|                   | Turn-ON                            | V <sub>EN</sub> rising                                                                                                             |       |      | 0.6  | ٧     |

| EN                | Turn-OFF                           | V <sub>EN</sub> falling                                                                                                            | 0.4   |      |      | ٧     |

|                   | Leakage current                    |                                                                                                                                    |       | 1    |      | μΑ    |

| SVI serial bu     | ıs                                 |                                                                                                                                    |       |      |      |       |

| SVCLCK,           | Input high                         |                                                                                                                                    | 0.65  |      |      | ٧     |

| SVDATA            | Input low                          |                                                                                                                                    |       |      | 0.45 | ٧     |

| SVDATA,<br>ALERT# | Voltage low (ACK)                  | I <sub>SINK</sub> = -5 mA                                                                                                          |       |      | 50   | mV    |

| PMBus             |                                    |                                                                                                                                    |       |      |      |       |

| SMDATA,           | Input high                         |                                                                                                                                    | 1.75  |      |      | ٧     |

| SMCLK             | Input low                          |                                                                                                                                    |       |      | 1.45 | ٧     |

| SMAL#             | Voltage low                        | I <sub>SINK</sub> = -4 mA                                                                                                          |       |      | 13   | Ω     |

| Reference a       | nd DAC                             |                                                                                                                                    |       |      |      | •     |

| K <sub>VID</sub>  | V <sub>OUT</sub> accuracy (MPhase) | FBR to $V_{CORE}$ ; RGND to $GND_{CORE}$ $VID>1.000 V$                                                                             | -0.5  |      | 0.5  | %     |

| K <sub>SVID</sub> | V <sub>OUT</sub> accuracy (SPhase) | JMODE=OFF; V <sub>UNCORE</sub> /V <sub>CORE</sub><br>SFBR to V <sub>UNCORE</sub> ; SRGND to<br>GND <sub>UNCORE</sub> ; VID>1.000 V | 0.49  |      | 0.51 |       |

| 01.5              |                                    | JMODE=ON; SFBR to V <sub>UNCORE</sub> ;<br>SRGND to GND <sub>UNCORE</sub> ;                                                        | -5    |      | 5    | mV    |

|                   | LL accuracy (MPhase)               | $I_{INFOx}$ = 0 μA; N=3; $R_{G}$ =866 $Ω$                                                                                          | -2.25 |      | 1.75 | μΑ    |

| $\Delta_{DROOP}$  | 0 to full load                     | $I_{INFOx}$ = 20 μA; N=3; R <sub>G</sub> =866 Ω                                                                                    | -2.5  |      | 2.5  | μΑ    |

| k <sub>IMON</sub> | IMON accuracy (MPhase)             | $I_{INFOx} = 0$ ; N=3; R <sub>G</sub> =866 $\Omega$                                                                                | 0     |      | 0.75 | μΑ    |

|                   | INION accuracy (MFHase)            | $I_{INFOx}$ = 20 μA; N=3; R <sub>G</sub> =866 Ω                                                                                    | -1    |      | 1    | μΑ    |

| A <sub>0</sub>    | EA DC gain <sup>(1)</sup>          |                                                                                                                                    |       | 100  |      | dB    |

| SR                | Slew-rate <sup>(1)</sup>           | COMP to SGND = 10 pF                                                                                                               |       | 20   |      | V/µs  |

| DVVD              | Slew-rate fast                     | Multi-phase section                                                                                                                | 10    |      |      | mV/μs |

| DVID              | Slew-rate slow                     | iviuiu-priase seciion                                                                                                              | 2.5   |      |      | mV/μs |

| רואים             | Slew-rate fast                     | Single phase section                                                                                                               | 5     |      |      | mV/μs |

| DVID              | Slew-rate slow                     | Single-phase section                                                                                                               | 1.25  |      |      | mV/μs |

Table 5. Electrical characteristics (continued)

| Symbol                  | Parameter Test conditions       |                                           | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------------------|-------------------------------------------|------|------|------|------|

| IMON ADC                | GetReg(15h)                     | - V(IMON) = 0.992 V                       |      | CC   |      | Hex  |

| IMON ADC                | Accuracy                        | - V(IIVIOIN) = 0.992 V                    | C0   |      | CF   | Hex  |

| PWM output              | s and ENDRV                     |                                           |      |      |      |      |

| PWMx,                   | Output high                     | I = 1 mA                                  |      | 5    |      | V    |

| SPWM                    | Output low                      | I = -1 mA                                 |      |      | 0.2  | V    |

| I <sub>PWM1</sub>       |                                 | Sourced from pin, EN=0                    |      | 10   |      | μΑ   |

| I <sub>PWM2</sub>       | Test current                    | Sourced from pin, EN=0                    |      | 0    |      | μΑ   |

| I <sub>PWM3, SPWM</sub> |                                 | Sourced from pin, EN=0                    |      | -10  |      | μΑ   |

| ENDRV                   | Voltage low                     | I <sub>ENDRV</sub> = -4 mA                |      |      | 0.4  | V    |

| Protection (b           | ooth sections)                  |                                           |      |      |      |      |

| OVP                     | Overvoltage protection          | rotection VSEN rising; wrt Ref.           |      |      | 200  | mV   |

| UVP                     | Undervoltage protection         | VSEN falling; wrt Ref; Ref > 500 mV       | -525 |      | -375 | mV   |

| FBR DISC                | FB disconnection                | V <sub>CS-</sub> rising, above VSEN/SVSEN | 650  | 700  | 750  | mV   |

| FBG DISC                | FBG disconnection               | FBR rising wrt VID                        | 950  | 1000 | 1050 | mV   |

| VR_RDY,<br>SVR_RDY      | Voltage low                     | I <sub>SINK</sub> = -4 mA                 |      |      | 0.4  | ٧    |

| V <sub>OC_TOT</sub>     | OC threshold                    | V <sub>ILIM</sub> rising, to GND          | 2.45 | 2.5  | 2.55 | V    |

| I <sub>OC_TH</sub>      | Constant current <sup>(1)</sup> | MPhase only                               |      | 35   |      | μΑ   |

| VR_HOT                  | Voltage low                     | I <sub>SINK</sub> = -4 mA                 |      |      | 13   | Ω    |

| Gate drive c            | ontrol                          |                                           |      |      |      |      |

|                         | Max. current <sup>(1)</sup>     | Any PS                                    |      | 200  |      | mA   |

| GDC                     | Impedance                       | PS00h (GDC = VDRV)                        |      | 6    |      | Ω    |

|                         | Impedance                       | > PS00h (GDC = VCC5)                      |      | 6    |      | Ω    |

<sup>1.</sup> Guaranteed by design, not subject to test.

# 4 Device configuration and pin-strapping tables

The L6759D is fully compliant with Intel® VR12/IMVP7 SVID protocol Rev1.5, document # 456098. To guarantee proper device and CPU operations, refer to this document for bus design and layout guidelines. Different platforms may require different pull-up impedance on the SVI bus. Impedance matching and spacing between SVDATA, SVCLK, and ALERT# must be followed.

### 4.1 JMode

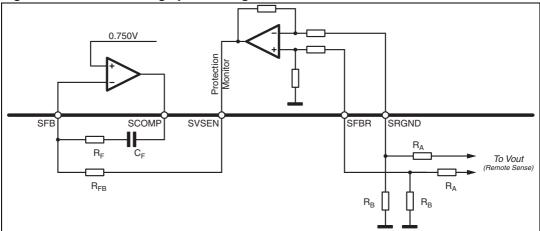

When enabled, single-phase is an independent regulator with 0.75 V fixed reference (load-line disabled - TM can be used as enable for the single-phase).

Output voltage higher than the internal reference may be achieved by adding a proper resistor divider (RA, RB - see *Figure 5*). To maintain precision in output voltage regulation, it is recommended to provide both SFBR and SRGND with the same divider.

#### **Equation 1**

$$V_{OUT} = 0.750V \cdot \frac{RA + RB}{RB}$$

Figure 5. JMode: voltage positioning

## 4.2 Programming HiZ level

The L6759D is able to manage different levels for HiZ on PWMx guaranteeing flexibility in driving different external drivers as well as DrMOS ICs.

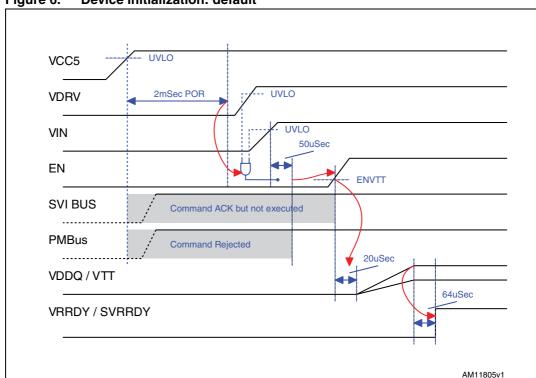

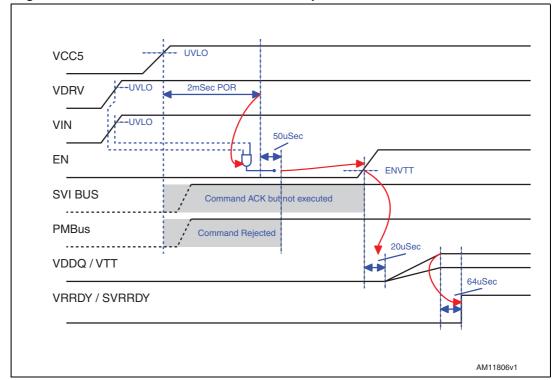

Once VCC5, VDRV, and VIN voltages are above the respective UVLO (undervoltage lockout) thresholds (see *Figure 6*), the device uses PWM1 and PWM2 to detect the driver/DrMOS connected in order to program the suitable Hiz level of PWMx signals. During regulation, the Hiz level is used to force the external MOSFETs into high impedance state.

- PWM1 sources a constant 10 μA current, if its voltage results higher than 2.8 V, the HiZ level used during the regulation is 1.4 V, if lower, PWM2 information is used.

- PWM2 is kept in HiZ, if its voltage results higher than 2 V, the HiZ level used during the regulation is 2 V, if lower, 1.6 V.

An external resistor divider can be placed on PWM1 and PWM2 to force the detection of the correct HiZ level. They must be designed considering the external driver/DrMOS selected and the HiZ level requested.

Table 6. Pin-strapping (1)

| Rdown | Rup  | IMAX                    |             |           | ADDR     |         |       |       |               |     |    |

|-------|------|-------------------------|-------------|-----------|----------|---------|-------|-------|---------------|-----|----|

| [kΩ]  | [kΩ] | IMAX [A] <sup>(2)</sup> | JMode       | VВООТ     | SVI ADDR | VFDE    | DPM12 | DPM23 | Droop<br>core |     |    |

| 10    | 1.5  |                         | ON          | 1.500 V   |          |         | 12 A  | 24 A  | ON            |     |    |

| 10    | 2.7  | N · 25 + 56             | ON          | 1.350 V   |          |         | 12 A  | 24 A  | OFF           |     |    |

| 22    | 6.8  | 11. 25 + 50             | OFF         | 1.500 V   |          |         | 10 A  | 20 A  | ON            |     |    |

| 10    | 3.6  |                         | OFF         | 1.350 V   |          | OFF     | 10 A  | 20 A  | OFF           |     |    |

| 27    | 11   |                         | ON          | 1.500 V   |          | OFF     | 8 A   | 18 A  | ON            |     |    |

| 12    | 5.6  | N · 25 + 48             | ON          | 1.350 V   |          |         | O A   | 10 A  | OFF           |     |    |

| 82    | 43   | 111 25 + 40             | OFF         | 1.500 V   |          |         | OFF   | OFF   | ON            |     |    |

| 13    | 7.5  |                         | OFF         | 1.350 V   | 0100b    |         | OIT   | OFF   | OFF           |     |    |

| 56    | 36   | N · 25 + 40             |             | ON        | 1.500 V  | 01000   |       | 12 A  | 24 A          | ON  |    |

| 18    | 13   |                         | ON          | 1.350 V   |          |         | 12 A  | 24 A  | OFF           |     |    |

| 15    | 12   |                         | OFF         | 1.500 V   |          |         | 10 A  | 20 A  | ON            |     |    |

| 18    | 16   |                         | OFF         | 1.350 V   |          | ON      | 10 A  | 20 A  | OFF           |     |    |

| 15    | 14.7 |                         | ON          | 1.500 V   |          | ON      | 8 A   | 18 A  | ON            |     |    |

| 10    | 11   | N · 25 + 32             | ON          | 1.350 V   |          |         | O A   | 10 A  | OFF           |     |    |

| 18    | 22   | N · 20 + 32             | N · 20 + 32 | N 20 + 32 | OFF      | 1.500 V |       |       | OFF           | OFF | ON |

| 56    | 75   |                         | OFF         | 1.350 V   |          |         | OFF   | OFF.  | OFF           |     |    |

Table 6. Pin-strapping (1) (continued)

| Rdown | Rup  |                         | IMAX        |         | ADDR     |      |                    |                    |                    |     |

|-------|------|-------------------------|-------------|---------|----------|------|--------------------|--------------------|--------------------|-----|

| [kΩ]  | [kΩ] | IMAX [A] <sup>(2)</sup> | JMode       | VBOOT   | SVI ADDR | VFDE | DPM12              | DPM23              | Droop<br>core      |     |

| 10    | 15   |                         |             | ON      | 1.500 V  |      |                    | 12 A               | 24 A               | ON  |

| 12    | 20   | N · 25 + 24             | ON          | 1.350 V |          |      | 12.7               |                    | OFF                |     |

| 12    | 22.6 | 111 25 + 24             | OFF         | 1.500 V |          | OFF  | 10 A               | 20 A               | ON                 |     |

| 39    | 82   |                         | OFF         | 1.350 V |          |      |                    |                    | OFF                |     |

| 47    | 110  |                         | ON          | 1.500 V |          | OFF  | 8 A                | 18 A               | ON                 |     |

| 10    | 27   | N · 25 + 16             | N 25   16   | ON      | 1.350 V  |      |                    | 0 7                | 10 A               | OFF |

| 22    | 68   |                         | N · 25 + 10 | OFF     | 1.500 V  |      |                    | OFF <sup>(4)</sup> | OFF <sup>(5)</sup> | ON  |

| 10    | 36   |                         | OFF         | 1.350 V | 0010b    |      | OI I V             | OI I V             | OFF                |     |

| 18    | 75   | N · 25 + 8              | ON          | 1.500 V | 00100    |      | 12 A               | 24 A               | ON                 |     |

| 15    | 75   |                         |             | ON      | 1.350 V  |      |                    | 12 A               | 24 A               | OFF |

| 10    | 59   |                         | OFF         | 1.500 V |          |      | 10 A               | 20 A               | ON                 |     |

| 10    | 75   |                         | OFF         | 1.350 V |          | ON   | 10 A               | 20 A               | OFF                |     |

| 10    | 100  | N · 25                  | N OF        | ON      | 1.500 V  |      | ON                 | 8 A                | 18 A               | ON  |

| 10    | 150  |                         |             | ON      | 1.350 V  |      |                    | O A                | 10 A               | OFF |

| 10    | 220  |                         | OFF         | 1.500 V |          |      | OFF <sup>(4)</sup> | OFF <sup>(5)</sup> | ON                 |     |

| 10    | Open |                         | 011         | 1.350 V |          |      | 011 . /            | OI I · · /         | OFF                |     |

- 1. Suggested values, divider needs to be connected between VCC5 pin and GND.

- $2. \quad \ \ N \ is \ the \ number \ of \ phase \ programmed \ for \ the \ multi-phase \ section.$

- 3. Address for multi-phase. Single-phase not accessible.

- 4. Transition between 1Phase and 2Phase operation is set to 12 A but disabled in PS00h (minimum phase number in PS00h is 2).

- 5. Dynamic phase management disabled, IC always working at maximum possible number of phases except when in >PS00h when transitioning between 1Phase and 2Phase at 12 A.

Table 7. PMBus address definition

| SVI address (see <i>Table 6</i> ) | COMP to GND | PMBus address |

|-----------------------------------|-------------|---------------|

|                                   | 4.99 k      | EEh           |

| 0100b                             | 14.99 k     | EAh           |

| 01005                             | 24.99 k     | E6h           |

|                                   | Open        | E2h           |

|                                   | 4.99 k      | ECh           |

| 0010b                             | 14.99 k     | E8h           |

| 00100                             | 24.99 k     | E4h           |

|                                   | Open        | E0h           |

## 5 Device description and operation

The L6759D is a programmable 2/3-phase PWM controller that provides complete control logic and protection to realize a high performance step-down DC-DC voltage regulator optimized for advanced DDR memory power supply. The device features 2<sup>nd</sup> generation LTB Technology<sup>TM</sup>: through a load transient detector, it is able to turn on simultaneously all the phases. This allows the output voltage deviation to be minimized and, in turn, to minimize system costs by providing the fastest response to a load transition.

The L6759D implements current reading across the inductor in fully differential mode. A sense resistor in series to the inductor can be also considered to improve reading precision. The current information read corrects the PWM output in order to equalize the average current carried by each phase.

The controller supports VR12 specifications featuring 25 MHz SVI bus and all the required registers. The platform may program the defaults for these registers through dedicated pin-strapping.

A complete set of protection is available: overvoltage, undervoltage, overcurrent (per-phase and total) and feedback disconnection guarantee the load to be safe under all conditions.

Special power management features like DPM, VFDE and GDC modify the phase number, gate driving voltage and switching frequency to optimize the efficiency over the load range.

The L6759D is available in VFQFPN48 with a 6x6 mm body package.

### 5.1 Device initialization

Figure 6. Device initialization: default

Figure 7. Device initialization: alternative sequence

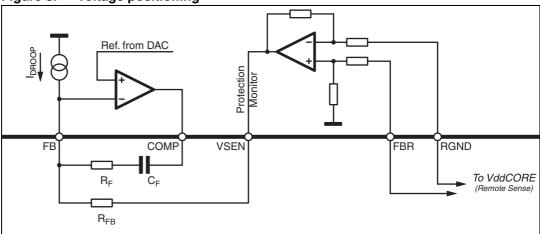

## 6 Output voltage positioning

Output voltage positioning is performed by selecting the controller operative-mode for the two sections and by programming the droop function effect (see *Figure 8*). The controller reads the current delivered by each section by monitoring the voltage drop across the DCR inductors. The current ( $I_{DROOP} / I_{SDROOP}$ ) sourced from the FB / SFB pins, directly proportional to the read current, causes the related section output voltage to vary according to the external  $R_{FB} / R_{SFB}$  resistor, so implementing the desired load-line effect.

The L6759D embeds a dual remote-sense buffer to sense remotely the regulated voltage of each section without any additional external components. In this way, the output voltage programmed is regulated, compensating for board and socket losses. Keeping the sense traces parallel and guarded by a power plane results in common mode coupling for any picked-up noise.

Figure 8. Voltage positioning

## 6.1 Multi-phase section - phase # programming

The multi-phase section implements a flexible 2 to 3 interleaved-phase converter. To program the desired number of phases, pull up with a 1 k $\Omega$  resistor to VCC5 the PWMx signal that is not required to be used.

Caution:

For the disabled phase(s), the current reading pins need to be properly connected to avoid errors in current-sharing and voltage-positioning: CSxP needs to be connected to the regulated output voltage while CSxN needs to be connected to CSxP through the same R<sub>G</sub> resistor used for the active phases. See *Figure 2* for details on 2-phase connections.

# 6.2 Multi-phase section - current reading and current sharing loop

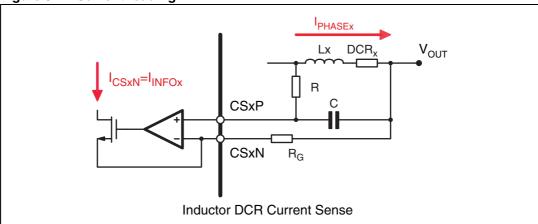

The L6759D embeds a flexible, fully-differential current sense circuitry that is able to read across inductor parasitic resistance or across a sense resistor placed in series to the inductor element. The fully-differential current reading rejects noise and allows the placing of the sensing element in different locations without affecting the measurement's accuracy. The

trans-conductance ratio is issued by the external resistor  $R_G$  placed outside the chip between the CSxN pin toward the reading points. The current sense circuit always tracks the current information, the CSxP pin is used as a reference keeping the CSxN pin to this voltage. To correctly reproduce the inductor current, an R-C filtering network must be introduced in parallel to the sensing element. The current that flows from the CSxN pin is then given by the following equation (see *Figure 9*):

#### **Equation 2**

$$I_{CSxN} = \frac{DCR}{R_G} \cdot \frac{1 + s \cdot L / DCR}{1 + s \cdot R \cdot C} \cdot I_{PHASEx}$$

Considering the matching of the time constant between the inductor and the R-C filter applied (time constant mismatches cause the introduction of poles into the current reading network causing instability. In addition, it is also important for the load transient response and to let the system show resistive equivalent output impedance) it results:

#### **Equation 3**

$$\frac{L}{\text{DCR}} = \, \text{R} \cdot \, \, \, \text{C} \quad \Rightarrow \quad \text{I}_{\text{CSxN}} = \frac{\text{R}_{\text{L}}}{\text{R}_{\text{G}}} \cdot \, \, \text{I}_{\text{PHASEx}} = \, \text{I}_{\text{INFOx}}$$

Figure 9. Current reading

The current read through the CSxP / CSxN pairs is converted into a current  $I_{INFOx}$  proportional to the current delivered by each phase and the information about the average current  $I_{AVG} = \Sigma I_{INFOx}$  / N is internally built into the device (N is the number of working phases). The error between the read current  $I_{INFOx}$  and the reference  $I_{AVG}$  is then converted into a voltage that, with a proper gain, is used to adjust the duty cycle whose dominant value is set by the voltage error amplifier in order to equalize the current carried by each phase.

# 6.3 Multi-phase section - defining load-line

The L6759D introduces a dependence of the output voltage on the load current recovering part of the drop due to the output capacitor ESR in the load transient. Introducing a dependence of the output voltage on the load current, a static error, proportional to the output current, causes the output voltage to vary according to the sensed current.

577

Figure 9 shows the current sense circuit used to implement the load-line. The current flowing across the inductor(s) is read through the R-C filter across the CSxP and CSxN pins.  $R_G$  programs a trans-conductance gain and generates a current  $I_{CSx}$  proportional to the current of the phase. The sum of the  $I_{CSx}$  current, with proper gain eventually adjusted by the PMBus commands, is then sourced by the FB pin ( $I_{DROOP}$ ).  $R_{FB}$  gives the final gain to program the desired load-line slope (Figure 8).

Time constant matching between the inductor (L / DCR) and the current reading filter (RC) is required to implement a real equivalent output impedance of the system, so voiding over and/or undershoot of the output voltage as a consequence of a load transient. The output voltage characteristic vs. load current is then given by:

#### **Equation 4**

$$V_{OUT} = VID - R_{FB} \cdot I_{DROOP} = VID - R_{FB} \cdot \frac{DCR}{R_{G}} \cdot I_{OUT} = VID - R_{LL} \cdot I_{OUT}$$

where  $R_{LL}$  is the resulting load-line resistance implemented by the multi-phase section.

The R<sub>FB</sub> resistor can be then designed according to the R<sub>LL</sub> specifications as follows:

#### **Equation 5**

$$R_{FB} = R_{LL} \cdot \frac{R_{G}}{DCR}$$

### 6.4 Multi-phase section - IMON information

The voltage on the IMON pin contains the analog information related to the current delivered by the VR and it is digitized for VR12 current reporting. The pin sources a copy of the droop current:

#### **Equation 6**

$$I_{IMON} = I_{DROOP} = \frac{DCR}{R_G} \cdot I_{OUT}$$

See Section 6 for details about current reading.

The lout register contains analog-to-digital conversion of the voltage present on the IMON pin considering the following relationships:

- a) V<sub>IMON</sub> = I<sub>IMON</sub> · R<sub>IMON</sub> where R<sub>IMON</sub> is the resistor connected between IMON and GND.

- V<sub>IMON</sub>=1.24 V corresponds to IMAX. R<sub>IMON</sub> is designed according to this relationship.

Note: