Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 38 V, 500 mA synchronous step-down switching regulator with 30 µA quiescent current

Datasheet - production data

#### **Features**

- 0.5 A DC output current

- 4 V to 38 V operating input voltage

- Low consumption mode or low noise mode

- 30 μA I<sub>Q</sub> at light-load (LCM V<sub>OUT</sub> = 3.3 V)

- 8 μA <sub>IQ-SHTDWN</sub>

- Output voltage adjustable from 0.85 V to V<sub>IN</sub>

- Adjustable f<sub>SW</sub> (250 kHz 2 MHz)

- Embedded output voltage supervisor

- Synchronization

- Adjustable soft-start time

- Internal current limiting

- Overvoltage protection

- Output voltage sequencing

- Peak current mode architecture

- R<sub>DSON HS</sub> = 360 mΩ, R<sub>DSON LS</sub> = 150 mΩ

- Thermal shutdown

## **Applications**

- Designed for 12 V and 24 V buses

- Programmable logic controllers (PLCs)

- Decentralized intelligent nodes

- Sensors and low noise applications (LNM)

### **Description**

The L6985F is a step-down monolithic switching regulator able to deliver up to 0.5 A DC. The output voltage adjustability ranges from 0.85V to VIN. Thanks to the P-channel MOSFET high-side power element, the device features 100% of the duty cycle operation. The wide input voltage range meets the specification for the 5 V, 12 V and 24 V power supplies. The "Low Consumption Mode" (LCM) is designed for applications active during the idle mode, so it maximizes the efficiency at the light-load with the controlled output voltage ripple. The "Low Noise Mode" (LNM) makes the switching frequency constant overload current range, meeting the low noise application specification. The output voltage supervisor manages the reset phase for any digital load (µC, FPGA). The RST open collector output can also implement output voltage sequencing during the power-up phase. The synchronous rectification, designed for high efficiency at the medium - heavy load, and the high switching frequency capability make the size of the application compact. Pulse-by-pulse current sensing on both power elements implements effective constant current protection.

Contents L6985F

## **Contents**

| 1 | App  | lication schematic                 | 4  |

|---|------|------------------------------------|----|

| 2 | Pin  | settings                           | 5  |

|   | 2.1  | Pin connection                     | 5  |

|   | 2.2  | Pin description                    | 5  |

|   | 2.3  | Maximum ratings                    | 6  |

|   | 2.4  | Thermal data                       | 7  |

|   | 2.5  | ESD protection                     | 7  |

| 3 | Elec | etrical characteristics            | 8  |

| 4 | Fund | ctional description                | 12 |

|   | 4.1  | Power supply and voltage reference | 13 |

|   |      | Switchover feature                 | 13 |

|   | 4.2  | Voltages monitor                   | 13 |

|   | 4.3  | Soft-start and inhibit             | 14 |

|   |      | 4.3.1 Ratiometric startup          | 20 |

|   |      | 4.3.2 Output voltage sequencing    | 22 |

|   | 4.4  | Error amplifier                    | 22 |

|   | 4.5  | Light-load operation               | 23 |

|   |      | 4.5.1 Low noise mode (LNM)         | 23 |

|   |      | 4.5.2 Low consumption mode (LCM)   | 24 |

|   | 4.6  | Switchover feature                 | 28 |

|   |      | 4.6.1 LCM                          | 28 |

|   |      | 4.6.2 LNM                          | 28 |

|   | 4.7  | Overcurrent protection             | 29 |

|   |      | OCP and switchover feature         | 32 |

|   | 4.8  | Overvoltage protection             | 34 |

|   | 4.9  | Thermal shutdown                   | 35 |

| 5  | Clos  | ing the loop                                            | 6 |

|----|-------|---------------------------------------------------------|---|

|    | 5.1   | G <sub>CO</sub> (s) control to output transfer function | 6 |

|    | 5.2   | Error amplifier compensation network                    | 8 |

|    | 5.3   | Voltage divider                                         | 9 |

|    | 5.4   | Total loop gain 4                                       | 0 |

|    | 5.5   | Compensation network design                             | 2 |

| 6  | Арр   | ication notes4                                          | 3 |

|    | 6.1   | Output voltage adjustment                               | 3 |

|    | 6.2   | Switching frequency                                     | 3 |

|    | 6.3   | MLF pin                                                 | 4 |

|    | 6.4   | Voltage supervisor                                      | 4 |

|    | 6.5   | Synchronization (LNM)                                   | 5 |

|    | 6.6   | Design of the power components                          | 0 |

|    |       | 6.6.1 Input capacitor selection                         | 0 |

|    |       | 6.6.2 Inductor selection                                | 1 |

|    |       | 6.6.3 Output capacitor selection                        | 2 |

| 7  | App   | ication board 5                                         | 4 |

| 8  | Effic | iency curves                                            | 8 |

| 9  | Pack  | age information                                         | 2 |

|    | 9.1   | HTSSOP16 package information                            | 2 |

| 10 | Orde  | er codes 6                                              | 4 |

| 11 | Rovi  | sion history 6                                          | 4 |

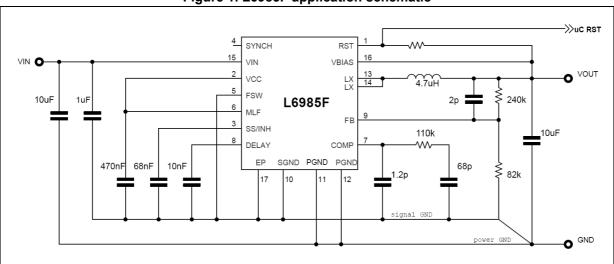

## 1 Application schematic

Figure 1. L6985F application schematic

L6985F Pin settings

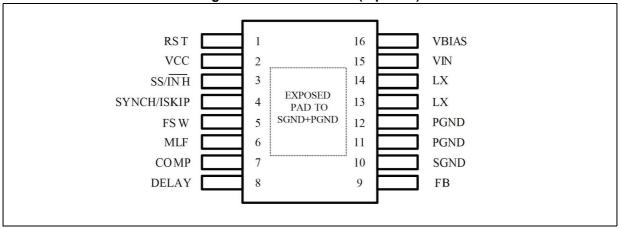

## 2 Pin settings

### 2.1 Pin connection

Figure 2. Pin connection (top view)

## 2.2 Pin description

Table 1. Pin description

| No. | Pin            | Description                                                                                                                                                                                                                           |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RST            | The RST open collector output is driven low when the output voltage is out of regulation. The RST is released after an adjustable time DELAY once the output voltage is over the active delay threshold.                              |

| 2   | VCC            | Connect a ceramic capacitor (≥ 470 nF) to filter internal voltage reference. This pin supplies the embedded analog circuitry.                                                                                                         |

| 3   | SS/INH         | An open collector stage can disable the device clamping this pin to GND ( $\overline{\text{INH}}$ mode). An internal current generator (4 $\mu$ A typ.) charges the external capacitor to implement the soft-start.                   |

| 4   | SYNCH/<br>ISKP | The pin features Master / Slave synchronization in LNM (see Section 6.5 on page 45) and skip current level selection in LCM (see Section 4.5.2 on page 24).                                                                           |

| 5   | FSW            | A pull-up resistor (E24 series only) to VCC or pull-down to GND selects the switching frequency. Pinstrapping is active only before the soft-start phase to minimize the IC consumption.                                              |

| 6   | MLF            | A pull-up resistor (E24 series only) to VCC or pull-down to GND selects the low noise mode/low consumption mode and the active RST threshold. Pinstrapping is active only before the soft-start phase to minimize the IC consumption. |

| 7   | COMP           | Output of the error amplifier. The designed compensation network is connected at this pin.                                                                                                                                            |

| 8   | DELAY          | An external capacitor connected at this pin sets the time DELAY to assert the rising edge of the RST o. c. after the output voltage is over the reset threshold. If this pin is left floating, RST is like a Power Good.              |

| 9   | FB             | Inverting input of the error amplifier                                                                                                                                                                                                |

| 10  | SGND           | Signal GND                                                                                                                                                                                                                            |

| 11  | PGND           | Power GND                                                                                                                                                                                                                             |

Pin settings L6985F

| Table 1.  | Pin | description | (continued)   |

|-----------|-----|-------------|---------------|

| I abic i. |     | acscription | (COIILIIIGEA) |

| No. | Pin   | Description                                                                                                                                                                                                       |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | PGND  | Power GND                                                                                                                                                                                                         |

| 13  | LX    | Switching node                                                                                                                                                                                                    |

| 14  | LX    | Switching node                                                                                                                                                                                                    |

| 15  | VIN   | DC input voltage                                                                                                                                                                                                  |

| 16  | VBIAS | Typically connected to the regulated output voltage. An external voltage reference can be used to supply a part of the analog circuitry to increase the efficiency at the light-load. Connect to GND if not used. |

| -   | E. p. | Exposed pad must be connected to SGND, PGND.                                                                                                                                                                      |

## 2.3 Maximum ratings

Stressing the device above the rating listed in *Table 2: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 2. Absolute maximum ratings

| Symbol                            | Description                          | Min.       | Max.                                | Unit |

|-----------------------------------|--------------------------------------|------------|-------------------------------------|------|

| V <sub>IN</sub>                   |                                      | -0.3       | 40                                  | V    |

| DELAY                             |                                      | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| PGND                              |                                      | SGND - 0.3 | SGND + 0.3                          | V    |

| SGND                              |                                      |            |                                     | V    |

| V <sub>CC</sub>                   |                                      | -0.3       | (V <sub>IN</sub> + 0.3) or (max. 4) | V    |

| SS / INH                          |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| MLF                               | See Table 1                          | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| COMP                              | See <i>Table 1</i>                   | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| VOUT                              |                                      | -0.3       | 10                                  | V    |

| FSW                               |                                      | -0.3       | V <sub>CC</sub> + 0.3               | V    |

| SYNCH                             |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| V <sub>BIAS</sub>                 |                                      | -0.3       | (V <sub>IN</sub> + 0.3) or (max. 6) | V    |

| RST                               |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| LX                                |                                      | -0.3       | V <sub>IN</sub> + 0.3               | V    |

| TJ                                | Operating temperature range          | -40        | 150                                 | °C   |

| T <sub>STG</sub>                  | Storage temperature range            |            | -65 to 150                          | °C   |

| T <sub>LEAD</sub>                 | Lead temperature (soldering 10 sec.) |            | 260                                 | °C   |

| I <sub>HS</sub> , I <sub>LS</sub> | High-side / low-side switch current  |            | 2                                   | Α    |

L6985F Pin settings

## 2.4 Thermal data

Table 3. Thermal data

| Symbol             | Parameter                                                                                                        | Value | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------|-------|------|

| R <sub>th JA</sub> | Thermal resistance junction ambient (device soldered on the STMicroelectronics <sup>®</sup> demonstration board) | 40    | °C/W |

| R <sub>th JC</sub> | Thermal resistance junction to exposed pad for board design (not suggested to estimate TJ from power losses).    | 5     | C/W  |

## 2.5 ESD protection

Table 4. ESD protection

| Symbol | Test condition | Value | Unit |

|--------|----------------|-------|------|

| ESD    | НВМ            | 2     | kV   |

|        | MM             | 200   | V    |

|        | CDM            | 500   | V    |

Electrical characteristics L6985F

## 3 Electrical characteristics

$T_J$  = 25 °C,  $V_{IN}$  = 12 V unless otherwise specified.

**Table 5. Electrical characteristics**

| Symbol               | Parameter                                             | Test condition                                                   |     | Min.                                   | Тур. | Max. | Unit  |

|----------------------|-------------------------------------------------------|------------------------------------------------------------------|-----|----------------------------------------|------|------|-------|

| V <sub>IN</sub>      | Operating input voltage range                         |                                                                  |     | 4                                      |      | 38   |       |

| V <sub>INH</sub>     | V <sub>CC</sub> UVLO rising threshold                 |                                                                  |     | 2.7                                    |      | 3.5  | V     |

| V <sub>INL</sub>     | V <sub>CC</sub> UVLO falling threshold                |                                                                  |     | 2.4                                    |      | 3.5  |       |

|                      |                                                       | Duty cycle < 20%                                                 |     | 8.0                                    |      |      |       |

| I <sub>PK</sub>      | Peak current limit                                    | Duty cycle = 100% closed loop operation                          |     | 0.65                                   |      |      | А     |

| I <sub>VY</sub>      | Valley current limit                                  |                                                                  |     | 0.9                                    |      |      |       |

|                      | Ckin ourrant limit                                    | LCM, V <sub>SYNCH</sub> = GND                                    | (1) | 0.15                                   | 0.35 | 0.5  |       |

| I <sub>SKIP</sub>    | Skip current limit                                    | LCM, V <sub>SYNCH</sub> = VCC                                    | (2) |                                        | 0.1  |      |       |

| I <sub>VY_SNK</sub>  | Reverse current limit                                 | LNM or V <sub>OUT</sub> overvoltage                              |     | 0.5                                    | 1    | 2    |       |

| R <sub>DSON HS</sub> | High-side RDSON                                       | I <sub>SW</sub> = 0.5 A                                          |     |                                        | 0.36 | 0.72 | Ω     |

| R <sub>DSON LS</sub> | Low-side RDSON                                        | I <sub>SW</sub> = 0.5 A                                          |     |                                        | 0.15 | 0.30 | 2.2   |

| f <sub>SW</sub>      | Selected switching frequency                          | FSW pinstrapping before SS                                       |     | See Table 6: f <sub>SW</sub> selection |      |      |       |

| I <sub>FSW</sub>     | FSW biasing current                                   | SS ended                                                         |     |                                        | 0    | 500  | nA    |

| LCM/LNM              | Low noise mode /<br>Low consumption mode<br>selection | MLF pinstrapping before SS                                       |     | See Table 7 on page 11                 |      |      | ie 11 |

| I <sub>MLF</sub>     | MLF biasing current                                   | SS ended                                                         |     |                                        | 0    | 500  | nA    |

| D                    | Duty cycle                                            |                                                                  | (2) | 0                                      |      | 100  | %     |

| T <sub>ON MIN</sub>  | Minimum On time                                       |                                                                  |     |                                        | 80   |      | ns    |

| VCC regul            | ator                                                  |                                                                  |     |                                        |      |      |       |

| V                    | LDO output voltage                                    | V <sub>BIAS</sub> = GND (no switchover)                          |     | 2.9                                    | 3.3  | 3.6  |       |

| V <sub>CC</sub>      | LDO output voltage                                    | V <sub>BIAS</sub> = 5 V (switchover)                             |     | 2.9                                    | 3.3  | 3.6  |       |

| swo                  | V <sub>BIAS</sub> threshold                           | Switch internal supply from $V_{\text{IN}}$ to $V_{\text{BIAS}}$ |     | 2.85                                   |      | 3.2  | V     |

| 300                  | (3 V< V <sub>BIAS</sub> < 5.5 V)                      | Switch internal supply from $V_{BIAS}$ to $V_{IN}$               |     | 2.78                                   |      | 3.15 |       |

Table 5. Electrical characteristics (continued)

| Symbol                 | Parameter                                | Test condition                                                                                                                                                                                     | Note | Min.  | Тур. | Max.  | Unit |  |  |

|------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|--|--|

| Power con              | sumption                                 |                                                                                                                                                                                                    |      |       |      |       |      |  |  |

| I <sub>SHTDWN</sub>    | Shutdown current from V <sub>IN</sub>    | V <sub>SS/INH</sub> = GND                                                                                                                                                                          |      | 4     | 8    | 15    | μА   |  |  |

|                        |                                          | $\begin{aligned} & \textbf{LCM - SWO} \\ & \textbf{V}_{\text{REF}} < \textbf{V}_{\text{FB}} < \textbf{V}_{\text{OVP}} \text{ (SLEEP)} \\ & \textbf{V}_{\text{BIAS}} = 3.3 \text{ V} \end{aligned}$ | (3)  | 4     | 10   | 15    |      |  |  |

|                        | Outlease at a company from N             | $\begin{aligned} & \textbf{LCM - NO SWO} \\ & \textbf{V}_{REF} < \textbf{V}_{FB} < \textbf{V}_{OVP} \text{ (SLEEP)} \\ & \textbf{V}_{BIAS} = \textbf{GND} \end{aligned}$                           | (3)  | 35    | 70   | 120   | — μA |  |  |

| IQ OPVIN               | Quiescent current from V <sub>IN</sub>   | LNM - SWO<br>V <sub>FB</sub> = GND (NO SLEEP)<br>V <sub>BIAS</sub> = 3.3 V                                                                                                                         |      | 0.5   | 1.5  | 5     | mA   |  |  |

|                        |                                          | LNM - NO SWO  V <sub>FB</sub> = GND (NO SLEEP)  V <sub>BIAS</sub> = GND                                                                                                                            |      | 2     | 2.8  | 6     | IIIA |  |  |

|                        | Quiescent current from V <sub>BIAS</sub> | LCM - SWO<br>$V_{REF} < V_{FB} < V_{OVP}$ (SLEEP)<br>$V_{BIAS} = 3.3 \text{ V}$                                                                                                                    | (3)  | 25    | 50   | 115   | μΑ   |  |  |

| I <sub>Q</sub> OPVBIAS |                                          | <b>LNM - SWO</b> $V_{FB} = GND (NO SLEEP)$ $V_{BIAS} = 3.3 V$                                                                                                                                      |      | 0.5   | 1.2  | 5     | mA   |  |  |

| Soft-start             |                                          |                                                                                                                                                                                                    |      |       |      |       |      |  |  |

| V <sub>INH</sub>       | VSS threshold                            | SS rising                                                                                                                                                                                          |      | 200   | 460  | 700   | mV   |  |  |

| V <sub>INH HYST</sub>  | VSS hysteresis                           |                                                                                                                                                                                                    |      |       | 100  | 140   | IIIV |  |  |

| I <sub>SS CH</sub>     | C <sub>SS</sub> charging current         | V <sub>SS</sub> < V <sub>INH</sub> OR<br>t < T <sub>SS SETUP</sub> OR<br>V <sub>EA+</sub> > V <sub>FB</sub>                                                                                        | (2)  |       | 1    |       | μΑ   |  |  |

|                        |                                          | $t > T_{SS SETUP} AND$<br>$V_{EA+} < V_{FB}$                                                                                                                                                       | (2)  |       | 4    |       | F    |  |  |

| V <sub>SS START</sub>  | Start of internal error amplifier ramp   |                                                                                                                                                                                                    |      | 0.995 | 1.1  | 1.150 | V    |  |  |

| SS <sub>GAIN</sub>     | SS/INH to internal error amplifier gain  |                                                                                                                                                                                                    |      |       | 3    |       |      |  |  |

| Error amp              | lifier                                   |                                                                                                                                                                                                    |      |       |      |       |      |  |  |

| V <sub>OUT</sub>       | Voltage feedback                         |                                                                                                                                                                                                    |      | 0.841 | 0.85 | 0.859 | V    |  |  |

| I <sub>VOUT</sub>      | VOUT biasing current                     |                                                                                                                                                                                                    |      |       | 50   | 500   | nA   |  |  |

| A <sub>V</sub>         | Error amplifier gain                     |                                                                                                                                                                                                    | (2)  |       | 100  |       | dB   |  |  |

| I <sub>COMP</sub>      | EA output current capability             |                                                                                                                                                                                                    |      | ±6    | ±12  | ±25   | μΑ   |  |  |

Electrical characteristics L6985F

Table 5. Electrical characteristics (continued)

| Symbol                   | Parameter                                                                    | Test condition                                                                                | Note | Min.  | Тур.    | Max.     | Unit |

|--------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-------|---------|----------|------|

| Inner curre              | ent loop                                                                     |                                                                                               | l .  | ı     |         |          |      |

| 9cs                      | Current sense transconductance (V <sub>COMP</sub> to inductor current gain)  | I <sub>PK</sub> = 0.5 A                                                                       | (2)  |       | 1.67    |          | A/V  |

| $V_{PP} \cdot g_{CS}$    | Slope compensation                                                           |                                                                                               | (4)  | 0.2   | 0.3     | 0.4      | Α    |

| Overvoltaç               | ge protection                                                                |                                                                                               | •    |       |         |          |      |

| V <sub>OVP</sub>         | Overvoltage trip (V <sub>OVP</sub> /V <sub>REF</sub> )                       |                                                                                               |      | 1.15  | 1.2     | 1.25     |      |

| V <sub>OVP</sub><br>HYST | Overvoltage hysteresis                                                       |                                                                                               |      | 0.5   | 2       | 5        | %    |

| Synchroni                | zation (fan out: 6 slave device                                              | es typ.)                                                                                      |      |       |         |          |      |

| f <sub>SYN MIN</sub>     | Synchronization frequency                                                    | LNM; f <sub>SW</sub> = VCC                                                                    |      | 266.5 |         |          | kHz  |

| V <sub>SYN TH</sub>      | SYNCH input threshold                                                        | LNM, SYNCH rising                                                                             |      | 0.70  |         | 1.2      | V    |

| I <sub>SYN</sub>         | SYNCH pulldown current                                                       | LNM, V <sub>SYN</sub> = 1.2 V                                                                 |      |       | 0.7     |          | mA   |

|                          | High level output                                                            | LNM, 5 mA sinking load                                                                        |      | 1.40  |         |          | V    |

| V <sub>SYN OUT</sub>     | Low level output                                                             | LNM, 0.7 mA sourcing load                                                                     |      |       |         | 0.6      | V    |

| Reset                    |                                                                              |                                                                                               | •    | •     |         |          |      |

| V <sub>THR</sub>         | Selected RST threshold                                                       | MLF pinstrapping before SS                                                                    |      | See   | Table 1 | 7 on pag | e 11 |

| V <sub>THR HYST</sub>    | RST hysteresis                                                               |                                                                                               | (2)  |       | 2       |          | %    |

| \/                       | RST open collector output                                                    | V <sub>IN</sub> > V <sub>INH</sub> AND V <sub>FB</sub> < V <sub>TH</sub><br>4 mA sinking load |      |       |         | 0.4      | V    |

| V <sub>RST</sub>         |                                                                              | 2 < V <sub>IN</sub> < V <sub>INH</sub><br>4 mA sinking load                                   |      |       |         | 0.8      | V    |

| Delay                    |                                                                              |                                                                                               | •    | •     |         |          |      |

| V <sub>THD</sub>         | RST open collector released as soon as V <sub>DELAY</sub> > V <sub>THD</sub> | V <sub>FB</sub> > V <sub>THR</sub>                                                            |      | 1.19  | 1.234   | 1.258    | V    |

| I <sub>D CH</sub>        | C <sub>DELAY</sub> charging current                                          | $V_{FB} > V_{THR}$                                                                            |      | 1     | 2       | 3        | μΑ   |

| Thermal s                | hutdown                                                                      |                                                                                               | •    |       |         |          |      |

| T <sub>SHDWN</sub>       | Thermal shutdown temperature                                                 |                                                                                               | (2)  |       | 165     |          | 9.0  |

| T <sub>HYS</sub>         | Thermal shutdown hysteresis                                                  |                                                                                               | (2)  |       | 30      |          | °C   |

<sup>1.</sup> Parameter tested in static condition during the testing phase. Parameter value may change over dynamic application condition.

<sup>2.</sup> Not tested in production.

<sup>3.</sup> LCM enables SLEEP mode at the light-load.

<sup>4.</sup> Measured at  $f_{sw}$  = 250 kHz.

$T_J$  = 25 °C,  $V_{IN}$  = 12 V unless otherwise specified.

Table 6. f<sub>SW</sub> selection

| Symbol          | R <sub>VCC</sub> (E24 series) | R <sub>GND</sub> (E24 series) | Tj  | f <sub>SW</sub> min. | f <sub>SW</sub> typ. | f <sub>SW</sub> max. | Unit |

|-----------------|-------------------------------|-------------------------------|-----|----------------------|----------------------|----------------------|------|

|                 | 0 Ω                           | NC                            |     | 225                  | 250                  | 275                  |      |

|                 | 1.8 kΩ                        | NC                            |     |                      | 285                  |                      |      |

|                 | 3.3 kΩ                        | NC                            | (1) |                      | 330                  |                      |      |

|                 | 5.6 kΩ                        | NC                            |     |                      | 380                  |                      |      |

|                 | 10 kΩ                         | NC                            |     |                      | 435                  |                      |      |

|                 | NC                            | 0 Ω                           |     | 450                  | 500                  | 550                  |      |

|                 | 18 kΩ                         | NC                            |     |                      | 575                  |                      | kHz  |

| f               | 33 kΩ                         | NC                            | (1) |                      | 660                  |                      |      |

| f <sub>SW</sub> | 56 kΩ                         | NC                            |     |                      | 755                  |                      |      |

|                 | NC                            | 1.8 kΩ                        |     |                      | 870                  |                      |      |

|                 | NC                            | 3.3 kΩ                        |     | 900                  | 1000                 | 1100                 |      |

|                 | NC                            | 5.6 kΩ                        |     |                      | 1150                 |                      |      |

|                 | NC                            | 10 kΩ                         | (1) |                      | 1310                 |                      |      |

|                 | NC                            | 18 kΩ                         |     |                      | 1500 <sup>(2)</sup>  |                      |      |

|                 | NC                            | 33 kΩ                         |     | 1575                 | 1750 <sup>(2)</sup>  | 1925                 |      |

|                 | NC                            | 56 kΩ                         |     | 1800                 | 2000 <sup>(2)</sup>  | 2200                 |      |

- 1. Not tested in production.

- 2. No synchronization as slave in LNM.

$T_J$  = 25 °C,  $V_{IN}$  = 12 V unless otherwise specified.

Table 7. LNM / LCM selection table

| Symbol           | R <sub>VCC</sub><br>(E24 1%) | R <sub>GND</sub><br>(E24 1%) | Operating mode | V <sub>RST</sub> /V <sub>OUT</sub><br>(tgt. value) | V <sub>RST</sub><br>min. | V <sub>RST</sub><br>typ. | V <sub>RST</sub><br>max. | Unit |

|------------------|------------------------------|------------------------------|----------------|----------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| V <sub>RST</sub> | 0 Ω                          | NC                           | LCM            | 93%                                                | 0.779                    | 0.791                    | 0.802                    | V    |

|                  | 8.2 kΩ                       | NC                           |                | 80%                                                | 0.670                    | 0.680                    | 0.690                    |      |

|                  | 18 kΩ                        | NC                           |                | 87%                                                | 0.728                    | 0.740                    | 0.751                    |      |

|                  | 39 kΩ                        | NC                           |                | 96%                                                | 0.804                    | 0.816                    | 0.828                    |      |

|                  | NC                           | 0 Ω                          | LNM            | 93%                                                | 0.779                    | 0.791                    | 0.802                    |      |

|                  | NC                           | 8.2 kΩ                       |                | 80%                                                | 0.670                    | 0.680                    | 0.690                    |      |

|                  | NC                           | 18 kΩ                        |                | 87%                                                | 0.728                    | 0.740                    | 0.751                    |      |

|                  | NC                           | 39 kΩ                        |                | 96%                                                | 0.804                    | 0.816                    | 0.828                    |      |

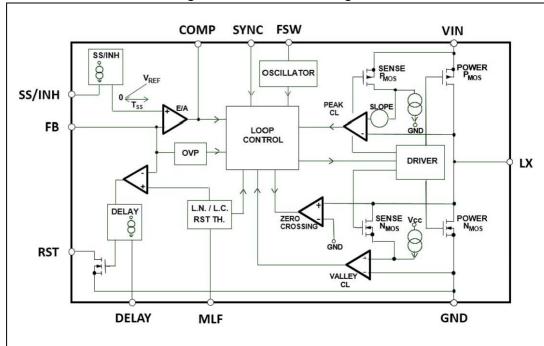

## 4 Functional description

The L6985F device is based on a "peak current mode", constant frequency control. As a consequence, the intersection between the error amplifier output and the sensed inductor current generates the PWM control signal to drive the power switch.

The device features LNM (low noise mode) that is forced PWM control, or LCM (low consumption mode) to increase the efficiency at the light-load.

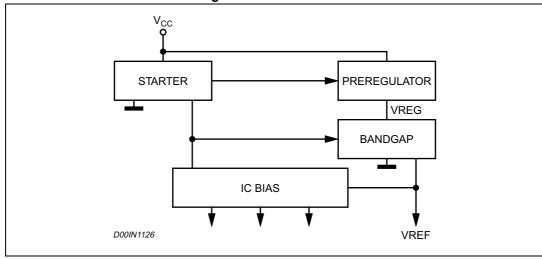

The main internal blocks shown in the block diagram in Figure 3 are:

- Embedded power elements. Thanks to the P-channel MOSFET as a high-side switch the device features a low dropout operation

- A fully integrated sawtooth oscillator with adjustable frequency

- A transconductance error amplifier

- The high-side current sense amplifier to sense the inductor current

- A "Pulse Width Modulator" (PWM) comparator and the driving circuitry of the embedded power elements

- The soft-start blocks to ramp the error amplifier reference voltage and so decreases the inrush current at power-up. The SS/INH pin inhibits the device when driven low.

- The switchover capability of the internal regulator to supply a portion of the quiescent current when the V<sub>BIAS</sub> pin is connected to an external output voltage

- The synchronization circuitry to manage a master / slave operation and the synchronization to an external clock

- The current limitation circuit to implement the constant current protection, sensing a pulse-by-pulse high-side / low-side switch current. In case of heavy short-circuit the current protection is fold back to decrease the stress of the external components

- A circuit to implement the thermal protection function

- The OVP circuitry to discharge the output capacitor in case of an overvoltage event

- The MLF pin strapping sets the LNM/LCM mode and the thresholds of the RST comparator

- FSW pinstrapping sets the switching frequency

- The RST open collector output

Figure 3. Internal block diagram

### 4.1 Power supply and voltage reference

The internal regulator block consists of a start-up circuit, the voltage pre-regulator that provides the current to all the blocks and the bandgap voltage reference. The starter supplies the startup current when the input voltage goes high and the device is enabled (SS/INH pin over the inhibits threshold).

The pre-regulator block supplies the bandgap cell and the rest of the circuitry with a regulated voltage that has a very low supply voltage noise sensitivity.

#### Switchover feature

The switchover scheme of the pre-regulator block features to derive the main contribution of the supply current for the internal circuitry from an external voltage (3 V <  $V_{BIAS}$  < 5.5 V is typically connected to the regulated output voltage). This helps to decrease the equivalent quiescent current seen at  $V_{IN}$ . (Please refer to Section 4.6: Switchover feature on page 28).

## 4.2 Voltages monitor

An internal block continuously senses the  $V_{CC}$ ,  $V_{BIAS}$  and  $V_{BG}$ . If the monitored voltages are good, the regulator starts operating. There is also a hysteresis on the  $V_{CC}$  (UVLO).

Figure 4. Internal circuit

#### 4.3 Soft-start and inhibit

The soft-start and inhibit features are multiplexed on the same pin. An internal current source charges the external soft-start capacitor to implement a voltage ramp on the SS/INH pin. The device is inhibited as long as the SS/INH pin voltage is lower than the  $V_{INH}$  threshold and the soft-start takes place when the SS/INH pin crosses  $V_{SS\ START}$ . (See Figure 5).

The internal current generator sources a 1  $\mu$ A typ. current when the voltage of the V<u>CC</u> pin crosses the UVLO threshold. The current increases to 4  $\mu$ A typ. as soon as the SS/INH voltage is higher than the V<sub>INH</sub> threshold. This feature helps to decrease the current consumption in inhibit mode. An external open collector can be used to set the inhibit operation clamping the SS/INH voltage below the V<sub>INH</sub> threshold.

The startup feature minimizes the inrush current and decreases the stress of the power components during the power-up phase. The ramp implemented on the reference of the erro<u>r amplifier</u> has a gain three times higher ( $SS_{GAIN}$ ) than the external ramp present at the SS/INH pin.

EA reference

V<sub>SS START</sub>

V<sub>SS INH</sub>

Internal soft start signal

V<sub>CC</sub> pin

Figure 5. Soft-start phase

The  $C_{SS}$  is dimensioned accordingly with *Equation 1*:

#### **Equation 1**

$$C_{SS} = SS_{GAIN} \bullet \frac{I_{SSCH} \bullet T_{SS}}{V_{FB}} = 3 \bullet \frac{4\mu A \bullet T_{SS}}{0.85V}$$

where  $T_{SS}$  is the soft-start time,  $I_{SS\ CH}$  the charging current and  $V_{FB}$  the reference of the error amplifier.

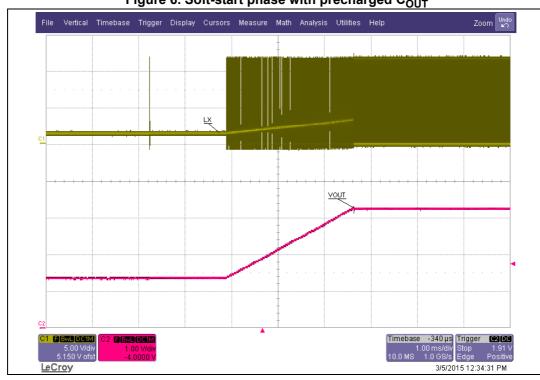

The soft-start block supports the precharged output capacitor.

Figure 6. Soft-start phase with precharged C<sub>OUT</sub>

During the normal operation a new soft-start cycle takes place in case of:

- Thermal shutdown event

- UVLO event

- The device is driven in INH mode

The soft-start capacitor is discharged with a 0.6 mA typ. current capability for 1 msec time max. For complete and proper capacitor discharge in case of fault condition, a maximum  $C_{SS} = 67$  nF value is suggested.

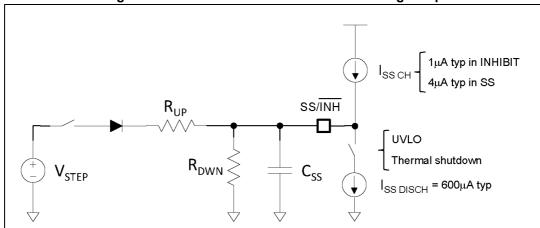

The application example in *Figure 7* shows how to enable the L6985F and perform the soft-start phase driven by an external voltage step.

Figure 7. Enable the device with external voltage step

The maximum capacitor value has to be limited to guarantee the device can discharge it in case of a thermal shutdown and UVLO events (see Section 4.3.1), so restart the switching activity ramping the error amplifier reference voltage.

#### **Equation 2**

$$C_{SS} < \frac{-1 \text{ msec}}{R_{SS\_EQ} \cdot ln \left(1 - \frac{V_{SS\_FINAL} - 0.9 \text{ V}}{600 \text{ } \mu A - R_{SS\_EQ}}\right)}$$

where:

#### **Equation 3**

$$R_{SS\_EQ} = \frac{R_{UP} \cdot R_{DWN}}{R_{UP} + R_{DWN}} \qquad V_{SS\_FINAL} = (V_{STEP} - V_{DIODE}) \cdot \frac{R_{DWN}}{R_{UP} + R_{DWN}}$$

The optional diode prevents to disable the device if the external source drops to ground.

$R_{UP}$  value is selected in order to make the capacitor charge at first approximation independent from the internal current generator (4  $\mu$ A typ. current capability, see *Table 5 on page 8*), so:

#### **Equation 4**

$$\frac{V_{STEP} - V_{DIODE} - V_{SSEND}}{R_{UP}} \gg I_{SSCHARGE} \equiv 4 \mu A$$

where:

#### **Equation 5**

$$V_{SS END} = V_{SS START} + \frac{V_{FB}}{SS_{GAIN}}$$

represents the SS/ $\overline{\text{INH}}$  voltage correspondent to the end of the ramp on the error amplifier (see *Figure 5*); refer to *Table 5* for V<sub>SS START</sub>, V<sub>FB</sub> and SS<sub>GAIN</sub> parameters.

As a consequence the voltage across the soft-start capacitor can be written as:

#### **Equation 6**

$$v_{SS}(t) = V_{SS\_FINAL} \cdot \frac{1}{1 - e^{-\frac{t}{C_{SS} \cdot R_{SS\_EQ}}}}$$

$R_{SS\_DOWN}$  is selected to guarantee the device stays in inhibit mode when the internal generator sources 1  $\mu A$  typ. out of the SS/INH pin and  $V_{STEP}$  is not present:

#### **Equation 7**

$$R_{DWN} \cdot I_{SS\ INHIBIT} \equiv R_{DWN} \cdot 1 \ \mu A \ll V_{INH} \equiv 200 \ mV$$

so:

#### **Equation 8**

$$R_{DWN} < 100 \text{ k}\Omega$$

$R_{UP}$  and  $R_{DWN}$  are selected to guarantee:

#### **Equation 9**

$$V_{SS FINAL} \cong 2 V > V_{SS END}$$

The time to ramp the internal voltage reference can be calculated from *Equation 10*:

#### **Equation 10**

$$T_{SS} = C_{SS} \cdot R_{SS\_EQ} \cdot In \left( \frac{V_{SS\_FINAL} - V_{SS\_START}}{V_{SS\_FINAL} - V_{SS\_END}} \right)$$

that is the equivalent soft-start time to ramp the output voltage.

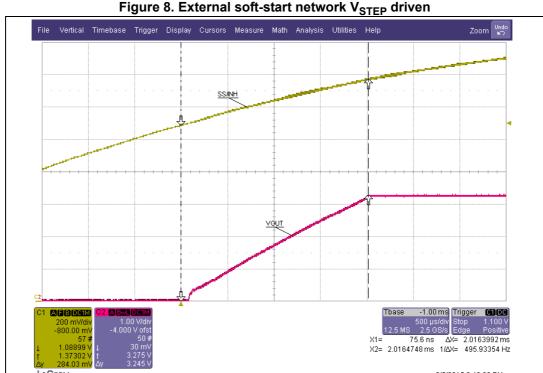

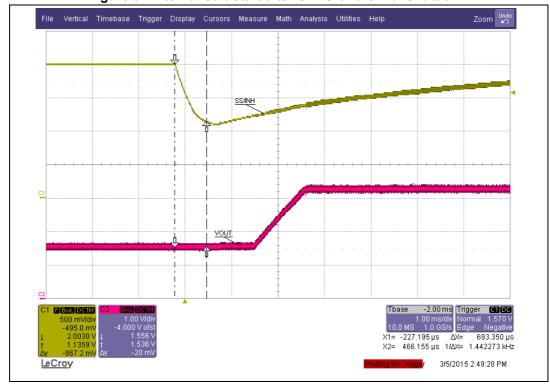

*Figure 8* shows the soft-start phase with the following component selection:  $R_{UP}$  = 180 k $\Omega$ ,  $R_{DWN}$  = 33 k $\Omega$ ,  $C_{SS}$  = 200 nF, the 1N4148 is a small signal diode and  $V_{STEP}$  = 13 V.

The circuit in Figure 7 introduces a time delay between  $V_{\mbox{\scriptsize STEP}}$  and the switching activity that can be calculated as:

#### **Equation 11**

$$\mathsf{T}_{\mathsf{SS}\;\mathsf{DELAY}} = \mathsf{C}_{\mathsf{SS}} \cdot \mathsf{R}_{\mathsf{SS}\_\mathsf{EQ}} \cdot \mathsf{In} \Big( \frac{\mathsf{V}_{\mathsf{SS}\_\mathsf{FINAL}}}{\mathsf{V}_{\mathsf{SS}\_\mathsf{FINAL}} - \mathsf{V}_{\mathsf{SS}\;\mathsf{START}}} \Big)$$

*Figure 9* shows how the device discharges the soft-start capacitor after an UVLO or thermal shutdown event in order to restart the switching activity ramping the error amplifier reference voltage.

Figure 9. External soft-start after UVLO or thermal shutdown

### 4.3.1 Ratiometric startup

The ratiometric startup is implemented sharing the same soft-start capacitor for a set of the L6985F devices.

V<sub>OUT2</sub>

V<sub>OUT1</sub>

V<sub>OUT1</sub>

Figure 10. Ratiometric startup

As a consequence all the internal current generators charge in parallel the external capacitor. The capacitor value is dimensioned accordingly with *Equation 12*:

#### **Equation 12**

$$C_{SS} = n_{L6985F} \bullet SS_{GAIN} \bullet \frac{I_{SSCH} \bullet T_{SS}}{V_{FB}} = n_{L6985F} \bullet 3 \bullet \frac{4\mu A \bullet T_{SS}}{0.85V}$$

where  $n_{L6985F}$  represents the number of devices connected in parallel.

For better tracking of the different output voltages the synchronization of the set of regulators is suggested.

Figure 11. Ratiometric startup operation

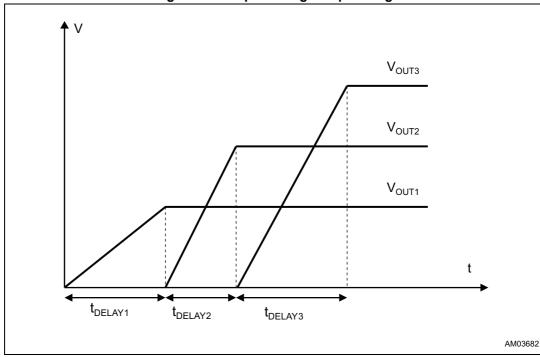

#### 4.3.2 Output voltage sequencing

The L6985F device implements sequencing connecting the RST pin of the master device to the SS/INH of the slave. The slave is inhibited as long as the master output voltage is outside of the regulation so implementing the sequencing (see *Figure 12*).

Figure 12. Output voltage sequencing

High flexibility is achieved thanks to the programmable RST thresholds (see *Table 7 on page 11*) and programmable delay time. To minimize the component count the DELAY pin capacitor can be also omitted so the pin works as a normal Power Good.

## 4.4 Error amplifier

The voltage error amplifier is the core of the loop regulation. It is a transconductance operational amplifier whose non inverting input is connected to the internal voltage reference (0.85 V), while the inverting input (FB) is connected to the external divider or directly to the output voltage.

| Description        | Values |  |  |  |  |

|--------------------|--------|--|--|--|--|

| Transconductance   | 155 μS |  |  |  |  |

| Low frequency gain | 100 dB |  |  |  |  |

Table 8. Uncompensated error amplifier characteristics

The error amplifier output is compared with the inductor current sense information to perform PWM control. The error amplifier also determines the burst operation at the light-load when the LCM is active.

### 4.5 Light-load operation

The MLF pinstrapping during the power-up phase determines the light-load operation (refer to *Table 7 on page 11*).

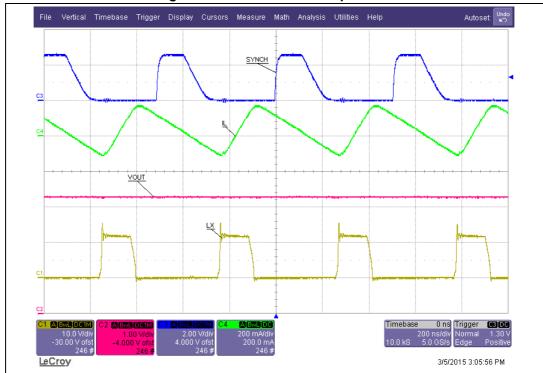

#### 4.5.1 Low noise mode (LNM)

The low noise mode implements a forced PWM operation over the different loading conditions. The LNM features a constant switching frequency to minimize the noise in the final application and a constant voltage ripple at fixed  $V_{IN}$ . The regulator in steady loading condition never skip pulses and it operates in the continuous conduction mode (CCM) over the different loading conditions thus making this operation mode ideal for noise sensitive applications.

Figure 13. Low noise mode operation

### 4.5.2 Low consumption mode (LCM)

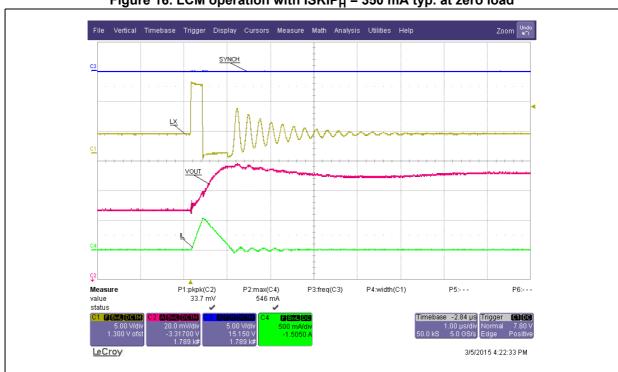

The low consumption mode maximizes the efficiency at the light-load. The regulator prevents the switching activity whenever the switch peak current request is lower than the  $I_{SKIP}$  threshold (350 mA typical). As a consequence the L6985F device works in bursts and it minimizes the quiescent current request in the meantime between the switching operation. In the LCM operation, the pin SYNCH/ISKIP level dynamically defines the  $I_{SKIP}$  current threshold (see *Table* 9).

Table 9. I<sub>SKIP</sub> current level

| SYNCH / ISKIP (pin 4) | I <sub>SKIP</sub> current threshold |  |  |

|-----------------------|-------------------------------------|--|--|

| LOW                   | ISKIP <sub>H</sub> = 0.35 A typical |  |  |

| HIGH                  | ISKIP <sub>L</sub> = 0.1 A typical  |  |  |

The ISKIP programmability helps to optimize the performance in terms of the output voltage ripple or efficiency at the light-load, that are parameters which disagree each other by definition.

A lower skip current level minimizes the voltage ripple but increases the switching activity (time between bursts gets closer) since less energy per burst is transfered to the output voltage at the given load. On the other side, a higher skip level reduces the switching activity and improves the efficiency at the light-load but worsen the voltage ripple.

No difference in terms of the voltage ripple and conversion efficiency for the medium and high load current level, that is when the device operates in the discontinuous or continuous mode (DCM vs. CCM).

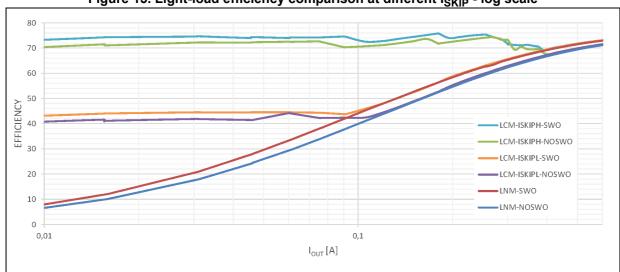

Figure 14 and Figure 15 report the efficiency measurements with  $V_{OUT}$  = 3.3 V to highlight the ISKIP<sub>H</sub> and ISKIP<sub>L</sub> efficiency gap at the light-load also in comparison with the LNM operation. The same efficiency at the medium / high load is confirmed at different ISKIP levels.

Figure 14. Light-load efficiency comparison at different ISKIP - linear scale 70 60 50 EFFICIENCY 40 LCM-ISKIPH-SWO LCM-ISKIPH-NOSWO 30 LCM-ISKIPL-SWO LCM-ISKIPL-NOSWO 20 -LNM-SWO 10 -LNM-NOSWO 0 0,1 0,2 0,5 0.4 0.6 I<sub>OUT</sub> [A]

24/65 DocID027836 Rev 2

Figure 15. Light-load efficiency comparison at different I<sub>SKIP</sub> - log scale

Figure 16 and Figure 17 show the LCM operation at the different ISKIP level.

Figure 16 shows the ISKIP $_{\rm H}$  = 350 mA typ. and so 34 mV output voltage ripple.

Figure 17 shows the ISKIP $_{\rm L}$  = 100 mA typ. and so 13 mV output voltage ripple.

Figure 16. LCM operation with ISKIP<sub>H</sub> = 350 mA typ. at zero load