Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### Automotive PSI5 transceiver IC

#### Datasheet - production data

#### **Features**

- · AEC-Q100 qualified

- 2-channel PSI5 transceiver compatible with rev. 1.3 and rev. 2.x

- Manchester coded digital data transmission

- High data transmission speed of 125 kbps (optional 83.3 kbps and 189 kbps)

- High EMC robustness and low emission

- Bootstrap circuits for sync pulses

- Current limitation and voltage clamp on interface pins

- Integrated charge pump stage for preregulation with spread spectrum approach

- Integrated FLL module for high accuracy timing control

- · Reverse voltage protection structure

- Short to ground tolerant with ±1.5 V ground shift

- · 32-bit SPI interface with address multiplexing

- Operating voltage: V<sub>B</sub> = 4.8 V (5.2 V for sync pulses with 3.5 V step) to 35 V

- Ambient temperature range: -40°C to 140 °C

- Package: VFQFPN28 or TQFP32EP

#### **Description**

The Peripheral Sensor Interface (PSI5) is an interface for automotive sensor applications. PSI5 is an open standard based on existing sensor interfaces for peripheral sensors and offers a universal and flexible solution for multiple sensor applications.

The PSI5 interface allows asynchronous or synchronous operations and different bus modes. The device is compatible with both v1.3 and v2.x PSI5 revisions (limitations are specified inside this document). It operates with a wide range of sensor supply current and variable data word length (8 to 28 bit).

The sensors are connected to the ECU using the same line for power supply and data transmission. The transceiver IC provides a preregulated voltage to the sensors and reads in the transmitted sensor data.

The PSI5 interface allows either point to point connection or bussed mode.

**Table 1. Device summary**

| Order code | Package              | Packing     |

|------------|----------------------|-------------|

| L9663      | TOED32 (Exposed pad) | Tray        |

| L9663-TR   | TQFP32 (Exposed pad) | Tape & Reel |

| L9663-1    | VFQFPN28             | Tray        |

| L9663-TR-1 | VIQIPNZO             | Tape & Reel |

Contents L9663

## **Contents**

| 1 | Ove  | rall desc          | cription                                                                 | 6  |  |  |  |

|---|------|--------------------|--------------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Simplif            | fied block diagram                                                       | 6  |  |  |  |

|   | 1.2  | Main f             | unctionality                                                             | 7  |  |  |  |

|   | 1.3  | VQFPI              | N28 pins description                                                     | 9  |  |  |  |

|   | 1.4  | TQFP               | 32 pins description                                                      | 11 |  |  |  |

|   | 1.5  | Maxim              | um ratings                                                               | 13 |  |  |  |

|   | 1.6  | Detaile            | ed block diagram                                                         | 14 |  |  |  |

|   | 1.7  | Power              | up sequence                                                              | 16 |  |  |  |

| 2 | Pow  | er supp            | ly                                                                       | 17 |  |  |  |

|   | 2.1  | Interna            | al supply                                                                | 17 |  |  |  |

|   | 2.2  | V <sub>AS</sub> su | ipply and pre-regulator                                                  | 18 |  |  |  |

|   | 2.3  | Voltage            | e supply for synchronous pulse generation $V_{\mbox{\scriptsize SYNCx}}$ | 19 |  |  |  |

|   | 2.4  | Power              | supply for PSI5 sensor line                                              | 20 |  |  |  |

|   | 2.5  | Freque             | ency references                                                          | 22 |  |  |  |

|   | 2.6  | Reset              | handling                                                                 | 24 |  |  |  |

| 3 | Sate | llite inte         | erface                                                                   | 25 |  |  |  |

|   | 3.1  | Receiv             | ver with digital sampling and filtering                                  | 25 |  |  |  |

|   | 3.2  | Manch              | Manchester decoder and error detection                                   |    |  |  |  |

|   | 3.3  | Receiv             | ve block                                                                 | 26 |  |  |  |

|   |      | 3.3.1              | PSI5 receive register                                                    | 27 |  |  |  |

|   |      | 3.3.2              | Sensor data buffer                                                       | 30 |  |  |  |

|   |      | 3.3.3              | Interrupt generator                                                      | 33 |  |  |  |

|   |      | 3.3.4              | Automatic storage of sensor initialization data                          | 33 |  |  |  |

|   | 3.4  | Upstre             | am data buffer                                                           | 35 |  |  |  |

|   | 3.5  | Trigge             | r pulse generator for synchronous pulses                                 | 36 |  |  |  |

|   | 3.6  | Synch              | ronous pulse generator                                                   | 37 |  |  |  |

|   | 3.7  | Safety             | concepts                                                                 | 38 |  |  |  |

|   |      | 3.7.1              | Voltage monitoring check                                                 | 38 |  |  |  |

|   |      | 3.7.2              | Sensor data consistency                                                  | 38 |  |  |  |

|   |      | 3.7.3              | Buffer empty check                                                       | 39 |  |  |  |

L9663 Contents

|   |      | 0.7.4     | DOUT, weath also also                             | 00  |

|---|------|-----------|---------------------------------------------------|-----|

|   |      | 3.7.4     | DOUTx path check                                  |     |

|   |      | 3.7.5     | Cross coupling test                               | 40  |

| 4 | Diag | nosis .   |                                                   | 42  |

|   | 4.1  | PSIx c    | output voltage clamping circuit                   | 42  |

|   | 4.2  | PSIx c    | output under voltage monitoring                   | 42  |

|   | 4.3  | PSIx s    | short circuit detection                           | 43  |

|   | 4.4  | PSIx r    | everse voltage monitoring                         | 44  |

|   | 4.5  |           | nder/over voltage monitoring                      |     |

|   | 4.6  |           | oring of Synchronous Pulse amplitude              |     |

| 5 | Com  | munica    | ation interface                                   | 47  |

|   | 5.1  | Device    | e registers                                       | 47  |

|   | 5.2  | SPI in    | terface                                           | 82  |

|   |      | 5.2.1     | Physical layer and signal description             | 82  |

|   |      | 5.2.2     | Clock and data characteristics                    | 83  |

|   |      | 5.2.3     | Frame definition                                  | 84  |

|   |      | 5.2.4     | Communication frames                              | 84  |

|   | 5.3  | Direct    | interface                                         | 87  |

| 6 | Elec | trical cl | naracteristics                                    | 88  |

|   | 6.1  | SPI in    | terface                                           | 96  |

| 7 | Erra | ta        |                                                   | 99  |

| 8 | Pack | kage inf  | formation                                         | 100 |

|   | 8.1  | TQFP:     | 32 (7x7x1.0 mm exp. pad down) package information | 100 |

|   | 8.2  | VFQF      | PN-28 (5x5x1.0 mm) package information            | 102 |

| 9 | Revi | sion his  | story                                             | 104 |

List of tables L9663

## List of tables

| Table 1.  | Device summary                                            | 1   |

|-----------|-----------------------------------------------------------|-----|

| Table 2.  | VQFPN28 pin-out                                           | 9   |

| Table 3.  | TQFP32 pin-out                                            | 11  |

| Table 4.  | Pin maximum ratings                                       | 13  |

| Table 5.  | Time (t0-t2) vs SensorData                                | 30  |

| Table 6.  | Error codes in sensor communication                       | 31  |

| Table 7.  | Faults priority                                           |     |

| Table 8.  | Time (t0-t7) vs SensorData                                | 32  |

| Table 9.  | Doutx test mode bit value                                 | 39  |

| Table 10. | Operating conditions                                      | 88  |

| Table 11. | VINTx internal supply                                     | 88  |

| Table 12. | V <sub>AS</sub> supply                                    |     |

| Table 13. | V <sub>AS</sub> external MOS                              | 89  |

| Table 14. | V <sub>AS</sub> pre regulator                             | 90  |

| Table 15. | V <sub>SYNCx</sub> · · · · · · · · · · · · · · · · · · ·  | 91  |

| Table 16. | PSI5 output supply                                        | 91  |

| Table 17. | PSI5 receiver                                             | 92  |

| Table 18. | Sync generator                                            | 93  |

| Table 19. | Reset                                                     | 94  |

| Table 20. | VAS under/over voltage monitoring                         | 94  |

| Table 21. | Synchronous pulse amplitude monitoring                    | 95  |

| Table 22. | Time slot monitoring                                      | 95  |

| Table 23. | Digital I/O                                               | 95  |

| Table 24. | Frequency references                                      | 95  |

| Table 25. | SPI communication timing                                  | 97  |

| Table 26. | Direct interface                                          | 97  |

| Table 27. | Errata                                                    | 99  |

| Table 28. | TQFP32 (7x7x1.0 mm exp. pad down) package mechanical data | 101 |

| Table 29. | VFQFPN-28 (5x5x1.0 mm) package mechanical data            | 102 |

| Table 30  | Document revision history                                 | 104 |

L9663 List of figures

# List of figures

| -ıgure 1.  | Simplified block diagram                                                                     |    | 6   |

|------------|----------------------------------------------------------------------------------------------|----|-----|

| igure 2.   | VQFPN28 pins connection diagram (top view)                                                   |    | 9   |

| igure 3.   | TQFP32 pins connection diagram (top view)                                                    | 1  | 1   |

| igure 4.   | Detailed block diagram                                                                       | 1  | 4   |

| igure 5.   | Supply line model for PSI5                                                                   | 1  | 5   |

| igure 6.   | Power-up sequence of transceiver IC                                                          | 1  | 6   |

| igure 7.   | Internal power supply and reset generation                                                   | 1  | 7   |

| igure 8.   | Input structure of supply                                                                    | 1  | 7   |

| igure 9.   | V <sub>AS</sub> application diagram                                                          | 1  | 9   |

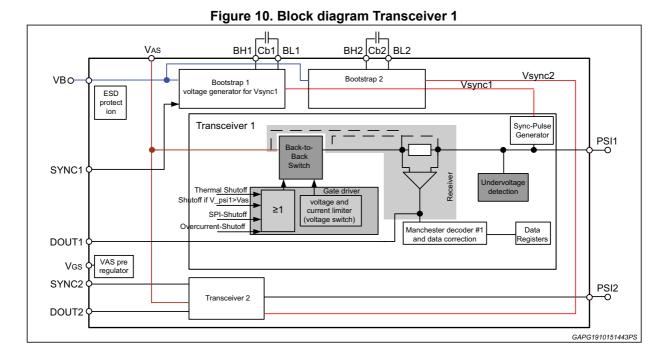

| igure 10.  | Block diagram Transceiver 1                                                                  | 2  | 1:1 |

| igure 11.  | Internal oscillator vs external clock frequency                                              | 2  | 23  |

| igure 12.  | FLL clock error detection                                                                    | 2  | :3  |

| Figure 13. | Block diagram of incoming data buffer                                                        |    |     |

| igure 14.  | PSI5 v1.3 frame                                                                              |    |     |

| Figure 15. | PSI5 v2.0 frame                                                                              |    |     |

| Figure 16. | Sensor buffer in synchronous mode diagram                                                    | 3  | 0   |

| igure 17.  | Sensor buffer in asynchronous mode diagram                                                   |    |     |

| igure 18.  | Block diagram with interrupt pins                                                            |    |     |

| Figure 19. | Timing diagram                                                                               |    |     |

| igure 20.  | ECU to sensor communication diagram                                                          |    |     |

| igure 21.  | Short (in case 1 $\mu$ s < $t_w$ < 5 $\mu$ s) Sync Pulse trigger, compliant to PSI5 standard | 3  | 8   |

| igure 22.  | Timing for PSIx under voltage detection                                                      |    |     |

| igure 23.  | Timing for PSIx reverse voltage detection                                                    |    |     |

| igure 24.  | Timing for V <sub>AS</sub> under voltage detection                                           |    |     |

| igure 25.  | Timing for sync pulse voltage monitoring                                                     |    |     |

| igure 26.  | SPI interface                                                                                |    |     |

| igure 27.  | Operation on internal register (with upstream data buffer)                                   |    |     |

| igure 28.  | Init data reading                                                                            |    |     |

| igure 29.  | Sensor data reading                                                                          |    |     |

| igure 30.  | Sync generator                                                                               |    |     |

| igure 31.  | SPI communication timing diagram                                                             |    |     |

| igure 32.  | TQFP32 (7x7x1.0 mm exp. pad down) package outline                                            |    |     |

| igure 33.  | VFQFPN-28 (5x5x1.0 mm) package outline                                                       | 10 | 2   |

L9663 **Overall description**

## **Overall description**

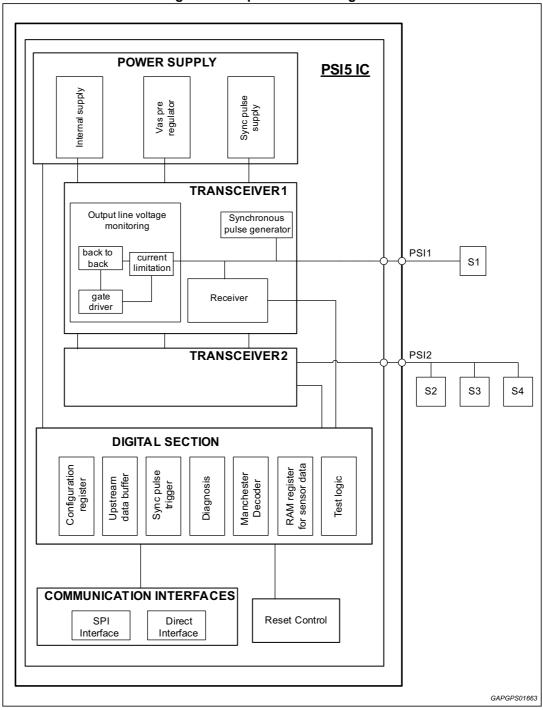

#### 1.1 Simplified block diagram

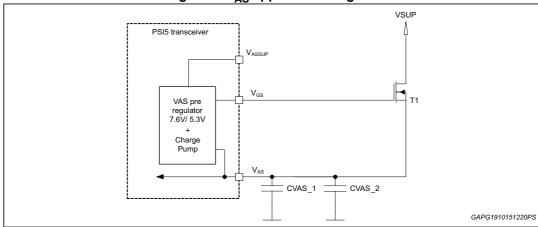

Figure 1. Simplified block diagram

L9663 Overall description

### 1.2 Main functionality

The transceiver IC can be used in two different modes (Mode 1 or Mode 2)<sup>(a)</sup>. The system configuration called Mode 1 performs the decoding effort of sensor signals in the IC. The system configuration called Mode 2 is a frontend to a PSI5 decoder contained in an external device (typically a  $\mu$ C with a dedicated module).

The transceiver IC can monitor all internally generated relevant voltages, such as  $V_{SYNCx}$   $V_{AS}$  and  $V_{PSIx}$ .

The PSI5 interfaces inside the IC are supplied by a separate input pin VAS. If only asynchronous mode is required, the VAS voltage is sufficient for the sensor power supply. When synchronous mode is required, a higher voltage than VAS is needed in order to generate the synchronous pulses. This voltage VSYNCx is generated by a dedicated bootstrap circuit for each channel.

For direct supply from battery, the transceiver IC includes a  $V_{AS}$  pre-regulator supplied by VASSUP-pin: the pre-regulator can drive an external FET to regulate the VAS voltage to 7.6 V or 5.3 V. In case of low voltage level at VASSUP, an integrated charge pump is implemented, with supply from VASSUP.

The internal analog and digital circuits are supplied by VB. The external voltage on VDD pin is used to supply the digital output pins; VDD pin can be used to switch the digital outputs from 5 V output level (default) to 3.3 V output level.

The PSI5 transceiver is functional in the whole  $V_{DD}$ , VB, VASSUP and  $V_{AS}$  power supply range.

The internal voltage supplies (V<sub>SYNCx</sub>) are automatically activated by the transceiver IC depending on the operating mode whenever they are needed.

Each transceiver interface can be activated and deactivated by an SPI command. At startup, the interfaces are off by default.

The communication interface block includes two different interfaces. In mode 1, SPI is used for data transfer. In mode 2, the direct interface is used. The data from and to the sensors will be transmitted bit-wise between the transceiver IC and the  $\mu$ C. The data evaluation and error handling for frame errors will be done in the PSI5 controller which is integrated in the  $\mu$ C.

Transceiver 1 and 2 supply the sensors and generate the synchronous pulses for synchronous data transfer (if required) from the sensors to the transceiver and for data transfer from the ECU to the sensors.

A data transfer from the ECU to the sensors can be performed:

- by using sync pulses with different duration (PSI5 2.x standard)

- by masking of sync pulses (PSI5 1.3 and 2.x standard)

The sync pulse trigger can be generated by an SPI command, by a dedicated pin (for connection to the Synchronous Pulse Output Block included in the microcontroller) or by an integrated automatic timer.

a. Mode 1 and Mode 2 are two system architectures which relate on the way L9663 communicates with the microcontroller. Depending on the chosen architecture, the µC must configure the IC with the correct setup.

DocID028693 Rev 3 7/105

Overall description L9663

The Transceivers 1 and 2 limit the current and the PSIx voltage (PSI5-requirement when VAS is too high because of failure in the VAS power supply, less than 11 V in data transmission or less than 16.5 V in sync pulse).

The current modulated signal received from sensor is detected and digitally converted. This sensor data will then either be:

- First Manchester decoded by the Manchester Decoder block with mark space error correction and then transferred to the "receive data buffer" module (Mode 1). The data from the new sensor frames will be saved in a buffer and then will be transferred to the μC via SPI.

- Transferred directly to the µC (Mode 2). In this case the output of the transceiver is a Manchester-coded signal without error correction that falls under microcontroller responsibility.

L9663 Overall description

### 1.3 VQFPN28 pins description

RESETN VINTD DGND Σ CS SYNC1 21 SCLK DOUT1 20 MOSI 2 CLKIN 3 19 NC SYNC2 4 18 VGS 17 DOUT2 5 VASSUP 6 **16** VΒ NC BH1 15 BH2 GAPGPS01664

Figure 2. VQFPN28 pins connection diagram (top view)

Table 2. VQFPN28 pin-out

| Pin | Pin Name Description Pin type |                                                                            |                  |        |  |  |

|-----|-------------------------------|----------------------------------------------------------------------------|------------------|--------|--|--|

| 1   | SYNC1                         | Direct interface sync pulse trigger 1                                      | ı                | local  |  |  |

|     |                               | ,                                                                          | '                | iocai  |  |  |

| 2   | DOUT1                         | Direct interface 1/Interrupt 1                                             | 0                | local  |  |  |

| 3   | CLKIN                         | External clock input                                                       | I                | local  |  |  |

| 4   | SYNC2                         | Direct Interface sync pulse trigger 2                                      | 1                | local  |  |  |

| 5   | DOUT2                         | Direct interface 2/Interrupt 2                                             | 0                | local  |  |  |

| 6   | NC <sup>(1)</sup>             | -                                                                          | -                | -      |  |  |

| 7   | BH1                           | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 1 | I/O              | local  |  |  |

| 8   | BL1                           | Bootstrap capacitor pin 2, transceiver 1                                   | I/O              | local  |  |  |

| 9   | GND1                          | Ground return for PSI5 interface (analog ground and substrate ground)      | round and supply |        |  |  |

| 10  | PSI1                          | PSI5 Interface 1                                                           | I/O              | global |  |  |

| 11  | V <sub>AS</sub>               | PSI5 Interface pre-regulated voltage supply                                | supply           | local  |  |  |

| 12  | PSI2                          | PSI5 Interface 2                                                           | I/O              | global |  |  |

| 13  | GND2                          | Ground return for PSI5 interface (analog ground and substrate ground)      | supply           | local  |  |  |

| 14  | BL2                           | Bootstrap capacitor pin 2, transceiver 2                                   | I/O              | local  |  |  |

| 15  | BH2                           | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 2 | I/O              | local  |  |  |

Overall description L9663

Table 2. VQFPN28 pin-out (continued)

| Pin | Name               | Description Pin type                             |        | type   |

|-----|--------------------|--------------------------------------------------|--------|--------|

| 16  | V <sub>B</sub>     | Input voltage supply                             | supply | global |

| 17  | V <sub>ASSUP</sub> | VAS pre-regulator and charge pump voltage supply | supply | global |

| 18  | V <sub>GS</sub>    | Gate driver for V <sub>AS</sub> pre-regulator    | I/O    | local  |

| 19  | NC <sup>(2)</sup>  | -                                                | -      | -      |

| 20  | MOSI               | SPI input                                        | I      | local  |

| 21  | SCLK               | SPI Clock                                        | I      | local  |

| 22  | CS                 | SPI Chip Select                                  | I      | local  |

| 23  | RESETN             | Reset                                            | I      | local  |

| 24  | TM                 | Test-mode pin <sup>(3)</sup>                     | I      | local  |

| 25  | V <sub>INTD</sub>  | Internal digital supply voltage                  | supply | local  |

| 26  | DGND               | Digital ground                                   | supply | local  |

| 27  | V <sub>DD</sub>    | Digital I/O supply                               | supply | local  |

| 28  | MISO               | SPI output                                       | 0      | local  |

<sup>1.</sup> Not connected internally, must be left open.

<sup>2.</sup> Not connected internally, it can be connected to GND externally.

<sup>3.</sup> It must be connected to GND, for safety reasons.

L9663 Overall description

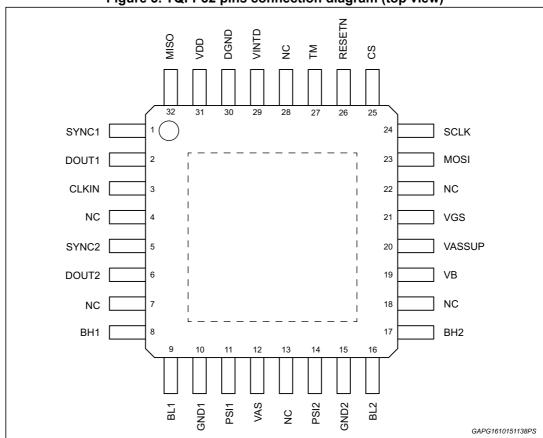

### 1.4 TQFP32 pins description

Figure 3. TQFP32 pins connection diagram (top view)

Note:

The exposed pad is electrically shorted to the substrate and to pins GND1 and GND2. These three nodes have to be kept shorted on the application.

Table 3. TQFP32 pin-out

| Pin | Name              | Description                                                                | Pin type |       |

|-----|-------------------|----------------------------------------------------------------------------|----------|-------|

| 1   | SYNC1             | Direct interface sync pulse trigger 1                                      | I        | local |

| 2   | DOUT1             | Direct interface 1/Interrupt 1                                             | 0        | local |

| 3   | CLKIN             | External clock input                                                       | I        | local |

| 4   | NC <sup>2</sup>   | -                                                                          | -        | -     |

| 5   | SYNC2             | Direct Interface sync pulse trigger 2                                      | I        | local |

| 6   | DOUT2             | Direct interface 2/Interrupt 2                                             | 0        | local |

| 7   | NC <sup>(1)</sup> | -                                                                          | -        | -     |

| 8   | BH1               | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 1 |          |       |

| 9   | BL1               | Bootstrap capacitor pin 2, transceiver 1                                   | I/O      | local |

Overall description L9663

Table 3. TQFP32 pin-out (continued)

| Pin | Name               | Description                                                                | Pin type |        |

|-----|--------------------|----------------------------------------------------------------------------|----------|--------|

| 10  | GND1               | Ground return for PSI5 interface (analog ground and substrate ground)      | supply   | local  |

| 11  | PSI1               | PSI5 Interface 1                                                           | I/O      | global |

| 12  | V <sub>AS</sub>    | PSI5 Interface pre-regulated voltage supply                                | supply   | local  |

| 13  | NC <sup>(2)</sup>  | -                                                                          | -        | -      |

| 14  | PSI2               | PSI5 Interface 2                                                           | I/O      | global |

| 15  | GND2               | Ground return for PSI5 interface (analog ground and substrate ground)      | supply   | local  |

| 16  | BL2                | Bootstrap capacitor pin 2, transceiver 2                                   | I/O      | local  |

| 17  | BH2                | Bootstrap capacitor pin 1 or SYNC voltage supply (from ECU), transceiver 2 | I/O      | local  |

| 18  | NC <sup>(1)</sup>  | -                                                                          | -        | -      |

| 19  | V <sub>B</sub>     | Input voltage supply                                                       | supply   | global |

| 20  | V <sub>ASSUP</sub> | VAS pre-regulator and charge pump voltage supply                           | supply   | global |

| 21  | V <sub>GS</sub>    | Gate driver for V <sub>AS</sub> pre-regulator                              | I/O      | local  |

| 22  | NC <sup>2</sup>    | -                                                                          | -        | -      |

| 23  | MOSI               | SPI input                                                                  | I        | local  |

| 24  | SCLK               | SPI Clock                                                                  | I        | local  |

| 25  | CS                 | SPI Chip Select                                                            | I        | local  |

| 26  | RESETN             | Reset                                                                      | I        | local  |

| 27  | TM                 | Test-mode pin <sup>(3)</sup>                                               | I        | local  |

| 28  | NC <sup>(2)</sup>  | -                                                                          | -        | -      |

| 29  | V <sub>INTD</sub>  | Internal digital supply voltage                                            | supply   | local  |

| 30  | DGND               | Digital ground                                                             | supply   | local  |

| 31  | $V_{DD}$           | Digital I/O supply                                                         | supply   | local  |

| 32  | MISO               | SPI output                                                                 | 0        | local  |

<sup>1.</sup> Not connected internally, must be left open.

<sup>2.</sup> Not connected internally, it can be left open or connected to GND externally.

<sup>3.</sup> It must be connected to GND, for safety reasons.

L9663 Overall description

## 1.5 Maximum ratings

Within the maximum ratings, no damage to the component shall occur. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

All maximum ratings can occur at the same time.

All analog voltages are related to the potential at substrate ground (GND1 and GND2, internally shorted), all digital voltages are related to DGND.

Operative voltage conditions are specified in Section 6.

Table 4. Pin maximum ratings

| Symbol                                   | Description                                                                                  | Min   | Max                      | Unit |

|------------------------------------------|----------------------------------------------------------------------------------------------|-------|--------------------------|------|

| Power supp                               | ly                                                                                           |       |                          | !    |

| V <sub>B</sub> , V <sub>ASSUP</sub>      | Input voltage range                                                                          | -0.3  | 40                       | V    |

| V <sub>AS</sub>                          | Pre-regulated voltage range                                                                  | -0.3  | 40                       | V    |

| $V_{DD}$                                 | Supply voltage range for digital I/O pins                                                    | -0.3  | 6.5                      | V    |

| V <sub>INTD</sub>                        | Internal digital supply voltage                                                              | -0.3  | 4.6                      | V    |

| BHx, BLx                                 | Voltage range of bootstrap capacitor or SYNC voltage supply (from ECU)                       | -0.3  | 40                       | V    |

| Other pins                               |                                                                                              |       |                          | •    |

| PSI1, PSI2                               | Voltage of sensor interface                                                                  | -1.5  | 40                       | V    |

| $V_{GS}$                                 | Pre-regulator gate voltage range                                                             | -0.3  | 40                       | V    |

| RESETN                                   | Reset input pin range                                                                        | -0.3  | 6.5                      | V    |

| TM                                       | Test mode input pin range                                                                    | -0.3  | 6.5                      | V    |

| CLKIN                                    | Clock input pin range                                                                        | -0.3  | 6.5                      | V    |

| CS, SCLK,<br>MOSI                        | SPI communication pin range                                                                  | -0.3  | 6.5                      | V    |

| MISO                                     | SPI communication pin range                                                                  | -0.3  | V <sub>DD</sub> +0.3≤6.5 | V    |

| D <sub>OUT1</sub> ,<br>D <sub>OUT2</sub> | Direct interface pin range                                                                   | -0.3  | V <sub>DD</sub> +0.3≤6.5 | V    |

| SYNC1,<br>SYNC2                          | Sync pulse trigger input range                                                               | -0.3  | 6.5                      | V    |

| ESD robusti                              | ness                                                                                         |       |                          |      |

| -                                        | ESD according to Human Body Model (HBM), Q100-002 for pins PSIx, VB, VASSUP; (100 pF/1.5 kΩ) | ±4000 | -                        | V    |

| -                                        | ESD according to Human Body Model (HBM), Q100-002 for all other pins; (100 pF/1,5 kΩ)        | ±2000 | -                        | V    |

| -                                        | ESD according to Charged Device Model (CDM), Q100-011 Corner pins                            | ±750  | -                        | V    |

| -                                        | ESD according to Charged Device Model (CDM), Q100-011 Non-corner pins                        | ±500  | -                        | V    |

Overall description L9663

Table 4. Pin maximum ratings (continued)

| Symbol         | Description                                    |     | Max | Unit |  |

|----------------|------------------------------------------------|-----|-----|------|--|

| Temperature    |                                                |     |     |      |  |

| T <sub>a</sub> | Ambient operating temperature range            | -40 | 140 | °C   |  |

| T <sub>j</sub> | Junction operating temperature range           | -40 | 175 | °C   |  |

| Rthja          | Package thermal resistance (on PCB JEDEC 2s2p) |     | 45  | °C/W |  |

The device offers a high level of flexibility on power supply configuration. The calculated maximum power dissipation can reach 1.6 W considering the worst case configuration.

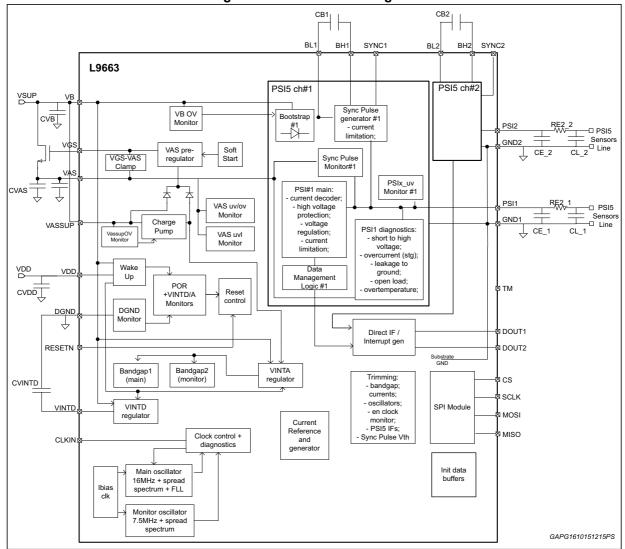

### 1.6 Detailed block diagram

Figure 4. Detailed block diagram

L9663 Overall description

The high supply voltage of the IC can be a battery or a regulated voltage provided by the ECLI

To reduce disturbances on the voltage supply which might have a negative influence on the PSIx interface and therefore lead to bit errors, a PI filter can be employed in the supply line.

Possible power supply configurations<sup>(b)</sup> are:

- VB, VASSUP connected to VSUP, VAS and V<sub>SYNCx</sub> generated by the IC with external components (as in the above figure);

- VAS, VB, VASSUP connected to VSUP, V<sub>SYNCx</sub> generated by bootstrap, no external MOS, VGS pin open;

- VB, VASSUP, BH1, BH2 connected to VSUP, no external capacitors CBx, VAS generated by IC pre-regulator and external MOS;

- VB connected to VSUP, VASSUP connected to 0V (charge pump off), VAS supplied by an external source and VSYNCx generated by the IC with external components.

The values of the external components RE2\_x, CE\_x and CL\_x are specified in PSI5 standard.

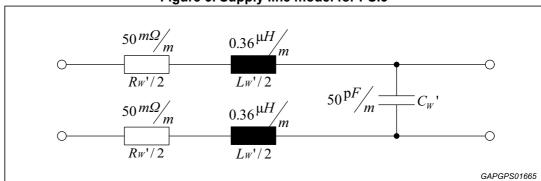

The assumed line model for the PSI5 interface on which the transceiver IC operates is as follows:

Figure 5. Supply line model for PSI5

b. The high supply voltage VSUP must be in the correct operative range of connected pins.

DocID028693 Rev 3

Overall description L9663

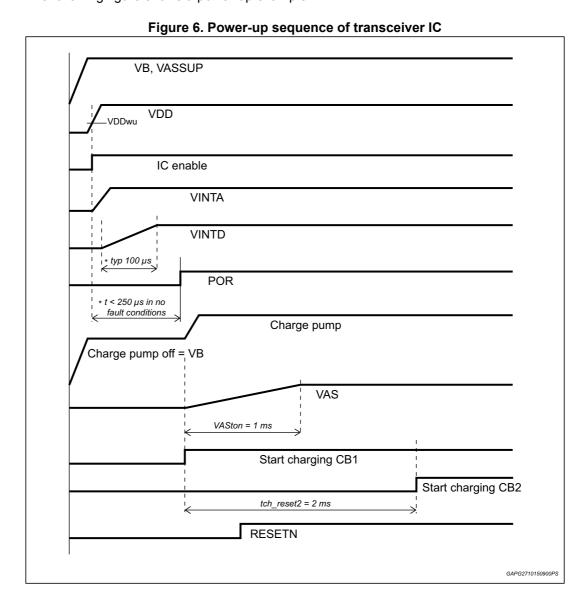

#### 1.7 Power up sequence

When VDD is higher than the startup threshold and VB is available the IC is switched on.

To reduce disturbances on its voltage supply, the transceiver IC does a staggered startup of its internal voltage supplies.

While RESETN is low, the PSIx lines are deactivated to reduce power consumption and to increase system safety.

The transceiver IC can be configured to operate in the standard current mode (4 mA up to 19 mA) or in the extended current mode (4 mA up to 35 mA). Moreover, both channels can be configured to allow the extension to a maximum quiescent current of 45 mA, only in case of asynchronous mode.

The synchronous sensors send data only after a synchronous pulse is triggered via the dedicated pin or by SPI.

The following figure shows a power-up example.

L9663 Power supply

### 2 Power supply

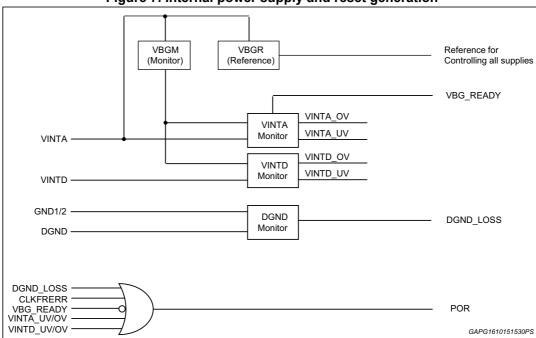

#### 2.1 Internal supply

The internal analog and digital part is supplied by the supply voltage VB. The necessary power supply for the internal digital and analog parts is generated internally by the transceiver IC. The generated voltage is monitored. In case of under/over voltage, the transceiver IC performs a power on reset (POR).

Figure 7. Internal power supply and reset generation

#### Basic features:

- Voltage regulator

- Under / Over voltage monitoring

- Reset generation of the IC in case of under / over voltage

Power supply L9663

A ceramic capacitor with a typical capacitance of 100 nF is required as a blocking capacitor close to the pins  $V_{DD}$  and VB.

The internal supply voltages  $V_{INTD}$  (supply voltage for digital part) and  $V_{INTA}$  (supply voltage for analog part) are monitored for under voltage and over voltage to prevent the transceiver IC from malfunction. The reference for the voltage monitoring is a bandgap voltage, supplied by  $V_{INTA}$ . The device integrates two separated instances of bandgap voltage regulators; one of these bandgaps is used as voltage reference for the internal regulators, while the other one is used for monitoring the voltage levels. In case of under or over voltage, the transceiver IC is set into reset: outside reset thresholds full functionality is granted.

The functionality of the digital part only depends on the voltages on  $V_{\text{INTD}}$ . In order to improve noise emissions and stability of the regulator, the digital supply line needs an external decoupling 100 nF ceramic capacitor to be connected between  $V_{\text{INTD}}$  and DGND and close to them.

DGND ground line is protected against ground loss scenarios. In case DGND line would be at least DGND<sub>OPEN</sub> above the reference ground lines GND1/2, a POR is asserted.

The transceiver IC returns to normal operation with full functionality as soon as the POR is released.

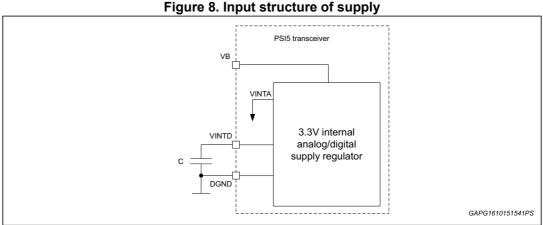

### 2.2 V<sub>AS</sub> supply and pre-regulator

The  $V_{AS}$  pre-regulator sets the  $V_{AS}$  voltage if no regulated voltage with the necessary value is available in the ECU.

The pre-regulator is designed for two different regulated voltages at  $V_{AS}$ : 5.3 V or 7.6 V, selectable by a SPI command. The supply of external FET can be chosen at application level according to the required voltage at VAS pin.

Two possible applications are:

- V<sub>AS</sub> typical of 5.3 V; external FET supplied by ECU internal voltage, typically 6 V.

- V<sub>AS</sub> typical of 7.6 V; external FET directly supplied from battery, from 8 V to 35 V.

#### Basic features:

- Gate control for an external n-ch FET transistor with integrated charge pump stage

- Gate control is switched on if no power on reset condition is present

- Configurable output voltage: either 5.3 V or 7.6 V.

L9663 Power supply

Figure 9. V<sub>AS</sub> application diagram

When POR is active, the  $V_{GS}$  output pin is driven low to keep external N-ch switched off. The  $V_{AS}$  pre-regulator is automatically activated with a soft start at POR and automatically switched off, after a filter time, if  $V_{AS}$  falls below  $V_{VASU\_off}$ . It can be later controlled off or on by means of a dedicated VAS\_EN bit. To protect the external component from exceeding maximum allowed gate to source voltage if VAS is shorted to ground by a fault, an internal passive clamp is implemented on  $V_{GS}$ .

The integrated charge pump, supplied by VASSUP, assures proper voltage regulation in case of low voltage conditions. It is automatically switched off in case the voltage on  $V_{ASSUP}$  is high enough to allow proper regulation.

If the pre-regulator is not needed, the VAS\_EN bit can be set to '0' to switch off the pre-regulator itself. The pin  $V_{GS}$  can be left open, and the  $V_{AS}$  pin directly connected to the regulated voltage in the ECU.

The pre-regulator is active independently of RESETN input pin if the supply voltage of the internal analog/digital circuits is available.

### 2.3 Voltage supply for synchronous pulse generation V<sub>SYNCx</sub>

To use synchronous PSI5 sensors and for ECU-to-sensor communication, the transceiver IC needs to generate synchronization pulses. These require a voltage which is higher than  $V_{AS}$ .

This module generates the necessary voltage  $V_{SYNCx}$  by two bootstrap circuits. Two capacitors with two transceiver IC pins each are used as external components of this module.

The bootstrap blocks start pre-charging the external capacitors after POR (with a 2 ms time gap between the first and second block).

The bootstrap circuits are enabled by default, activated by internal logic with timing sync pulses dependent, and can be disabled later on through a dedicated SPI command. The bootstrap block can recharge the capacitor so that subsequent sync pulses are allowed with a minimum period of 200  $\mu$ s.

A useful option is the possibility to connect the BHx pin directly to a high voltage rail. In this configuration, VB has also to be connected to the same high voltage rail and the bootstrap

Power supply L9663

circuit can be bypassed by disabling it through the dedicated SPI command (bit 12 of CH1 CR2, CH2 CR2, writable during PROG phase).

The bootstrap blocks are automatically switched off in case the voltage on VB is high enough to allow proper regulation. In this case both CBx capacitors should be omitted.

The  $V_{SYNCx}$  voltage can supply a 2.5 V minimum sync pulse as per PSI5 v2.x low power mode down to  $V_B$  = 4.8 V and a 3.5 V minimum sync pulse down to  $V_B$  = 5.2 V, with a maximum quiescent current level of 35mA and down to minimum 200  $\mu$ s period between sync pulses. The block is protected against reverse feeding to  $V_B$ .

The bootstrap module is fully functional while V<sub>B</sub> and V<sub>DD</sub> are all inside their specified voltage ranges.

#### 2.4 Power supply for PSI5 sensor line

Basic features:

- Reverse voltage protection structure

- Voltage limitation and current limitation for PSIx input/output

- Protection against negative voltages on PSIx transceiver pin due to ground shifts

- Disconnection of PSIx from V<sub>AS</sub> in failure cases

The PSI5 transceiver IC is supplied directly from the pin  $V_{AS}$ . It includes blocks with the following functionalities:

- Reverse voltage protection structure and gate driver block for

- Voltage clamp on PSIx in case of V<sub>AS</sub> fault

- Backward voltage supply blocking mechanism from PSIx to V<sub>AS</sub>

- Sensor supply by switching V<sub>AS</sub> to the PSIx pin

- Disconnection of PSIx from the VAS if required or in failure cases

- Under voltage detection block to implement cross coupling test between the two channels (see Section 3.7.5 and 4.2)

- Receiver block for Sensor Data receive (see Section 3.1 for details).

The reverse voltage protection structure is also used to switch off the PSIx transceiver channel, if:

- the local junction temperature exceeds its maximum rating and the channel is in overcurrent

- an overcurrent condition on PSIx is detected (STG)

- a short to battery is detected

- it is requested via SPI or RESETN pin.

In case of short to battery on the PSIx lines, there is no interference to any other IC pin/supply including SPI.

The two interfaces can be enabled by SPI command, and the enable has effect only if VAS under voltage signals are not asserted.

If an over temperature condition (OT) occurs, the interface that is also in overcurrent condition is switched off and a failure bit is set. The fault bit is latched and cleared only when a SPI switch off command is sent for confirmation on the line that was automatically switched off. The shutoff of one interface does not affect the second interface.

577

L9663 Power supply

If an overcurrent condition on PSIx is detected, the current limitation is active and after a filter time  $t_{\text{filt}}$  a fault bit is set and the interface is shut off. In order to switch on again, the interface must be first switched off by SPI and then switched on, as for over temperature.

The channels' switch off by overcurrent can be disabled if the corresponding bits STG MASK for every channel are set in the SPI registers.

During start up, a configurable blanking time is implemented (128  $\mu$ s/5 ms/10 ms, see BLANKING\_SEL bits in SPI register); during this time current limitation is active, even though the interface will not shut off for overcurrent, thermal shutdown is always active, the PSI5 receiver is disabled, and some fault flags are masked (short to battery, under voltage, leakage to ground).

The quiescent current is monitored for minimum and maximum value, depending on the range selected by SPI (CH1\_CR1, QC\_SEL bits). In failure case the corresponding bit in the diagnostic register is set (SR2).

The voltage at PSIx is compared with VAS to monitor short to battery condition: if an over voltage occurs PSIx is disconnected from VAS and the corresponding bit in diagnostic register is set (STBx in SR2), In over voltage condition also low quiescent current bit is set (OLx in SR2) after a transient time.

Power supply L9663

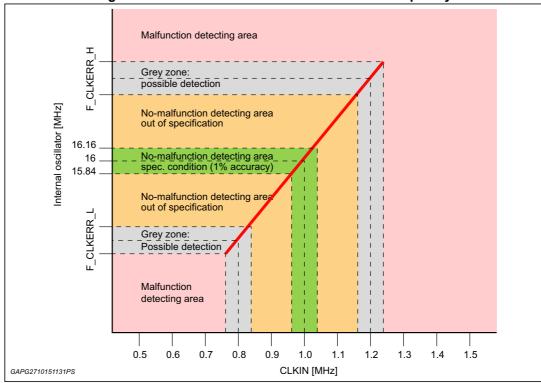

#### 2.5 Frequency references

The device comes with an integrated accurate oscillator, used for any of the internal circuitry, with no need of external connections or components. The nominal clock frequency is 16 MHz with a ±5% accuracy.

Should the application need some more accurate timing reference, a discrete pin CLKIN is provided. An external clock reference can be connected to this pin. The PSI5 transceiver IC offers an integrated FLL module that tracks this input to provide a high accurate clock reference (±1%). This feature can be used especially if accurate timeslot control needs to be achieved.

External signal on CLKIN can be configured as follows (see CLKIN\_CFG bits in GCR1 SPI register):

- 1 MHz square signal

- 4 MHz square signal

- No signal (Not connected pin)

Pin CLKIN can be grounded when not used. The pin input circuit implements a pull-down structure.

The FLL module tracking the CLKIN signal is off by default.

The PSI5 transceiver IC implements a safety function for monitoring the device clock reference, both in case it is derived from the CLKIN signal through the FLL module or internally generated. In the first condition the monitoring is always activated, while in the second condition it can be enabled by programming in ST (storing a '1' in a dedicated OTP<sup>(c)</sup> bit) and another oscillator generator is used for monitoring.<sup>(d)</sup>

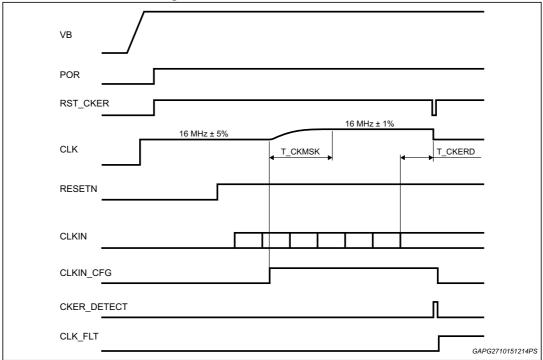

When the CLKIN\_CFG is set, the FLL tries to close the LOOP and a mask counter of T\_CKMSK (16 ms MAX) is used to count the maximum transient time.

During this time, regardless the CLK frequency the CKER\_DETECT is masked, i.e the device doesn't detect a clock error.

After this time, if the CLKIN frequency is in the correct range, the loop is closed and the CLK frequency is inside the 1% tolerance; if the CLKIN frequency is outside the malfunction detecting range, a clock error is detected after a detection time  $T_CKERD$ , the device is reset and the  $CLK_FLT$  is set so that the  $\mu C$  can read the reset source.

The T\_CKERD and the transient during detection time depend on the CLKIN frequency behavior; the figure below shows the behavior of the internal oscillator as function of the external one.

22/105 DocID028693 Rev 3

c. One Time Programmable bit: it can be programmed by ST only.

d. For clock error detection by internal monitor oscillator see errata n.3367, Section 7: Errata.

L9663 Power supply

Figure 11. Internal oscillator vs external clock frequency

If the CLKIN is stuck the device behavior is shown in the figure below: in this case during the detection time the tolerance is still inside the 1% tolerance until the device enters reset (T\_CKERD max 260  $\mu$ s).

Figure 12. FLL clock error detection

Power supply L9663

#### 2.6 Reset handling

Four different sources are considered in resetting the IC:

- POR (Power On Reset, see Section 2.1)

- RESETN pin

- SW\_RESET

- CKER\_DETECT

All these sources of reset, when asserted, will switch off the PSIx lines and reset to default value the device registers (including those registers for configuration).

Additionally to the hardware resets (by pin/POR), a reset can also be initiated by software (SW\_RESET).

The command SW\_RESET initiates a soft reset-sequence if all of the following conditions are fulfilled (see also the DCR register in SPI section):

- unlocked state: it means that if the UNLOCK command is not received the command SW\_RESET has no effect;

- The command SW\_RESET is sent in next SPI communication of the unlock command.

A SW\_RESET initiates soft reset-sequence and resets all digital parts of the device, except POR and RST flag that is set in SR3 register.

L9663 Satellite interface

#### 3 Satellite interface

#### 3.1 Receiver with digital sampling and filtering

This module has the following features:

- The output current signal is mirrored and converted to the digital domain

- Automatic synchronization on entire PSI5 frames

- Fast DAC digital conversion of sensed currents with digital filtering

- Static DC current set point tracking of PSI5 guiescent current.

- Tracking of modulated PSI5 current signal

The quiescent current tracking can be configured to work in two ways (reg. ADVSET1, ADVSET3, bits FREEZE\_DIS): continuous mode tracking or tracking between consecutive frames till the first edge of a new frame is recognized. In the second case, the quiescent current is frozen till the end of the frame.

To recognize the PSI5 current signal level the receiver compares the digitally converted and filtered current with a threshold. This threshold can be fixed or dynamic, depending on the configuration selected by SPI (reg. ADVSET).

In fixed threshold mode the user must program the right delta current threshold, according to the application requirements. The threshold is obtained as tracked quiescent current plus the programmed threshold.

In dynamic threshold mode, the threshold is dynamically adapted considering the PSI5 current input signal.

For detailed explanation on all the possible configurations refer to ADVSET registers section.

Depending on the selected configuration, the threshold for the sensor signal can be permanently tracked, separately for each PSI5 interface. The IC is designed to compensate erratic changes of the quiescent current in the bus according to PSI5 standard requirements.

The v2.x standard low power mode is not supported with dynamic threshold mode.

Micro cuts up to 10µs do not affect the DC current tracking in a way that more than one frame will be lost.

The PSI5 Receiver is designed to operate at:

- 83.3 Kbps typical (slow mode)

- 125 Kbps typical (standard mode)

- 189 Kbps typical (fast mode).