Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Single and dual PMOS high-side H-bridge

#### Datasheet - production data

#### **Features**

- Full path R<sub>DSON</sub> less than 540 mΩ

- Continuous load current > 3 A

- Operating battery supply voltage 5 V to 28 V

- Operating V<sub>DD</sub> supply voltage 4.5 V to 5.5 V

- All ECU internal pins can withstand up to 18 V

- Output switching frequency up to 11 kHz

- Monitoring of V<sub>DD</sub> supply voltage

- SPI programmable output current limitation from 5 A to 8.6 A (in 3 steps)

- Over temperature and short circuit protection

- Full diagnosis capability

- Fast switch-off open-drain input/output

- Current-monitoring with current feedback output signal CF

- SPI-interface for configuration and diagnosis

- Error history in second diagnosis register

- Two independent enable pins: "/ABE" and "DIS"

- Control of power stages by SPI or two input signals, PWM and DIR (configurable via SPI)

- Logic levels 5 V compatible

- Conformity to improved EMC requirements due to smart H-bridge switching

#### **Description**

L9959S/L9959U and L9959T are single and dual integrated H-bridges for resistive and inductive loads featuring output current direction and supervising functions.

The PowerSSO24 houses one full H-Bridge, while the PowerSSO36 houses both two H-Bridges that can work in parallel, through independent input driving commands, and one full H-bridge, by improving PCB footprint design versus different target applications.

Target application ranges from throttle control actuators to exhaust gas recirculation control valves in automotive domain to a more general use to drive DC and Stepper motors.

Table 1. Device summary

| Order code  | Package    | Packing     |

|-------------|------------|-------------|

| L9959S-TR-D | PowerSSO24 | Tape & Reel |

| L9959T-TR-D | PowerSSO36 | Tape & Reel |

| L9959U-TR-D | PowerSSO36 | Tape & Reel |

Contents L9959

## **Contents**

| 1 | Bloc  | k diagram                                              | 3 |

|---|-------|--------------------------------------------------------|---|

| 2 | Pins  | description                                            | 7 |

|   | 2.1   | Pin definitions and functions                          | 3 |

| 3 | Elect | trical specifications13                                | 3 |

|   | 3.1   | Absolute maximum ratings                               | 3 |

|   | 3.2   | ESD protection                                         | 3 |

|   | 3.3   | Thermal data                                           | 1 |

|   | 3.4   | Electrical characteristics                             | 1 |

|   | 3.5   | Outputs OUT1 and OUT2                                  | 3 |

|   | 3.6   | Temperature dependent current reduction                | J |

|   | 3.7   | Free-wheeling diodes                                   | J |

|   | 3.8   | SPI / logic electrical characteristics                 | 1 |

| 4 | Appl  | ication information                                    | 3 |

|   | 4.1   | Power stage switching behavior                         | 3 |

|   |       | 4.1.1 PWM mode (same current direction)                | 3 |

|   |       | 4.1.2 DIR-change mode                                  | 4 |

|   | 4.2   | Protection and monitoring                              | 5 |

|   |       | 4.2.1 Current feedback                                 | 3 |

|   |       | 4.2.2 Current limitation                               | 7 |

|   |       | 4.2.3 Temperature dependent current reduction          | 7 |

|   |       | 4.2.4 Short to battery (SCB) and short to Ground (SCG) | 3 |

|   |       | 4.2.5 Short circuit over load (SCL)                    |   |

|   |       | 4.2.6 Open load (OL)                                   | 9 |

|   | 4.3   | VS-undervoltage                                        | 9 |

|   | 4.4   | Inverse current at V <sub>S</sub> 29                   | 9 |

|   | 4.5   | /ABE pin                                               | ) |

|   | 4.6   | VDD-monitor                                            | ) |

|   | 4.7   | VDD-monitor test                                       | ) |

|   | 4.8   | Power-on reset                                         | 1 |

L9959 Contents

| 5 | SPI  | functior  | nal description                          | 32 |

|---|------|-----------|------------------------------------------|----|

|   | 5.1  | Gener     | al description                           | 32 |

|   |      | 5.1.1     | SPI select (SS)                          | 32 |

|   |      | 5.1.2     | Serial data In (SI)                      | 32 |

|   |      | 5.1.3     | Serial clock (SCK)                       | 32 |

|   |      | 5.1.4     | Serial out (SO)                          | 32 |

|   |      | 5.1.5     | SPI communication flow                   | 32 |

|   | 5.2  | SPI-in:   | struction                                | 33 |

|   | 5.3  | Device    | e register map                           | 34 |

|   | 5.4  | SPI - c   | control and status registers             | 35 |

|   |      | 5.4.1     | Reset sources                            | 40 |

|   |      | 5.4.2     | Configuration registers reset sources    | 40 |

| 6 | Арр  | lication  | circuit                                  | 41 |

| 7 | Pacl | kage inf  | formation                                | 42 |

|   | 7.1  | Power     | SSO-24 (exposed pad) package information | 42 |

|   | 7.2  | Power     | SSO-36 (exposed pad) package information | 45 |

| 8 | Revi | ision his | story                                    | 48 |

List of tables L9959

## List of tables

| Table 1.  | Device summary                                              | 1 |

|-----------|-------------------------------------------------------------|---|

| Table 2.  | L9959S PSSO24 pin-out                                       | 8 |

| Table 3.  | L9959T (Two H-Bridge drivers in one package) PSSO36 pin-out | 9 |

| Table 4.  | L9959U (Single version in PSSO36) pin out                   | 2 |

| Table 5.  | Absolute maximum ratings                                    | 3 |

| Table 6.  | ESD protection                                              | 3 |

| Table 7.  | Thermal data1                                               | 4 |

| Table 8.  | Supply                                                      | 4 |

| Table 9.  | Power-on reset                                              | 5 |

| Table 10. | V <sub>DD</sub> monitoring                                  | 5 |

| Table 11. | Undervoltage shutdown                                       | 6 |

| Table 12. | On-resistance (4.5 V < V <sub>S</sub> < 28 V)               | 6 |

| Table 13. | Power output switching times (8 V < V <sub>S</sub> < 18 V)  | 6 |

| Table 14. | Current feedback (CF)                                       | 8 |

| Table 15. | Current limiting                                            | 9 |

| Table 16. | Over-current detection (8 V < V <sub>S</sub> < 18 V)        | 9 |

| Table 17. | Open-load detection                                         | 0 |

| Table 18. | Retest delay                                                |   |

| Table 19. | Temperature dependent current reduction                     | 0 |

| Table 20. | Free-wheel diodes                                           | 0 |

| Table 21. | Inputs: SI, SS, SCK, DIR, DIS and PWM; Output: SO           | 1 |

| Table 22. | Dynamic characteristics                                     | 2 |

| Table 23. | Device states with respect to supply voltage                | 1 |

| Table 24. | SPI instruction byte                                        | 3 |

| Table 25. | Check byte                                                  | 4 |

| Table 26. | Command overview                                            | 4 |

| Table 27. | Device identifier (ID)                                      | 5 |

| Table 28. | Revision register (REV)                                     | 5 |

| Table 29. | DIA_REG1 3                                                  | 5 |

| Table 30. | Diagnosis bits (DIA_REG1)                                   | 6 |

| Table 31. | Diagnosis register 2 (DIA_REG2)                             | 6 |

| Table 32. | Diagnosis bits (DIA_REG2)                                   |   |

| Table 33. | Configuration register (CONFIG_REG)                         | 7 |

| Table 34. | Current Level (CONFIG_REG)                                  |   |

| Table 35. | Status and configuration register (STATCON_REG)             | 8 |

| Table 36. | Special register (SPECIAL_REG)                              | 9 |

| Table 37. | PowerSSO-24 (exposed pad) package mechanical data           |   |

| Table 38. | PowerSSO-36 (exposed pad) package mechanical data           |   |

| Table 39. | Document revision history                                   | 8 |

L9959 List of figures

# List of figures

| Figure 1.  | Block diagram                                     | 6    |

|------------|---------------------------------------------------|------|

| Figure 2.  | PSSO24 pin connection (top view)                  | 7    |

| Figure 3.  | PSSO36 pin connection (top view)                  |      |

| Figure 4.  | PSSO36 (Single version) pin connection (top view) | 8    |

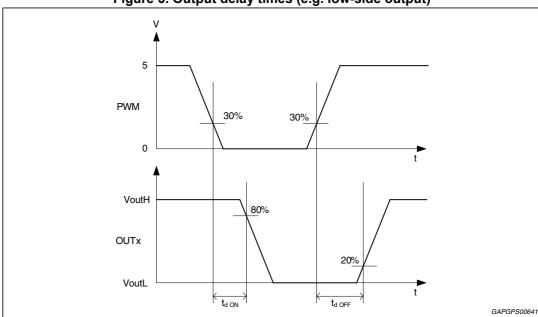

| Figure 5.  | Output delay times (e.g. low-side output)         | . 17 |

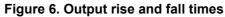

| Figure 6.  | Output rise and fall times                        | . 17 |

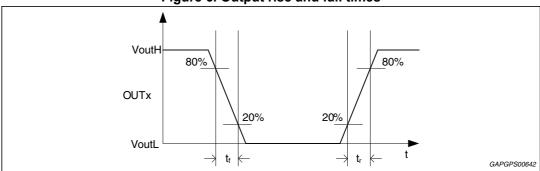

| Figure 7.  | Output disable and enable time (/ABE Input)       | . 17 |

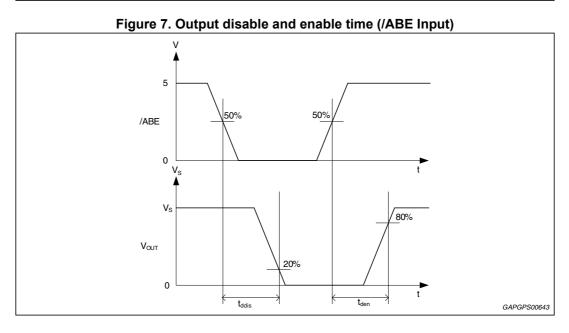

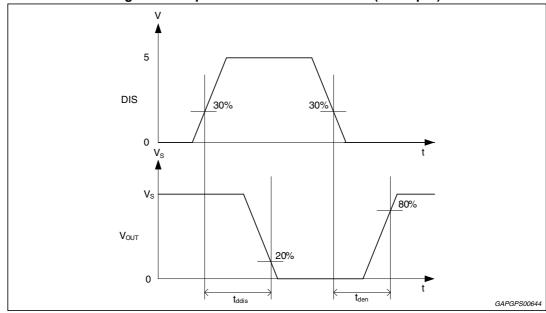

| Figure 8.  | Output disable and enable time (DIS Input)        | . 18 |

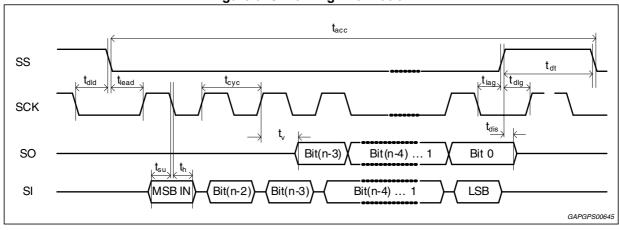

| Figure 9.  | SPI timing information                            |      |

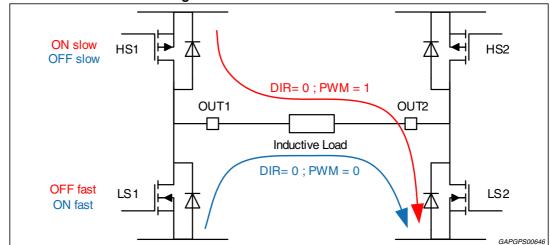

| Figure 10. | PWM mode current flow                             |      |

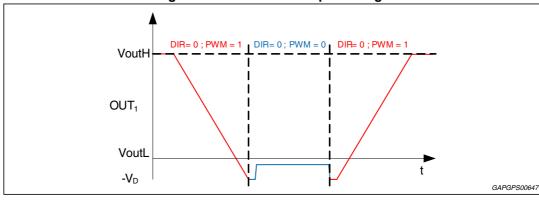

| Figure 11. | PWM mode output voltage                           | . 24 |

| Figure 12. | DIR-change (current is changing its direction)    | . 24 |

| Figure 13. | DIR-change current flow phase 2                   | . 25 |

| Figure 14. | DIR-change output voltage                         |      |

| Figure 15. | Current feedback and current limiting             | . 26 |

| Figure 16. | Current limitation                                |      |

| Figure 17. | Temperature dependent current reduction           |      |

| Figure 18. | Current limiting and short circuit                | . 28 |

| Figure 19. | Write access                                      |      |

| Figure 20. | Read access                                       |      |

| Figure 21. | Application circuit                               | . 41 |

| Figure 22. | PowerSSO-24 (exposed pad) package outline         |      |

| Figure 23. | PowerSSO-36 (exposed pad) package outline         | . 45 |

Block diagram L9959

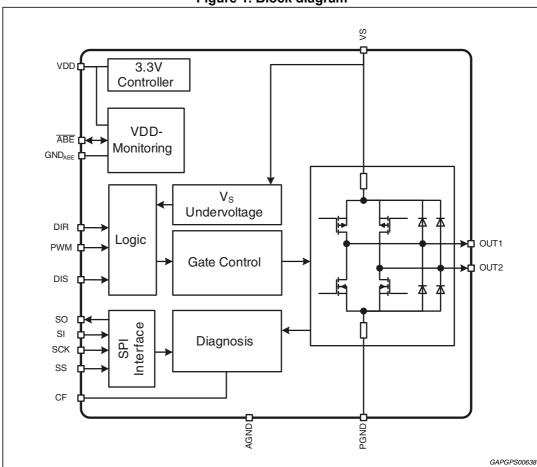

## 1 Block diagram

Figure 1. Block diagram

L9959 Pins description

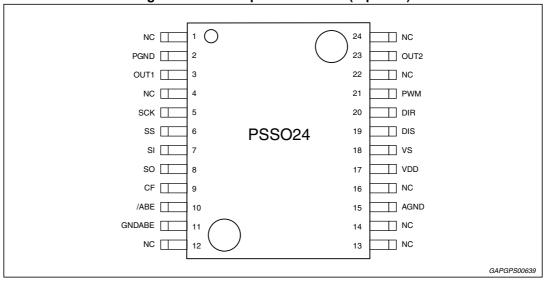

## 2 Pins description

Figure 2. PSSO24 pin connection (top view)

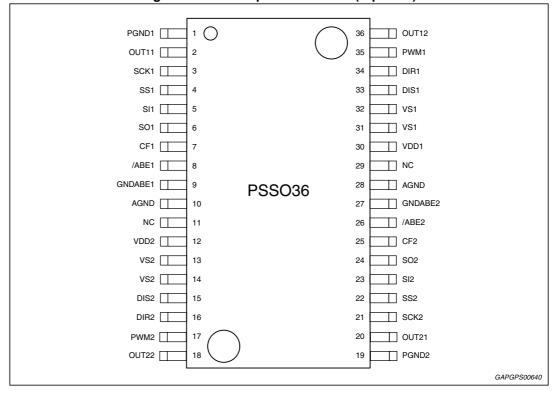

Figure 3. PSSO36 pin connection (top view)

Pins description L9959

☐ OUT2 PGND | 36 35 OUT1 🔲 \_\_\_\_ PWM \_\_\_ DIR 34 SCK [ DIS ss 🔲 33 □ vs SI 🔲 32 □ VS so 🔲 31 \_\_\_\_ VDD CF [ □ NC /ABE GNDABE [ \_\_\_\_ AGND PSSO36 NC [ 27 □ NC NC [ □ NC NC | 12 25 NC  $\square$ 13 24 □ NC NC  $\square$ 14 23 NC 🔲 15 □ NC NC 🗌 16 21 □ NC 17 20 □ NC NC \_\_\_ 18 19 □ NC NC [ GAPG2010151556PS

Figure 4. PSSO36 (Single version) pin connection (top view)

### 2.1 Pin definitions and functions

Table 2. L9959S PSSO24 pin-out

| Pin                                   | Symbol | Function                                                                                                                                  |  |

|---------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 4,<br>12, 13,<br>14, 16,<br>22, 24 | NC     | To be connected to GND on PCB.                                                                                                            |  |

| 2                                     | PGND   | Power Ground                                                                                                                              |  |

| 3                                     | OUT1   | Bridge output 1 and 2: The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor.                         |  |

| 5                                     | SCK    | erial clock input:<br>nis input controls the internal shift register of the SPI.                                                          |  |

| 6                                     | SS     | Slave Select input: The serial data transfer between the device and the micro controller is enabled by pulling the input SS to low level. |  |

| 7                                     | SI     | Slave in (Serial data input): The input receives serial data from the microcontroller.                                                    |  |

| 8                                     | SO     | Slave Out (Serial data output): The diagnosis data is available via the SPI through this tristate-output.                                 |  |

L9959 Pins description

Table 2. L9959S PSSO24 pin-out (continued)

| Pin | Symbol | Function                                                                                                                                                                            |  |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9   | CF     | Current Proportional Feedback output: The CF pin provides in conjunction with an external resistor an output current, which is proportional to the H-Bridge current.                |  |

| 10  | /ABE   | Bidirectional Ability/Enable Pin: Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input is pulled to low, all output stages are switched off. |  |

| 11  | GNDABE | Sense Ground for VDD monitoring                                                                                                                                                     |  |

| 15  | AGND   | Device Ground. (Connected to Exposed PAD)                                                                                                                                           |  |

| 17  | VDD    | VDD Supply: 5 V Supply                                                                                                                                                              |  |

| 18  | VS     | Power supply voltage for power stage outputs (external reverse protection required)                                                                                                 |  |

| 19  | DIS    | Disable input: DIS switches OUT1 and OUT2 to tristate.                                                                                                                              |  |

| 20  | DIR    | Direction input: The DIR pin controls the switch direction of OUT1 and OUT2.                                                                                                        |  |

| 21  | PWM    | PWM input:<br>The PWM input switches OUT1 and OUT2.                                                                                                                                 |  |

| 23  | OUT2   | Bridge output 1 and 2: The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor.                                                                   |  |

| EP  | AGND   | Exposed Pad: Connected to AGND.                                                                                                                                                     |  |

Table 3. L9959T (Two H-Bridge drivers in one package) PSSO36 pin-out

| Pin | Symbol               | Function                                                                                                                                                                                              |  |

|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | PGND1 <sup>(1)</sup> | round: nportant: For the capability of driving the full current at the outputs, all ground pins must be  xternally connected.                                                                         |  |

| 2   | OUT11                | idge output 11, 12, 21, and 22: le bridge outputs are built of a high-side p-channel and a low-side N-channel transistor. le bridge outputs of chip 1 are OUT11 and OUT12, of chip 2 OUT21 and OUT22. |  |

| 3   | SCK1                 | erial clock input: his input controls the internal shift register of the SPI. CK1 belongs to chip 1 and SCK2 to chip 2.                                                                               |  |

| 4   | SS1                  | Slave Select input: The serial data transfer between the device and the micro controller is enabled by pulling the input SS to low level. SS1 belongs to chip 1 and SS2 to chip 2.                    |  |

| 5   | SI1                  | Slave in (Serial data input): The input receives serial data from the microcontroller. SI1 belongs to chip 1 and SI2 to chip 2.                                                                       |  |

| 6   | SO1                  | Slave Out (Serial data output): The diagnosis data is available via the SPI through this tristate-output. SO1 belongs to chip 1 and SO2 to chip 2.                                                    |  |

Pins description L9959

Table 3. L9959T (Two H-Bridge drivers in one package) PSSO36 pin-out (continued)

| Pin     | Symbol               | Function                                                                                                                                                                                                                     |  |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7       | CF1                  | Current Proportional Feedback output: The CF pin provides in conjunction with an external resistor an output current, which is proportional to the H-Bridge current. CF1 belongs to OUT11 and OUT12, CF2 to OUT21 and OUT22. |  |

| 8       | /ABE1                | Bidirectional Ability/Enable Pin 1: Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input is pulled to low, all output stages are switched off. /ABE1 belongs to chip 1.               |  |

| 9       | GNDABE1              | Sense Ground for VDD monitoring                                                                                                                                                                                              |  |

| 10, 28  | AGND                 | Device Ground. (Connected to Exposed PAD)                                                                                                                                                                                    |  |

| 11, 29  | NC                   | To be connected to GND on PCB.                                                                                                                                                                                               |  |

| 12      | VDD2 <sup>(2)</sup>  | VDD Supply: 5V Supply.                                                                                                                                                                                                       |  |

| 13, 14, | VS2 <sup>(3)</sup>   | Power supply voltage for power stage outputs (external reverse protection required): Important: For the capability of driving the full current at the outputs all pins of VS must be externally connected.                   |  |

| 15      | DIS2                 | Disable input 2: DIS2 switches OUT21 and OUT22 to tristate.                                                                                                                                                                  |  |

| 16      | DIR2                 | Direction input 2: DIR2 pin controls the switch direction of OUT21 and OUT22.                                                                                                                                                |  |

| 17      | PWM2                 | PWM input 2: PWM1 input switches OUT21 and OUT22.                                                                                                                                                                            |  |

| 18      | OUT22                | Bridge output 11, 12, 21, and 22: The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor. The bridge outputs of chip 1 are OUT11 and OUT12, of chip 2 OUT21 and OUT22.                    |  |

| 19      | PGND2 <sup>(1)</sup> | Ground: Important: For the capability of driving the full current at the outputs, all ground pins must be externally connected.                                                                                              |  |

| 20      | OUT21                | Bridge output 11, 12, 21, and 22: The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor. The bridge outputs of chip 1 are OUT11 and OUT12, of chip 2 OUT21 and OUT22.                    |  |

| 21      | SCK2                 | Serial clock input: This input controls the internal shift register of the SPI. SCK1 belongs to chip 1 and SCK2 to chip 2.                                                                                                   |  |

| 22      | SS2                  | Slave Select input: The serial data transfer between the device and the micro controller is enabled by pulling the input SS to low level. SS1 belongs to chip 1 and SS2 to chip 2.                                           |  |

| 23      | SI2                  | Slave in (Serial data input): The input receives serial data from the microcontroller. SI1 belongs to chip 1 and SI2 to chip 2.                                                                                              |  |

| 24      | SO2                  | Slave Out (Serial data output): The diagnosis data is available via the SPI through this tristate-output. SO1 belongs to chip 1 and SO2 to chip 2.                                                                           |  |

L9959 Pins description

Table 3. L9959T (Two H-Bridge drivers in one package) PSSO36 pin-out (continued)

| Pin    | Symbol              | Function                                                                                                                                                                                                                     |  |

|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 25     | CF2                 | Current Proportional Feedback output: The CF pin provides in conjunction with an external resistor an output current, which is proportional to the H-Bridge current. CF1 belongs to OUT11 and OUT12, CF2 to OUT21 and OUT22. |  |

| 26     | /ABE2               | Bidirectional Ability/Enable Pin 2:  Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input so pulled to low, all output stages are switched off. /ABE2 belongs to chip 2.              |  |

| 27     | GNDABE2             | Sense Ground for VDD monitoring                                                                                                                                                                                              |  |

| 30     | VDD1 <sup>(2)</sup> | VDD Supply: 5V Supply.                                                                                                                                                                                                       |  |

| 31, 32 | VS1 <sup>(3)</sup>  | Power supply voltage for power stage outputs (external reverse protection required): Important: For the capability of driving the full current at the outputs all pins of VS must b externally connected.                    |  |

| 33     | DIS1                | Disable input 1: DIS1 switches OUT11 and OUT12 to tristate                                                                                                                                                                   |  |

| 34     | DIR1                | Direction input 1: DIR1 pin controls the switch direction of OUT11 and OUT12.                                                                                                                                                |  |

| 35     | PWM1                | PWM input 1:<br>PWM1 input switches OUT11 and OUT12.                                                                                                                                                                         |  |

| 36     | OUT12               | Bridge output 11, 12, 21, and 22: The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor. The bridge outputs of chip 1 are OUT11 and OUT12, of chip 2 OUT21 and OUT22.                    |  |

| EP     | AGND <sup>(4)</sup> | Exposed PAD: connected to AGND                                                                                                                                                                                               |  |

<sup>1.</sup> Pins 1 is referred to die 1, whereas 19 is referred to die 2.

<sup>2.</sup> Pins 12 is referred to die 2, whereas 30 is referred to die 1.

<sup>3.</sup> Pins 13 and 14 are referred to die 2, whereas pins 31 and 32 are referred to die1.

<sup>4.</sup> Pins 10 is referred to die 2, whereas 28 is referred to die 1.

Pins description L9959

Table 4. L9959U (Single version in PSSO36) pin out

| Pin                                                                                          | Symbol | Function                                                                                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                                                                            | PGND   | Ground: Important: For the capability of driving the full current at the outputs, all ground pins must be externally connected.                                                                            |  |

| 2                                                                                            | OUT1   | The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor.                                                                                                                 |  |

| 3                                                                                            | SCK    | Serial clock input: This input controls the internal shift register of the SPI.                                                                                                                            |  |

| 7                                                                                            | CF     | Current Proportional Feedback output: The CF pin provides in conjunction with an external resistor an output current, which is proportional to the H-Bridge current                                        |  |

| 8                                                                                            | /ABE   | Bidirectional Ability/Enable Pin: Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input is pulled to low, all output stages are switched off.                        |  |

| 9                                                                                            | GNDABE | Sense Ground for VDD monitoring                                                                                                                                                                            |  |

| 10,11,<br>12,13,<br>14,15,<br>16,17,<br>18,19,<br>20,21,<br>22,23,<br>24,25,<br>26,27,<br>29 | NC     | To be connected to GND on PCB.                                                                                                                                                                             |  |

| 28                                                                                           | AGND   | Device Ground. (Connected to Exposed PAD)                                                                                                                                                                  |  |

| 30                                                                                           | VDD    | VDD Supply: 5 V Supply.                                                                                                                                                                                    |  |

| 31, 32                                                                                       | VS1    | Power supply voltage for power stage outputs (external reverse protection required): Important: For the capability of driving the full current at the outputs all pins of VS must be externally connected. |  |

| 33                                                                                           | DIS    | Disable input : DIS switches OUT1 and OUT2 to tristate                                                                                                                                                     |  |

| 34                                                                                           | DIR    | Direction input: DIR pin controls the switch direction of OUT1 and OUT2.                                                                                                                                   |  |

| 35                                                                                           | PWM    | PWM input: PWM input switches OUT1 and OUT2.                                                                                                                                                               |  |

| 36                                                                                           | OUT2   | The bridge outputs are built of a high-side p-channel and a low-side N-channel transistor.                                                                                                                 |  |

### 3 Electrical specifications

### 3.1 Absolute maximum ratings

#### Warning:

Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE program and other relevant quality document.

Table 5. Absolute maximum ratings

| Symbol                                                                                      | Parameter / Test condition                                                                           | Value [DC Voltage] | Unit |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------|------|

| V <sub>VS</sub>                                                                             | DC supply voltage The device is able to sustain load dump as specified in the ISO16750 documentation | -1.0 to +40        | V    |

| V <sub>VDD</sub>                                                                            | Stabilized supply voltage, logic supply                                                              | -0.3 to 18         | V    |

| C <sub>F</sub> <sup>(1)</sup>                                                               | Current feedback output                                                                              | -0.3 to 18         | V    |

| $\begin{matrix} V_{SI}, V_{SCK}, V_{SS}, V_{SO}, \\ V_{DIR}, V_{PWM}, V_{DIS} \end{matrix}$ | Logic input / output voltage range                                                                   | -0.3 to 18         | V    |

| V <sub>OUTn</sub>                                                                           | Output voltage (n = 1,2 or 11,12,21,22);<br>V <sub>OUTn</sub> < V <sub>S</sub> + 1 V                 | -1.0 to 40         | V    |

|                                                                                             | Dynamic pulse / t < 500ms; V <sub>OUTn</sub> < V <sub>S</sub> + 2 V                                  | -2.0 to 40         | V    |

| т                                                                                           | Operating junction temperature                                                                       | -40 to 150         | °C   |

| T <sub>j</sub>                                                                              | Dynamic junction temperature (1000hrs)                                                               | 150 to 175         | °C   |

| T <sub>stg</sub>                                                                            | Storage temperature                                                                                  | -55 to 150         | °C   |

<sup>1.</sup> It is withstood at  $V_S = 18 \text{ V}$

### 3.2 ESD protection

Table 6. ESD protection

| Parameter                                                                                                                        | Value             | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| All pins versus ground group (AGND, PGND1, PGND2, GND_ABE1, GND_ABE2)                                                            | ±2 <sup>(1)</sup> | kV   |

| VS pin, Power Output Pins: OUT1, OUT2 or OUT11, OUT12, OUT21, OUT22 versus ground group (AGND, PGND1, PGND2, GND_ABE1, GND_ABE2) | ±4 <sup>(2)</sup> | kV   |

<sup>1.</sup> HBM according to MIL 883C, Method 3015.7 or EIA/JESD22-A114-A.

<sup>2.</sup> HBM with all unzipped pins grounded.

#### 3.3 Thermal data

Table 7. Thermal data

| Symbol                | Parameter                                                    | Value | Unit |

|-----------------------|--------------------------------------------------------------|-------|------|

| R <sub>thj-case</sub> | Thermal resistance junction-to-case (max) for L9959S, L9959T | 2.0   | °C/W |

### 3.4 Electrical characteristics

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V; all outputs open; T<sub>j</sub> = -40 °C to 150 °C, unless otherwise specified.

Table 8. Supply

| Symbol                              | Parameter                                          | Test condition                                                                                                                 | Min. | Тур. | Max. | Unit |

|-------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>S</sub>                      | Operating voltage range                            | -                                                                                                                              | 4.5  | -    | 28   | V    |

|                                     |                                                    | $V_{DD}$ = 5 V; $V_{S}$ = 5 V and $V_{S}$ = 18 V; Bridge disabled                                                              | -    | -    | 5    | mA   |

| I <sub>VS</sub>                     | V <sub>S</sub> current consumption in active mode  | $V_{DD}$ = 5 V; $V_{S}$ = 5 V and $V_{S}$ = 18 V; $f_{OUT}$ = 2 kHz; $I_{OUT}$ = 0 A                                           | -    | -    | 6    | mA   |

|                                     | active mode                                        | $V_{DD} = 5 \text{ V}; V_{S} = 5 \text{ V} \text{ and } V_{S} = 18 \text{ V}; f_{OUT} = 10 \text{ kHz}; I_{OUT} = 0 \text{ A}$ | -    | -    | 14   | mA   |

|                                     |                                                    | $V_{DD}$ = 5 V; $V_{S}$ = 28 V;<br>$f_{OUT}$ = 10 kHz; $I_{OUT}$ = 0 A                                                         | -    | -    | 14   | mA   |

| I <sub>VS(stby)</sub>               | V <sub>S</sub> current consumption in passive mode | V <sub>DD</sub> = 0 V                                                                                                          | 0    | -    | 2.5  | mA   |

| V <sub>VS_slew</sub> <sup>(1)</sup> | Slew rate on V <sub>S</sub>                        | -                                                                                                                              | -    | -    | 100  | V/µs |

| V <sub>VS_slew</sub> <sup>(2)</sup> | Slew rate on V <sub>S</sub>                        | -                                                                                                                              | -    | -    | 20   | V/µs |

| $V_{DD}$                            | Operating voltage range                            | -                                                                                                                              | 4.5  | -    | 5.5  | V    |

| I <sub>VDD</sub>                    | V <sub>DD</sub> supply current                     | V <sub>S</sub> = 18 V; V <sub>DD</sub> = 5 V                                                                                   | -    | -    | 10   | mA   |

<sup>1.</sup> No change of parameters for VDD-monitoring and in SPI logic

<sup>2.</sup> No change of parameters

#### Table 9. Power-on reset

| Symbol                | Parameter                     | Test condition | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------------------|----------------|------|------|------|------|

| V <sub>DDRES</sub>    | Reset active threshold        | -              | 2.8  | -    | 3.4  | V    |

| V <sub>DDPOR</sub>    | Power-on reset threshold      | -              | 3.3  | -    | 4    | V    |

| V <sub>DDPORHYS</sub> | Power-on reset hysteresis     | -              | -    | 600  | -    | mV   |

| t <sub>POR</sub>      | Power-on reset extension time | -              | -    | -    | 1    | ms   |

### Table 10. V<sub>DD</sub> monitoring

| Symbol                | Parameter                                                                               | Test condition                                                                                                              | Min.               | Тур. | Max. | Unit  |

|-----------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|-------|

| V <sub>DD</sub>       | V <sub>DD</sub> monitoring voltage range                                                | -                                                                                                                           | V <sub>DDPOR</sub> | -    | 18   | V     |

| V <sub>DD_THL</sub>   | Under voltage threshold                                                                 | V <sub>S</sub> = 0 V                                                                                                        | 4.2                | -    | 4.5  | V     |

| V <sub>DD_THH</sub>   | Over voltage threshold                                                                  | V <sub>S</sub> = 0 V                                                                                                        | 5.25               | -    | 5.5  | V     |

| t <sub>FIL_OFF</sub>  | Switch-off filtering time                                                               | Cuaranta ad hu again                                                                                                        | 60                 | -    | 135  | μs    |

| t <sub>FIL_ON</sub>   | Switch-on filtering time                                                                | Guaranteed by scan.                                                                                                         | 60                 | -    | 135  | μs    |

| V <sub>TEST_THL</sub> | Under voltage test threshold                                                            | -                                                                                                                           | 5.25               | -    | 5.5  | V     |

| V <sub>TEST_THH</sub> | Over voltage test threshold                                                             | -                                                                                                                           | 4.2                | -    | 4.4  | V     |

| V <sub>DD_MR</sub>    | Full V <sub>DD</sub> supply range                                                       | -                                                                                                                           | -0.3               | -    | 18   | V     |

| V <sub>DD_SLEW</sub>  | V <sub>DD</sub> slew                                                                    | -                                                                                                                           |                    | -    | 500  | mV/μs |

| ΔV <sub>DD_THX</sub>  | Threshold (V <sub>DD_THH</sub> , V <sub>DD_THL</sub> ) shift during vs. inverse current | -                                                                                                                           | -0.1               | -    | 0.1  | V     |

| V <sub>ABE_INL</sub>  | /ABE input low-level                                                                    | -                                                                                                                           | -0.3               | -    | 1.65 | V     |

| V <sub>ABE_INH</sub>  | /ABE input high-level                                                                   | -                                                                                                                           | 3.15               | -    | 18   | V     |

| V <sub>ABE_INHY</sub> | /ABE input hysteresis                                                                   | -                                                                                                                           | 0.2                | -    | 1.0  | V     |

|                       |                                                                                         | 0 V < V <sub>ABE</sub> < 1.5 V                                                                                              | 0                  | -    | 60   | μA    |

| I <sub>ABE_IN</sub>   | /ABE input pull-down current                                                            | V <sub>ABE</sub> = 2.1 V, 5 V, 18 V;<br>V <sub>S</sub> = 18 V; V <sub>DD</sub> = 5 V,<br>18 V                               | 20                 | 40   | 60   | μА    |

| V <sub>ABE_OUTL</sub> | /ABE output low voltage                                                                 | $2.5~\mathrm{V} < \mathrm{V}_\mathrm{DD} < \mathrm{V}_\mathrm{DD\_THL}; \\ \mathrm{I}_\mathrm{ABE\_OUTL} < 2.5~\mathrm{mA}$ | 0                  | -    | 1.0  | V     |

| V <sub>ABE_OUTL</sub> | /ABE output low voltage                                                                 | V <sub>DD_THH</sub> < V <sub>DD</sub> < 18V;<br>I <sub>ABE_OUTL</sub> < 7.5 mA                                              | 0                  | -    | 1.2  | V     |

| V <sub>ABE_OUTL</sub> | /ABE output passive low voltage                                                         | -                                                                                                                           | 0                  | -    | 1.2  | V     |

| Δl <sub>ABE</sub>     | I <sub>ABE</sub> Change during vs. inverse current                                      | -                                                                                                                           | -100               |      | 100  | μA    |

| Symbol              | Parameter            | Test condition                           | Min. | Тур. | Max. | Unit |

|---------------------|----------------------|------------------------------------------|------|------|------|------|

| V <sub>UV_OFF</sub> | VS UV threshold      | VS decreasing                            | 3.1  | 3.8  | 4.5  | V    |

| V <sub>UV_ON</sub>  | VS UV threshold      | VS increasing                            | 3.3  | 4.0  | 4.7  | V    |

| V <sub>UV_HYS</sub> | VS UV hysteresis     | V <sub>UV_ON</sub> - V <sub>UV_OFF</sub> | 0.1  | -    | 1    | V    |

| t <sub>FUV</sub>    | VS UV detection time | -                                        | -    | -    | 1.5  | μs   |

### 3.5 Outputs OUT1 and OUT2

Table 12. On-resistance  $(4.5 \text{ V} < \text{V}_{\text{S}} < 28 \text{ V})$

| Symbol                       | Parameter                      | Test condition                                                              | Min. | Тур. | Max. | Unit |

|------------------------------|--------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| r <sub>ONVS</sub><br>OUT1,2  | On-resistance to supply        | $V_{DD} = 5 \text{ V}; V_{S} = 10 \text{ V},$<br>$I_{OUT1,2} = 3 \text{ A}$ | -    | -    | 315  | mΩ   |

| r <sub>ONGND</sub><br>OUT1,2 | On-resistance to PGND          | $V_{DD} = 5 \text{ V}; V_{S} = 10 \text{ V},$<br>$I_{OUT1,2} = 3 \text{ A}$ | 1    | -    | 225  | mΩ   |

|                              | Switched-off output current of | V <sub>DD</sub> = 5 V; V <sub>S</sub> = 13 V;<br>V <sub>OUT</sub> = 0 V     | -200 | -    | -    | μA   |

|                              | OUT 4 0                        | $V_{DD}$ = 5 V; $V_{S}$ = 13 V; $V_{OUT}$ = $V_{S}$                         | -    | -    | 200  | μA   |

Table 13. Power output switching times (8 V < V<sub>S</sub> < 18 V)

| Symbol                            | Parameter                                                                                        | Test condition                                                                                                  | Min.         | Тур. | Max.     | Unit |

|-----------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------|------|----------|------|

| t <sub>d ON</sub>                 | Output delay time driver on                                                                      | -                                                                                                               | -            | -    | 6        | μs   |

| t <sub>d OFF</sub>                | Output delay time driver off                                                                     | -                                                                                                               | -            | -    | 20       | μs   |

| t <sub>d dis</sub> <sup>(1)</sup> | Disable delay time                                                                               |                                                                                                                 | -            | -    | 12.5     | μs   |

| t <sub>d pwon</sub>               | Power-on delay time                                                                              | Guaranteed through scan.                                                                                        | -            | -    | 1        | ms   |

| t <sub>d en</sub>                 | Enable delay time                                                                                |                                                                                                                 | -            | -    | 50       | μs   |

| dl <sub>OUT</sub> /dt             | Current slew rate                                                                                | -                                                                                                               | -            | 1.6  |          | A/µs |

| dV <sub>OUTHS</sub> /dt           | Output rise/fall slew-rate high-side slow selected with bit SR = 0 fast selected with bit SR = 1 | V - 5 V - 44 V                                                                                                  | 0.975<br>2.8 | -    | 2.7<br>8 | V/µs |

| dV <sub>rOUTLS</sub> /dt          | Output rise slew-rate low-side valid only after the toggling of DIR input                        | $V_{DD} = 5 \text{ V; } V_{S} = 14 \text{ V}$<br>$R_{LOAD1,2} = 2.6 \Omega (8 V_{S}),$<br>$6 \Omega (18 V_{S})$ | 0.975        | -    | 2.7      | V/µs |

| dV <sub>fOUTLS</sub> /dt          | Output fall slew-rate low-side                                                                   |                                                                                                                 | 2.5          | 4    | 8        | V/µs |

| f <sub>pwmmax</sub>               | PWM input frequency                                                                              | -                                                                                                               | -            | -    | 11       | kHz  |

<sup>1.</sup> Driven by /ABE or DIS input.

16/49 DocID027540 Rev 3

<sup>2.</sup> The slew-rates ( $dV_{OUT}/dt1$ ) are defined by dV (voltage difference 20% - 80%) divided by the rise-/fall times ( $t_r/t_f$  see Figure 6: Output rise and fall times).

Figure 5. Output delay times (e.g. low-side output)

Figure 8. Output disable and enable time (DIS Input)

Table 14. Current feedback (CF)

| Symbol                         | Parameter         | Test condition                                                                                                         | Min. | Тур.  | Max. | Unit     |

|--------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|------|-------|------|----------|

|                                |                   | $V_S > 6.5 \text{ V}$ , OUTx = 0 A,<br>$T_{J=}$ -40 °C; Current<br>level 2,3,4                                         | 0.01 | 0.05  | 0.20 | <b>V</b> |

| V <sub>CF</sub> <sup>(1)</sup> | CF voltage range  | $V_S > 6.5 \text{ V, OUTx} = 250\text{mA, T}_J = 130 ^{\circ}\text{C;}$<br>Current level 2,3,4                         | 0.04 | 0.275 | 0.5  | ٧        |

| VCF Y                          | CF voltage range  | $V_S > 6.5 \text{ V}, \text{ OUTx} = 0.4 \text{ *}$<br>$I_{clx}, T_J = 130 \text{ °C}; \text{ Current}$<br>level 2,3,4 | 1.71 | 1.80  | 1.89 | >        |

|                                |                   | $V_S > 6.5 \text{ V}$ , OUTx = $I_{Clx}$<br>$T_J = -40^{\circ}\text{C}$ to 150°C;<br>Current level 2,3,4               | 3.82 | 4.5   | 5.18 | <b>V</b> |

| R <sub>CF</sub> <sup>(2)</sup> | CF resistor range | -                                                                                                                      | -    | 5.1   | -    | kΩ       |

| I <sub>OFFSET</sub>            | CF offset current | -                                                                                                                      | -    | 10    | -    | μΑ       |

Measured at a 5.1k resistor between CF and GND (R<sub>CF</sub>). Levels see Table 34 Current Level (CONFIG\_REG).

Note: This signal has an individual error ±5 % in each of the three currents levels, at trimming temperature of 130 °C. Additional an individual error ±10 % in each of the three current levels over temperature and aging. So the maximum error is of ±15 % in each of the three current levels. The offset and the gain errors may be different in each current level. The adjustment is done at 130 °C and compensates the error corresponding to 0.4 \* Iclx

18/49 DocID027540 Rev 3

<sup>2.</sup> Defined by design, not tested.

**Table 15. Current limiting**

| Symbol                               | Parameter                             | Test condition           | Min.                      | Тур. | Max.                       | Unit |

|--------------------------------------|---------------------------------------|--------------------------|---------------------------|------|----------------------------|------|

| I <sub>CL2</sub>   <sup>(1)</sup>    | Current limit <sub>2</sub>            |                          | 4.25                      | 5    | 5.75                       | Α    |

| I <sub>CL3</sub>   <sup>(1)</sup>    | Current limit <sub>3</sub>            | R <sub>CF</sub> = 5.1 kΩ | 5.6                       | 6.6  | 7.6                        | Α    |

| I <sub>CL4</sub>   <sup>(1)</sup>    | Current limit <sub>4</sub>            |                          | 7.3                       | 8.6  | 9.9                        | Α    |

| I <sub>HYS2-4</sub>   <sup>(1)</sup> | Current limit hysteresis <sub>1</sub> | -                        | -5%<br>ICL <sub>2-4</sub> | -    | -10%<br>ICL <sub>2-4</sub> | А    |

| t <sub>b</sub>                       | Blanking time                         | Guaranteed through scan. | 8                         | 11   | 15                         | μs   |

| t <sub>trans</sub>                   | Time between two transient            |                          | 90                        | -    | 130                        | μs   |

<sup>1.</sup> Programmable current levels see *Table 34* Current Level (CONFIG\_REG). Measured using a 5.1 kΩ resistor between CF and GND (R<sub>CF</sub>).

Table 16. Over-current detection (8  $V < V_S < 18 V$ )

| Symbol                                | Parameter                                     | Test condition          | Min. | Тур. | Max. | Unit |

|---------------------------------------|-----------------------------------------------|-------------------------|------|------|------|------|

| II <sub>OC2_LS</sub> I <sup>(1)</sup> | Low side over current threshold <sub>2</sub>  | V <sub>DD</sub> = 5 V   | 4.9  | -    | 8.2  | Α    |

| II <sub>OC3_LS</sub> I <sup>(1)</sup> | Low side over current threshold <sub>3</sub>  | V <sub>DD</sub> = 5 V   | 6.7  | -    | 11.1 | А    |

| II <sub>OC4_LS</sub> I <sup>(1)</sup> | Low side over current threshold <sub>4</sub>  | V <sub>DD</sub> = 5 V   | 8.4  | -    | 14   | Α    |

| II <sub>OC2_HS</sub> I <sup>(1)</sup> | High side over current threshold <sub>2</sub> | V <sub>DD</sub> = 5 V   | 5.5  | -    | 9.2  | Α    |

| II <sub>OC3_HS</sub> I <sup>(1)</sup> | High side over current threshold <sub>3</sub> | V <sub>DD</sub> = 5 V   | 6.9  | -    | 11.5 | Α    |

| II <sub>OC4_HS</sub> I <sup>(1)</sup> | High side over current threshold <sub>4</sub> | V <sub>DD</sub> = 5 V   | 8.6  | -    | 14.4 | Α    |

| I <sub>TRACK-2</sub> <sup>(2)</sup>   | I <sub>OC2</sub>   -    <sub>CL2</sub>        | V <sub>DD</sub> = 5 V   | 0.4  | -    | 5.5  | Α    |

| I <sub>TRACK-3</sub> <sup>(2)</sup>   | 1 <sub>OC3</sub>   -  1 <sub>CL3</sub>        | V <sub>DD</sub> = 5 V   | 0.4  | -    | 5.5  | Α    |

| I <sub>TRACK-4</sub> <sup>(2)</sup>   | 1 <sub>OC4</sub>   -  1 <sub>CL4</sub>        | V <sub>DD</sub> = 5 V   | 0.4  | -    | 5.5  | Α    |

| t <sub>DF</sub>                       | Delay time for fault detection                | guaranteed by design    | 1    | 2    | 4.5  | μs   |

| t <sub>DF_off</sub>                   | Switch-off delay time                         | -                       |      |      | 6    | μs   |

| t <sub>DF_del</sub>                   | Delayed switch-off time                       | -                       | 20   |      | 200  | μs   |

| t <sub>SC</sub>                       | Short-circuit detection                       | guaranteed through scan | 292  | 350  | 413  | μs   |

<sup>1.</sup> Programmable current levels see *Table 34* Current Level (CONFIG\_REG).

<sup>2.</sup> Tracking values are referred for both LS and HS.

Table 17. Open-load detection

| Symbol                | Parameter                                    | Test condition           | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------|--------------------------|------|------|------|------|

| R <sub>OL</sub>       | Open-load detection threshold                | -                        | 5    | -    | 50   | kΩ   |

| t <sub>DIAGOL</sub>   | Open-load diagnosis enable delay             | Guaranteed through scan. | 100  | -    | 150  | ms   |

| t <sub>DIAGOL1</sub>  | Open-load diagnosis filter time <sub>1</sub> |                          | 2.4  | -    | 3.6  | ms   |

| t <sub>DIAGOL2</sub>  | Open-load diagnosis filter time <sub>2</sub> |                          | 200  | -    | 300  | μs   |

| V <sub>out1_OFF</sub> | Out1 voltage regulator                       | -                        | 1.67 | -    | 1.97 | V    |

Note:

If the value of the connected load is below 5 k $\Omega$  no Open Load is detected; whereas if the value of the connected load is more than 50 k $\Omega$ , Open Load is detected.

If the load is in the range between (5 to 50)  $k\Omega$ , the Open Load diagnosis could be not reliable.

Table 18. Retest delay

| Symbol                    | Parameter                                | Test condition           | Min. | Тур. | Max. | Unit |

|---------------------------|------------------------------------------|--------------------------|------|------|------|------|

| t <sub>delay retest</sub> | Retest delay for failures: SCB, SCG, SCL | Guaranteed through scan. | 290  | 350  | 410  | μs   |

### 3.6 Temperature dependent current reduction

Table 19. Temperature dependent current reduction

| Symbol                            | Parameter                                        | Test condition           | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------------------------------------------------|--------------------------|------|------|------|------|

| I <sub>L_TSD</sub>                | Current limit at T <sub>SD</sub>                 | -                        | 1.4  | 2.5  | 3.6  | Α    |

| T <sub>ILR</sub>                  | Start of temperature dependent current reduction | -                        | 150  | 165  | -    | ů    |

| T <sub>SD</sub>                   | Thermal shut-down                                | -                        | 175  | -    | -    | °C   |

| T <sub>SD</sub> -T <sub>ILR</sub> | Range of temperature dependent current reduction | -                        | 20   | 25   | 30   | °C   |

| T <sub>fTSD</sub>                 | Thermo-shut-down detection filter time           | Guaranteed through scan. | 6    | -    | 18   | μs   |

Note: see also Figure 17: Temperature dependent current reduction.

### 3.7 Free-wheeling diodes

Table 20. Free-wheel diodes

| Symbol                         | Parameter                                 | Test condition         | Min. | Тур. | Max. | Unit |

|--------------------------------|-------------------------------------------|------------------------|------|------|------|------|

| U <sub>D</sub>                 | Free-wheeling diode forward voltage       | I <sub>OUT</sub> = 3 A | -    | -    | 2    | V    |

| T <sub>it</sub> <sup>(1)</sup> | Free-wheeling diode reverse recovery time | -                      | -    | -    | 100  | ns   |

1. Not subject to production test; specified by design.

## 3.8 SPI / logic electrical characteristics

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V, 4.5 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V; all outputs open; T<sub>j</sub> = -40 °C to 150 °C, unless otherwise specified.

Table 21. Inputs: SI, SS, SCK, DIR, DIS and PWM; Output: SO

| Symbol                             | Parameter                                                                              | Test condition                       | Min      | Тур | Max     | Unit |

|------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|----------|-----|---------|------|

| Inputs: SI,                        | SS, SCK DIR, PWM                                                                       |                                      | <u>'</u> |     |         |      |

| V <sub>IL</sub>                    | Input voltage low-level                                                                | V <sub>DD</sub> = 5 V                | -0.3     | -   | 0.75    | V    |

| V <sub>IH</sub>                    | Input voltage high-level                                                               | V <sub>DD</sub> = 5 V                | 1.75     | -   | VDD+0.3 | V    |

| V <sub>IHYS</sub>                  | Input hysteresis                                                                       | V <sub>DD</sub> = 5 V                | 0.2      | -   | 1.0     | V    |

| R <sub>PUin</sub>                  | Input pull-up resistor                                                                 | V <sub>DD</sub> = 5 V                | 50       | -   | 250     | kΩ   |

| I <sub>INx</sub>                   | PWM, DIR input current                                                                 | V <sub>INx</sub> > 3.0V              | -5       | -   | 5       | μA   |

| C <sub>Slin</sub> <sup>(1)</sup>   | SI input capacitance                                                                   | -                                    | -        | -   | 10      | pF   |

| C <sub>SCKin</sub> <sup>(1)</sup>  | SCK input capacitance                                                                  | -                                    | -        | -   | 10      | pF   |

| C <sub>SSin</sub> <sup>(1)</sup>   | SS Input Capacitance                                                                   | -                                    | -        | -   | 15      | pF   |

| C <sub>DIR,PWMin</sub>             | DIR, PWM input capacitance                                                             | -                                    | -        | -   | 20      | pF   |

| Input: DIS                         |                                                                                        |                                      |          |     |         |      |

| R <sub>DISPU</sub>                 | Pull-up resistor                                                                       | 0 V < V <sub>DIS</sub> < 2.1 V       | 10       | -   | 45      | kΩ   |

| I <sub>DISx</sub>                  | DIS input current                                                                      | V <sub>DIS</sub> > 3 V               | -5       | -   | 5       | μA   |

| C <sub>DIS in</sub> <sup>(1)</sup> | DIS input capacitance                                                                  | -                                    | -        | -   | 20      | pF   |

| t <sub>DIS</sub>                   | DIS pulse width                                                                        | -                                    | 0.5      | 1   | 1.5     | μs   |

| Input pin di                       | isturbance (SI, SS, SCK DIR, F                                                         | PWM,DIS)                             |          |     |         |      |

| ΔVx_HL                             | Change of V <sub>IH</sub> and V <sub>IL</sub> during inverse current on V <sub>S</sub> | Net cubic stand to to at in          | -0.1     | -   | 0.1     | V    |

| ΔISx                               | Change of input current of SPI input pins during inverse current on V <sub>S</sub>     | Not subjected to test in production. | -100     | -   | 100     | μA   |

| Output: SO                         |                                                                                        |                                      |          |     |         |      |

| V <sub>SOL</sub>                   | Output voltage low level                                                               | I <sub>OL</sub> = 2 mA,              | 0        | -   | 0.4     | V    |

| V <sub>SOH</sub>                   | Output voltage high level                                                              | I <sub>OH</sub> = -2 mA              | VDD-0.5  | -   | VDD     | V    |

| SR <sub>SO</sub> <sup>(1)</sup>    | Slew rate                                                                              | C <sub>LOAD</sub> = 200 pF           | 0.3      | -   | 0.6     | V/ns |

| I <sub>SOLK</sub>                  | Tristate leakage current                                                               | $V_{SS} = V_{DD}$                    | -10      | -   | 10      | μA   |

| C <sub>SO out</sub> <sup>(1)</sup> | SO output capacitance                                                                  | -                                    | -        | -   | 10      | pF   |

|                                    | disturbance (SO)                                                                       |                                      | 1        |     | -       |      |

| ΔI <sub>SOLK</sub>                 | Change of I <sub>SOLK</sub> during inverse Current on VS                               | -                                    | -100     | -   | 100     | μA   |

<sup>1.</sup> Not measured in production test. Parameter guaranteed by design.

**Table 22. Dynamic characteristics**

| Symbol            | Parameter         | Test condition                                    | Min. | Тур. | Max. | Unit |

|-------------------|-------------------|---------------------------------------------------|------|------|------|------|

| t <sub>cyc</sub>  | Cycle time        | -                                                 | 490  | -    | -    | ns   |

| t <sub>lead</sub> | Enable lead time  | -                                                 | 300  | -    | -    | ns   |

| t <sub>lag</sub>  | Enable lag time   | -                                                 | 150  | -    | -    | ns   |

|                   | Data valid        | SCK = 2 V; SO = 0.2 V;<br>C <sub>L</sub> = 40 pF  | 40   | -    | -    | ns   |

| t <sub>v</sub>    |                   | SCK = 2 V; SO = 0.2 V;<br>C <sub>L</sub> = 200 pF | 150  | -    | -    | ns   |

|                   |                   | SCK = 2 V; SO = 0.2 V;<br>C <sub>L</sub> = 350 pF | 230  | -    | -    | ns   |

| t <sub>su</sub>   | Data setup time   | -                                                 | 40   | -    | -    | ns   |

| t <sub>h</sub>    | Data hold time    | -                                                 | 40   | -    | -    | ns   |

| t <sub>dis</sub>  | Disable time      | -                                                 | 0    | -    | 100  | ns   |

| t <sub>dt</sub>   | Transfer delay    | -                                                 | 300  | -    | -    | ns   |

| t <sub>dld</sub>  | Disable lead time | -                                                 | 250  | -    | -    | ns   |

| t <sub>dlg</sub>  | Disable lag time  | -                                                 | 250  | -    | -    | ns   |

| t <sub>acc</sub>  | Access time       | -                                                 | 8.35 | -    | -    | μs   |

Figure 9. SPI timing information

### 4 Application information

#### 4.1 Power stage switching behavior

The L9959 output stages can either be controlled by the pins PWM and DIR or by their corresponding SPI registers (SPWM and SDIR: see *Table 33* in Configuration Register (CONFIG\_REG)). The SPI bit MUX in the configuration register (CONFIG\_REG) is used to define the driving control strategy of the H-bridge. If the power stages are disabled by /ABE or DIS, this bit is reset and the pins PWM and DIR control the outputs.

The active free-wheeling, in which the body diode is actively shorted by its associated Power-MOS, can be disabled by the bit **FW** in the configuration register (CONFIG\_REG). By default, active free-wheeling is enabled.

The device minimizes electro-magnetic emission by switching the high-side and low-side drivers in a special sequence. Two cases are distinguished: The PWM-mode, during which the current direction does not change and the direction switches using the DIR, which changes the current direction (see *Figure 10*, *Figure 12* and *Figure 13*).

#### 4.1.1 PWM mode (same current direction)

The PWM input pin switches the high-/low-side output of the half-bridge, which is selected by the DIR pin.

DIR = '0': OUT1 is switched, DIR = '1': OUT2 is switched.

PWM = '0': Switched low-side is on, PWM = '1': Switched high-side is on.

Figure 10. PWM mode current flow

Figure 11. PWM mode output voltage

During PWM mode the high-side (e.g. *Figure 10* HS1) output is switched off with a slow slew rate until it is off and the low-side body-diode has taken over the entire current (passive freewheeling). Then the associated low-side transistor (e.g. *Figure 10* LS1) is turned on with a fast slope to reduce the voltage across the device and to minimize the power.

The output is pulled to high voltage, by first turning off the low-side driver with a fast slew rate and, after it is off, the high-side driver is switched on by a slow one (e.g. *Figure 10* LS1, HS1).

This assures, that the voltage and current change over the body diode is done smoothly, reducing the electromagnetic emission.

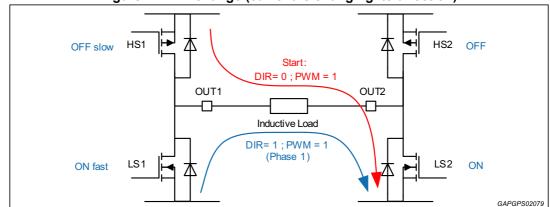

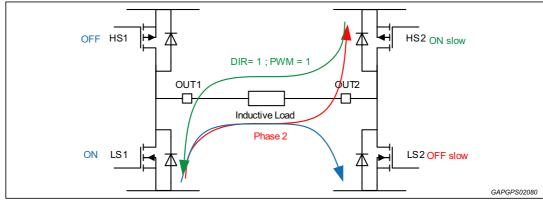

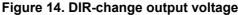

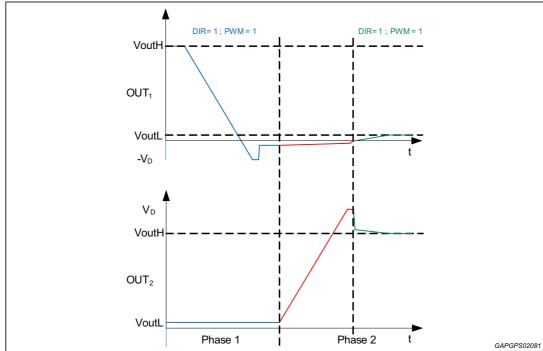

#### 4.1.2 DIR-change mode

The first part of the sequence is identical to the PWM-mode (s.a.). After this has been finished and the associated low-side driver is on (e.g. *Figure 12* LS1), in phase 1 the other low-side driver is turned on (e.g *Figure 12* LS2) to enter passive freewheeling phase. Then in phase 2 the low-side output of OUT2 is switched-off slowly and the current through the load is taken over by the body-diode of the high-side (e.g. *Figure 13* HS2).

Depending on the inductance of the load, the current vanishes more or less quickly. After the low-side driver is turned off, the high-side is switched on with a slow slew-rate.

This assures, that direction switch occurs while the current over the load has vanished, which reduces the electromagnetic emission.

Figure 12. DIR-change (current is changing its direction)

577

Figure 13. DIR-change current flow phase 2

### 4.2 Protection and monitoring

A set of failure as Short-circuit to Ground (SCG), Short-circuit to battery (SCB) and Short-circuit to load (SCL) errors (SBC, SCG, SCL) are confirmed after their occurrence by accessing the error condition after time  $t_{delay\_retest}$  a second time. Only after the error is confirmed, it is entered into the diagnosis register 1 (DIA\_REG1), and the device is disabled and no further diagnosis is run.

The device can be enabled again by the following actions: Power-on reset, disabling and enabling the device using the pins /ABE or DIS (e.g. disabling - enabling sequence). The diagnosis registers can be cleared by sending a reset command by SPI (STATCON\_REG) to either diagnosis register 1 (DIA\_REG1) or 2 (DIA\_REG2). The bit1 (Reset) of the CONFIG\_REG if forced to zero resets both the device registers configuration and diagnosis registers to default but is not able to restart the device. In order to restart IC it is necessary