Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Hi-Speed USB 2.0 to 10/100/1000 Ethernet Controller with HSIC

# **Highlights**

- Single Chip Hi-Speed (HS) USB 2.0 to 10/100/ 1000 Ethernet Controller

- Integrated Gigabit PHY with HP Auto-MDIX

- Integrated 10/100/1000 Ethernet MAC (Full-Duplex Support)

- Integrated USB 2.0 Device Controller

- Integrated USB PHY

- · Low Power Consumption

- Compliant with Energy Efficient Ethernet IEEE 802.3az

- Wake on LAN support (WoL)

- Configuration via One Time Programmable (OTP)

Memory

- NetDetach provides automatic USB attach/detach when Ethernet cable is connected/removed

# **Target Applications**

- · Automotive Infotainment

- · Notebook/Tablet Docking Stations

- · Detachable Laptops

- · USB Port Replicators

- Standalone USB to Ethernet Dongles

- · Embedded Systems / CE Devices

- · Set-Top Boxes / Video Recorders

- · Test Instrumentation / Industrial

## System Considerations

- Power and I/Os

- Multiple power management features

- 12 GPIOs

- Supports bus and self-powered operation

- Variable voltage I/O supply (1.8V-3.3V)

- · Software Support

- Windows 7, 8, 8.1, and 10 driver

- Linux driver

- Mac OS driver

- UEFI support

- PXE support

- Windows line command OTP/EEPROM programming and testing utility

- Packaging

- Pb-free RoHS compliant 56-pin SQFN (8 x 8 mm)

- Environmental

- Commercial temperature range (0°C to +70°C)

- Industrial temperature range (-40°C to +85°C)

## **Key Benefits**

- USB 2.0 Device Controller

- Supports HS (480 Mbps), and FS (12 Mbps) modes

- Four endpoints supported

- Supports vendor specific commands

- Remote wakeup supported

- Integrated HSIC interface

- 10/100/1000 Ethernet Controller

- Compliant with IEEE802.3/802.3u/802.3ab/802.3az

- -10BASE-T/100BASE-TX/1000BASE-T support

- -Full- and half-duplex capability (only full-duplex operation at 1000 Mbps)

- Controller Modes

- -Microsoft AOAC support (Always On Always Connected)

- -Supports Microsoft NDIS 6.2 large send offload

- -Full-duplex flow control

- -Loop-back modes

- -Supports IEEE 802.1q VLAN tagging

- -VLAN tag based packet filtering (all 4096 tags)

- -Flexible address filtering modes

- -33 exact matches (unicast or multicast)

- -512-bit hash filter for multicast frames

- -Pass all multicast

- -Promiscuous unicast/multicast modes

- -Inverse filtering

- -Pass all incoming with status report

- -Supports various statistical counters

- -PME pin support

- Frame Features

- -Supports 32 wake-up frame patterns

- -Preamble generation and removal

- -Automatic 32-bit CRC generation and checking

- -9 KB jumbo frame support

- -Automatic payload padding and pad removal

- -Supports Rx/Tx checksum offloads (IPv4, IPv6, TCP, UDP, IGMP, ICMP)

- -Ability to add and strip IEEE 802.1q VLAN tags

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| 1.0 Preface                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.0 Introduction                                                                                                                    |     |

| 3.0 Pin Descriptions and Configuration                                                                                              |     |

| 4.0 Power Connections                                                                                                               |     |

| 5.0 USB Device Controller                                                                                                           | 17  |

| 6.0 FIFO Controller (FCT)                                                                                                           | 43  |

| 7.0 Receive Filtering Engine (RFE)                                                                                                  | 60  |

| 8.0 10/100/1000 Ethernet MAC                                                                                                        |     |

| 9.0 Gigabit Ethernet PHY (GPHY)                                                                                                     | 91  |

| 10.0 EEPROM Controller (EEP)                                                                                                        | 99  |

| 11.0 One Time Programmable (OTP) Memory                                                                                             |     |

| 12.0 Resets                                                                                                                         |     |

| 13.0 Clocks and Power management (CPM)                                                                                              |     |

| 14.0 Power Management Event (PME) Operation                                                                                         |     |

| 15.0 Register Descriptions                                                                                                          | 140 |

| 16.0 Operational Characteristics                                                                                                    | 262 |

| 14.0 Power Management Event (PME) Operation  15.0 Register Descriptions  16.0 Operational Characteristics  17.0 Package Information | 270 |

| 18.0 Revision History                                                                                                               | 273 |

# 1.0 PREFACE

# 1.1 General Terms

TABLE 1-1: GENERAL TERMS

| Term                       | Description                                                                                                                                                                                      |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 10BASE-T                   | 10 Mbps Ethernet, IEEE 802.3 compliant                                                                                                                                                           |  |

| 100BASE-TX                 | 100 Mbps Fast Ethernet, IEEE802.3u compliant                                                                                                                                                     |  |

| 1000BASE-T                 | 100 Mbps Fast Ethernet, IEEE802.3ab compliant                                                                                                                                                    |  |

| ADC                        | Analog-to-Digital Converter                                                                                                                                                                      |  |

| AFE                        | Analog Front End                                                                                                                                                                                 |  |

| ALR                        | Address Logic Resolution                                                                                                                                                                         |  |

| AN                         | Auto-Negotiation                                                                                                                                                                                 |  |

| AOAC                       | Always on Always Connected                                                                                                                                                                       |  |

| ARP                        | Address Resolution Protocol                                                                                                                                                                      |  |

| BELT                       | Best Effort Latency Tolerance                                                                                                                                                                    |  |

| BLW                        | Baseline Wander                                                                                                                                                                                  |  |

| Byte                       | 8 bits                                                                                                                                                                                           |  |

| СРМ                        | Clocks and Power Management                                                                                                                                                                      |  |

| CSMA/CD                    | Carrier Sense Multiple Access/Collision Detect                                                                                                                                                   |  |

| CSR                        | Control and Status Registers                                                                                                                                                                     |  |

| CTR                        | Counter                                                                                                                                                                                          |  |

| DA                         | Destination Address                                                                                                                                                                              |  |

| DWORD                      | 32 bits                                                                                                                                                                                          |  |

| EC                         | Embedded Controller                                                                                                                                                                              |  |

| EEE                        | Energy Efficient Ethernet                                                                                                                                                                        |  |

| EP                         | USB Endpoint                                                                                                                                                                                     |  |

| EPC                        | EEPROM Controller                                                                                                                                                                                |  |

| FCS                        | Frame Check Sequence - The extra checksum characters added to the end of an Ethernet frame, used for error detection and correction.                                                             |  |

| FCT                        | FIFO Controller                                                                                                                                                                                  |  |

| FIFO                       | First In First Out buffer                                                                                                                                                                        |  |

| FS                         | Full Speed                                                                                                                                                                                       |  |

| FSM                        | Finite State Machine                                                                                                                                                                             |  |

| FW                         | Firmware                                                                                                                                                                                         |  |

| GMII                       | Gigabit Media Independent Interface                                                                                                                                                              |  |

| GPIO                       | General Purpose I/O                                                                                                                                                                              |  |

| GPHY                       | Gigabit Ethernet Physical Layer                                                                                                                                                                  |  |

| Host                       | External system (Includes processor, application software, etc.)                                                                                                                                 |  |

| HS                         | High Speed                                                                                                                                                                                       |  |

| HW                         | Hardware. Refers to function implemented by digital logic.                                                                                                                                       |  |

| IGMP                       | Internet Group Management Protocol                                                                                                                                                               |  |

| Inbound                    | Refers to data input to the device from the host                                                                                                                                                 |  |

| LDO                        | Linear Drop-Out Regulator                                                                                                                                                                        |  |

| Level-Triggered Sticky Bit | This type of status bit is set whenever the condition that it represents is asserted. The bit remains set until the condition is no longer true and the status bit is cleared by writing a zero. |  |

TABLE 1-1: GENERAL TERMS (CONTINUED)

| Term     | Description                                                                                                                                                                                                                                                                  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LFPS     | Low Frequency Periodic Signal                                                                                                                                                                                                                                                |  |  |

| LFSR     | Linear Feedback Shift Register                                                                                                                                                                                                                                               |  |  |

| LPM      | Link Power Management                                                                                                                                                                                                                                                        |  |  |

| Isb      | Least Significant Bit                                                                                                                                                                                                                                                        |  |  |

| LSB      | Least Significant Byte                                                                                                                                                                                                                                                       |  |  |

| LTM      | Latency Tolerance Messaging                                                                                                                                                                                                                                                  |  |  |

| MAC      | Media Access Controller                                                                                                                                                                                                                                                      |  |  |

| MDI      | Medium Dependent Interface                                                                                                                                                                                                                                                   |  |  |

| MDIX     | Media Dependent Interface with Crossover                                                                                                                                                                                                                                     |  |  |

| MEF      | Multiple Ethernet Frames                                                                                                                                                                                                                                                     |  |  |

| MII      | Media Independent Interface                                                                                                                                                                                                                                                  |  |  |

| MIIM     | Media Independent Interface Management                                                                                                                                                                                                                                       |  |  |

| MIL      | MAC Interface Layer                                                                                                                                                                                                                                                          |  |  |

| MLD      | Multicast Listening Discovery                                                                                                                                                                                                                                                |  |  |

| MLT-3    | Multi-Level Transmission Encoding (3-Levels). A tri-level encoding method where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0".                                                            |  |  |

| msb      | Most Significant Bit                                                                                                                                                                                                                                                         |  |  |

| MSB      | Most Significant Byte                                                                                                                                                                                                                                                        |  |  |

| NRZI     | Non Return to Zero Inverted. This encoding method inverts the signal for a "1" and leaves the signal unchanged for a "0"                                                                                                                                                     |  |  |

| N/A      | Not Applicable                                                                                                                                                                                                                                                               |  |  |

| NC       | No Connect                                                                                                                                                                                                                                                                   |  |  |

| OTP      | One Time Programmable                                                                                                                                                                                                                                                        |  |  |

| OUI      | Organizationally Unique Identifier                                                                                                                                                                                                                                           |  |  |

| Outbound | Refers to data output from the device to the host                                                                                                                                                                                                                            |  |  |

| PCS      | Physical Coding Sublayer                                                                                                                                                                                                                                                     |  |  |

| PHY      | Physical Layer                                                                                                                                                                                                                                                               |  |  |

| PISO     | Parallel In Serial Out                                                                                                                                                                                                                                                       |  |  |

| PLL      | Phase Locked Loop                                                                                                                                                                                                                                                            |  |  |

| PMD      | Physical Medium Dependent                                                                                                                                                                                                                                                    |  |  |

| PME      | Power Management Event                                                                                                                                                                                                                                                       |  |  |

| PMIC     | Power Management IC                                                                                                                                                                                                                                                          |  |  |

| POR      | Power on Reset                                                                                                                                                                                                                                                               |  |  |

| PTP      | Precision Time Protocol                                                                                                                                                                                                                                                      |  |  |

| QWORD    | 64 bits                                                                                                                                                                                                                                                                      |  |  |

| RESERVED | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must always be zero for write operations. Unless otherwise noted, values are not guaranteed when reading reserved bits. Unless otherwise noted, do not read or write to reserved addresses. |  |  |

| RFE      | Receive Filtering Engine                                                                                                                                                                                                                                                     |  |  |

| RGMII    | Reduced Gigabit Media Independent Interface                                                                                                                                                                                                                                  |  |  |

| RMON     | Remote Monitoring                                                                                                                                                                                                                                                            |  |  |

|          | Reduced Media Independent Interface                                                                                                                                                                                                                                          |  |  |

| RMII     |                                                                                                                                                                                                                                                                              |  |  |

| RST      | Reset                                                                                                                                                                                                                                                                        |  |  |

# TABLE 1-1: GENERAL TERMS (CONTINUED)

| Term | Description                                                                                         |  |

|------|-----------------------------------------------------------------------------------------------------|--|

| SA   | Source Address                                                                                      |  |

| SCSR | System Control and Status Registers                                                                 |  |

| SEF  | Single Ethernet Frame                                                                               |  |

| SFD  | Start of Frame Delimiter - The 8-bit value indicating the end of the preamble of an Ethernet frame. |  |

| SIPO | Serial In Parallel Out                                                                              |  |

| SMI  | Serial Management Interface                                                                         |  |

| SMNP | Simple Network Management Protocol                                                                  |  |

| SQE  | Signal Quality Error (also known as "heartbeat")                                                    |  |

| SSD  | Start of Stream Delimiter                                                                           |  |

| TMII | Turbo Media Independent Interface                                                                   |  |

| UDP  | User Datagram Protocol - A connectionless protocol run on top of IP networks                        |  |

| URX  | USB Bulk-Out Receiver                                                                               |  |

| USB  | Universal Serial Bus                                                                                |  |

| UTX  | USB Bulk-In Transmitter                                                                             |  |

| UUID | Universally Unique IDentifier                                                                       |  |

| VSM  | Vendor Specific Messaging                                                                           |  |

| WORD | 16 bits                                                                                             |  |

| ZLP  | Zero Length USB Packet                                                                              |  |

# 1.2 Buffer Types

TABLE 1-2: BUFFER TYPES

| Buffer Type | Description                                                                                                                                                                                                                                   |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VIS         | Variable voltage Schmitt-triggered input                                                                                                                                                                                                      |  |  |

| O8          | Output with 8 mA sink and 8 mA source                                                                                                                                                                                                         |  |  |

| OD8         | Open-drain output with 8 mA sink                                                                                                                                                                                                              |  |  |

| O12         | Output with 12 mA sink and 12 mA source                                                                                                                                                                                                       |  |  |

| OD12        | Open-drain output with 12 mA sink                                                                                                                                                                                                             |  |  |

| HSIC        | High-Speed Inter-Chip (HSIC) USB Electrical Specification compliant input/output                                                                                                                                                              |  |  |

| PU          | 50 μA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                        |  |  |

|             | Note: Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.  |  |  |

| PD          | 50 μA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                    |  |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |  |  |

| Al          | Analog Input                                                                                                                                                                                                                                  |  |  |

| AIO         | Analog bidirectional                                                                                                                                                                                                                          |  |  |

| ICLK        | Crystal oscillator input pin                                                                                                                                                                                                                  |  |  |

| OCLK        | Crystal oscillator output pin                                                                                                                                                                                                                 |  |  |

| Р           | Power pin                                                                                                                                                                                                                                     |  |  |

# 1.3 Register Nomenclature

TABLE 1-3: REGISTER NOMENCLATURE

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                                                                                                                          |  |

| W                          | Write: A register or bit with this attribute can be written.                                                                                                                                                                                                                                                                                                                      |  |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                                                                                                                      |  |

| RS                         | Read to Set: This bit is set on read.                                                                                                                                                                                                                                                                                                                                             |  |

| RC                         | Read to Clear: Contents is cleared after the read. Writes have no effect.                                                                                                                                                                                                                                                                                                         |  |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                                                                                                               |  |

| WC                         | Write One to Clear: Writing a one clears the value. Writing a zero has no effect                                                                                                                                                                                                                                                                                                  |  |

| WAC                        | Write Anything to Clear: Writing anything clears the value.                                                                                                                                                                                                                                                                                                                       |  |

| LL                         | Latch Low: Clear on read of register.                                                                                                                                                                                                                                                                                                                                             |  |

| LH                         | Latch High: Clear on read of register.                                                                                                                                                                                                                                                                                                                                            |  |

| SC                         | <b>Self-Clearing:</b> Contents are self-cleared after the being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                                                                                                                         |  |

| SS                         | <b>Self-Setting:</b> Contents are self-setting after being cleared. Writes of one have no effect. Contents can be read.                                                                                                                                                                                                                                                           |  |

| RO/LH                      | <b>Read Only, Latch High:</b> This mode is used by the Ethernet PHY registers. Bits with this attribute will stay high until the bit is read. After it is read, the bit will remain high, but will change to low if the condition that caused the bit to go high is removed. If the bit has not been read, the bit will remain high regardless of a change to the high condition. |  |

| NALR                       | <b>Not Affected by Lite Reset.</b> The state of NASR bits do not change on assertion of a lite reset.                                                                                                                                                                                                                                                                             |  |

| NASR                       | <b>Not Affected by Software Reset.</b> The state of NASR bits do not change on assertion of a software reset.                                                                                                                                                                                                                                                                     |  |

| RESERVED                   | <b>Reserved Field:</b> Reserved fields must be written with zeros, unless otherwise indicated, to ensure future compatibility. The value of reserved bits is not guaranteed on a read.                                                                                                                                                                                            |  |

## 2.0 INTRODUCTION

# 2.1 General Description

The LAN7850 is a high performance Hi-SpeedUSB 2.0 to 10/100/1000 Ethernet controller with an integrated 10/100/1000 Ethernet PHY and High-Speed Inter-Connect (HSIC) interface. With applications ranging from notebook/tablet docking stations, set-top boxes, and PVRs, to USB port replicators, USB to Ethernet dongles, embedded systems, and test instrumentation, the LAN7850 is a high performance and cost effective USB/HSIC to Ethernet connectivity solution.

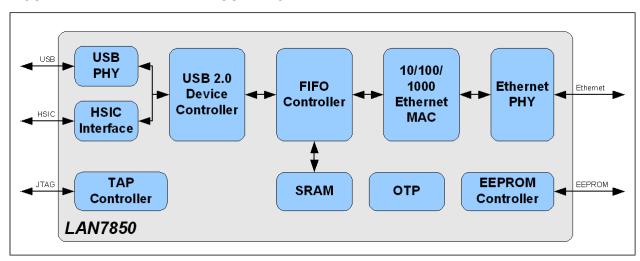

The LAN7850 contains an integrated 10/100/1000 Ethernet MAC and PHY, Filtering Engine, USB PHY (with HSIC interface), Hi-Speed USB 2.0 device controller, TAP controller, EEPROM controller, and a FIFO controller with internal packet buffering.

The internal USB 2.0 device controller and USB PHY are compliant with the USB 2.0 Hi-Speed standard. The LAN7850 implements Control, Interrupt, Bulk-in, and Bulk-out USB Endpoints.

The Ethernet controller supports auto-negotiation, auto-polarity correction, HP Auto-MDIX, and is compliant with the IEEE 802.3u, IEEE 802.3u, IEEE 802.3ab, and 802.3az (Energy Efficient Ethernet) standards. ARP and NS offload are also supported.

Multiple power management features are provided, including Energy Efficient Ethernet (IEEE 802.3az), support for Microsoft's Always On Always Connected (AOAC), and "Magic Packet", "Wake On LAN", and "Link Status Change" wake events. Wake events can be programmed to initiate a USB remote wakeup. Up to 32 different AOAC wake-up frame patterns are supported along with Microsoft's WPD (Whole Packet Detection).

An internal EEPROM controller exists to load various USB and Ethernet configuration parameters. For EEPROM-less applications, the LAN7850 provides 1K Bytes of OTP memory that can be used to preload this same configuration data before enumeration. The integrated IEEE 1149.1 compliant TAP controller provides boundary scan via JTAG.

The LAN7850 is available in commercial and industrial temperature range versions. An internal block diagram of the LAN7850 is shown in Figure 2-1.

FIGURE 2-1: INTERNAL BLOCK DIAGRAM

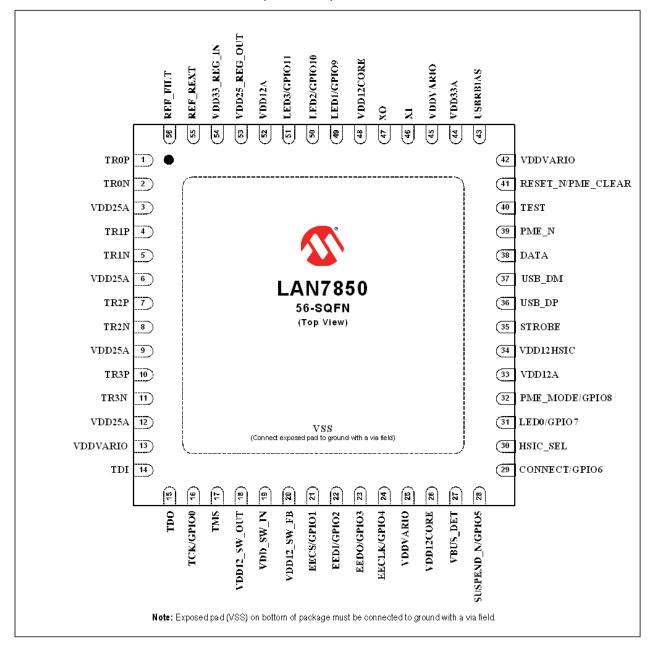

# 3.0 PIN DESCRIPTIONS AND CONFIGURATION

# 3.1 Pin Assignments

FIGURE 3-1: PIN ASSIGNMENTS (TOP VIEW)

**Note:** When an "\_N" is used at the end of the signal name, it indicates that the signal is active low. For example, RESET\_N indicates that the reset signal is active low.

The buffer type for each signal is indicated in the "Buffer Type" column of the pin description tables in Section 3.2, "Pin Descriptions". A description of the buffer types is provided in Section 1.2, "Buffer Types".

TABLE 3-1: PIN ASSIGNMENTS

| Pin Number                                    | Pin Name        | Pin Number | Pin Name          |  |

|-----------------------------------------------|-----------------|------------|-------------------|--|

| 1                                             | TR0P            | 29         | CONNECT/GPIO6     |  |

| 2                                             | TR0N            | 30         | HSIC_SEL          |  |

| 3                                             | VDD25A          | 31         | LED0/GPIO7        |  |

| 4                                             | TR1P            | 32         | PME_MODE/GPIO8    |  |

| 5                                             | TR1N            | 33         | VDD12A            |  |

| 6                                             | VDD25A          | 34         | VDD12HSIC         |  |

| 7                                             | TR2P            | 35         | STROBE            |  |

| 8                                             | TR2N            | 36         | USB_DP            |  |

| 9                                             | VDD25A          | 37         | USB_DM            |  |

| 10                                            | TR3P            | 38         | DATA              |  |

| 11                                            | TR3N            | 39         | PME_N             |  |

| 12                                            | VDD25A          | 40         | TEST              |  |

| 13                                            | VDDVARIO        | 41         | RESET_N/PME_CLEAR |  |

| 14                                            | TDI             | 42         | VDDVARIO          |  |

| 15                                            | TDO             | 43         | USBRBIAS          |  |

| 16                                            | TCK/GPIO0       | 44         | VDD33A            |  |

| 17                                            | TMS             | 45         | VDDVARIO          |  |

| 18                                            | VDD12_SW_OUT    | 46         | XI                |  |

| 19                                            | VDD_SW_IN       | 47         | XO                |  |

| 20                                            | VDD12_SW_FB     | 48         | VDD12CORE         |  |

| 21                                            | EECS/GPIO1      | 49         | LED1/GPIO9        |  |

| 22                                            | EEDI/GPIO2      | 50         | LED2/GPIO10       |  |

| 23                                            | EEDO/GPIO3      | 51         | LED3/GPIO11       |  |

| 24                                            | EECLK/GPIO4     | 52         | VDD12A            |  |

| 25                                            | VDDVARIO        | 53         | VDD25_REG_OUT     |  |

| 26                                            | VDD12CORE       | 54         | VDD33_REG_IN      |  |

| 27                                            | VBUS_DET        | 55         | REF_REXT          |  |

| 28                                            | SUSPEND_N/GPIO5 | 56         | REF_FILT          |  |

| Exposed Pad (VSS) must be connected to ground |                 |            |                   |  |

# 3.2 Pin Descriptions

**TABLE 3-2: PIN DESCRIPTIONS**

| Name                                 | Symbol   | Buffer<br>Type | Description                                                                                                                                                      |  |

|--------------------------------------|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Gigabit Ethernet Pins                |          |                |                                                                                                                                                                  |  |

| Ethernet TX/RX Positive Channel 0    | TR0P     | AIO            | Transmit/Receive Positive Channel 0.                                                                                                                             |  |

| Ethernet TX/RX<br>Negative Channel 0 | TRON     | AIO            | Transmit/Receive Negative Channel 0.                                                                                                                             |  |

| Ethernet TX/RX Positive Channel 1    | TR1P     | AIO            | Transmit/Receive Positive Channel 1.                                                                                                                             |  |

| Ethernet TX/RX<br>Negative Channel 1 | TR1N     | AIO            | Transmit/Receive Negative Channel 1.                                                                                                                             |  |

| Ethernet TX/RX Positive Channel 2    | TR2P     | AIO            | Transmit/Receive Positive Channel 2.                                                                                                                             |  |

| Ethernet TX/RX<br>Negative Channel 2 | TR2N     | AIO            | Transmit/Receive Negative Channel 2.                                                                                                                             |  |

| Ethernet TX/RX Positive Channel 3    | TR3P     | AIO            | Transmit/Receive Positive Channel 3.                                                                                                                             |  |

| Ethernet TX/RX<br>Negative Channel 3 | TR3N     | AIO            | Transmit/Receive Negative Channel 3.                                                                                                                             |  |

| External PHY<br>Reference Filter     | REF_FILT | Al             | External PHY Reference Filter. Connect to an external 1uF capacitor to ground.                                                                                   |  |

| External PHY<br>Reference Resistor   | REF_REXT | Al             | External PHY Reference Resistor. Connect to an external 2K 1.0% resistor to ground.                                                                              |  |

| 1                                    |          | ·              | JSB Pins                                                                                                                                                         |  |

| USB 2.0<br>DPLUS                     | USB_DP   | AIO            | Hi-Speed USB data plus.                                                                                                                                          |  |

| USB 2.0<br>DMINUS                    | USB_DM   | AIO            | Hi-Speed USB Speed data minus.                                                                                                                                   |  |

| External USB<br>Bias Resistor        | USBRBIAS | Al             | Used for setting HS transmit current level and on-chip termination impedance. Connect to an external 12K 1.0% resistor to ground.                                |  |

| HSIC STROBE                          | STROBE   | HSIC           | Bi-directional data strobe signal as defined in the High-<br>Speed Inter-Chip USB Electrical Specification.                                                      |  |

| HSIC DATA                            | DATA     | HSIC           | Bi-directional Double Data Rate (DDR) data signal that is synchronous to the STROBE signal as defined in the High-Speed Inter-Chip USB Electrical Specification. |  |

|                                      |          | Misce          | Illaneous Pins                                                                                                                                                   |  |

| Detect Upstream<br>VBUS Power        | VBUS_DET | VIS<br>(PD)    | Detects the state of the upstream bus power.                                                                                                                     |  |

|                                      |          |                | For bus powered operation, this pin must be tied to VDD33A. Refer to Section 4.0, "Power Connections" for additional information.                                |  |

| USB Connect                          | CONNECT  | O12            | This pin asserts when the device is attempting to attach to the USB host.                                                                                        |  |

|                                      |          |                | This pin is intended to help address a known bug on existing HSIC host controllers where the HSIC connect signaling is missed.                                   |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| TABLE 0-2. TIN              | ABLE 3-2: PIN DESCRIPTIONS (CONTINUED) |                        |                                                                                                                                                                                                |  |

|-----------------------------|----------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                        | Symbol                                 | Buffer<br>Type         | Description                                                                                                                                                                                    |  |

| HSIC Select                 | HSIC_SEL                               | VIS                    | When tied to VDD, the device HSIC interface is enabled. Otherwise, the USB 2.0 interface is enabled.                                                                                           |  |

|                             |                                        |                        | <b>Note:</b> This is a static signal that may not be changed at run time.                                                                                                                      |  |

| PME                         | PME_N                                  | O8/OD8                 | This pin is used to signal PME when the PME mode of operation is in effect.                                                                                                                    |  |

| PME Mode Select             | PME_MODE                               | VIS                    | This pin serves as the PME mode selection input when the PME mode of operation is in effect.                                                                                                   |  |

| PME Clear                   | PME_CLEAR                              | VIS                    | This pin may serves as PME clear input when the PME mode of operation is in effect.                                                                                                            |  |

| USB Suspend                 | SUSPEND_N                              | O12                    | This pin is asserted when the device is in one of the suspend states as defined in Section 13.3, "Suspend States".                                                                             |  |

|                             |                                        |                        | This pin may be configured to place an external switcher into a low power state such as when the device is in SUSPEND2.                                                                        |  |

| General Purpose<br>I/O 0-11 | GPIO[0:11]                             | VIS/O8/<br>OD8<br>(PU) | These general purpose I/O pins are each fully programmable as either a push-pull output, an open-drain output, or a Schmitt-triggered input. A programmable pull-up may optionally be enabled. |  |

| Indicator LEDs 0-3          | LED[0:3]                               | OD12                   | These LEDs can be configured to indicate Ethernet link, activity, duplex, and collision. Refer to Section 9.3, "LED Interface," on page 94 for additional information.                         |  |

| System Reset                | RESET_N                                | VIS                    | System reset. This pin is active low.                                                                                                                                                          |  |

|                             |                                        |                        | If this signal is unused it must be pulled-up to VDD.                                                                                                                                          |  |

| Test Pin                    | TEST                                   | VIS                    | Test pin. This pin is used for internal purposes only and must be connected to ground for proper operation.                                                                                    |  |

| ·                           |                                        | Е                      | EPROM                                                                                                                                                                                          |  |

| EEPROM<br>Chip Select       | EECS                                   | 012                    | This pin drives the chip select output of the external EEPROM.                                                                                                                                 |  |

| EEPROM Data In              | EEDI                                   | VIS                    | This pin is driven by the EEDO output of the external EEPROM.                                                                                                                                  |  |

| EEPROM Data Out             | EEDO                                   | 012                    | This pin drives the EEDI input of the external EEPROM.                                                                                                                                         |  |

| EEPROM Clock                | EECLK                                  | 012                    | This pin drives the EEPROM clock of the external EEPROM.                                                                                                                                       |  |

|                             |                                        | •                      | JTAG                                                                                                                                                                                           |  |

| JTAG<br>Test Mode Select    | TMS                                    | VIS                    | JTAG test mode select.                                                                                                                                                                         |  |

| JTAG<br>Test Clock          | TCK                                    | VIS                    | JTAG test clock.                                                                                                                                                                               |  |

|                             |                                        |                        | The maximum operating frequency of this clock is half of the system clock.                                                                                                                     |  |

| JTAG<br>Test Data Input     | TDI                                    | VIS                    | JTAG data input.                                                                                                                                                                               |  |

| JTAG<br>Test Data Output    | TDO                                    | O12                    | JTAG data output.                                                                                                                                                                              |  |

TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                                      | Symbol        | Buffer<br>Type | Description                                                                                                                    |  |

|-------------------------------------------|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Clock Interface                           |               |                |                                                                                                                                |  |

| Crystal Input                             | XI            | ICLK           | External 25 MHz crystal input.                                                                                                 |  |

|                                           |               |                | Note: This pin can also be driven by a single-ended clock oscillator. When this method is used, XO should be left unconnected. |  |

| Crystal Output                            | XO            | OCLK           | External 25 MHz crystal output.                                                                                                |  |

|                                           | I/O Power     | pins, Core     | Power Pins, and Ground Pad                                                                                                     |  |

| Variable I/O Power<br>Supply Input        | VDDVARIO      | Р              | +1.8V - +3.3V variable supply for I/Os.  Refer to Section 4.0, "Power Connections," on page 16 for connection information.     |  |

| +3.3V Analog                              | VDD33A        | Р              | +3.3V analog power supply for USB 2.0 AFE.                                                                                     |  |

| Power Supply Input                        |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |

| +2.5V Analog<br>Power Supply Input        | VDD25A        | Р              | +2.5V analog power supply input for Gigabit Ethernet PHY.  Refer to Section 4.0, "Power Connections," on page 16 for           |  |

|                                           |               |                | connection information.                                                                                                        |  |

| +1.2V Ethernet Port<br>Power Supply Input | VDD12A        | Р              | +1.2V analog power supply input for USB PLL/AFE.  Refer to Section 4.0, "Power Connections," on page 16 for                    |  |

|                                           |               |                | connection information.                                                                                                        |  |

| +1.2V Digital Core<br>Power Supply Input  | VDD12CORE     | Р              | +1.2V digital core power supply input.  Refer to Section 4.0, "Power Connections," on page 16 for                              |  |

|                                           |               |                | connection information.                                                                                                        |  |

| +1.2V HSIC Power<br>Supply Input          | VDD12HSIC     | Р              | +1.2V HSIC power supply input.  Refer to Section 4.0, "Power Connections," on page 16 for                                      |  |

|                                           |               |                | connection information.                                                                                                        |  |

| +3.3V LDO Input                           | VDD33_REG_IN  | Р              | +3.3V power supply input to the integrated LDO.                                                                                |  |

| Voltage                                   |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |

| +2.5V LDO Output                          | VDD25_REG_OUT | Р              | +2.5V power supply output from the integrated LDO. This is used to supply power to Gigabit Ethernet PHY AFE.                   |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |

| Switcher Input                            | VDD_SW_IN     | Р              | +2.5V-+3.3V input voltage for switching regulator.                                                                             |  |

| Voltage                                   |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |

| Switcher Feedback                         | VDD12_SW_FB   | Р              | Feedback pin for the integrated switching regulator.                                                                           |  |

|                                           |               |                | Refer to Section 4.0, "Power Connections," on page 16 for connection information.                                              |  |

|                                           |               |                | Note: To disable the switcher, tie this pin to VDD_SW_IN.                                                                      |  |

# TABLE 3-2: PIN DESCRIPTIONS (CONTINUED)

| Name                             | Symbol       | Buffer<br>Type | Description                                                                                                           |

|----------------------------------|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------|

| +1.2V Switcher<br>Output Voltage | VDD12_SW_OUT | Р              | +1.2V power supply output voltage for switching regulator.  Refer to Section 4.0, "Power Connections," on page 16 for |

|                                  |              |                | connection information.                                                                                               |

| Ground                           | VSS          | Р              | Common Ground                                                                                                         |

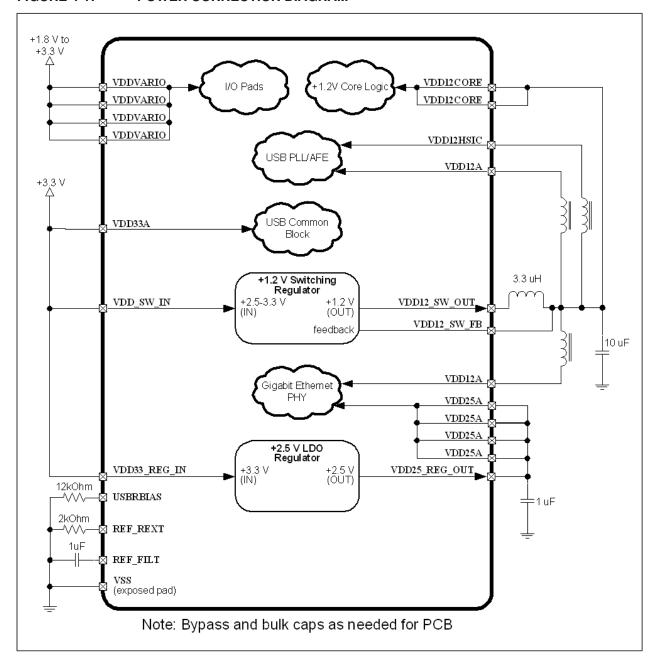

## 4.0 POWER CONNECTIONS

Figure 4-1 illustrates the device power connections in a typical application. Refer to the device reference schematic for additional information. Refer to Section 3.0, "Pin Descriptions and Configuration," on page 10 for additional pin information.

FIGURE 4-1: POWER CONNECTION DIAGRAM

Note: For 3.3V I/O operation, the VDDVARIO and +3.3V supplies may be connected together.

To disable the internal switcher, tie the VDD12\_SW\_FB pin to VDD\_SW\_IN.

### 5.0 USB DEVICE CONTROLLER

#### 5.1 Overview

The USB functionality consists of five major parts. The USB PHY, UDC (USB Device Controller), URX (USB Bulk Out Receiver), UTX (USB Bulk In Transmitter), and CTL (USB Control Block).

The UDC is configured to support one configuration, one interface, one alternate setting, and four endpoints. Streams are not supported in this device. The URX and UTX implement the Bulk-Out and Bulk-In endpoints respectively. The CTL manages Control and Interrupt endpoints.

Each USB Controller endpoint is unidirectional with even numbered endpoints handling the OUT (from the host, actually RX into the device) direction and odd numbered endpoints handling the IN (to the host, actually TX from the device) direction.

The UDC endpoint numbers start at 0 and increment. Endpoint numbers are not skipped and have a fixed mapping to the USB endpoint numbers. The corresponding USB endpoint is obtained by dividing the UDC endpoint number by 2 (rounding down). For example, single directional endpoint 0 indicates USB OUT endpoint 0, and single directional endpoint 1 corresponds to USB IN endpoint 0.

The mapping of the device's USB endpoints to the UDC endpoints is shown in Table 5-1. As can be seen, one IN and two OUT endpoints on the UDC are not utilized.

| Endpoint Function | USB EP number |

|-------------------|---------------|

| Control OUT       | 0             |

| Control IN        | 0             |

| unused            | NA            |

| Bulk IN           | 1             |

| Bulk OUT          | 2             |

| unused            | NA            |

| unused            | NA            |

| Interrupt IN      | 3             |

TABLE 5-1: DEVICE TO UDC ENDPOINT MAPPING

# 5.2 Control Endpoint

The Control endpoint is handled by the CTL (USB Control) module. The CTL module is responsible for handling standard USB requests, as well as USB vendor commands. The UDC does not handle USB commands. These commands are passed to the CTL for completion.

# 5.2.1 USB STANDARD COMMAND PROCESSING

This section lists the supported USB standard device requests. The basic format of a device request is shown in section 9.3 of the USB 2.0 specification and the standard device requests are described in section 9.4. Valid values of the parameters are given below.

Per the USB specifications, if an unsupported or invalid request is made to a USB device, the device responds by returning STALL in the Data or Status stage of the request. Receipt of an unsupported or invalid request does NOT cause the optional Halt feature on the control pipe to be set.

For each request supported, the USB specifications provide details on the device behavior during the various configuration states and on the conditions which will return a Request Error. Some requests affect the state of the hardware.

In order to implement the Get Descriptor command, the CTL manages a 128x32 Descriptor RAM. The RAMs contents are initialized via the EEPROM or OTP, after a system reset occurs. The Descriptor RAM may also be programmed by the device driver to support EEPROM-Less mode.

TABLE 5-2: STRING DESCRIPTOR INDEX MAPPINGS

| INDEX | STRING NAME          |

|-------|----------------------|

| 0     | Language ID          |

| 1     | Manufacturer ID      |

| 2     | Product ID           |

| 3     | Serial Number        |

| 4     | Configuration String |

| 5     | Interface String     |

When the UDC decodes a Get Descriptor command, it will pass a pointer to the CTL. The CTL uses this pointer to determine what the command is and how to fill it.

#### 5.2.1.1 Clear Feature

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wValue - Specifies the feature, 1=Device Remote Wakeup and 0=Endpoint Halt.

windex - Always 0 when the device is selected, specifies the interface number (always 0) when an interface is selected or the direction/endpoint number (0, 80h, 81h, 2 or 83h) when an endpoint is selected.

A ClearFeature(Endpoint Halt) request will clear the USB 2.0 data toggle for the specified endpoint.

## 5.2.1.2 Get Configuration

All parameters are fixed per the USB specifications.

#### 5.2.1.3 Get Descriptor

wValue - The high byte selects the descriptor type. The supported descriptors for this command are 1=Device, 2=Configuration (including Interface, Endpoint descriptors and Endpoint Companion descriptors (USB 2.1 LPM)), 3=String, 6=Device Qualifier (HS/FS), 7=Other Speed Configuration (USB2.0). The low byte selects the descriptor index and must be 0.

**Note:** Direct access to the Interface, Endpoint and Endpoint Companion (USB 2.1 LPM) descriptors are not supported by this command and will cause a USB stall.

wIndex - Specifies the Language ID for string descriptors or is 0 for other descriptors.

wLength - Specifies the number of bytes to return. If the descriptor is longer than the wLength field, only the initial bytes of the descriptor are returned. If the descriptor is shorter than the wLength field, the device indicates the end of the control transfer by sending a short packet when further data is requested. A short packet is defined as a packet shorter than the maximum payload size or a zero length data packet.

#### 5.2.1.4 Get Interface

wIndex - Specifies the interface, always 0 for this device.

### 5.2.1.5 Get Status

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wIndex - Always 0 when the device is selected, specifies the interface number (always 0) when an interface is selected or the direction/endpoint number (0, 80h, 81h, 2 or 83h) when an endpoint is selected.

**Note:** Power Method (PWR\_SEL) in Hardware Configuration Register (HW\_CFG) is used as the source for the Self-Power bit (D0).

#### 5.2.1.6 Set Address

wValue - Specifies the new device address.

Per the USB specification, the USB device does not change its device address until after the Status stage of this request is completed successfully. This is a difference between this request and all other requests. For all other requests, the operation indicated must be completed before the Status stage.

### 5.2.1.7 Set Configuration

wValue - The lower byte specifies the configuration value.

The device supports only one configuration. A value of 1 places the device into the Configured state while a value of 0 places the device into the Address state.

The Halt feature is reset for all endpoints upon the receipt of this request with a valid configuration value.

The USB 2.0 data toggle for all endpoints are initialized upon the receipt of this request with a valid configuration value.

#### 5.2.1.8 Set Descriptor

This optional request is not supported and the device responds by returning STALL.

#### 5.2.1.9 Set Feature

bmRequestType - 00h for the device, 01h for interfaces and 02h for endpoints.

wValue - Specifies the feature, 1=Device Remote Wakeup, 2=device Test Mode, 0=Endpoint Halt.