# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## LAN8820/LAN8820

### RGMII 10/100/1000 Ethernet Transceiver with HP Auto-MDIX Support

#### Highlights

- Single-Chip Ethernet Physical Layer Transceiver (PHY)

- Compliant with IEEE 802.3ab (1000BASE-T), IEEE 802.3u (Fast Ethernet), and ISO 802-3/IEEE 802.3 (10BASE-T)

- HP Auto-MDIX support in accordance with IEEE 802.3ab specification at 10/100/1000 Mbps operation

- Miniature 56-pin QFN lead-free RoHS compliant package with RGMII (8 x 8 x 0.85 mm height)

- · Implements Reduced Power Operating Modes

#### **Target Applications**

- Set-Top Boxes

- Networked Printers and Servers

- Test Instrumentation

- · LAN on Motherboard

- Embedded Telecom Applications

- Video Record/Playback Systems

- Cable Modems/Routers

- DSL Modems/Routers

- · Digital Video Recorders

- · IP and Video Phones

- · Wireless Access Points

- · Digital Televisions

- Digital Media Adapters/Servers

- · Gaming Consoles

- POE Applications

#### Key Benefits

- High-Performance 10/100/1000 Ethernet Transceiver

- Compliant with IEEE 802.3ab (1000BASE-T)

- Compliant with IEEE 802.3/802.3u (Fast Ethernet)

- Compliant with ISO 802-3/IEEE 802.3 (10BASE-T)

- 10BASE-T, 100BASE-TX and 1000BASE-T support

- Loop-back modes

- Auto-negotiation (NEXT page support)

- Automatic polarity detection and correction

- Link status change wake-up detection

- Vendor specific register functions

- Supports reduced pin count RGMII interface

- Controlled impedance outputs

- Supports RGMII ID mode

- Three status LED outputs

- Compliant with IEEE 802.3-2005 standards

- RGMII pins tolerant to 3.6V

- Integrated DSP implements adaptive equalizer, echo cancelers, and crosstalk cancelers

- Efficient digital baseline wander correction

- Power and I/Os

- Various low power modes

- 2.5V I/O supply

- Miscellaneous Features

- IEEE 1149.1 (JTAG) boundary scan

- Multiple clock options 25MHz crystal or 25MHz single-ended clock

- Packaging

- 56-pin QFN (8x8 mm) RoHS compliant package with RGMII

- Environmental

- Commercial temperature range (0°C to +70°C)

- Industrial temperature range (-40°C to +85°C)

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### **Table of Contents**

| 1.0 Introduction                        | 4  |

|-----------------------------------------|----|

| 2.0 Pin Description and Configuration   | 5  |

| 3.0 Functional Description              | 13 |

| 1.0 Register Descriptions               |    |

| 5.0 Operational Characteristics         |    |

| 5.0 Package Outline                     |    |

| Appendix A: Data Sheet Revision History | 78 |

| The Microchip Web Site                  | 80 |

| Customer Change Notification Service    | 80 |

| Customer Support                        | 80 |

| Product Identification System           | 81 |

### 1.0 INTRODUCTION

The LAN8820/LAN8820i is a low-power 10BASE-T/100BASE-TX/1000BASE-T Gigabit Ethernet physical layer (PHY) transceiver that is fully compliant with the IEEE 802.3 and 802.3ab standards.

The LAN8820/LAN8820i can be configured to communicate with an Ethernet MAC via the standard RGMII interface. It contains a full-duplex transceiver for 1000 Mbps operation on four pairs of category 5 or better balanced twisted pair cable. Per IEEE 802.3-2005 standards, all digital interface pins are tolerant to 3.6V.

The LAN8820/LAN8820i is configurable via hardware and software, supporting both IEEE 802.3-2005 compliant and vendor-specific register functions via SMI. The LAN8820/LAN8820i implements Auto-Negotiation to automatically determine the best possible speed and duplex mode of operation. HP Auto-MDIX support allows the use of direct connect or crossover cables.

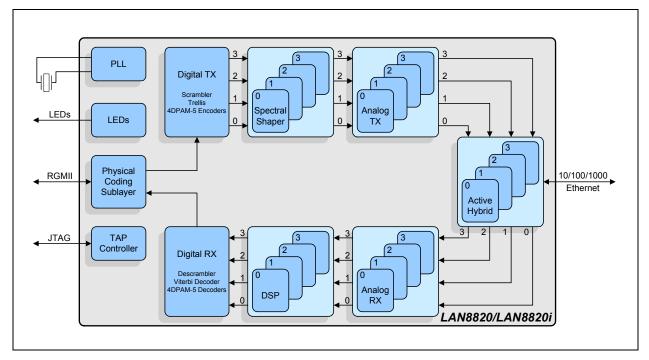

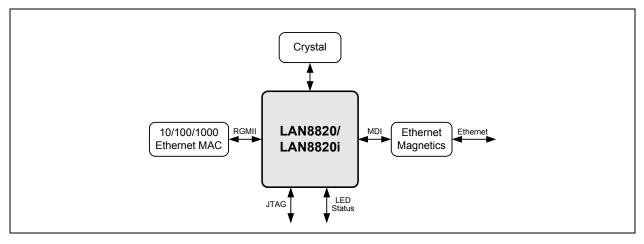

An internal block diagram of the LAN8820/LAN8820i is shown in Figure 1-1. A typical system-level diagram is shown in Figure 1-2.

#### FIGURE 1-1: INTERNAL BLOCK DIAGRAM

FIGURE 1-2: SYSTEM LEVEL BLOCK DIAGRAM

#### 2.0 PIN DESCRIPTION AND CONFIGURATION

#### TABLE 2-1: RGMII INTERFACE PINS

| Num<br>Pins | Name                | Symbols | Buffer<br>Type | Description                                                                                                     |

|-------------|---------------------|---------|----------------|-----------------------------------------------------------------------------------------------------------------|

| 1           | Transmit Data 0     | TXD0    | IS<br>(PD)     | The MAC transmits data to the PHY using this signal.                                                            |

| 1           | Transmit Data 1     | TXD1    | IS<br>(PD)     | The MAC transmits data to the PHY using this signal.                                                            |

| 1           | Transmit Data 2     | TXD2    | IS<br>(PD)     | The MAC transmits data to the PHY using this signal.                                                            |

| 1           | Transmit Data 3     | TXD3    | IS<br>(PD)     | The MAC transmits data to the PHY using this signal.                                                            |

| 1           | Transmit<br>Control | TXCTRL  | IS<br>(PD)     | Indicates both the transmit data enable (TXEN) and transmit error (TXER) functions per the RGMII specification. |

| 1           | Transmit Clock      | TXC     | IS<br>(PD)     | Used to latch data from the MAC into the PHY.<br>1000BASE-T: 125MHz<br>100BASE-TX: 25MHz<br>10BASE-T: 2.5MHz    |

| 1           | Receive Data 0      | RXD0    | O6             | The PHY transfers data to the MAC using this signal.                                                            |

| 1           | Receive Data 1      | RXD1    | O6             | The PHY transfers data to the MAC using this signal.                                                            |

| 1           | Receive Data 2      | RXD2    | O6             | The PHY transfers data to the MAC using this signal.                                                            |

| 1           | Receive Data 3      | RXD3    | O6             | The PHY transfers data to the MAC using this signal.                                                            |

| 1           | Receive Control     | RXCTRL  | O6             | Indicates both the receive data valid (RXDV) and receive error (RXER) functions per the RGMII specification.    |

| 1           | Receive Clock       | RXC     | O6             | Used to transfer data to the MAC.<br>1000BASE-T: 125 MHz<br>100BASE-TX: 25 MHz<br>10BASE-T: 2.5 MHz             |

**Note 2-1** Configuration strap values are latched on hardware reset. Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. Refer to Section 3.8, "Configuration," on page 23 for additional information.

| <b>TABLE 2-2:</b> | SERIAL MANAGEMENT INTERFACE (SMI) PINS |

|-------------------|----------------------------------------|

|-------------------|----------------------------------------|

| Num<br>Pins | Name                      | Symbols | Buffer<br>Type | Description                                    |

|-------------|---------------------------|---------|----------------|------------------------------------------------|

| 1           | SMI Clock                 | MDC     | IS<br>(PD)     | Serial Management Interface clock.             |

| 1           | SMI Data Input/<br>Output | MDIO    | IS/O8<br>(PU)  | Serial Management Interface data input/output. |

#### TABLE 2-3: LED & CONFIGURATION PINS

| Num<br>Pins | Name                                                           | Symbols      | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 10BASE-T Link<br>LED Indicator                                 | 10_LED       | O8             | 10BASE-T LED link indication. Refer to Section 3.9.1, "LEDs," on page 27 for additional information.                                                                                                                                                                                                                                       |

|             | 100BASE-TX<br>Link LED<br>Indicator                            | 100_LED      | O8             | 100BASE-TX LED link indication. Refer to Section 3.9.1, "LEDs," on page 27 for additional information.                                                                                                                                                                                                                                     |

| 1           | Hardware<br>Power Down<br>(HPD) Mode<br>Configuration<br>Strap | HPD_MODE     | IS<br>(PD)     | This configuration strap is used to select the<br>Hardware Power Down (HPD) mode. When pulled-<br>up, the PLL is not disabled when HPD is asserted.<br>When pulled-down, the PLL is disabled when HPD<br>is asserted.                                                                                                                      |

|             |                                                                |              |                | Refer to Section 3.7.3, "Hardware Power-Down," on page 23 for additional information.                                                                                                                                                                                                                                                      |

|             |                                                                |              |                | See Note 2-2 for more information on configuration straps.                                                                                                                                                                                                                                                                                 |

|             | 1000BASE-T<br>Link LED<br>Indicator                            | 1000_LED     | O8             | 1000BASE-T LED link indication. Refer to Section 3.9.1, "LEDs," on page 27 for additional information.                                                                                                                                                                                                                                     |

| 1           | RGMII ID Mode<br>Enable<br>Configuration<br>Strap              | RGMILID MODE | IS<br>(PD)     | This configuration strap is used to configure the RGMII PHY TXC/RXC delay enable bit defaults. When pulled-up, the RGMII PHY TXC/RXC delays are enabled by default. When pulled-down, the RGMII PHY TXC/RXC delays are disabled be default.                                                                                                |

|             |                                                                |              |                | Refer to Section 3.3, "RGMII Interface," on page 18 for more information. See Note 2-2 for more information on configuration straps.                                                                                                                                                                                                       |

| 1           | Configuration<br>Input 0                                       | CONFIG0      | IS<br>(PD)     | This pin sets the PHYADD[1:0] bits of the 10/100<br>Special Modes Register on reset or power-up. It<br>must be connected to VSS, 100_LED, 1000_LED,<br>or VDD25IO. Refer to Section 3.8.1.2,<br>"CONFIG[3:0] Configuration Pins," on page 24 for<br>additional information.                                                                |

| 1           | Configuration<br>Input 1                                       | CONFIG1      | IS<br>(PD)     | This pin sets the PAUSE bit of the Auto Negotiation<br>Advertisement Register and PHYADD [2] bit of the<br>10/100 Special Modes Register on reset or power-<br>up. It must be connected to VSS, 100_LED,<br>1000_LED, or VDD25IO. Refer to Section 3.8.1.2,<br>"CONFIG[3:0] Configuration Pins," on page 24 for<br>additional information. |

| <b>TABLE 2-3:</b> | LED & CONFIGURATION PINS (CONTINUED) |

|-------------------|--------------------------------------|

|-------------------|--------------------------------------|

| Num<br>Pins | Name                     | Symbols | Buffer<br>Type | Description                                                                                                                                                                                                                                                                       |

|-------------|--------------------------|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Configuration<br>Input 2 | CONFIG2 | IS<br>(PD)     | This pin sets the MOD[1:0] bits of the Extended<br>Mode Control/Status Register on reset or power-<br>up. It must be connected to VSS, 100_LED,<br>1000_LED, or VDD25IO. Refer to Section 3.8.1.2,<br>"CONFIG[3:0] Configuration Pins," on page 24 for<br>additional information. |

| 1           | Configuration<br>Input 3 | CONFIG3 | IS<br>(PD)     | This pin sets the MOD[3] bit of the Extended Mode<br>Control/Status Register on reset or power-up. It<br>must be connected to 1000_LED. Refer to Section<br>3.8.1.2, "CONFIG[3:0] Configuration Pins," on<br>page 24 for additional information.                                  |

**Note 2-2** Configuration strap values are latched on hardware reset. Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. Refer to Section 3.8, "Configuration," on page 23 for additional information.

| TABLE 2-4: | ETHERNET PINS |

|------------|---------------|

|            |               |

| Num Pins | Name                                     | Symbol   | Buffer<br>Type | Description                                                                                |

|----------|------------------------------------------|----------|----------------|--------------------------------------------------------------------------------------------|

| 1        | Ethernet TX/<br>RX Positive<br>Channel 0 | TR0P     | AIO            | Transmit/Receive Positive Channel 0.                                                       |

| 1        | Ethernet TX/<br>RX Negative<br>Channel 0 | TRON     | AIO            | Transmit/Receive Negative Channel 0.                                                       |

| 1        | Ethernet TX/<br>RX Positive<br>Channel 1 | TR1P     | AIO            | Transmit/Receive Positive Channel 1.                                                       |

| 1        | Ethernet TX/<br>RX Negative<br>Channel 1 | TR1N     | AIO            | Transmit/Receive Negative Channel 1.                                                       |

| 1        | Ethernet TX/<br>RX Positive<br>Channel 2 | TR2P     | AIO            | Transmit/Receive Positive Channel 2.                                                       |

| 1        | Ethernet TX/<br>RX Negative<br>Channel 2 | TR2N     | AIO            | Transmit/Receive Negative Channel 2.                                                       |

| 1        | Ethernet TX/<br>RX Positive<br>Channel 3 | TR3P     | AIO            | Transmit/Receive Positive Channel 3.                                                       |

| 1        | Ethernet TX/<br>RX Negative<br>Channel 3 | TR3N     | AIO            | Transmit/Receive Negative Channel 3.                                                       |

| 1        | External PHY<br>Bias Resistor            | ETHRBIAS | AI             | Used for the internal bias circuits. Connect to an external 8.06K 1.0% resistor to ground. |

TABLE 2-5: JTAG PINS

| Num Pins | Name                     | Symbol | Buffer<br>Type | Description                                                                                  |

|----------|--------------------------|--------|----------------|----------------------------------------------------------------------------------------------|

| 1        | JTAG Test<br>Data Out    | TDO    | O8             | JTAG (IEEE 1149.1) data output.                                                              |

| 1        | JTAG Test<br>Data Input  | TDI    | IS<br>(PU)     | JTAG (IEEE 1149.1) data input.<br><b>Note:</b> When not used, tie this pin to VDD25IO.       |

| 1        | JTAG Test<br>Clock       | ТСК    | IS<br>(PD)     | JTAG (IEEE 1149.1) test clock.<br><b>Note:</b> When not used, tie this pin to VSS.           |

| 1        | JTAG Test<br>Mode Select | TMS    | IS<br>(PU)     | JTAG (IEEE 1149.1) test mode select.<br><b>Note:</b> When not used, tie this pin to VDD25IO. |

#### TABLE 2-6: MISCELLANEOUS PINS

| Num Pins | Name                   | Symbol | Buffer<br>Type | Description                                                                                                                                                                       |

|----------|------------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Crystal Input          | XI     | ICLK           | External 25 MHz crystal input.<br><b>Note:</b> This pin can also be driven by a 25 MHz                                                                                            |

| 1        |                        |        |                | single-ended clock oscillator. When this<br>method is used, XO should be left<br>unconnected. Refer to Section 5.6,<br>"Clock Circuit," on page 75 for additional<br>information. |

| 1        | Crystal<br>Output      | XO     | OCLK           | External 25 MHz crystal output.                                                                                                                                                   |

| 1        | System Reset           | nRESET | IS<br>(PU)     | This active-low pin allows external hardware to reset the device.                                                                                                                 |

| 1        | Interrupt<br>Request   | IRQ    | O6             | Programmable interrupt request.<br><b>Note:</b> When used, this pin requires an<br>external 4.7K pull-up resistor.                                                                |

| 1        | Hardware<br>Power Down | HPD    | IS<br>(PD)     | When asserted, this pin places the device into<br>Hardware Power Down (HPD) mode. Refer to<br>Section 3.7.3, "Hardware Power-Down," on<br>page 23 for additional information.     |

| 1        | No Connect             | NC     | -              | This pin must be left floating for normal device operation.                                                                                                                       |

| Num Pins | Name                                                                | Symbol    | Buffer<br>Type | Description                                                                                                                                                   |

|----------|---------------------------------------------------------------------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | +2.5V<br>I/O Power<br>Supply Input                                  | VDD25IO   | Ρ              | +2.5V I/O power.<br>Refer to Section 3.10, "Application Diagrams," on<br>page 31 and the LAN8820/LAN8820i reference<br>schematics for connection information. |

| 6        | Digital Core<br>+1.2V Power<br>Supply Input                         | VDD12CORE | Р              | Refer to Section 3.10, "Application Diagrams," on page 31 and the LAN8820/LAN8820i reference schematics for connection information.                           |

| 4        | Ethernet<br>+1.2V Port<br>Power Supply<br>Input For<br>Channels 0-3 | VDD12A    | Ρ              | Refer to Section 3.10, "Application Diagrams," on page 31 and the LAN8820/LAN8820i reference schematics for connection information.                           |

| 1        | Ethernet<br>+1.2V Bias<br>Power Supply<br>Input                     | VDD12BIAS | Р              | Refer to Section 3.10, "Application Diagrams," on page 31 and the LAN8820/LAN8820i reference schematics for connection information.                           |

| 1        | Ethernet PLL<br>+1.2V Power<br>Supply Input                         | VDD12PLL  | Р              | Refer to Section 3.10, "Application Diagrams," on page 31 and the LAN8820/LAN8820i reference schematics for connection information.                           |

| Note 2-3 | Ground                                                              | VSS       | Р              | Common Ground                                                                                                                                                 |

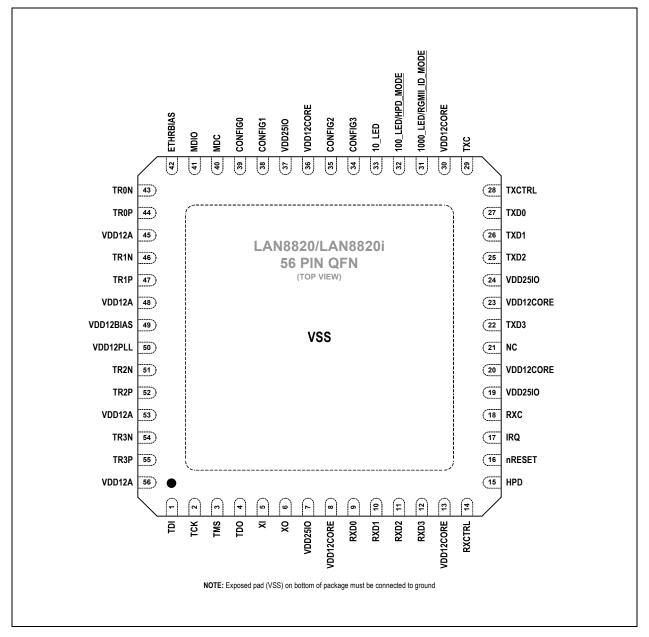

**Note 2-3** Exposed pad on package bottom (Figure 2-1).

| Pin<br>Num | Pin Name                                | Pin<br>Num | Pin Name  | Pin<br>Num | Pin Name                          | Pin<br>Num | Pin Name  |

|------------|-----------------------------------------|------------|-----------|------------|-----------------------------------|------------|-----------|

| 1          | TDI                                     | 15         | HPD       | 29         | TXC                               | 43         | TR0N      |

| 2          | тск                                     | 16         | nRESET    | 30         | VDD12CORE                         | 44         | TR0P      |

| 3          | TMS                                     | 17         | IRQ       | 31         | 1000_LED/<br><u>RGMII_ID_MODE</u> | 45         | VDD12A    |

| 4          | TDO                                     | 18         | RXC       | 32         | 100_LED/<br><u>HPD_MODE</u>       | 46         | TR1N      |

| 5          | XI                                      | 19         | VDD25IO   | 33         | 10_LED                            | 47         | TR1P      |

| 6          | хо                                      | 20         | VDD12CORE | 34         | CONFIG3                           | 48         | VDD12A    |

| 7          | VDD25IO                                 | 21         | NC        | 35         | CONFIG2                           | 49         | VDD12BIAS |

| 8          | VDD12CORE                               | 22         | TXD3      | 36         | VDD12CORE                         | 50         | VDD12PLL  |

| 9          | RXD0                                    | 23         | VDD12CORE | 37         | VDD25IO                           | 51         | TR2N      |

| 10         | RXD1                                    | 24         | VDD25IO   | 38         | CONFIG1                           | 52         | TR2P      |

| 11         | RXD2                                    | 25         | TXD2      | 39         | CONFIG0                           | 53         | VDD12A    |

| 12         | RXD3                                    | 26         | TXD1      | 40         | MDC                               | 54         | TR3N      |

| 13         | VDD12CORE                               | 27         | TXD0      | 41         | MDIO                              | 55         | TR3P      |

| 14         | RXCTRL                                  | 28         | TXCTRL    | 42         | ETHRBIAS                          | 56         | VDD12A    |

|            | EXPOSED PAD<br>MUST BE CONNECTED TO VSS |            |           |            |                                   |            |           |

TABLE 2-8: 56-QFN PIN ASSIGNMENTS

#### 2.1 Buffer Types

#### TABLE 2-9: BUFFER TYPES

| Buffer Type | Description                                                                                                                                                                                                                                          |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IS          | Schmitt-triggered input.                                                                                                                                                                                                                             |  |  |

| O6          | Output with 6 mA sink and 6 mA source.                                                                                                                                                                                                               |  |  |

| O8          | Output with 8 mA sink and 8 mA source.                                                                                                                                                                                                               |  |  |

| PU          | 50uA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                                |  |  |

|             | <b>Note:</b> Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.  |  |  |

| PD          | 50uA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                            |  |  |

|             | <b>Note:</b> Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |  |  |

| AI          | Analog input.                                                                                                                                                                                                                                        |  |  |

| AIO         | Analog bi-directional.                                                                                                                                                                                                                               |  |  |

| ICLK        | Crystal oscillator input pin.                                                                                                                                                                                                                        |  |  |

| OCLK        | Crystal oscillator output pin.                                                                                                                                                                                                                       |  |  |

| Р           | Power pin.                                                                                                                                                                                                                                           |  |  |

**Note 1:** The digital signals are not 5V tolerant. Refer to Section 5.1, "Absolute Maximum Ratings\*," on page 60 for additional buffer information.

#### 3.0 FUNCTIONAL DESCRIPTION

This chapter provides functional descriptions of the various device features. These features have been categorized into the following sections:

- Auto-negotiation

- HP Auto-MDIX

- RGMII Interface

- Serial Management Interface (SMI)

- Interrupt Management

- Resets

- Power-Down modes

- Configuration

- Miscellaneous Functions

- Application Diagrams

#### 3.1 Auto-negotiation

The purpose of the auto-negotiation function is to automatically configure the PHY to the optimum link parameters based on the capabilities of its link partner. Auto-negotiation is a mechanism for exchanging configuration information between two link-partners and automatically selecting the highest performance mode of operation supported by both sides. Autonegotiation is fully defined in clause 28 and clause 40 of the IEEE 802.3 specification.

Once auto-negotiation has completed, information about the resolved link can be passed back to the controller via the integrated Serial Management Interface (SMI). The results of the negotiation process are reflected in the Speed Indication field of the PHY Special Control / Status Register as well as the Auto Negotiation Link Partner Ability Register.

The advertised capabilities of the PHY are stored in Auto Negotiation Advertisement Register. The defaults advertised by the device are determined as described in Section 3.8.1.2.2, "Configuring the Mode of Operation (CONFIG[3:2])," on page 26.

The auto-negotiation protocol is a purely physical layer activity and proceeds independently of the MAC controller. When enabled, auto-negotiation is started by the occurrence of one of the following events:

- Hardware reset

- Software reset

- Power-down reset

- · Link status down

- Setting the Restart Auto-Negotiate bit of the Basic Control Register

On detection of one of these events, the device begins auto-negotiation by transmitting bursts of Fast Link Pulses (FLP). The data transmitted by an FLP burst is known as a "Link Code Word." This exchange of information allows link partners to determine the Highest Common Ability (HCD).

Once a capability match has been determined, the link code words are repeated with the acknowledge bit set. Any difference in the main content of the link code words at this time will cause auto-negotiation to re-start. Auto-negotiation will also re-start if all of the required FLP bursts are not received.

Writing the 100BASE-TX Full Duplex, 100BASE-TX, 10BASE-T Full Duplex, and 10BASE-T bits of the Auto Negotiation Advertisement Register allows software control of the advertised capabilities. However, writing the Auto Negotiation Advertisement Register does not automatically re-start auto-negotiation. The Restart Auto-Negotiate bit of the Basic Control Register must be set before the new abilities will be advertised. Auto-negotiation can also be disabled via software by clearing the Auto-Negotiation Enable bit of the Basic Control Register.

Auto-Negotiation also resolves the Master/Slave clocking relationship between two PHYs for a 1000BASE-T link. Refer to Section 3.1.4, "Master/Slave," on page 14 for additional information.

#### 3.1.1 RESTARTING AUTO-NEGOTIATION

Auto-negotiation can be restarted at any time by using the Restart Auto-Negotiate bit of the Basic Control Register. Auto-negotiation will also re-start if the link is broken at any time. A broken link is caused by signal loss. This may occur because of a cable break, or because of an interruption in the signal transmitted by the Link Partner. Auto-negotiation resumes in an attempt to determine the new link configuration.

## LAN8820/LAN8820I

If the management entity restarts Auto-negotiation by writing to the Restart Auto-Negotiate bit, the device will respond by stopping all transmission/receiving operations. Auto-negotiation will restart after approximately 1200 mS. The Link Partner will have also dropped the link and will resume auto-negotiation.

#### 3.1.2 DISABLING AUTO-NEGOTIATION

Auto-negotiation can be disabled via software by clearing the Auto-Negotiation Enable bit of the Basic Control Register. The device will then force its speed of operation to reflect the information in the Speed Select[1], Speed Select[0], and Duplex Mode bits of the Basic Control Register. These bits are ignored when auto-negotiation is enabled.

#### 3.1.3 PARALLEL DETECTION

If the LAN8820/LAN8820i is connected to a device lacking the ability to auto-negotiate (for example, no FLPs are detected), it is able to determine the speed of the link based on either 100M MLT-3 symbols or 10M Normal Link Pulses. In this case, the link is presumed to be half-duplex per the IEEE standard. This ability is known as "Parallel Detection". This feature ensures inter operability with legacy link partners.

The Ethernet MAC has access to information regarding parallel detect via the Auto Negotiation Expansion Register. If a link is formed via parallel detection, the Link Partner Auto-Negotiation Able bit of the Auto Negotiation Expansion Register is cleared to indicate that the Link Partner is not capable of auto-negotiation. If a fault occurs during parallel detection, the Parallel Detection Fault bit of this register is set.

The Auto Negotiation Link Partner Ability Register is updated with information from the link partner which is coded in the received FLPs. If the Link Partner is not auto-negotiation capable, then the Auto Negotiation Link Partner Ability Register is updated after completion of parallel detection to reflect the speed capability of the Link Partner.

Parallel detect cannot be used to establish Gigabit Ethernet links because echo cancellation and signal recovery on a Gigabit Ethernet link requires resolution of the Master/Slave clock relationship, which requires the exchange of FLPs.

#### 3.1.4 MASTER/SLAVE

In 1000BASE-T, one of the two link partner devices must be configured as Master and the other as Slave. The Master device transmits data using the local clock, while the Slave device uses the clock recovered from incoming data.

The Master and Slave assignments are set using the configuration pins as described in Section 3.8.1.2.2, "Configuring the Mode of Operation (CONFIG[3:2])," on page 26 or by using the Master/Slave Manual Config Enable and Master/Slave Manual Config Value bits of the Master/Slave Control Register. If both the link partner and the local device are manually given the same Master/Slave assignment, an error will be indicated in the Master/Slave Configuration Fault bit of the Master/Slave Status Register.

Depending on the link partner configuration, the manual Master/Slave mode can be resolved to sixteen possible outcomes, as shown in Table 3-1.

| LAN8820/LAN8820i<br>Advertisement | Link Partner<br>Advertisement | LAN8820/LAN8820i Result     | Link Partner Result         |

|-----------------------------------|-------------------------------|-----------------------------|-----------------------------|

| Single-Port                       | Single-Port                   | M/S resolved by random seed | M/S resolved by random seed |

| Single-Port                       | Multi-Port                    | Slave                       | Master                      |

| Single-Port                       | Manual Master                 | Slave                       | Master                      |

| Single-Port                       | Manual Slave                  | Master                      | Slave                       |

| Multi-Port                        | Single-Port                   | Master                      | Slave                       |

| Multi-Port                        | Multi-Port                    | M/S resolved by random seed | M/S resolved by random seed |

| Multi-Port                        | Manual Master                 | Slave                       | Master                      |

| Multi-Port                        | Manual Slave                  | Master                      | Slave                       |

| Manual Master                     | Single-Port                   | Master                      | Slave                       |

#### TABLE 3-1: MASTER/SLAVE RESOLUTION FOR 1000BASE-T

| LAN8820/LAN8820i<br>Advertisement | Link Partner<br>Advertisement | LAN8820/LAN8820i Result | Link Partner Result |

|-----------------------------------|-------------------------------|-------------------------|---------------------|

| Manual Master                     | Multi-Port                    | Master                  | Slave               |

| Manual Master                     | Manual Master                 | No Link                 | No Link             |

| Manual Master                     | Manual Slave                  | Master                  | Slave               |

| Manual Slave                      | Single-Port                   | Slave                   | Master              |

| Manual Slave                      | Multi-Port                    | Slave                   | Master              |

| Manual Slave                      | Manual Master                 | Slave                   | Master              |

| Manual Slave                      | Manual Slave                  | No Link                 | No Link             |

#### TABLE 3-1: MASTER/SLAVE RESOLUTION FOR 1000BASE-T (CONTINUED)

#### 3.1.5 MANUAL OPERATION

The device supports a manual (forced) operation for test purposes. In manual operation, the user sets the link speed (10Mbps or 100Mbps) and the duplex state (full or half).

Auto-negotiation must be disabled in order to manually configure the speed and the duplex. This may be accomplished using the configuration pins, as described in Section 3.8.1.2.2, "Configuring the Mode of Operation (CONFIG[3:2])," on page 26, or by using the Basic Control Register as described in Section 3.1.2, "Disabling Auto-negotiation," on page 14. For 10BASE-T and 100BASE-TX, the link state of the device is determined by the Speed Select[1], Speed Select[0], and Duplex Mode bits of the Basic Control Register. Manual operation at a link speed of 1000Mbps is not supported.

#### 3.1.6 HALF VS. FULL-DUPLEX

Half-duplex operation relies on the CSMA/CD (Carrier Sense Multiple Access / Collision Detect) protocol to handle network traffic and collisions. In this mode, the internal carrier sense signal, CRS, responds to both transmit and receive activity. If data is received while the PHY is transmitting, a collision results.

In full-duplex mode, the PHY is able to transmit and receive data simultaneously and collision detection is disabled. In this mode, the internal CRS responds only to receive activity. In 10BASE-T and 100BASE-T mode, CRS is redefined to respond only to received activity. In 1000BASE-T, CRS is disabled.

Table 3-2 describes the behavior of the internal CRS bit under all receive/transmit conditions.

| Mode             | Speed    | Duplex      | Activity     | CRS Behavior<br>(Note 3-1) |

|------------------|----------|-------------|--------------|----------------------------|

| Manual           | 10 Mbps  | Half-Duplex | Transmitting | Active                     |

| Manual           | 10 Mbps  | Half-Duplex | Receiving    | Active                     |

| Manual           | 10 Mbps  | Full-Duplex | Transmitting | Low                        |

| Manual           | 10 Mbps  | Full-Duplex | Receiving    | Active                     |

| Manual           | 100 Mbps | Half-Duplex | Transmitting | Active                     |

| Manual           | 100 Mbps | Half-Duplex | Receiving    | Active                     |

| Manual           | 100 Mbps | Full-Duplex | Transmitting | Low                        |

| Manual           | 100 Mbps | Full-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 10 Mbps  | Half-Duplex | Transmitting | Active                     |

#### TABLE 3-2: CRS BEHAVIOR

© 2009-2016 Microchip Technology Inc.

| Mode             | Speed    | Duplex      | Activity     | CRS Behavior<br>(Note 3-1) |

|------------------|----------|-------------|--------------|----------------------------|

| Auto-Negotiation | 10 Mbps  | Half-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 10 Mbps  | Full-Duplex | Transmitting | Low                        |

| Auto-Negotiation | 10 Mbps  | Full-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 100 Mbps | Half-Duplex | Transmitting | Active                     |

| Auto-Negotiation | 100 Mbps | Half-Duplex | Receiving    | Active                     |

| Auto-Negotiation | 100 Mbps | Full-Duplex | Transmitting | Low                        |

| Auto-Negotiation | 100 Mbps | Full-Duplex | Receiving    | Active                     |

#### TABLE 3-2: CRS BEHAVIOR (CONTINUED)

**Note 3-1** The internal CRS signal operates in two modes: Active and Low. When in Active mode, the internal CRS will transition high and low upon line activity, where a high value indicates a carrier has been detected. In Low mode, the internal CRS stays low and does not indicate carrier detection.

#### 3.2 HP Auto-MDIX

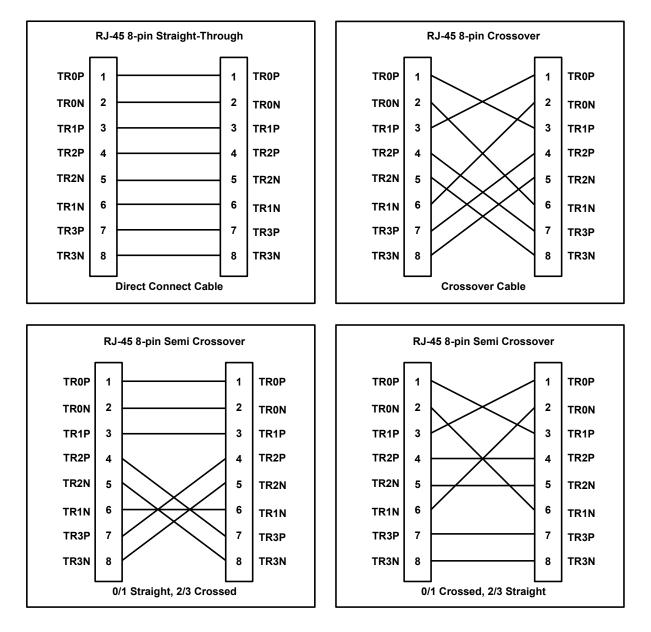

HP Auto-MDIX facilitates the use of CAT-5 (100BASE-T) media UTP interconnect cable without consideration of interface wiring scheme. If a user plugs in either a direct connect LAN cable, or a crossover patch cable, as shown in Figure 3-1, the Auto-MDIX PHY is capable of configuring the twisted pair pins for correct transceiver operation.

The internal logic of the device detects the TX and RX pins of the connecting device. It can automatically re-assign channel 0 and 1 if required to establish a link. In 1000BASE-T mode, it can re-assign channel 2 and 3. Crossover resolution precedes the actual auto-negotiation process that involves exchange of FLPs to advertise capabilities. Automatic MDI/ MDIX is described in IEEE 802.3ab Clause 40, section 40.8.2. Since the RX and TX line pairs are interchangeable, special PCB design considerations are needed to accommodate the symmetrical magnetics and termination of an Auto-MDIX design.

Auto-MDIX is enabled by default, and can be disabled by the Auto MDIX Disable bit in the 10/100 Mode Control/Status Register. When Auto-MDIX is disabled, the TX and RX pins can be configured manually by the MDI/MDI-X 0:1 and MDI/MDI-X 2:3 bits in the Extended Mode Control/Status Register.

The device includes an advanced crossover resolution capability called Semi Crossover. This is an extension to HP Auto-MDIX that corrects for a cable with only two pairs crossed. If Semi Crossover is enabled, after the device has attempted to establish a link with all four signal pairs normal or crossed, it will attempt to establish a link with pairs 2/3 switched and 0/1 straight, and then with pairs 0/1 switched and pairs 2/3 straight. The Semi Crossover is enabled by default, and can be disabled by the Semi Crossover Enable bit in the 10/100 Mode Control/Status Register.

After resolution of crossed pairs is complete, using either HP Auto-MDIX or the Semi Crossover function, the MDI/MDI-X status is reported through the XOVER Resolution 0:1 and XOVER Resolution 2:3 bits of the User Status 2 Register.

### FIGURE 3-1: CABLE CONNECTION TYPES: STRAIGHT-THROUGH, CROSSOVER, SEMI CROSSOVER

#### 3.2.1 REQUIRED ETHERNET MAGNETICS

The magnetics selected for use with the device should be an Auto-MDIX style magnetic available from several vendors. Refer to Application Note 8.13 "Suggested Magnetics" for the latest qualified and suggested magnetics. Vendors and part numbers are provided in this application note.

#### 3.3 RGMII Interface

The device communicates with an external MAC using the Reduced Gigabit Media Independent Interface (RGMII). The RGMII is compliant with the RGMII standard, and provides support for 1000BASE-T, 100BASE-TX, or 10BASE-T operation.

The RGMII consists of the RXC, RXD[3:0], RXCTRL, TXC, TXD[3:0] and TXCTRL signals. All transmission related signals, TXC, TXD[3:0] and TXCTRL, are generated by the MAC. The TXC transmit clock is used to synchronize the TXD[3:0] data and TXCTRL control signals. All reception related signals, RXC, RXD[3:0] and RXCTRL, are generated by the device. The RXC receive clock is used to synchronic the RXD[3:0] data and RXCTRL control signals.

The RGMII interface supports both Version 1.3 and Version 2.0 of the RGMII specification. Version 1.3 of the RGMII Specification requires a 1.5 to 2ns clock delay via a PCB trace delay. Version 2.0 of the RGMII Specification introduces the option of an on-chip Internal Delay (ID). These distinct RGMII modes of operation are referred to as "Non-ID Mode" and "ID Mode", respectively, throughout the document. Refer to the RGMII specification for additional details.

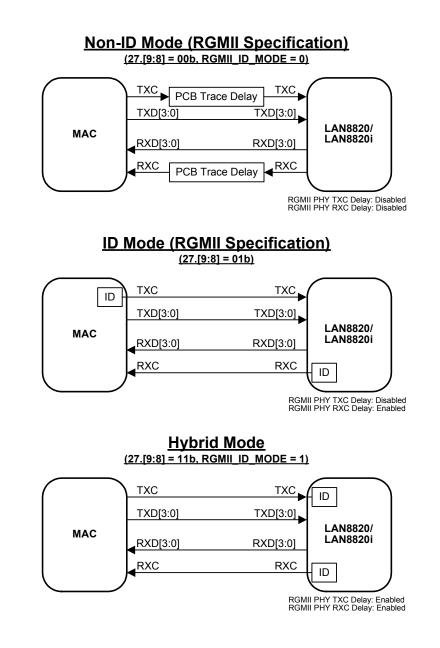

In addition to the standard Non-ID and ID modes of operation, the device supports a hybrid mode of operation, for a total of 3 RGMII modes. These modes are summarized below:

**Non-ID Mode** - Per the RGMII specification, no internal delay is generated at the MAC or the device(PHY). External PCB trace delays are required to meet RGMII timing requirements.

**ID Mode** - Per the RGMII specification, an internal delay is generated on TXC at the MAC, and an ID is generated on RXC at the device(PHY). No PCB trace delay is required.

Hybrid Mode - In this mode, the device(PHY) will generate an ID on both TXC and RXC. This mode may be used to eliminate the PCB trace delay requirement when utilizing a non-ID MAC.

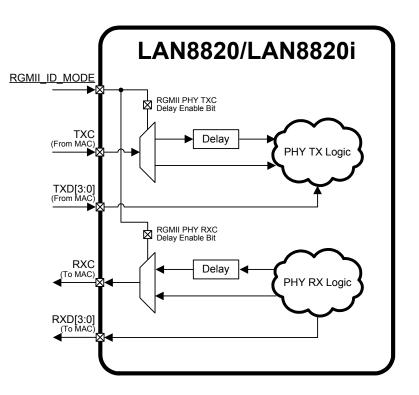

The RGMII mode is configured via the RGMII PHY TXC Delay Enable and RGMII PHY RXC Delay Enable bits of the Control / Status Indications Register (29.[9:8]). The default values of these bits are configured via the <u>RGMII\_ID\_MODE</u> configuration strap. Figure 3-2 details the RGMII mode configuration logic. For additional information on the <u>RGMII\_ID\_MODE</u> <u>MODE</u> configuration strap, refer to Section 3.8.1.1, "Configuration Straps," on page 24.

#### FIGURE 3-2: RGMII MODE CONFIGURATION LOGIC

The various RGMII modes and their corresponding configuration settings are summarized in Figure 3-3.

#### FIGURE 3-3: RGMII MODES OF OPERATION

**Note:** Strapping <u>RGMII\_ID\_MODE</u> high sets the device into Hybrid Mode. In order to set the device into ID Mode, the RGMII PHY TXC Delay Enable and RGMII PHY RXC Delay Enable bits of the Control / Status Indications Register (27.[9:8]) must be configured via software to 01b.

Timing information for the RGMII interface is provided in Section 5.5, "AC Specifications," on page 65. For additional information on the RGMII interface, refer to the RGMII specification.

#### 3.3.1 MII ISOLATE MODE

The device may be configured to electrically isolate the RGMII pins by setting the Isolate bit of the Basic Control Register. In this mode, all MAC data interface output pins are HIGH and all MAC data interface input pins are ignored. In this mode, the SMI interface is kept active, allowing the MAC to access the SMI registers and generate interrupts. All MDI operations are halted while in isolate mode.

#### 3.4 Serial Management Interface (SMI)

The Serial Management Interface is used to control the device and obtain its status. This interface supports the standard PHY registers required by Clause 22 of the 802.3 standard, as well as "vendor-specific" registers allowed by the specification. Non-supported registers (such as 11 to 14) will be read as hexadecimal "FFFF". Device registers are detailed in Section 4.0, "Register Descriptions," on page 34.

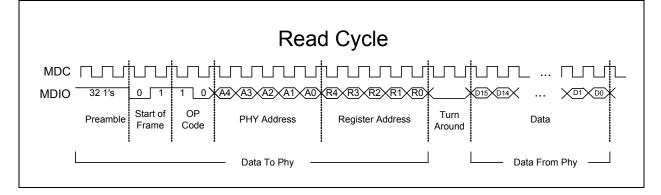

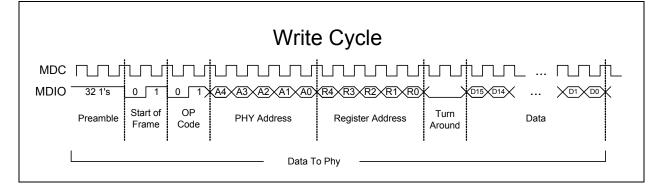

At the system level, SMI provides 2 signals: MDIO and MDC. The MDC signal is an aperiodic clock provided by the station management controller (SMC). MDIO is a bi-directional data SMI input/output signal that receives serial data (commands) from the controller SMC and sends serial data (status) to the SMC. The minimum time between edges of the MDC is 160 ns. There is no maximum time between edges. The minimum cycle time (time between two consecutive rising or two consecutive falling edges) is 400 ns. These modest timing requirements allow this interface to be easily driven by the I/O port of a microcontroller.

The data on the MDIO line is latched on the rising edge of the MDC. The frame structure and timing of the data is shown in Figure 1-1 and Figure 1-2. The timing relationships of the MDIO signals are further described in Section 5.5.6, "SMI Timing," on page 73.

#### FIGURE 3-4: MDIO TIMING AND FRAME STRUCTURE - READ CYCLE

#### FIGURE 3-5: MDIO TIMING AND FRAME STRUCTURE - WRITE CYCLE

#### 3.5 Interrupt Management

The device supports multiple interrupt capabilities which are not a part of the IEEE 802.3 specification. An active low asynchronous interrupt signal may be generated on the IRQ pin when selected events are detected, as configured by the Interrupt Mask Register.

To set an interrupt, the corresponding mask bit in the Interrupt Mask Register must be set (see Table 3-3). When the associated event occurs, the IRQ pin will be asserted. When the corresponding event to deassert IRQ is true, the IRQ pin will be deasserted. All interrupts are masked following a reset.

**Note:** Table 3-3 utilizes register index and bit number referencing in lieu of individual names. For example, "30.10" is used to reference bit 10 (transmitter elastic buffer overflow interrupt enable) of the Interrupt Mask Register (register index 30).

| Mask     | Interrupt Source Flag |                                         | Interrupt Source Flag Interrupt Source |                             | Event to Assert<br>IRQ                  | Event to Deassert<br>IRQ                                                                                  |

|----------|-----------------------|-----------------------------------------|----------------------------------------|-----------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 30.15:11 | 29.15:11              | RESERVED                                | -NA-                                   | -NA-                        | -NA-                                    | -NA-                                                                                                      |

| 30.10    | 29.10                 | Transmitter Elastic<br>Buffer Overflow  | -NA-                                   | -NA-<br>(Note 3-3)          | Transmitter Elastic<br>Buffer Overflow  | Overflow condition resolved                                                                               |

| 30.9     | 29.9                  | Transmitter Elastic<br>Buffer Underflow | -NA-                                   | -NA-<br>(Note 3-3)          | Transmitter Elastic<br>Buffer Underflow | Underflow condition resolved                                                                              |

| 30.8     | 29.8                  | Idle Error Count<br>Overflow            | 10.7:0                                 | Idle Error Count            | Idle Error Count<br>Overflow            | Reading register 10                                                                                       |

| 30.7     | 29.7                  | ENERGYON                                | 17.1                                   | ENERGYON                    | Rising 17.1<br>(Note 3-2)               | Falling 17.1 or<br>Reading register 29                                                                    |

| 30.6     | 29.6                  | Auto-Negotiation complete               | 1.5                                    | Auto-Negotiate<br>Complete  | Rising 1.5                              | Falling 1.5 or<br>Reading register 29                                                                     |

| 30.5     | 29.5                  | Remote Fault<br>Detected                | 1.4                                    | Remote Fault                | Rising 1.4                              | Falling 1.4, or<br>Reading register 1 or<br>Reading register 29                                           |

| 30.4     | 29.4                  | Link Down                               | 1.2                                    | Link Status                 | Falling 1.2                             | Reading register 1 or<br>Reading register 29                                                              |

| 30.3     | 29.3                  | RESERVED                                | -NA-                                   | -NA-                        | -NA-                                    | -NA-                                                                                                      |

| 30.2     | 29.2                  | Parallel Detection<br>Fault             | 6.4                                    | Parallel<br>Detection Fault | Rising 6.4                              | Falling 6.4 or<br>Reading register 6, or<br>Reading register 29 or<br>Re-AutoNegotiate or<br>Link down    |

| 30.1     | 29.1                  | Auto-Negotiation<br>Page Received       | 6.1                                    | Page Received               | Rising 6.1                              | Falling of 6.1 or<br>Reading register 6, or<br>Reading register 29<br>Re-auto-negotiate, or<br>Link Down. |

#### TABLE 3-3: INTERRUPT MANAGEMENT TABLE

Note 3-2 The ENERGYON bit of the 10/100 Mode Control/Status Register (17.1) defaults to "1" after a hardware reset. If no energy is detected before 256mS, the ENERGYON bit will be cleared. When ENERGYON is "0" and energy is detected, due to the establishment of a valid link or the PHY auto-negotiation moving past the ability detect state, the ENERGYON bit will be set and the INT7 bit of the Interrupt Source Flags Register will assert. If ENERGYON is set and the energy is removed, the INT7 bit will assert. The ENERGYON bit will clear 256mS after the interrupt. If the PHY is in manual mode, INT7 will be asserted 256mS after the link is broken. If the PHY is auto-negotiating, INT7 will be asserted 256mS after the PHY returns to the ability detect state (maximum of 1.5S after the link

is broken). To prevent an unexpected assertion of IRQ, the ENERGYON interrupt mask (INT7\_EN) should always be cleared as part of the ENERGYON interrupt service routine.

**Note 3-3** The transmitter FIFO depth can be adjusted via the Transmitter FIFO Depth field of the Extended Mode Control/Status Register (19.10:9).

#### 3.6 Resets

The device provides the following chip-level reset sources:

- Hardware Reset (nRESET)

- Software Reset

- Power-Down Reset

- 3.6.1 HARDWARE RESET (NRESET)

**Note:** System implementers should connect the nRESET input pin to an output pin from the respective MAC or microcontroller, so that the required power-up sequence can be performed without causing a full system reset event.

A hardware reset will occur when the system reset nRESET input pin is driven low. Anytime nRESET is asserted, it must be held low for the minimum time specified in Section 5.5.4, "Reset Timing," on page 68 to ensure proper reset to the PHY. Following a hardware reset, the device resets the device registers and relatches the configuration straps and CON-FIG[3:0] pins.

On first power-up of the device, the sequence below must be also be followed to ensure the device exits reset in the correct operational state:

- 1. Perform a hardware reset on power-up as per Section 5.5.3, "Power-On Hardware Reset Timing," on page 67.

- 2. Wait a minimum of 250mS

- 3. Write SMI Register 0 (Basic Control Register) = 0x4040

- 4. Wait a minimum of 1 second

- 5. Assert the nRESET input pin (nRESET = 0)

- 6. Wait a minimum of 50mS

- 7. Deassert the nRESET input pin (nRESET = 1)

After completing this sequence, the LAN8820/LAN8820i will be in the default states and ready for any initialization or configuration and allow operation.

**Note:** A hardware reset (nRESET assertion) is required following power-up. Refer to Section 5.5.3, "Power-On Hardware Reset Timing," on page 67 for additional information.

#### 3.6.2 SOFTWARE RESET

A software reset is initiated by writing a '1' to the PHY Soft Reset (RESET) bit of the Basic Control Register. This selfclearing bit will return to '0' after approximately 256µs, at which time the PHY reset is complete. This reset initializes the logic within the PHY, with the exception of register bits marked as "NASR" (Not Affected by Software Reset).

Following a software reset, the device configuration is reloaded from the register bit values, and not from the configuration straps and CONFIG[3:0] pins. The device does not relatch the hardware configuration settings. For example, if the device is powered up and a configuration strap is changed from its initial power up state, a software reset will not load the new strap setting.

#### 3.6.3 POWER-DOWN RESET

A power-down reset is automatically activated when the device comes out of the power-down mode. During powerdown, the registers are not reset. Configuration straps and CONFIG[3:0] pins are not latched as a result of a powerdown reset. The power-down reset is internally extended by 256  $\mu$ s after exiting the power-down mode to allow the PLLs to stabilize before the logic is released from reset. Refer to Section 3.7, "Power-Down modes," on page 23 for details on the various power-down modes.

#### 3.7 Power-Down modes

The device supports 3 power-down modes:

- General Power-Down

- Energy Detect Power-Down

- Hardware Power-Down

#### 3.7.1 GENERAL POWER-DOWN

This power-down mode is controlled by the Power Down bit of the Basic Control Register. In this mode, the entire device is powered-down except for the serial management interface. The device remains in the general power-down mode while Power Down is set. When Power Down is cleared, the device powers up and is automatically reset (via a Power-Down Reset). For maximum power savings, auto-negotiation should be disabled before enabling the general power-down mode.

#### 3.7.2 ENERGY DETECT POWER-DOWN

This power-down mode is controlled by the EDPWRDOWN bit of the 10/100 Mode Control/Status Register. In this mode, when no energy is present on the line, nothing is transmitted and the device is powered-down except for the management interface, the SQUELCH circuit and the ENERGYON logic.

The ENERGYON bit in the 10/100 Mode Control/Status Register is asserted when there is valid energy from the line (100BASE-TX, 10BASE-T, or Auto-Negotiation signals) and the PHY powers-up. It automatically resets itself into the previous state prior to power-down, and stays in active mode as long as energy exists on the line. If the ENGERGYON interrupt is enabled (INT7\_EN of the Interrupt Mask Register), IRQ is asserted.

#### Note: The first and possibly second packet to activate ENERGYON may be lost.

#### 3.7.3 HARDWARE POWER-DOWN

This power-down mode is controlled by the HPD pin. In this mode, the entire device is powered-down except for the serial management interface. The <u>HPD\_MODE</u> configuration strap selects whether the PLL will be shut down when in hardware power-down mode. To exit the hardware power-down mode, the HPD pin must be deasserted, followed by the deassertion of the Power Down bit in the Basic Control Register. If the hardware power-down mode is set to shut down the PLL, a software reset must also be issued.

- Note 1: The device will wake-up in the hardware power-down mode if the HPD pin is asserted during hardware reset.

- 2: For additional information on the <u>HPD\_MODE</u> configuration strap, refer to Section 3.8.1.1, "Configuration Straps," on page 24.

#### 3.8 Configuration

The device mode of operation may be controlled by hardware and software (register-selectable) configuration options. The initial configuration may be selected in hardware as described in Section 3.8.1. In addition, register-selectable software configuration options may be used to further define the functionality of the transceiver as described in Section 3.8.2. The device supports both IEEE 802.3-2005 compliant and vendor-specific register functions.

#### 3.8.1 HARDWARE CONFIGURATION

Hardware configuration is controlled via multiple configuration straps and the CONFIG[3:0] configuration pins. These items are detailed in the following sub-sections.

#### 3.8.1.1 Configuration Straps

Configuration straps are multi-function pins that are driven as outputs during normal operation. During a Hardware Reset (nRESET), these outputs are tri-stated. The high or low state of the signal is latched following de-assertion of the reset and is used to determine the default configuration of a particular feature. Table 3-4 details the configuration straps. Configuration straps are also listed as part of Section 2.0, "Pin Description and Configuration," on page 5 with underlined names.

Configuration straps include internal resistors in order to prevent the signal from floating when unconnected. If a particular configuration strap is connected to a load, an external pull-up or pull-down should be used to augment the internal resistor to ensure that it reaches the required voltage level prior to latching. The internal resistor can also be overridden by the addition of an external resistor.

- **Note 1:** The system designer must guarantee that configuration straps meet the timing requirements specified in Section 5.5.3, "Power-On Hardware Reset Timing," on page 67. If configuration straps are not at the correct voltage level prior to being latched, the device may capture incorrect strap values.

- 2: Configuration straps must never be driven as inputs. If required, configuration straps can be augmented, or overridden with external resistors.

| Configuration<br>Strap | Description                                                                                                       | Logic 0<br>(PD)                 | Logic 1<br>(PU)         |

|------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------|

| HPD_MODE               | Selects the hardware power-down (HPD) mode                                                                        | HPD with PLL disabled (Default) | HPD with PLL<br>enabled |

| RGMII_ID_MODE          | Configures the RGMII PHY TXC/RXC delay<br>enable bits of the Control / Status Indications<br>Register (27.[9:8]). | 27.[9:8] = 00b<br>(Default)     | 27.[9:8] = 11b          |

|                        | Refer to Section 3.3, "RGMII Interface," on page 18 for additional information.                                   |                                 |                         |

#### TABLE 3-4: CONFIGURATION STRAPS

#### 3.8.1.2 CONFIG[3:0] Configuration Pins

The device provides 4 dedicated configuration pins, CONFIG[3:0], which are used to select the default SMI address and mode of operation. The CONFIG[3:0] configuration pins differ from configuration straps in that they are single-purpose pins and have different latch timing requirements. The high or low states of the CONFIG[3:0] pins are latched following deassertion of a Hardware Reset (nRESET). Refer to Section 5.5.3, "Power-On Hardware Reset Timing," on page 67 for additional CONFIG[3:0] timing information.

Each CONFIG[3:0] configuration pin can be connected in one of four ways. The Configuration Pin Value (CPV) represented by each connection option is shown in Table 3-5.

| CONFIGURATION PIR |  |  |  |

|-------------------|--|--|--|

| Value             |  |  |  |

| CPV(0)            |  |  |  |

| CPV(1)            |  |  |  |

| CPV(2)            |  |  |  |

| CPV(3)            |  |  |  |

|                   |  |  |  |

### TABLE 3-5:HARDWARE CONNECTION DETERMINES<br/>CONFIGURATION PIN VALUE (CPV)

Using the CPV nomenclature for each CONFIG[3:0] pin, Section 3.8.1.2.1 describes how to configure the SMI address and Section 3.8.1.2.2 describes how to configure the initial mode of operation.

**Note:** The HPD pin is also a dedicated configuration pin. HPD forces the entire device to power down except for the management interface. The Hardware Power-Down mode is described in Section 3.7.3, "Hardware Power-Down," on page 23.

#### 3.8.1.2.1 Configuring the SMI Address (CONFIG[1:0])

The SMI address may be configured via hardware to any value between 0 and 7. If an address greater than 7 is required, the user can configure the PHY address using Software Configuration via the PHYADD[4:0] field of the 10/100 Special Modes Register (after SMI communication at an address is established).

The CONFIG1 pin is used to configure both the SMI address and the value of the Pause Operation (PAUSE) bit in the Auto Negotiation Advertisement Register. The user must first determine the desired PAUSE value. The configuration pin values for CONFIG1 and CONFIG0 should then be selected using Table 3-6 (PAUSE=0) or Table 3-7 (PAUSE=1), respectively.

#### TABLE 3-6:SMI ADDRESS CONFIGURATION WITH PAUSE=0

| PHYADD[2:0] | CONFIG1 | CONFIG0 |

|-------------|---------|---------|

| 000         | CPV(0)  | CPV(0)  |

| 001         | CPV(0)  | CPV(1)  |

| 010         | CPV(0)  | CPV(2)  |

| 011         | CPV(0)  | CPV(3)  |

| 100         | CPV(1)  | CPV(0)  |

| 101         | CPV(1)  | CPV(1)  |

| 110         | CPV(1)  | CPV(2)  |

| 111         | CPV(1)  | CPV(3)  |

#### TABLE 3-7: SMI ADDRESS CONFIGURATION WITH PAUSE=1

| PHYADD[2:0] | CONFIG1 | CONFIG0 |

|-------------|---------|---------|

| 000         | CPV(2)  | CPV(0)  |

| 001         | CPV(2)  | CPV(1)  |

| 010         | CPV(2)  | CPV(2)  |

| 011         | CPV(2)  | CPV(3)  |

| 100         | CPV(3)  | CPV(0)  |

| 101         | CPV(3)  | CPV(1)  |

| 110         | CPV(3)  | CPV(2)  |

| 111         | CPV(3)  | CPV(3)  |

© 2009-2016 Microchip Technology Inc.