Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High Performance Two Port 10/100 Managed Ethernet Switch with 32-Bit Non-PCI CPU Interface

# **Highlights**

- High performance and full featured 2 port switch with VLAN, QoS packet prioritization, Rate Limiting, IGMP monitoring and management functions

- · Easily interfaces to most 32-bit embedded CPU's

- Unique Virtual PHY feature simplifies software development by mimicking the multiple switch ports as a single port MAC/PHY

- Integrated IEEE 1588 Hardware Time Stamp Unit

# **Target Applications**

- · Cable, satellite, and IP set-top boxes

- · Digital televisions

- · Digital video recorders

- · VoIP/Video phone systems

- · Home gateways

- Test/Measurement equipment

- · Industrial automation systems

# **Key Benefits**

- · Ethernet Switch Fabric

- 32K buffer RAM

- 1K entry forwarding table

- Port based IEEE 802.1Q VLAN support (16 groups)

- Programmable IEEE 802.1Q tag insertion/removal

- IEEE 802.1d spanning tree protocol support

- QoS/CoS Packet prioritization

- 4 dynamic QoS queues per port

- Input priority determined by VLAN tag, DA lookup, TOS, DIFFSERV or port default value

- Programmable class of service map based on input priority

- Remapping of 802.1Q priority field on per port basis

- Programmable rate limiting at the ingress/egress ports with random early discard, per port / priority

- IGMP v1/v2/v3 monitoring for Multicast packet filtering

- Programmable filter by MAC address

- · Switch Management

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic on any ports or port pairs

- Fully compliant statistics (MIB) gathering counters

- Control registers configurable on-the-fly

- Ports

- 2 internal 10/100 PHYs with HP Auto-MDIX support

- Fully compliant with IEEE 802.3 standards

- 10BASE-T and 100BASE-TX support

- Full and half duplex support

- Full duplex flow control

- Backpressure (forced collision) half duplex flow control

- Automatic flow control based on programmable levels

- Automatic 32-bit CRC generation and checking

- Automatic payload padding

- 2K Jumbo packet support

- Programmable interframe gap, flow control pause value

- Full transmit/receive statistics

- Auto-negotiation

- Automatic MDI/MDI-X

- Loop-back mode

- · High-performance host bus interface

- Provides in-band network communication path

- Access to management registers

- Simple, SRAM-like interface

- 32-bit data bus

- Big, little, and mixed endian support

- Large TX and RX FIFO's for high latency applications

- Programmable water marks and threshold levels

- Host interrupt support

- · IEEE 1588 Hardware Time Stamp Unit

- Global 64-bit tunable clock

- Master or slave mode per port

- Time stamp on TX or RX of Sync and Delay\_req packets per port, Timestamp on GPIO

- 64-bit timer comparator event generation (GPIO or IRQ)

- · Comprehensive Power Management Features

- Wake on LAN

- Wake on link status change (energy detect)

- Magic packet wakeup

- Wakeup indicator event signal

- · Other Features

- General Purpose Timer

- Serial EEPROM interface (I<sup>2</sup>C master or Microwire<sup>™</sup> master) for non-managed configuration

- Programmable GPIOs/LEDs

- Single 3.3V power supply

- · Available in Commercial Temp. Range

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| 1.0 Preface                                     | 4   |

|-------------------------------------------------|-----|

| 1.0 Preface                                     | 7   |

| 3.0 Pin Description and Configuration           | 13  |

| 4.0 Clocking, Resets, and Power Management      |     |

| 5.0 System Interrupts                           |     |

| 6.0 Switch Fabric                               |     |

| 7.0 Ethernet PHYs                               | 62  |

| 8.0 Host Bus Interface (HBI)                    | 76  |

| 9.0 Host MAC                                    | 86  |

| 10.0 Serial Management                          | 109 |

| 11.0 IEEE 1588 Hardware Time Stamp Unit         | 125 |

| 12.0 General Purpose Timer & Free-Running Clock | 131 |

| 13.0 GPIO/LED Controller                        | 132 |

| 14.0 Register Descriptions                      | 136 |

| 15.0 Operational Characteristics                |     |

| 16.0 Package Outlines                           | 301 |

| Appendix A: Data sheet Revision History         | 304 |

| The Microchip Web Site                          | 306 |

| Customer Change Notification Service            | 306 |

| Customer Support                                | 306 |

| Product Identification System                   | 307 |

# 1.0 PREFACE

# 1.1 General Terms

| 100BT                      | 100BASE-T (100Mbps Fast Ethernet, IEEE 802.3u)                                                                                                                                                                    |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                            |                                                                                                                                                                                                                   |  |  |  |

| ADC                        | Analog-to-Digital Converter                                                                                                                                                                                       |  |  |  |

| ALR                        | Address Logic Resolution                                                                                                                                                                                          |  |  |  |

| BLW                        | Baseline Wander                                                                                                                                                                                                   |  |  |  |

| ВМ                         | Buffer Manager - Part of the switch fabric                                                                                                                                                                        |  |  |  |

| BPDU                       | Bridge Protocol Data Unit - Messages which carry the Spanning Tree<br>Protocol information                                                                                                                        |  |  |  |

| Byte                       | 8-bits                                                                                                                                                                                                            |  |  |  |

| CSMA/CD                    | Carrier Sense Multiple Access / Collision Detect                                                                                                                                                                  |  |  |  |

| CSR                        | Control and Status Registers                                                                                                                                                                                      |  |  |  |

| CTR                        | Counter                                                                                                                                                                                                           |  |  |  |

| DA                         | Destination Address                                                                                                                                                                                               |  |  |  |

| DWORD                      | 32-bits                                                                                                                                                                                                           |  |  |  |

| EPC                        | EEPROM Controller                                                                                                                                                                                                 |  |  |  |

| FCS                        | Frame Check Sequence - The extra checksum characters added to the end of an Ethernet frame, used for error detection and correction.                                                                              |  |  |  |

| FIFO                       | First In First Out buffer                                                                                                                                                                                         |  |  |  |

| FSM                        | Finite State Machine                                                                                                                                                                                              |  |  |  |

| GPIO                       | General Purpose I/O                                                                                                                                                                                               |  |  |  |

| НВІ                        | Host Bus Interface. The physical bus connecting the LAN9312 to the host. Also referred to as the Host Bus.                                                                                                        |  |  |  |

| HBIC                       | Host Bus Interface Controller. The hardware module that interfaces the LAN9312 to the HBI.                                                                                                                        |  |  |  |

| Host                       | External system (Includes processor, application software, etc.)                                                                                                                                                  |  |  |  |

| IGMP                       | Internet Group Management Protocol                                                                                                                                                                                |  |  |  |

| Inbound                    | Refers to data input to the LAN9312 from the host                                                                                                                                                                 |  |  |  |

| Level-Triggered Sticky Bit | This type of status bit is set whenever the condition that it represents is asserted. The bit remains set until the condition is no longer true, and the status bit is cleared by writing a zero.                 |  |  |  |

| Isb                        | Least Significant Bit                                                                                                                                                                                             |  |  |  |

| LSB                        | Least Significant Byte                                                                                                                                                                                            |  |  |  |

| MDI                        | Medium Dependant Interface                                                                                                                                                                                        |  |  |  |

| MDIX                       | Media Independent Interface with Crossover                                                                                                                                                                        |  |  |  |

| MII                        | Media Independent Interface                                                                                                                                                                                       |  |  |  |

| MIIM                       | Media Independent Interface Management                                                                                                                                                                            |  |  |  |

| MIL                        | MAC Interface Layer                                                                                                                                                                                               |  |  |  |

| MLT-3                      | Multi-Level Transmission Encoding (3-Levels). A tri-level encoding method where a change in the logic level represents a code bit "1" and the logic output remaining at the same level represents a code bit "0". |  |  |  |

| msb                        | Most Significant Bit                                                                                                                                                                                              |  |  |  |

| MSB                        | Most Significant Byte                                                                                                                                                                                             |  |  |  |

| NRZI                       | Non Return to Zero Inverted. This encoding method inverts the signal for a "1" and leaves the signal unchanged for a "0"                                                                                          |  |  |  |

| N/A                        | Not Applicable                                                                                                                                                                                                    |  |  |  |

| NC                         | No Connect                                                                                                                                                                                                        |  |  |  |

| OUI                        | Organizationally Unique Identifier                                                                                                                                                                                |  |  |  |

| _ = =                      | - 0                                                                                                                                                                                                               |  |  |  |

| Outbound  | Refers to data output from the LAN9312 to the host                                                                                                                                                                                                                           |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO cycle | Program I/O cycle. An SRAM-like read or write cycle on the HBI.                                                                                                                                                                                                              |

| PISO      | Parallel In Serial Out                                                                                                                                                                                                                                                       |

| PLL       | Phase Locked Loop                                                                                                                                                                                                                                                            |

| PTP       | Precision Time Protocol                                                                                                                                                                                                                                                      |

| RESERVED  | Refers to a reserved bit field or address. Unless otherwise noted, reserved bits must always be zero for write operations. Unless otherwise noted, values are not guaranteed when reading reserved bits. Unless otherwise noted, do not read or write to reserved addresses. |

| RTC       | Real-Time Clock                                                                                                                                                                                                                                                              |

| SA        | Source Address                                                                                                                                                                                                                                                               |

| SFD       | Start of Frame Delimiter - The 8-bit value indicating the end of the preamble of an Ethernet frame.                                                                                                                                                                          |

| SIPO      | Serial In Parallel Out                                                                                                                                                                                                                                                       |

| SMI       | Serial Management Interface                                                                                                                                                                                                                                                  |

| SQE       | Signal Quality Error (also known as "heartbeat")                                                                                                                                                                                                                             |

| SSD       | Start of Stream Delimiter                                                                                                                                                                                                                                                    |

| UDP       | User Datagram Protocol - A connectionless protocol run on top of IP networks                                                                                                                                                                                                 |

| UUID      | Universally Unique IDentifier                                                                                                                                                                                                                                                |

| WORD      | 16-bits                                                                                                                                                                                                                                                                      |

|           |                                                                                                                                                                                                                                                                              |

# 1.2 Buffer Types

Table 1-1 describes the pin buffer type notation used in Section 3.0, "Pin Description and Configuration," on page 13 and throughout this document.

TABLE 1-1: BUFFER TYPES

| Buffer Type | Description                                                                                                                                                                                                                                          |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IS          | Schmitt-triggered Input                                                                                                                                                                                                                              |  |  |  |  |  |

| O8          | Output with 8mA sink and 8mA source                                                                                                                                                                                                                  |  |  |  |  |  |

| OD8         | Open-drain output with 8mA sink                                                                                                                                                                                                                      |  |  |  |  |  |

| O12         | Output with 12mA sink and 12mA source                                                                                                                                                                                                                |  |  |  |  |  |

| OD12        | Open-drain output with 12mA sink                                                                                                                                                                                                                     |  |  |  |  |  |

| PU          | 50uA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                                |  |  |  |  |  |

|             | <b>Note:</b> Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the LAN9312. When connected to a load that must be pulled high, an external resistor must be added. |  |  |  |  |  |

| PD          | 50uA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                            |  |  |  |  |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the LAN9312. When connected to a load that must be pulled low, an external resistor must be added.       |  |  |  |  |  |

| Al          | Analog input                                                                                                                                                                                                                                         |  |  |  |  |  |

| AO          | Analog output                                                                                                                                                                                                                                        |  |  |  |  |  |

| AIO         | Analog bi-directional                                                                                                                                                                                                                                |  |  |  |  |  |

| ICLK        | Crystal oscillator input pin                                                                                                                                                                                                                         |  |  |  |  |  |

| OCLK        | Crystal oscillator output pin                                                                                                                                                                                                                        |  |  |  |  |  |

| Р           | Power pin                                                                                                                                                                                                                                            |  |  |  |  |  |

# 1.3 Register Nomenclature

Table 1-2 describes the register bit attribute notation used throughout this document.

TABLE 1-2: REGISTER BIT TYPES

| Register Bit Type Notation | Register Bit Description                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R                          | Read: A register or bit with this attribute can be read.                                                                                                                                                                                                                                                                                                                             |

| W                          | Read: A register or bit with this attribute can be written.                                                                                                                                                                                                                                                                                                                          |

| RO                         | Read only: Read only. Writes have no effect.                                                                                                                                                                                                                                                                                                                                         |

| WO                         | Write only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                                                                                                                                                                                                  |

| WC                         | Write One to Clear: writing a one clears the value. Writing a zero has no effect                                                                                                                                                                                                                                                                                                     |

| WAC                        | Write Anything to Clear: writing anything clears the value.                                                                                                                                                                                                                                                                                                                          |

| RC                         | Read to Clear: Contents is cleared after the read. Writes have no effect.                                                                                                                                                                                                                                                                                                            |

| LL                         | Latch Low: Clear on read of register.                                                                                                                                                                                                                                                                                                                                                |

| LH                         | Latch High: Clear on read of register.                                                                                                                                                                                                                                                                                                                                               |

| SC                         | <b>Self-Clearing:</b> Contents are self-cleared after the being set. Writes of zero have no effect. Contents can be read.                                                                                                                                                                                                                                                            |

| SS                         | <b>Self-Setting:</b> Contents are self-setting after being cleared. Writes of one have no effect. Contents can be read.                                                                                                                                                                                                                                                              |

| RO/LH                      | Read Only, Latch High: Bits with this attribute will stay high until the bit is read. After it is read, the bit will either remain high if the high condition remains, or will go low if the high condition has been removed. If the bit has not been read, the bit will remain high regardless of a change to the high condition. This mode is used in some Ethernet PHY registers. |

| NASR                       | Not Affected by Software Reset. The state of NASR bits do not change on assertion of a software reset.                                                                                                                                                                                                                                                                               |

| RESERVED                   | Reserved Field: Reserved fields must be written with zeros to ensure future compatibility. The value of reserved bits is not guaranteed on a read.                                                                                                                                                                                                                                   |

Many of these register bit notations can be combined. Some examples of this are shown below:

- R/W: Can be written. Will return current setting on a read.

- R/WAC: Will return current setting on a read. Writing anything clears the bit.

## 2.0 INTRODUCTION

# 2.1 General Description

The LAN9312 is a full featured, 2 port 10/100 managed Ethernet switch designed for embedded applications where performance, flexibility, ease of integration and system cost control are required. The LAN9312 combines all the functions of a 10/100 switch system, including the switch fabric, packet buffers, buffer manager, media access controllers (MACs), PHY transceivers, and host bus interface. The LAN9312 complies with the IEEE 802.3 (full/half-duplex 10BASE-T and 100BASE-TX) Ethernet protocol specification and 802.1D/802.1Q network management protocol specifications, enabling compatibility with industry standard Ethernet and Fast Ethernet applications.

At the core of the LAN9312 is the high performance, high efficiency 3 port Ethernet switch fabric. The switch fabric contains a 3 port VLAN layer 2 switch engine that supports untagged, VLAN tagged, and priority tagged frames. The switch fabric provides an extensive feature set which includes spanning tree protocol support, multicast packet filtering and Quality of Service (QoS) packet prioritization by VLAN tag, destination address, port default value or DIFFSERV/TOS, allowing for a range of prioritization implementations. 32K of buffer RAM allows for the storage of multiple packets while forwarding operations are completed, and a 1K entry forwarding table provides ample room for MAC address forwarding tables. Each port is allocated a cluster of 4 dynamic QoS queues which allow each queue size to grow and shrink with traffic, effectively utilizing all available memory. This memory is managed dynamically via the buffer manager block within the switch fabric. All aspects of the switch fabric are managed via the switch fabric configuration and status registers, which are indirectly accessible via the memory mapped system control and status registers.

The LAN9312 provides 2 switched ports. Each port is fully compliant with the IEEE 802.3 standard and all internal MACs and PHYs support full/half duplex 10BASE-T and 100BASE-TX operation. The LAN9312 provides 2 on-chip PHYs, 1 Virtual PHY and 3 MACs. The Virtual PHY and the Host MAC are used to connect the LAN9312 switch fabric to the host bus interface. All ports support automatic or manual full duplex flow control or half duplex backpressure (forced collision) flow control. Automatic 32-bit CRC generation/checking and automatic payload padding are supported to further reduce CPU overhead. 2K jumbo packet (2048 byte) support allows for oversized packet transfers, effectively increasing throughput while deceasing CPU load. All MAC and PHY related settings are fully configurable via their respective registers within the LAN9312.

The integrated Host Bus Interface (HBI) easily interfaces to most 32-bit embedded CPU's via a simple SRAM like interface, enabling switch fabric access via the internal Host MAC and allowing full control over the LAN9312 via memory mapped system control and status registers. The HBI supports 32-bit operation with big, little, and mixed endian operations. Four separate FIFO mechanisms (TX/RX Data FIFO's, TX/RX Status FIFO's) interface the HBI to the Host MAC and facilitate the transferring of packet data and status information between the host CPU and the switch fabric. The LAN9312 also provides power management features which allow for wake on LAN, wake on link status change (energy detect), and magic packet wakeup detection. A configurable host interrupt pin allows the device to inform the host CPU of any internal interrupts.

The LAN9312 contains an I<sup>2</sup>C/Microwire master EEPROM controller for connection to an optional EEPROM. This allows for the storage and retrieval of static data. The internal EEPROM Loader can be optionally configured to automatically load stored configuration settings from the EEPROM into the LAN9312 at reset.

In addition to the primary functionality described above, the LAN9312 provides additional features designed for extended functionality. These include a configurable 16-bit General Purpose Timer (GPT), a 32-bit 25MHz free running counter, a 12-bit configurable GPIO/LED interface, and IEEE 1588 time stamping on all ports and select GPIOs. The IEEE time stamp unit provides a 64-bit tunable clock for accurate PTP timing and a timer comparator to allow time based interrupt generation.

The LAN9312's performance, features and small size make it an ideal solution for many applications in the consumer electronics and industrial automation markets. Targeted applications include: set top boxes (cable, satellite and IP), digital televisions, digital video recorders, voice over IP and video phone systems, home gateways, and test and measurement equipment.

# 2.2 Block Diagram

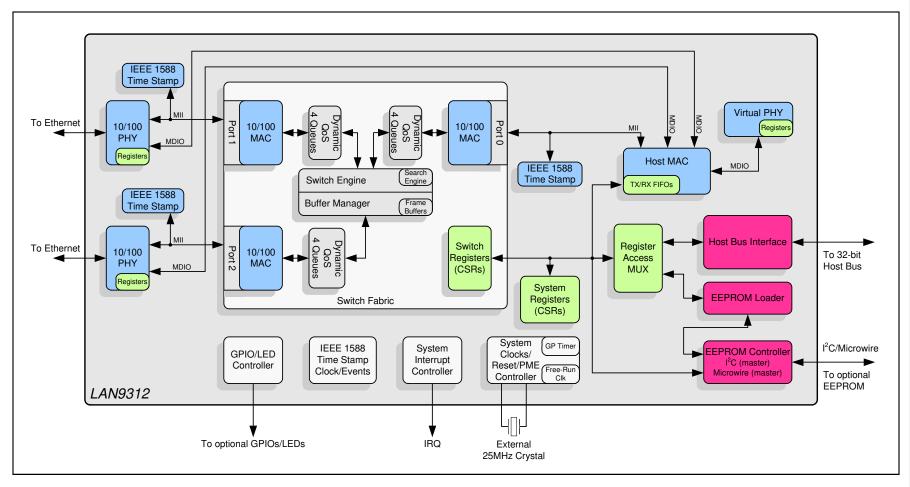

FIGURE 2-1: INTERNAL LAN9312 BLOCK DIAGRAM

#### 2.2.1 SYSTEM CLOCKS/RESET/PME CONTROLLER

A clock module contained within the LAN9312 generates all the system clocks required by the device. This module interfaces directly with the external 25MHz crystal/oscillator to generate the required clock divisions for each internal module, with the exception of the 1588 clocks, which are generated in the 1588 Time Stamp Clock/Events module. A 16-bit general purpose timer and 32-bit free-running clock are provided by this module for general purpose use.

The LAN9312 reset events are categorized as chip-level resets, multi-module resets, and single-module resets.

A chip-level reset is initiated by assertion of any of the following input events:

- · Power-On Reset

- nRST Pin Reset

A multi-module reset is initiated by assertion of the following:

- Digital Reset DIGITAL\_RST (bit 0) in the Reset Control Register (RESET\_CTL)

- Resets all LAN9312 sub-modules except the Ethernet PHYs (Port 1 PHY, Port 2 PHY, and Virtual PHY)

- Soft Reset SRST (bit 0) in the Hardware Configuration Register (HW\_CFG)

- Resets the HBI, Host MAC, and System CSRs below address 100h

A single-module reset is initiated by assertion of the following:

- Port 2 PHY Reset PHY2\_RST (bit 2) in the Reset Control Register (RESET\_CTL) or Reset (bit 15) in the Port x PHY Basic Control Register (PHY BASIC CONTROL x)

- Resets the Port 2 PHY

- Port 1 PHY Reset PHY1\_RST (bit 1) in the Reset Control Register (RESET\_CTL) or Reset (bit 15) in the Port x PHY Basic Control Register (PHY BASIC CONTROL x)

- Resets the Port 1 PHY

- Virtual PHY Reset VPHY\_RST (bit 0) in the Reset Control Register (RESET\_CTL), (bit 10) in the Power Management Control Register (PMT\_CTRL), or Reset (bit 15) in the Virtual PHY Basic Control Register (VPHY\_BASIC\_CTRL)

- Resets the Virtual PHY

The LAN9312 supports numerous power management and wakeup features. The Port 1 & 2 PHYs provide general power-down and energy detect power-down modes, which allow a reduction in PHY power consumption. The Host MAC provides wake-up frame detection and magic packet detection modes. The LAN9312 can be programmed to issue an external wake signal (PME) via several methods, including wake on LAN, wake on link status change (energy detect), and magic packet wakeup. The PME signal is ideal for triggering system power-up using remote Ethernet wakeup events.

#### 2.2.2 SYSTEM INTERRUPT CONTROLLER

The LAN9312 provides a multi-tier programmable interrupt structure which is controlled by the System Interrupt Controller. At the top level are the Interrupt Status Register (INT\_STS) and Interrupt Enable Register (INT\_EN). These registers aggregate and control all interrupts from the various LAN9312 sub-modules. The LAN9312 is capable of generating interrupt events from the following:

- · 1588 Time Stamp

- · Switch Fabric

- · Ethernet PHYs

- GPIOs

- Host MAC (FIFOs, power management)

- · General Purpose Timer

- Software (general purpose)

A dedicated programmable IRQ interrupt output pin is provided for external indication of any LAN9312 interrupts. The IRQ pin is controlled via the Interrupt Configuration Register (IRQ\_CFG), which allows configuration of the IRQ buffer type, polarity, and de-assertion interval.

#### 2.2.3 SWITCH FABRIC

The Switch Fabric consists of the following major function blocks:

#### 10/100 MACs

There is one 10/100 Ethernet MAC per switch fabric port, which provides basic 10/100 Ethernet functionality, including transmission deferral, collision back-off/retry, TX/RX FCS checking/generation, TX/RX pause flow control, and transmit back pressure. The 10/100 MACs act as an interface between the switch engine and the 10/100 PHYs (for ports 1 and 2). The port 0 10/100 MAC interfaces the switch engine to the Host MAC. Each 10/100 MAC includes RX and TX FIFOs and per port statistic counters.

#### · Switch Engine

This block, consisting of a 3 port VLAN layer 2 switching engine, provides the control for all forwarding/filtering rules and supports untagged, VLAN tagged, and priority tagged frames. The switch engine provides an extensive feature set which includes spanning tree protocol support, multicast packet filtering and Quality of Service (QoS) packet prioritization by VLAN tag, destination address, and port default value or DIFFSERV/TOS, allowing for a range of prioritization implementations. A 1K entry forwarding table provides ample room for MAC address forwarding tables.

#### Buffer Manager

This block controls the free buffer space, multi-level transmit queues, transmission scheduling, and packet dropping of the switch fabric. 32K of buffer RAM allows for the storage of multiple packets while forwarding operations are completed. Each port is allocated 1a cluster of 4 dynamic QoS queues which allow each queue size to grow and shrink with traffic, effectively utilizing all available memory. This memory is managed dynamically via the Buffer Manager block.

#### Switch CSRs

This block contains all switch related control and status registers, and allows all aspects of the switch fabric to be managed. These registers are indirectly accessible via the memory mapped system control and status registers

## 2.2.4 ETHERNET PHYS

The LAN9312 contains three PHYs: Port 1 PHY, Port 2 PHY and a Virtual PHY. The Port 1 & 2 PHYs are identical in functionality and each connect their corresponding Ethernet signal pins to the switch fabric MAC of their respective port. These PHYs interface with their respective MAC via an internal MII interface. The Virtual PHY provides the virtual functionality of a PHY and allows connection of the Host MAC to port 0 of the switch fabric as if it was connected to a single port PHY. All PHYs comply with the IEEE 802.3 Physical Layer for Twisted Pair Ethernet and can be configured for full/half duplex 100 Mbps (100BASE-TX) or 10Mbps (10BASE-T) Ethernet operation. All PHY registers follow the IEEE 802.3 (clause 22.2.4) specified MII management register set.

#### 2.2.5 HOST BUS INTERFACE (HBI)

The Host Bus Interface (HBI) module provides a high-speed asynchronous SRAM-like slave interface that facilitates communication between the LAN9312 and a host system. The HBI allows access to the System CSRs and handles byte swapping based on the dynamic endianess select. The HBI interfaces to the switch fabric via the Host MAC, which contains the TX/RX Data and Status FIFOs, Host MAC registers and power management features. The main features of the HBI are:

- · Asynchronous 32-bit Host Bus Interface

- Host Data Bus Endianess Control

- Direct FIFO Access Modes

- · System CSRs Access

- · Interrupt Support

# 2.2.6 HOST MAC

The Host MAC incorporates the essential protocol requirements for operating an Ethernet/IEEE 802.3-compliant node and provides an interface between the Host Bus Interface (HBI) and the Ethernet PHYs and Switch Fabric. On the front end, the Host MAC interfaces to the HBI via 2 sets of FIFO's (TX Data FIFO, TX Status FIFO, RX Data FIFO, RX Status FIFO). The FIFOs are a conduit between the HBI and the Host MAC through which all transmitted and received data and status information is passed. An additional bus is used to access the Host MAC CSR's via the Host MAC CSR Interface Command Register (MAC\_CSR\_CMD) and Host MAC CSR Interface Data Register (MAC\_CSR\_DATA) system registers.

On the back end, the Host MAC interfaces with the 10/100 Ethernet PHY's (Virtual PHY, Port 1 PHY, Port 2 PHY) via an internal SMI (Serial Management Interface) bus. This allows the Host MAC access to the PHY's internal registers via the Host MAC MII Access Register (HMAC\_MII\_ACC) and Host MAC MII Data Register (HMAC\_MII\_DATA). The Host MAC interfaces to the Switch Engine Port 0 via an internal MII (Media Independent Interface) connection allowing for incoming and outgoing Ethernet packet transfers.

The Host MAC can operate at either 100Mbps or 10Mbps in both half-duplex or full-duplex modes. When operating in half-duplex mode, the Host MAC complies fully with Section 4 of ISO/IEC 8802-3 (ANSI/IEEE standard) and ANSI/IEEE 802.3 standards. When operating in full-duplex mode, the Host MAC complies with IEEE 802.3 full-duplex operation standard.

#### 2.2.7 EEPROM CONTROLLER/LOADER

The EEPROM Controller is an I<sup>2</sup>C/Microwire master module which interfaces an optional external EEPROM with the system register bus and the EEPROM Loader. Multiple types (I<sup>2</sup>C/Microwire) and sizes of external EEPROMs are supported. Configuration of the EEPROM type and size are accomplished via the eeprom\_type\_strap and eeprom\_size\_strap[1:0] configuration straps respectively. Various commands are supported for each EEPROM type, allowing for the storage and retrieval of static data. The I<sup>2</sup>C interface conforms to the Philips I<sup>2</sup>C-Bus Specification.

The EEPROM Loader module interfaces to the EEPROM Controller, Ethernet PHYs, and the system CSRs. The EEPROM Loader provides the automatic loading of configuration settings from the EEPROM into the LAN9312 at reset. The EEPROM Loader runs upon a pin reset (nRST), power-on reset (POR), digital reset (DIGITAL\_RST bit in the Reset Control Register (RESET\_CTL)), or upon the issuance of a RELOAD command via the EEPROM Command Register (E2P\_CMD).

#### 2.2.8 1588 TIME STAMP

The IEEE 1588 Time Stamp modules provide hardware support for the IEEE 1588 Precision Time Protocol (PTP), allowing clock synchronization with remote Ethernet devices, packet time stamping, and time driven event generation. Time stamping is supported on all ports, with an individual IEEE 1588 Time Stamp module connected to each port via the MII bus. Any port may function as a master or a slave clock per the IEEE 1588 specification, and the LAN9312 as a whole may function as a boundary clock.

A 64-bit tunable clock is provided that is used as the time source for all IEEE 1588 time stamp related functions. The IEEE 1588 Clock/Events block provides IEEE 1588 clock comparison based interrupt generation and time stamp related GPIO event generation. Two LAN9312 GPIO pins (GPIO[8:9]) can be used to trigger a time stamp capture when configured as an input, or output a signal from the GPIO based on an IEEE 1588 clock target compare event when configured as an output. All features of the IEEE 1588 hardware time stamp unit can be monitored and configured via their respective IEEE 1588 configuration and status registers (CSRs).

# 2.2.9 GPIO/LED CONTROLLER

The LAN9312 provides 12 configurable general-purpose input/output pins which are controlled via this module. These pins can be individually configured via the GPIO/LED CSRs to function as inputs, push-pull outputs, or open drain outputs and each is capable of interrupt generation with configurable polarity. Two of the GPIO pins (GPIO[9:8]) can be used for IEEE 1588 timestamp functions, allowing GPIO driven 1588 time clock capture when configured as an input, or GPIO output generation based on an IEEE 1588 clock target compare event.

In addition, 8 of the GPIO pins can be alternatively configured as LED outputs. These pins, GPIO[7:0] (nP1LED[3:0] and nP2LED[3:0]), may be enabled to drive Ethernet status LEDs for external indication of various attributes of the switch ports.

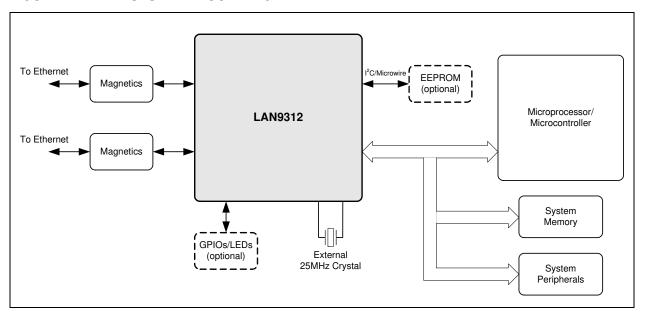

# 2.3 System Configuration

In a typical application, the LAN9312 Host Bus Interface (HBI) is connected to the host microprocessor/microcontroller via the asynchronous 32-bit interface, allowing access to the LAN9312 system configuration and status registers. The LAN9312 utilizes the internal Host MAC to provide a network path for the host CPU. The LAN9312 may share the host bus with additional system memory and/or peripherals. For more information on the HBI, refer to Section 8.0, "Host Bus Interface (HBI)," on page 76.

The 2 Ethernet ports of the LAN9312 must be connected to Auto-MDIX style magnetics for proper operation on the Ethernet network. Refer to the Microchip Application Note 8.13 "Suggested Magnetics" for further details.

The LAN9312 also supports optional EEPROM and GPIOs/LEDs. When an EEPROM is connected, the EEPROM loader can be used to load the initial device configuration from the external EEPROM via the I<sup>2</sup>C/Microwire interface.

A system configuration diagram of the LAN9312 in a typical embedded environment can be seen in Figure 2-2.

# FIGURE 2-2: SYSTEM BLOCK DIAGRAM

# 3.0 PIN DESCRIPTION AND CONFIGURATION

# 3.1 Pin Diagrams

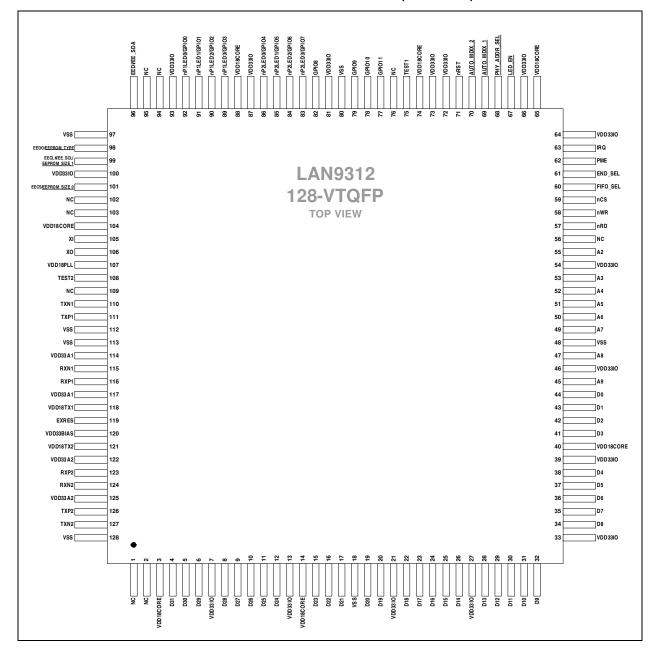

## 3.1.1 128-VTQFP PIN DIAGRAM

FIGURE 3-1: LAN9312 128-VTQFP PIN ASSIGNMENTS (TOP VIEW)

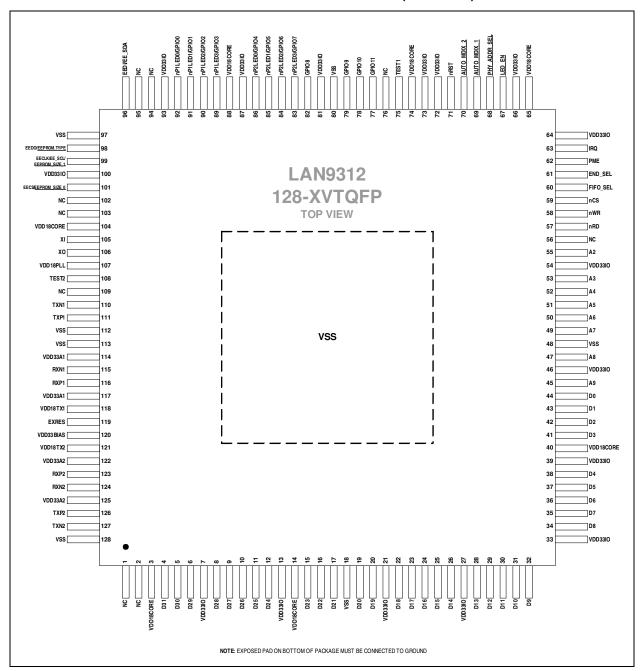

## 3.1.2 128-XVTQFP PIN DIAGRAM

FIGURE 3-2: LAN9312 128-XVTQFP PIN ASSIGNMENTS (TOP VIEW)

# 3.2 Pin Descriptions

This section contains the descriptions of the LAN9312 pins. The pin descriptions have been broken into functional groups as follows:

- LAN Port 1 Pins

- · LAN Port 2 Pins

- · LAN Port 1 & 2 Power and Common Pins

- · Host Bus Interface Pins

- EEPROM Pins

- Dedicated Configuration Strap Pins

- · Miscellaneous Pins

- PLL Pins

- · Core and I/O Power and Ground Pins

- No-Connect Pins

Note: A list of buffer type definitions is provided in Section 1.2, "Buffer Types," on page 5.

TABLE 3-1: LAN PORT 1 PINS

| Pin   | Name                           | Symbol      | Buffer<br>Type          | Description                                                                                                                                                                                                                                                        |  |  |

|-------|--------------------------------|-------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | Port 1 LED<br>Indicators       | nP1LED[3:0] | OD12                    | LED Indicators: When configured as LED outputs via the LED Configuration Register (LED_CFG), these pins are open-drain, active low outputs and the pull-ups and input buffers are disabled. The functionality of each pin is determined via the LED_CFG[9:8] bits. |  |  |

| 89-92 | General<br>Purpose I/O<br>Data | GPIO[3:0]   | IS/O12/O<br>D12<br>(PU) | +                                                                                                                                                                                                                                                                  |  |  |

|       |                                |             |                         | Note: See Section 13.0, "GPIO/LED Controller," on page 132 for additional details.                                                                                                                                                                                 |  |  |

| 110   | Port 1 Ethernet<br>TX Negative | TXN1        | AIO                     | Ethernet TX Negative: Negative output of Port 1<br>Ethernet transmitter. See Note 3-1 for additional information.                                                                                                                                                  |  |  |

| 111   | Port 1 Ethernet<br>TX Positive | TXP1        | AIO                     | Ethernet TX Positive: Positive output of Port 1 Ethernet transmitter. See Note 3-1 for additional information.                                                                                                                                                     |  |  |

| 115   | Port 1 Ethernet<br>RX Negative | RXN1        | AIO                     | Ethernet RX Negative: Negative input of Port 1 Ethernet receiver. See Note 3-1 for additional information.                                                                                                                                                         |  |  |

| 116   | Port 1 Ethernet<br>RX Positive | RXP1        | AIO                     | Ethernet RX Positive: Positive input of Port 1<br>Ethernet receiver. See Note 3-1 for additional information.                                                                                                                                                      |  |  |

Note 3-1 The pin names for the twisted pair pins apply to a normal connection. If HP Auto-MDIX is enabled and a reverse connection is detected or manually selected, the RX and TX pins will be swapped internally.

TABLE 3-2: LAN PORT 2 PINS

| Pin   | Name                           | Symbol      | Buffer<br>Type          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------------------|-------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Port 2 LED<br>Indicators       | nP2LED[3:0] | OD12                    | LED indicators: When configured as LED outputs via the LED Configuration Register (LED_CFG), these pins are open-drain, active low outputs and the pull-ups and input buffers are disabled. The functionality of each pin is determined via the LED_CFG[9:8] bits.                                                                                                                                                                                                   |

| 83-86 | General<br>Purpose I/O<br>Data | GPIO[7:4]   | IS/O12/O<br>D12<br>(PU) | General Purpose I/O Data: When configured as GPIO via the LED Configuration Register (LED_CFG), these general purpose signals are fully programmable as either push-pull outputs, opendrain outputs or Schmitt-triggered inputs by writing the General Purpose I/O Configuration Register (GPIO_CFG) and General Purpose I/O Data & Direction Register (GPIO_DATA_DIR). The pull-ups are enabled in GPIO mode. The input buffers are disabled when set as an output. |

|       |                                |             |                         | Note: See Section 13.0, "GPIO/LED Controller," on page 132 for additional details.                                                                                                                                                                                                                                                                                                                                                                                   |

| 127   | Port 2 Ethernet<br>TX Negative | TXN2        | AIO                     | Ethernet TX Negative: Negative output of Port 2 Ethernet transmitter. See Note 3-2 for additional information.                                                                                                                                                                                                                                                                                                                                                       |

| 126   | Port 2 Ethernet<br>TX Positive | TXP2        | AIO                     | Ethernet TX Positive: Positive output of Port 2 Ethernet transmitter. See Note 3-2 for additional information.                                                                                                                                                                                                                                                                                                                                                       |

| 124   | Port 2 Ethernet<br>RX Negative | RXN2        | AIO                     | Ethernet RX Negative: Negative input of Port 2 Ethernet receiver. See Note 3-2 for additional information.                                                                                                                                                                                                                                                                                                                                                           |

| 123   | Port 2 Ethernet<br>RX Positive | RXP2        | AIO                     | Ethernet RX Positive: Positive input of Port 2 Ethernet receiver. See Note 3-2 for additional information.                                                                                                                                                                                                                                                                                                                                                           |

Note 3-2 The pin names for the twisted pair pins apply to a normal connection. If HP Auto-MDIX is enabled and a reverse connection is detected or manually selected, the RX and TX pins will be swapped internally.

TABLE 3-3: LAN PORT 1 & 2 POWER AND COMMON PINS

| Pin     | Name                                   | Symbol    | Buffer<br>Type | Description                                                                                                       |

|---------|----------------------------------------|-----------|----------------|-------------------------------------------------------------------------------------------------------------------|

| 119     | Bias Reference                         | EXRES     | Al             | Bias Reference: Used for internal bias circuits.<br>Connect to an external 12.4K ohm, 1% resistor to<br>ground.   |

| 114,117 | +3.3V Port 1<br>Analog Power<br>Supply | VDD33A1   | Р              | +3.3V Port 1 Analog Power Supply  Refer to the LAN9312 reference schematic for additional connection information. |

| 122,125 | +3.3V Port 2<br>Analog Power<br>Supply | VDD33A2   | Р              | +3.3V Port 2 Analog Power Supply  Refer to the LAN9312 reference schematic for additional connection information. |

| 120     | +3.3V Master<br>Bias Power<br>Supply   | VDD33BIAS | Р              | +3.3V Master Bias Power Supply  Refer to the LAN9312 reference schematic for additional connection information.   |

TABLE 3-3: LAN PORT 1 & 2 POWER AND COMMON PINS (CONTINUED)

| Pin | Name                                           | Symbol   | Buffer<br>Type | Description                                                                                                                                                                                                                                           |

|-----|------------------------------------------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 121 | Port 2<br>Transmitter<br>+1.8V Power<br>Supply | VDD18TX2 | Р              | Port 2 Transmitter +1.8V Power Supply: This pin is supplied from the internal PHY voltage regulator. This pin must be tied to the VDD18TX1 pin for proper operation.  Refer to the LAN9312 reference schematic for additional connection information. |

| 118 | Port 1<br>Transmitter<br>+1.8V Power<br>Supply | VDD18TX1 | Р              | Port 1 Transmitter +1.8V Power Supply: This pin must be connected directly to the VDD18TX2 pin for proper operation.  Refer to the LAN9312 reference schematic for additional connection information.                                                 |

TABLE 3-4: HOST BUS INTERFACE PINS

|                                                     | ,                                    |          |                | T                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-----------------------------------------------------|--------------------------------------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin                                                 | Name                                 | Symbol   | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 4-6,<br>8-12,                                       | Host Bus Data                        | D[31:0]  | IS/O8          | <b>Host Bus Data High:</b> Bits 31-0 of the Host Bus 32-bit data port.                                                                                                                                                                                                                                                                        |  |  |  |  |

| 15-17,19,<br>20,22-26,<br>28-32,<br>34-38,<br>41-44 |                                      |          |                | Note: Big and little endianess is supported.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 45,47,<br>49-53,                                    | Host Bus<br>Address                  | A[9:2]   | IS             | Host Bus Address: 9-bit Host Bus Address Port used to select Internal CSR's and TX and RX FIFO's.                                                                                                                                                                                                                                             |  |  |  |  |

| 55                                                  |                                      |          |                | Note: The A0 and A1 bits are not used because the LAN9312 must be accessed on DWORD boundaries.                                                                                                                                                                                                                                               |  |  |  |  |

| 57                                                  | Read Strobe                          | nRD      | IS             | Read Strobe: Active low strobe to indicate a reac cycle. This signal is qualified by the nCS chip sele                                                                                                                                                                                                                                        |  |  |  |  |

| 58                                                  | Write Strobe                         | nWR      | IS             | <b>Write Strobe:</b> Active low strobe to indicate a write cycle. This signal is qualified by the nCS chip select.                                                                                                                                                                                                                            |  |  |  |  |

| 59                                                  | Chip Select                          | nCS      | IS             | <b>Chip Select:</b> Active low signal used to qualify read and write operations.                                                                                                                                                                                                                                                              |  |  |  |  |

| 60                                                  | Data FIFO<br>Direct Access<br>Select | FIFO_SEL | IS             | Data FIFO Direct Access Select: When driven high, all accesses to the LAN9312 are directed to the RX and TX Data FIFO's. All reads are from the RX Data FIFO, and all writes are to the TX Data FIFO. In this mode, the address input is ignored. Refer to Section 14.1.3, "Direct FIFO Access Mode," on page 137 for additional information. |  |  |  |  |

| 61                                                  | Endianess<br>Select                  | END_SEL  | IS             | Endianess Select: When this signal is set high, big endian mode is selected. When low, little endian mode is selected. This signal may be dynamically changed or held static. Refer to Section 8.0, "Host Bus Interface (HBI)," on page 76 for additional information.                                                                        |  |  |  |  |

**Note:** Refer to Section 8.0, "Host Bus Interface (HBI)," on page 76 for additional information regarding the use of these signals.

TABLE 3-5: EEPROM PINS

| Pin | Name                                                   | Symbol        | Buffer<br>Type | Description                                                                                                                                                                                                                        |

|-----|--------------------------------------------------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | EEPROM<br>Microwire Data<br>Input                      | EEDI          | IS<br>(PD)     | <b>EEPROM Microwire Data Input (EEDI):</b> In Microwire EEPROM mode ( <u>EEPROM TYPE</u> = 0), this pin is the Microwire EEPROM serial data input.                                                                                 |

| 96  | EEPROM I <sup>2</sup> C<br>Serial Data<br>Input/Output | EE_SDA        | IS/OD8         | EEPROM I <sup>2</sup> C Serial Data Input/Output (EE_SDA): In I <sup>2</sup> C EEPROM mode ( <u>EEPROM_TYPE</u> = 1), this pin is the I <sup>2</sup> C EEPROM serial data input/output.                                            |

|     |                                                        |               |                | <b>Note:</b> If I <sup>2</sup> C is selected, an external pull-up is required when using an EEPROM and is recommended if no EEPROM is attached.                                                                                    |

|     | EEPROM<br>Microwire Data<br>Output                     | EEDO          | O8             | <b>EEPROM Microwire Data Output:</b> In Microwire EEPROM mode ( <u>EEPROM TYPE</u> = 0), this pin is the Microwire EEPROM serial data output.                                                                                      |

|     |                                                        |               |                | <b>Note:</b> In I <sup>2</sup> C mode ( <u>EEPROM TYPE</u> =1), this pin is not used and is driven low.                                                                                                                            |

| 98  |                                                        |               |                | <b>Note:</b> When not using a Microwire or I <sup>2</sup> C EEPROM, an external pull-down resistor is recommended on this pin.                                                                                                     |

|     | EEPROM Type<br>Strap                                   | EEPROM_TYPE   | IS<br>Note 3-3 | EEPROM Type Strap: Configures the EEPROM type. See Note 3-4 0 = Microwire Mode 1 = I <sup>2</sup> C Mode                                                                                                                           |

|     |                                                        |               |                | Note: When not using a Microwire or I <sup>2</sup> C EEPROM, an external pull-down resistor is recommended on this pin.                                                                                                            |

|     | EEPROM<br>Microwire<br>Serial Clock                    | EECLK         | O8             | <b>EEPROM Microwire Serial Clock (EECLK):</b> In Microwire EEPROM mode ( <u>EEPROM_TYPE</u> = 0), this pin is the Microwire EEPROM clock output.                                                                                   |

|     | EEPROM I <sup>2</sup> C<br>Serial Clock                | EE_SCL        | IS/OD8         | <b>EEPROM I<sup>2</sup>C Serial Clock (EE_SCL):</b> In I <sup>2</sup> C EEPROM mode ( <u>EEPROM TYPE</u> =1), this pin is the I <sup>2</sup> C EEPROM clock input/open-drain output.                                               |

| 99  |                                                        |               |                | <b>Note:</b> If I <sup>2</sup> C is selected, an external pull-up is required when using an EEPROM and is recommended if no EEPROM is attached.                                                                                    |

|     | EEPROM Size<br>Strap 1                                 | EEPROM_SIZE_1 | IS<br>Note 3-5 | <b>EEPROM Size Strap 1:</b> Configures the high bit of the EEPROM size range as specified in Section 10.2, "I2C/Microwire Master EEPROM Controller," on page 109. This bit is not used for I <sup>2</sup> C EEPROMs. See Note 3-4. |

|     | EEPROM<br>Microwire Chip<br>Select                     | EECS          | O8             | <b>EEPROM Microwire Chip Select:</b> In Microwire EEPROM mode ( <u>EEPROM TYPE</u> = 0), this pin is the Microwire EEPROM chip select output.                                                                                      |

| 101 |                                                        |               |                | <b>Note:</b> In I <sup>2</sup> C mode ( <u>EEPROM TYPE</u> =1), this pin is not used and is driven low.                                                                                                                            |

|     | EEPROM Size<br>Strap 0                                 | EEPROM SIZE 0 | IS<br>Note 3-3 | <b>EEPROM Size Strap 0:</b> Configures the low bit of the EEPROM size range as specified in Section 10.2, "I2C/Microwire Master EEPROM Controller," on page 109. See Note 3-4.                                                     |

- Note 3-3 The IS buffer type is valid only during the time specified in Section 15.5.2, "Reset and Configuration Strap Timing," on page 292.

- Note 3-4 Configuration strap values are latched on power-on reset or nRST de-assertion. Configuration strap pins are identified by an underlined symbol name. Refer to Section 4.2.4, "Configuration Straps," on page 25 for more information.

Note 3-5 The IS buffer type is valid only during the time specified in Section 15.5.2, "Reset and Configuration Strap Timing," on page 292 and when in I<sup>2</sup>C mode.

TABLE 3-6: DEDICATED CONFIGURATION STRAP PINS

| Pin | Name                                 | Symbol        | Buffer<br>Type | Description                                                                                                                                                                                                                                                 |                        |                       |                       |  |

|-----|--------------------------------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------|--|

| 67  | LED Enable<br>Strap                  | <u>LED EN</u> | IS<br>(PU)     | LED Enable Strap: Configures the default value for the LED_EN bits in the LED Configuration Register (LED_CFG). When latched low, all 8 LED/GPIO pins are configured as GPIOs. When latched high, all 8 LED/GPIO pins are configured as LEDs. See Note 3-6. |                        |                       |                       |  |

|     | PHY Address<br>Strap                 | PHY ADDR SEL  | IS<br>(PU)     | PHY Address Select Strap: Configures the default MII management address values for the PHYs (Virtual, Port 1, and Port 2) as detailed in Section 7.1.1, "PHY Addressing," on page 62.                                                                       |                        |                       |                       |  |

| 68  |                                      |               |                | PHY_ADDR_SEL<br>VALUE                                                                                                                                                                                                                                       | VIRTUAL PHY<br>ADDRESS | PORT 1 PHY<br>ADDRESS | PORT 2 PHY<br>ADDRESS |  |