Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Ordering number : EN5505D

## **LB1845**

# PWM Current Controlling Stepping Motor Driver

http://onsemi.com

#### **Overview**

The LB1845 is a PWM current control type stepping motor driver that uses a bipolar drive scheme. It is particularly suitable for driving carriage and paper feed stepping motors in printers and similar products.

#### **Features**

- PWM current control (fixed off time scheme)

- Digital load current selection function

- Sustained output voltage: 45V

- Built-in thermal shutdown circuit

#### **Specifications**

**Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol              | Conditions                          | Ratings                 | Unit |

|-----------------------------|---------------------|-------------------------------------|-------------------------|------|

| Motor supply voltage        | V <sub>BB</sub> max |                                     | 45                      | ٧    |

| Peak output current         | I <sub>O</sub> peak | tW ≤ 20μs                           | 1.75                    | Α    |

| Continuous output current   | I <sub>O</sub> max  |                                     | 1.5                     | Α    |

| Logic block supply voltage  | v <sub>CC</sub>     |                                     | 7.0                     | V    |

| Logic input voltage range   | V <sub>IN</sub>     |                                     | -0.3 to V <sub>CC</sub> | ٧    |

| Emitter output voltage      | ٧E                  |                                     | 1.0                     | V    |

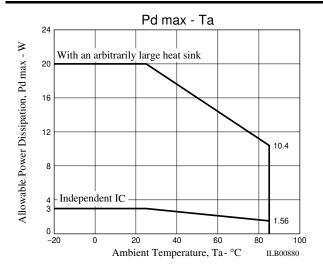

| Allowable power dissipation | Pd max1             | Independent IC                      | 3.0                     | W    |

|                             | Pd max2             | With an arbitrarily large heat sink | 20.0                    | W    |

| Operating temperature       | Topr                |                                     | -20 to +85              | °C   |

| Storage temperature         | Tstg                |                                     | -55 to +150             | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## **Recommended Operating Ranges** at $Ta = 25^{\circ}C$

| Parameter                  | Symbol           | Conditions | Ratings      | Unit |

|----------------------------|------------------|------------|--------------|------|

| Motor supply voltage       | V <sub>BB</sub>  |            | 10 to 44.5   | ٧    |

| Logic block supply voltage | v <sub>CC</sub>  |            | 4.75 to 5.25 | V    |

| Reference voltage          | V <sub>REF</sub> |            | 1.5 to 7.5   | V    |

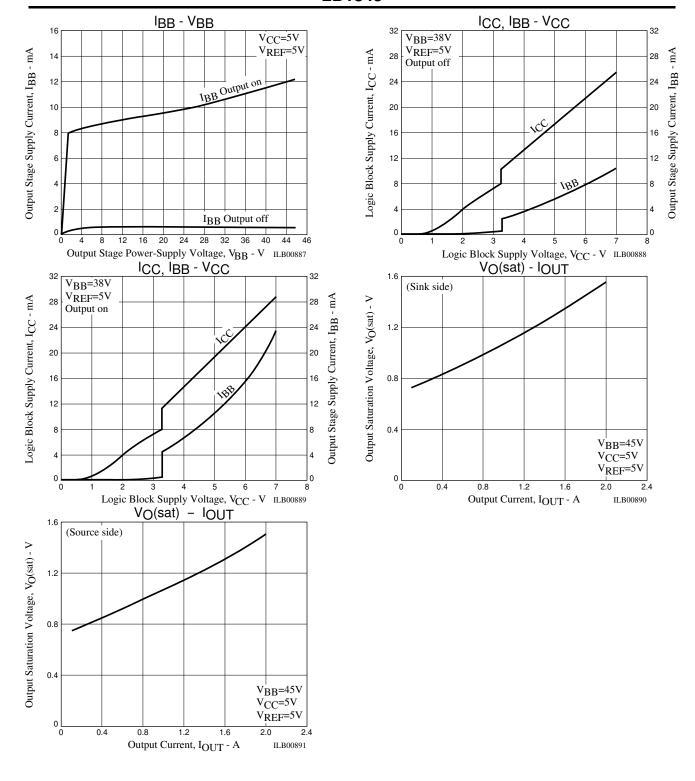

## **Electrical Characteristics** at Ta = 25°C, $V_{BB} = 38V$ , $V_{CC} = 5V$ , $V_{REF} = 5V$

| Dorometer                         | Cumbal                               | Conditions                                   |      | Ratings   |      |      |  |

|-----------------------------------|--------------------------------------|----------------------------------------------|------|-----------|------|------|--|

| Parameter                         | Symbol                               | Conditions                                   | min  | typ       | max  | unit |  |

| [Output Block]                    |                                      |                                              |      |           |      |      |  |

| Output stage supply current       | I <sub>BB</sub> ON                   |                                              |      | 12        | 16   | A    |  |

|                                   | I <sub>BB</sub> OFF                  |                                              |      | 0.7       | 0.9  | mA   |  |

| Output saturation voltage 1       | V <sub>O</sub> (sat)1                | I <sub>O</sub> = +1.0A Sink                  |      | 1.2       | 1.4  |      |  |

|                                   | V <sub>O</sub> (sat)2                | I <sub>O</sub> = +1.5A Sink                  |      | 1.4       | 1.7  |      |  |

|                                   | V <sub>O</sub> (sat)3                | I <sub>O</sub> = -1.0A Source                |      | 1.1       | 1.3  | V    |  |

|                                   | V <sub>O</sub> (sat)4                | I <sub>O</sub> = -1.5A Source                |      | 1.3       | 1.6  |      |  |

| Output leakage current            | I <sub>O</sub> (leak)1               | V <sub>O</sub> = V <sub>BB</sub> Sink        |      |           | 50   | μΑ   |  |

|                                   | I <sub>O</sub> (leak)2               | V <sub>O</sub> = 0V Source                   | -50  |           |      |      |  |

| Sustained output voltage          | V(sus)                               | *                                            | 45   |           |      | V    |  |

| [Logic Block]                     |                                      |                                              |      |           |      |      |  |

| Logic supply current              | I <sub>CC</sub> ON                   | $I_0 = 0.8V, I_1 = 0.8V$                     |      | 19.5 25.3 |      | A    |  |

|                                   | I <sub>CC</sub> OFF                  | I <sub>0</sub> = 2.4V, I <sub>1</sub> = 2.4V |      | 15.5      | 20.1 | mA   |  |

| Input voltage                     | V <sub>IH</sub>                      |                                              | 2.4  |           |      |      |  |

|                                   | $v_{IL}$                             |                                              |      |           | 8.0  | V    |  |

| Input current                     | lн                                   | V <sub>IH</sub> = 2.4V                       |      |           | 10   |      |  |

|                                   | I <sub>IL</sub>                      | V <sub>IL</sub> = 0.8V                       | -10  |           |      | μΑ   |  |

| Current control threshold voltage | V <sub>REF</sub> /V <sub>SENSE</sub> | $I_0 = 0.8V, I_1 = 0.8V$                     | 9.5  | 10        | 10.5 |      |  |

|                                   |                                      | I <sub>0</sub> = 2.4V, I <sub>1</sub> = 0.8V | 13.5 | 15        | 16.5 |      |  |

|                                   |                                      | I <sub>0</sub> = 0.8V, I <sub>1</sub> = 2.4V | 25.5 | 30        | 34.5 |      |  |

| Thermal shutdown temperature      | T <sub>S</sub>                       |                                              |      | 170       |      | °C   |  |

<sup>\*</sup> Note: Design guaranteed value.

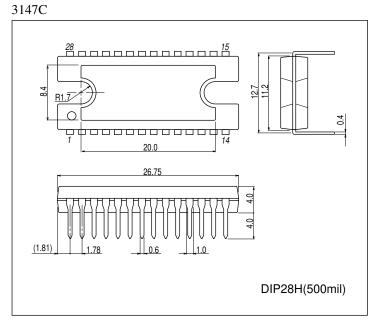

## **Package Dimensions**

unit: mm (typ)

## **Truth Table**

| ENABLE | PHASE | OUTA | OUTB |

|--------|-------|------|------|

| L      | Н     | Н    | L    |

| L      | L     | L    | Н    |

| Н      | -     | OFF  | OFF  |

| 10 | I <sub>1</sub> | Output Current                               |

|----|----------------|----------------------------------------------|

| L  | L              | $V_{REF}/(10\times R_{E}) = I_{OUT}$         |

| Н  | L              | $V_{REF}/(15\times R_E) = I_{OUT}\times 2/3$ |

| L  | Н              | $V_{REF}/(30\times R_E) = I_{OUT}\times 1/3$ |

| Н  | Н              | 0                                            |

Note: Outputs is OFF when ENABLE is high or in the  $I_0 = I_1 = high$  state.

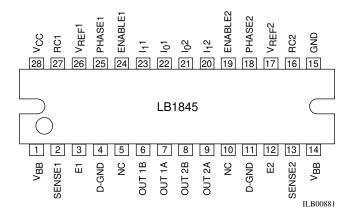

## **Pin Assignment**

## **Block Diagram**

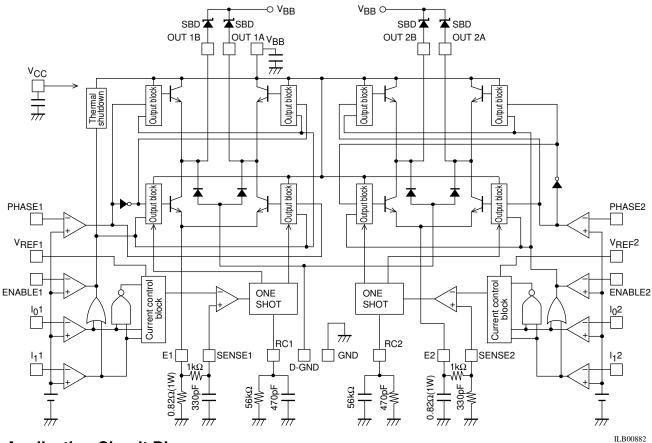

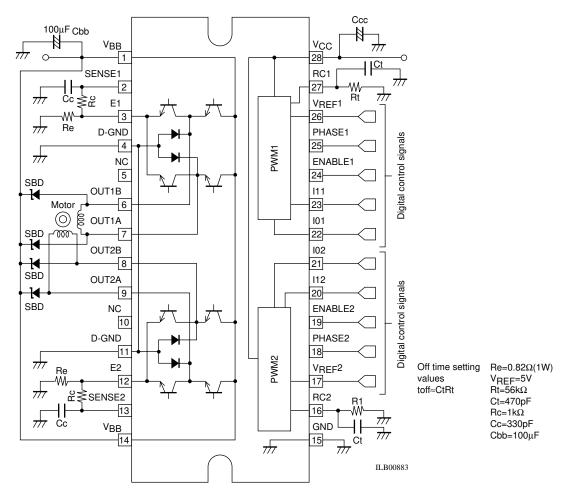

## **Application Circuit Diagram**

## **Pin Description**

| Pin No | Pin                                | Function                                                                                                                      |

|--------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1, 14  | V <sub>BB</sub>                    | Output stage power-supply voltage                                                                                             |

| 2      | SENSE1                             | Set current detection pins.                                                                                                   |

| 13     | SENSE2                             | Connect these pins, fed back through noise filters, to E1 and E2.                                                             |

| 3      | E1                                 | The set current is controlled by the resistors Re inserted between these pins and ground.                                     |

| 12     | E2                                 |                                                                                                                               |

| 4, 11  | D-GND                              | Internal diode anode connection                                                                                               |

| 6      | OUT1B                              | Outputs                                                                                                                       |

| 7      | OUT1A                              |                                                                                                                               |

| 8      | OUT2B                              |                                                                                                                               |

| 9      | OUT2A                              |                                                                                                                               |

| 15     | GND                                | Ground                                                                                                                        |

| 27     | RC1                                | Used to set the output off time for the switched output signal.                                                               |

| 16     | RC2                                | The fixed off times are set by the capacitors and resistors connected to these pins. toff = CR.                               |

| 26     | V <sub>REF</sub> 1                 | Output current settings                                                                                                       |

| 17     | V <sub>REF</sub> 2                 | The output current is determined by the voltage (in the range 1.5 to 7.5V) input to these pins.                               |

| 25     | PHASE1                             | Output phase switching inputs.                                                                                                |

| 18     | PHASE2                             | High-level input: OUTA = high, OUTB = low                                                                                     |

|        |                                    | Low-level input: OUTA = low, OUTB = high                                                                                      |

| 24     | ENABLE1                            | Output on/off settings                                                                                                        |

| 19     | ENABLE2                            | High-level input: output off                                                                                                  |

|        |                                    | Low-level input: output on                                                                                                    |

| 22, 23 | l <sub>0</sub> 1, l <sub>1</sub> 1 | Digital inputs that set the output current                                                                                    |

| 21, 20 | I <sub>0</sub> 2, I <sub>1</sub> 2 | The output currents can be set to 1/3, 2/3, or full by setting these pins to appropriate combinations of high and low levels. |

| 28     | V <sub>CC</sub>                    | Logic block power supply                                                                                                      |

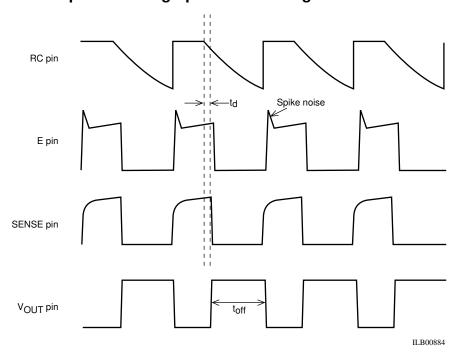

## Timing chart for pin switching operations during PWM drive

Figure 1 Switching Waveforms

$t_{off}$ : Output off time. Determined by external capacitor and resistor Ct and Rt. (toff  $\approx$  Ct  $\times$  Rt)  $t_{d}$ : Delay time between the point the set current is sensed at the SENSE pin and the point the output turns off.

#### **Usage Notes**

#### 1. External diode

Since this IC adopts a system based on lower side transistor switching drive, an external diode for the regenerative current that occurs during switching is required between  $V_{BB}$  and  $V_{OUT}$ . Use a Schottky barrier diode with a low feedthrough current.

#### 2. Noise filters

Since spike noise (see Figure 1) occurs when switching to the on state due to the external diode's feedthrough current, applications must remove noise from the SENSE pin with a noise filter (Cc, Rc) between the E pin and the SENSE pin.

However, note that if the values of Cc and Rc are too large, the SENSE voltage rise will be slowed, and the current setting will be shifted towards a higher current level.

#### 3. VREF pin

It is possible to change the output current continuously by continuously changing the  $V_{REF}$  pin voltage. However, this voltage cannot be set to 0V. The  $V_{REF}$  pin input impedance is  $26k\Omega$  ( $\pm30\%$ ) when  $V_{REF}$  is 5V. Since this pin is used to set the output current, applications must be designed so that noise does not appear on this pin's input.

#### 4. GND pin

Since this IC switches large currents, care must be taken to avoid ground loops when the IC is mounted in the application. The section of the PCB that handles large currents should be designed with a low-impedance pattern, and must be separated from the small signal sections of the circuit. In particular, the ground for the sense resistor Re must be as close as possible to the IC ground.

#### 5. Operation in hold mode

There are cases where a current somewhat larger than the current setting may flow in hold mode (light load mode). Since this IC adopts a lower side switching, lower side sense system, the emitter voltage falls and the sense voltage goes to 0 when the switching state goes to off. The circuit then always turns the output on after the toff period has elapsed. At this time, due to the light load, the existence of the time td, and the fact that the output goes on even if the output current is higher than the set current, the output current will be somewhat higher than the set current. Applications should set the current setting somewhat lower than required if this occurs.

6. Function for preventing the upper and lower outputs being on at the same time

This IC incorporates a built-in circuit that prevents the through currents that occur when the phase is switched. The table lists the output on and off delay times when PHASE and EANBLE are switched.

|                        |                | Sink side | Source side |

|------------------------|----------------|-----------|-------------|

| When PHASE is switched | On delay time  | 10μs      | 9μs         |

|                        | Off delay time | 1.5µs     | 3μs         |

| When ENABLE is on      | On delay time  | 9μs       | 9μs         |

|                        | Off delay time | 1.5µs     | 6.5µs       |

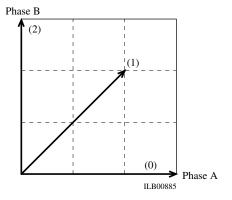

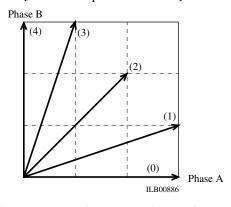

#### 7. 1-2 phase excitation and the double 1-2 phase excitation control sequence

To reduce the vibration that occurs when the motor turns, this IC supports 1-2 phase excitation and double 1-2 phase excitation by using the output current setting digital input pins  $I_0$  and  $I_1$  without changing the  $V_{REF}$  pin voltage. Tables 1 and 2 list that control sequence, and Figure 2 and Figure 3 present the composite vector diagram for this sequence.2. Noise filters

## Table 1 [1-2 phase excitation] 1/2 Step

#### ENABLE1 = ENABLE2 = 0

|    | Phase A |                  |                  |                  | Phase B |                  |                  |                  |

|----|---------|------------------|------------------|------------------|---------|------------------|------------------|------------------|

| No | PH1     | l <sub>1</sub> 1 | I <sub>0</sub> 1 | Current<br>Value | PH2     | I <sub>1</sub> 2 | I <sub>0</sub> 2 | Current<br>Value |

| 0  | 0       | 0                | 0                | 1                | *       | 1                | 1                | 0                |

| 1  | 0       | 0                | 1                | 2/3              | 0       | 0                | 1                | 2/3              |

| 2  | *       | 1                | 1                | 0                | 0       | 0                | 0                | 1                |

| 3  | 1       | 0                | 1                | 2/3              | 0       | 0                | 1                | 2/3              |

| 4  | 1       | 0                | 0                | 1                | *       | 1                | 1                | 0                |

| 5  | 1       | 0                | 1                | 2/3              | 1       | 0                | 1                | 2/3              |

| 6  | *       | 1                | 1                | 0                | 1       | 0                | 0                | 1                |

| 7  | 0       | 0                | 1                | 2/3              | 1       | 0                | 1                | 2/3              |

## Table 2 [Double 1-2 phase excitation] about 1/4 Step

ENABLE1 = ENABLE2 = 0

|    | Phase A |                  |                  |                  |     | Phase B          |                  |                  |

|----|---------|------------------|------------------|------------------|-----|------------------|------------------|------------------|

| No | PH1     | l <sub>1</sub> 1 | I <sub>0</sub> 1 | Current<br>Value | PH2 | I <sub>1</sub> 2 | 1 <sub>0</sub> 2 | Current<br>Value |

| 0  | 0       | 0                | 0                | 1                | *   | 1                | 1                | 0                |

| 1  | 0       | 0                | 0                | 1                | 0   | 1                | 0                | 1/3              |

| 2  | 0       | 0                | 1                | 2/3              | 0   | 0                | 1                | 2/3              |

| 3  | 0       | 1                | 0                | 1/3              | 0   | 0                | 0                | 1                |

| 4  | *       | 1                | 1                | 0                | 0   | 0                | 0                | 1                |

| 5  | 1       | 1                | 0                | 1/3              | 0   | 0                | 0                | 1                |

| 6  | 1       | 0                | 1                | 2/3              | 0   | 0                | 1                | 2/3              |

| 7  | 1       | 0                | 0                | 1                | 0   | 1                | 0                | 1/3              |

| 8  | 1       | 0                | 0                | 1                | *   | 1                | 1                | 0                |

| 9  | 1       | 0                | 0                | 1                | 1   | 1                | 0                | 1/3              |

| 10 | 1       | 0                | 1                | 2/3              | 1   | 0                | 1                | 2/3              |

| 11 | 1       | 1                | 0                | 1/3              | 1   | 0                | 0                | 1                |

| 12 | *       | 1                | 1                | 0                | 1   | 0                | 0                | 1                |

| 13 | 0       | 1                | 0                | 1/3              | 1   | 0                | 0                | 1                |

| 14 | 0       | 0                | 1                | 2/3              | 1   | 0                | 1                | 2/3              |

| 15 | 0       | 0                | 0                | 1                | 1   | 1                | 0                | 1/3              |

## **Composite Vector Diagram**

[1-2 phase excitation]

Figure 2 Composite Vector Diagram for the Sequence in Table 1 (1/4 cycle)

[Double 1-2 phase excitation]

Figure 3 Composite Vector Diagram for the Sequence in Table 2 (1/4 cycle)

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa