# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 1/8 to 1/16 Duty Dot Matrix LCD **Controller Driver**

#### www.onsemi.com

#### **Overview**

The LC450210PCH is the 1/8 to 1/16 duty dot matrix LCD controller driver. By controlling this driver with a microcontroller, it is used in applications such as character display and simple graphic display etc. This driver can drive a LCD panel of up to 3,200 dots ( $16 \times 16$  dot font: 1-line display of up to 12 digits and 128 segments,  $5 \times 7$  dot font: 2-line display of up to 40 digits). The operating temperature range is from -40 to  $+105^{\circ}$ C.

#### **Features**

1. Selectable duty ratio by serial data: 1/8 duty to 1/16 duty

| $1/8$ duty: $8 \times 200 = 1,600$ dots   | $1/11$ duty: $11 \times 200 = 2,200$ dots | $1/14$ duty: $14 \times 200 = 2,800$ dots |

|-------------------------------------------|-------------------------------------------|-------------------------------------------|

| $1/9$ duty: $9 \times 200 = 1,800$ dots   | $1/12$ duty: $12 \times 200 = 2,400$ dots | $1/15$ duty: $15 \times 200 = 3,000$ dots |

| $1/10$ duty: $10 \times 200 = 2,000$ dots | $1/13$ duty: $13 \times 200 = 2,600$ dots | $1/16$ duty: $16 \times 200 = 3,200$ dots |

- 2. Selectable LCD bias voltage ratio by serial data: 1/4 bias or 1/5 bias

- 3. Selectable inversion drive of LCD drive waveform by serial data: line inversion or frame inversion

- 4. Adjustable frame frequency of common and segment output waveforms and clock frequency of voltage booster by serial data, for preventing interference with the frequency of the backlight.

- 5. Selectable operation modes by serial data: power-saving mode (maintains display data),

the state of display (ON, all ON, all OFF, all forced OFF)

- 6. Built-in oscillator circuit (built-in resistor and capacitor for oscillation)

- 7. Selectable fundamental clock operating modes by serial data: internal oscillator operating mode or external clock operating mode

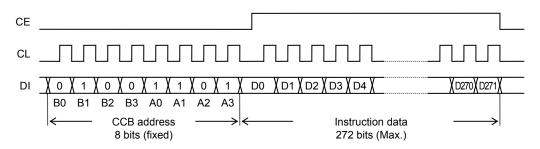

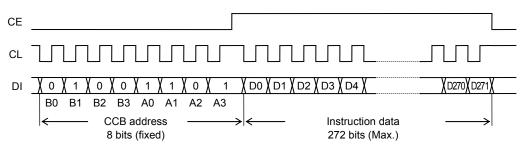

- 8. Input of serial data supports CCB\* format (for 5 V and 3 V)

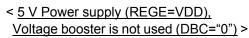

- 9. Selectable voltage range of power supply for logic block by setting REGE pad

(VDD): +4.5 V to +5.5 V (5 V power supply (REGE = VDD))

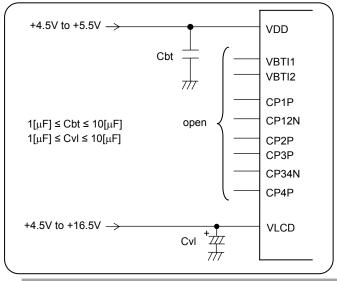

- +2.7 V to +3.6 V (3 V power supply (REGE = VSS))

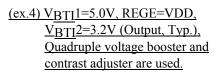

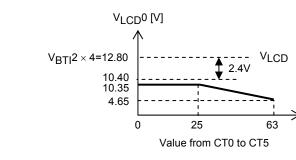

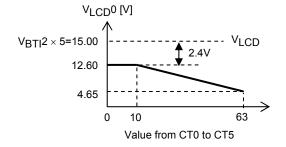

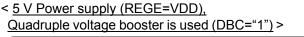

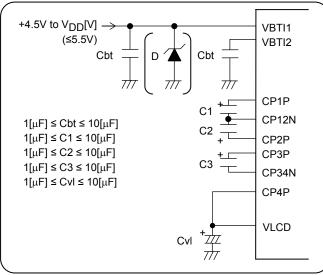

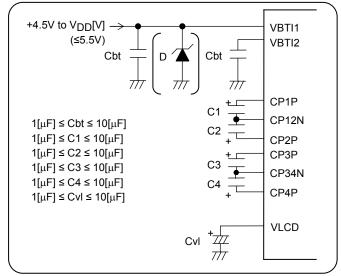

- 10. Built-in quadruple and quintuple voltage booster with discharge function Base voltage of boosting (VBTI2): +3.2 V (Typ.)

- (5 V power supply (REGE = VDD))  $(V_{BTI} = V_{BTI} = V_{ETI})$ : +2.7 V to  $V_{DD}[V]$  (3 V power supply (REGE = VSS))

- 11. Power supply for LCD driver block (V<sub>LCD</sub>): +16.0 V (Typ.)  $(V_{DD} = 5 V, Quintuple voltage booster is used.)$  $(V_{DD} = 3.3 \text{ V}, \text{Quintuple voltage booster is used.})$

- +16.5 V +4.5 V to +16.5 V (range with external power supply)

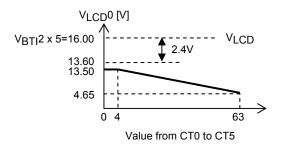

#### 12. Built-in contrast adjuster

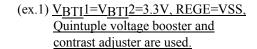

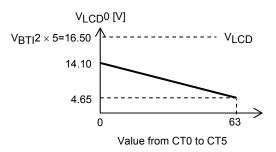

LCD drive bias voltage ( $V_{LCD0}$ ): +4.65 V to +13.5 V (Typ.) ( $V_{DD}$  = 5 V, Quintuple voltage booster is used.)

- +4.65 V to +14.1 V  $(V_{DD} = 3.3 V, Quintuple voltage booster is used.)$ +4.65 V to +14.1 V

- $(V_{LCD} = 16.5 V \text{ with external power supply})$

- 13. The initialization of this driver and the prevention of an unintended display are controllable by setting  $\overline{\text{RES}}$  pad.

14. Wide range of operating temperature: -40 to +105°C

15. CMOS process and chip with Au bumps

\* Computer Control Bus (CCB) is an ON Semiconductor's original bus format and the bus addresses are controlled by ON Semiconductor.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 53 of this data sheet.

### Specifications Absolute Maximum Ratings at Ta = 25°C, V<sub>SS</sub> = 0 V

| Parameter              | Symbol               | Conditions                                                                                                                                  | Ratings                        | Uni |

|------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----|

|                        |                      | VDD,<br>REGE = VDD                                                                                                                          | –0.3 to +6.0                   |     |

| Supply voltage         | V <sub>DD</sub> max  | VDD,<br>REGE = VSS                                                                                                                          | -0.3 to +4.2                   | V   |

|                        | V <sub>LCD</sub> max | VLCD (Note.1)                                                                                                                               | -0.3 to +17.0                  | 1   |

|                        |                      | CE, CL, DI, RES, TSIN1 to TSIN4, OSCI                                                                                                       | -0.3 to +4.2                   |     |

|                        | V <sub>IN</sub> 1    | CE, CL, DI, $\overline{\text{RES}}$ , TSIN1 to TSIN4, OSCI,<br>Supply more than 2.7 V to V <sub>DD</sub> before V <sub>IN</sub> 1 is input. | -0.3 to +6.0                   |     |

| Input voltage          | V <sub>IN</sub> 2    | VBTI1                                                                                                                                       | –0.3 to V <sub>DD</sub> +0.3   | V   |

|                        | V <sub>IN</sub> 3    | REGE                                                                                                                                        | -0.3 to +6.0                   | ]   |

|                        | V <sub>IN</sub> 4    | VLCD5 (Note.1)                                                                                                                              | –0.3 to V <sub>LCD</sub> +0.3  | 1   |

|                        | VOUT1                | VLCD                                                                                                                                        | –0.3 to V <sub>LCD</sub> +0.3  |     |

|                        | V <sub>OUT</sub> 2   | S1 to S200, COM1 to COM16                                                                                                                   | –0.3 to V <sub>LCD</sub> +0.3  |     |

| Output voltage         | V <sub>OUT</sub> 3   | CP12N, CP34N, VLOGIC, TSOUT1 to TSOUT3, TSO, $V_{DD} \leq 3.9V$ (REGE=VSS)                                                                  | –0.3 to V <sub>DD</sub> +0.3   | V   |

|                        |                      | CP12N, CP34N, VLOGIC, TSOUT1 to TSOUT3, TSO,<br>V <sub>DD</sub> > 3.9V (REGE=VDD)                                                           | -0.3 to +4.2                   |     |

|                        | VINOUT1              | CP1P, CP2P, CP3P, CP4P                                                                                                                      | –0.3 to V <sub>LCD</sub> +0.3  |     |

|                        | VINOUT2              | VLCD0, VLCD1, VLCD2, VLCD3, VLCD4 (Note.1)                                                                                                  | –0.3 to V <sub>LCD</sub> +0.3  | 1   |

| Input / Output voltage | VINOUT <sup>3</sup>  | VBTI2,<br>V <sub>BTI</sub> 1 ≤ 3.9 V (REGE = VSS)                                                                                           | –0.3 to V <sub>BTI</sub> 1+0.3 | v   |

|                        |                      | VBTI2,<br>V <sub>BTI</sub> 1 > 3.9 V (REGE = VDD)                                                                                           | -0.3 to +4.2                   |     |

|                        | IOUT1                | VLCD                                                                                                                                        | 8                              |     |

| Output current         | I <sub>OUT</sub> 2   | S1 to S200                                                                                                                                  | 0.3                            | m/  |

|                        | IOUT3                | COM1 to COM16                                                                                                                               | 1                              |     |

| Operating temperature  | Topr                 |                                                                                                                                             | -40 to +105                    | °C  |

| Storage temperature    | Tstg                 |                                                                                                                                             | –55 to +125                    | °C  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed,

damage may occur and reliability may be affected.

| Parameter                                                | Symbol                                                                               | Conditions                                                                                                      |                   |                    | Ratings       |                               | Uni  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|--------------------|---------------|-------------------------------|------|

|                                                          | Cymbol                                                                               |                                                                                                                 |                   | Min.               | Тур.          | Max.                          | 0.11 |

|                                                          | V <sub>DD</sub>                                                                      | VDD,<br>REGE = VDD                                                                                              |                   | 4.5                |               | 5.5                           |      |

| Supply voltage                                           | UU•                                                                                  | VDD,<br>REGE = VSS                                                                                              |                   | 2.7                |               | 3.6                           | V    |

|                                                          | V <sub>LCD</sub>                                                                     | VLCD,<br>When VLCD is supplied from the                                                                         | e outside.        | 4.5                |               | 16.5                          |      |

|                                                          | V <sub>BTI</sub> 1                                                                   | VBTI1,<br>V <sub>DD</sub> = 4.5 V to 5.5 V (REGE = V<br>Quadruple/Quintuple voltage bo                          |                   | 4.5                |               | V <sub>DD</sub>               | V    |

| Input base voltage for<br>voltage booster                | )/2                                                                                  | VBTI1, VBTI2 (VBTI1 = VBTI2),<br>V <sub>DD</sub> = 2.7 V to 3.6 V (REGE = V<br>Quadruple voltage booster is us  |                   | 2.7                |               | V <sub>DD</sub><br>(≤ 3.6)    | V    |

|                                                          | V <sub>BTI</sub> 2                                                                   | VBTI1, VBTI2 (VBTI1 = VBTI2),<br>V <sub>DD</sub> = 2.7 V to 3.3 V (REGE = V<br>Quintuple voltage booster is use | /SS),             | 2.7                |               | V <sub>DD</sub><br>(≤ 3.3)    | V    |

|                                                          | V <sub>LCD</sub> 0                                                                   | VLCD0,<br>Contrast adjuster is not used.                                                                        |                   | 4.5<br>(Note. 1)   | (Note. 1)     | V <sub>LCD</sub><br>(Note. 1) | V    |

| Input voltage for LCD<br>drive bias voltage<br>generator | V <sub>LCD</sub> 1<br>V <sub>LCD</sub> 2<br>V <sub>LCD</sub> 3<br>V <sub>LCD</sub> 4 | VLCD1, VLCD2, VLCD3, VLCD4<br>LCD drive bias voltage generato                                                   |                   |                    | (Note.1)      |                               | V    |

|                                                          | V <sub>LCD</sub> 5                                                                   | VLCD5                                                                                                           |                   |                    | 0<br>(Note.1) |                               | V    |

|                                                          | V/                                                                                   | CE, CL, DI, <del>RES</del> , OSCI<br>V <sub>DD</sub> = 4.5 V to 5.5 V (REGE = V                                 | /DD)              | 0.5V <sub>DD</sub> |               | 5.5                           |      |

| Input High-level<br>voltage                              | V <sub>IH</sub> 1                                                                    | CE, CL, DI, <u>RES</u> , OSCI<br>V <sub>DD</sub> = 2.7 V to 3.6 V (REGE = V                                     | /SS)              | 0.8V <sub>DD</sub> |               | 3.6                           | V    |

|                                                          | V <sub>IH</sub> 2                                                                    | REGE                                                                                                            |                   | 0.8V <sub>DD</sub> |               | 5.5                           |      |

|                                                          |                                                                                      | CE, CL, DI, $\overline{\text{RES}}$ , TSIN1 to TSIN<br>V <sub>DD</sub> = 4.5 V to 5.5 V (REGE = V               |                   | 0                  |               | 0.2V <sub>DD</sub>            |      |

| Input Low-level voltage                                  | V <sub>IL</sub> 1                                                                    | CE, CL, DI, RES, TSIN1 to TSIN<br>VDD = 2.7 V to 3.6 V (REGE = V                                                |                   | 0                  |               | 0.2V <sub>DD</sub>            | V    |

|                                                          | V <sub>IL</sub> 2                                                                    | REGE                                                                                                            |                   | 0                  |               | 0.2V <sub>DD</sub>            |      |

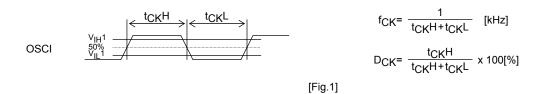

| External clock<br>input frequency                        | fCK                                                                                  | OSCI,<br>External clock operating mode                                                                          | Fig.1]            | 100                | 300           | 600                           | kH   |

| External clock duty                                      | DCK                                                                                  | OSCI,<br>External clock operating mode                                                                          | Fig.1]            | 30                 | 50            | 70                            | %    |

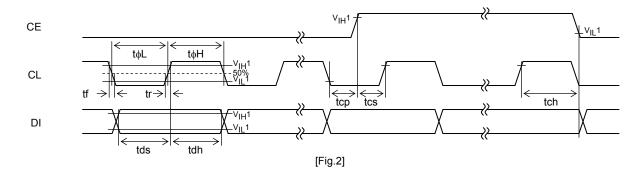

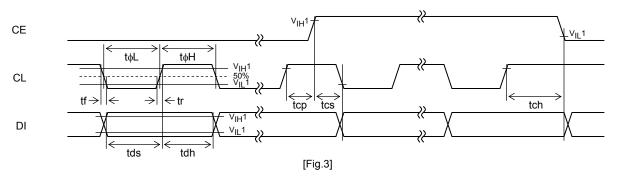

| Data setup time                                          | tds                                                                                  | CL, DI                                                                                                          | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| Data hold time                                           | tdh                                                                                  | CL, DI                                                                                                          | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| CE wait time                                             | tcp                                                                                  | CE, CL                                                                                                          | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| CE setup time                                            | tcs                                                                                  | CE, CL                                                                                                          | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| CE hold time                                             | tch                                                                                  | CE, CL                                                                                                          | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| High-level<br>clock pulse width                          | t∳H                                                                                  | CL                                                                                                              | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| Low-level<br>clock pulse width                           | tφL                                                                                  | CL                                                                                                              | Fig.2], [Fig.3]   | 160                |               |                               | ns   |

| Rise time                                                | tr                                                                                   | CE, CL, DI                                                                                                      | Fig.2], [Fig.3]   |                    | 160           |                               | ns   |

| Fall time                                                | tf                                                                                   | CE, CL, DI                                                                                                      | Fig.2], [Fig.3]   |                    | 160           |                               | ns   |

| Reset pulse<br>minimum width                             | twres                                                                                | RES                                                                                                             | Fig.5] to [Fig.8] | 1.0                |               |                               | ms   |

(Note.1) Follow a condition of  $V_{LCD} \ge V_{LCD} 0 > V_{LCD} 1 > V_{LCD} 2 > V_{LCD} 3 > V_{LCD} 4 > V_{LCD} 5$ .

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## Electrical Characteristics in the Allowable Operating Ranges

| Parameter                  | Symbol             | PAD                     | Conditions                                                                                           |                        | Ratings              |                        | Unit |

|----------------------------|--------------------|-------------------------|------------------------------------------------------------------------------------------------------|------------------------|----------------------|------------------------|------|

|                            | Cynlool            | שרי י                   |                                                                                                      | Min.                   | Тур.                 | Max.                   | Jint |

|                            |                    | CE, CL, DI,             | V <sub>DD</sub> = 4.5 V to 5.5 V (REGE = VDD)                                                        |                        | 0.03V <sub>DD</sub>  |                        |      |

| Hysteresis                 | VH                 | RES, OSCI               | V <sub>DD</sub> = 2.7 V to 3.6 V (REGE = VSS)                                                        |                        | 0.05V <sub>DD</sub>  |                        | V    |

|                            |                    |                         |                                                                                                      |                        |                      | 5.0                    |      |

|                            |                    | CE, CL, DI,             | V <sub>I</sub> = 3.6 V                                                                               |                        |                      | 5.0                    |      |

| Input High-level           | IIH1               | RES, OSCI               | $V_{\rm I} = 5.5 V$ ,                                                                                |                        |                      | 5.0                    | μA   |

| current                    |                    |                         | Supply more than 2.7 V to V <sub>DD</sub> before V <sub>I</sub> is input.                            |                        |                      |                        |      |

|                            | I <sub>IH</sub> 2  | REGE                    | V <sub>I</sub> = 5.5 V                                                                               |                        |                      | 5.0                    |      |

|                            |                    | CE, CL, DI,             |                                                                                                      |                        |                      |                        |      |

| Input Low-level<br>current | I <sub>IL</sub> 1  | RES,<br>TSIN1 to TSIN4, | $V_{I} = 0 V$                                                                                        | -5.0                   |                      |                        | μA   |

| current                    |                    | REGE, OSCI              |                                                                                                      |                        |                      |                        |      |

|                            |                    |                         | V <sub>DD</sub> = 5.5 V, V <sub>BTI</sub> 1 = 5.5 V, REGE = VDD,                                     |                        |                      |                        |      |

|                            |                    |                         | Quadruple voltage booster is used.                                                                   |                        |                      |                        |      |

|                            |                    |                         | Contrast adjuster is used.                                                                           |                        | 0.050                | 4 400                  |      |

|                            |                    |                         | LCD drive bias voltage generator is used.                                                            |                        | 2,050                | 4,100                  |      |

|                            |                    |                         | Common and segment outputs are open.                                                                 |                        |                      |                        |      |

|                            | IBTI1              | VBTI1                   | display on (normal display)                                                                          |                        |                      |                        |      |

|                            | вп                 | VBIII                   | V <sub>DD</sub> = 5.5 V, V <sub>BTI</sub> 1 = 5.5 V, REGE = VDD,                                     |                        |                      |                        |      |

|                            |                    |                         | Quintuple voltage booster is used.                                                                   |                        |                      |                        |      |

|                            |                    |                         | Contrast adjuster is used.                                                                           |                        | 2,550                | 5,100                  |      |

|                            |                    |                         | LCD drive bias voltage generator is used.                                                            |                        |                      |                        |      |

|                            |                    |                         | Common and segment outputs are open.<br>display on (normal display)                                  |                        |                      |                        |      |

| Input current for          |                    |                         | $V_{DD} = 3.6 \text{ V}, \text{ V}_{BTI} 1 = \text{ V}_{BTI} 2 = 3.6 \text{ V},$                     |                        |                      |                        | ł    |

| voltage booster            |                    |                         | REGE = VSS,                                                                                          |                        |                      |                        | μA   |

| 0                          |                    |                         | Quadruple voltage booster is used.                                                                   |                        |                      |                        |      |

|                            |                    |                         | Contrast adjuster is used.                                                                           |                        | 2,000                | 4,000                  |      |

|                            |                    |                         | LCD drive bias voltage generator is used.                                                            |                        |                      |                        |      |

|                            |                    |                         | Common and segment outputs are open.                                                                 |                        |                      |                        |      |

|                            | IBTI2              | VBTI2                   | display on (normal display)                                                                          |                        |                      |                        |      |

|                            | ·B11–              | V D H Z                 | V <sub>DD</sub> = 3.3 V, V <sub>BTI</sub> 1 = V <sub>BTI</sub> 2 = 3.3 V,                            |                        |                      |                        |      |

|                            |                    |                         | REGE = VSS,                                                                                          |                        |                      |                        |      |

|                            |                    |                         | Quintuple voltage booster is used.<br>Contrast adjuster is used.                                     |                        | 2,500                | 5,000                  |      |

|                            |                    |                         | LCD drive bias voltage generator is used.                                                            |                        | 2,300                | 3,000                  |      |

|                            |                    |                         | Common and segment outputs are open.                                                                 |                        |                      |                        |      |

|                            |                    |                         | display on (normal display)                                                                          |                        |                      |                        |      |

| ON-resistance of           |                    |                         | $V_{LCD}$ = 4.5 V (with external supply),                                                            |                        |                      |                        |      |

| segment driver             | R <sub>ONS</sub>   | S1 to S200              | $V_{LCD}0 = 4.5 V$ (with external input),                                                            |                        |                      | 20                     | kΩ   |

| output                     | 0110               |                         | $V_{LCD}$ 1 to $V_{LCD}$ 5 = 1/5 bias (with external input)                                          |                        |                      |                        |      |

| ON-resistance of           |                    |                         | $V_{I,CD} = 4.5 V$ (with external supply),                                                           |                        |                      |                        |      |

| common driver              | RONC               | COM1 to COM16           | $V_{\rm I CD}$ = 4.5 V (with external supply),<br>V <sub>I CD</sub> 0 = 4.5 V (with external input), |                        |                      | 20                     | kΩ   |

| output                     | ONC                |                         | $V_{LCD}$ 1 to $V_{LCD}$ 5 = 1/5 bias (with external input)                                          |                        |                      |                        |      |

| •                          |                    |                         | V <sub>BTI</sub> 1 = 4.5 V to 5.5 V (REGE = VDD)                                                     |                        |                      |                        |      |

|                            |                    |                         | Voltage booster is used.                                                                             |                        |                      |                        |      |

|                            | V <sub>BTI</sub> 2 | VBTI2                   | Contrast adjuster is not used.                                                                       | 3.09                   | 3.2                  | 3.3                    |      |

|                            | 511                |                         | LCD drive bias voltage generator is not used.                                                        |                        |                      |                        |      |

|                            |                    |                         | No-load.                                                                                             |                        |                      |                        |      |

|                            |                    |                         | Quadruple voltage booster is used.                                                                   |                        |                      |                        |      |

| Output voltage             |                    |                         | Contrast adjuster is not used.                                                                       | (V <sub>BTI</sub> 2×4) | V <sub>BTI</sub> 2×4 | (V <sub>BTI</sub> 2×4) | V    |

|                            |                    |                         | LCD drive bias voltage generator is not used.                                                        | -0.4                   | · D    =···          | +0.4                   |      |

|                            | V <sub>LCD</sub>   | VLCD                    | No-load.                                                                                             |                        |                      |                        |      |

|                            | 200                |                         | Quintuple voltage booster is used.                                                                   |                        |                      |                        |      |

|                            |                    |                         | Contrast adjuster is not used.                                                                       | (V <sub>BTI</sub> 2×5) | V <sub>BTI</sub> 2×5 | 16.5                   |      |

|                            |                    |                         | LCD drive bias voltage generator is not used.<br>No-load.                                            | -0.4                   |                      |                        |      |

| Oscillator                 |                    | Internal clock          | No load.                                                                                             |                        |                      |                        |      |

|                            | fosc               |                         | Internal oscillator operating mode                                                                   | 210                    | 300                  | 390                    | kHz  |

Continued on next page.

#### Continued from preceding page.

| Descenter     | Ourseland.        | DAD  | 0                                                                                                                                                                                                                                                       |      | Ratings |       | 1.1  |

|---------------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|------|

| Parameter     | Symbol            | PAD  | Conditions                                                                                                                                                                                                                                              | Min. | Тур.    | Max.  | Unit |

|               |                   |      | <power-saving mode=""><br/>V<sub>DD</sub> = 3.6 V (REGE = VSS),<br/>communication inactive,<br/>Input level is V<sub>SS</sub> or V<sub>DD</sub>.</power-saving>                                                                                         |      |         | 15    |      |

|               | I <sub>DD</sub> 1 | VDD  | < Power-saving mode ><br>V <sub>DD</sub> = 5.5 V (REGE = VDD),<br>communication inactive,<br>Input level is V <sub>SS</sub> or V <sub>DD</sub> .                                                                                                        |      | 50      | 120   |      |

| Power current |                   | ~    | <normal mode=""><br/>V<sub>DD</sub> = 3.6 V (REGE = VSS),<br/>display on (normal display),<br/>internal oscillator operating mode,<br/>communication inactive,<br/>Input level is V<sub>SS</sub> or V<sub>DD</sub>.</normal>                            |      | 100     | 500   | μΑ   |

|               | IDD2              | VDD  | < Normal mode ><br>V <sub>DD</sub> = 5.5 V (REGE = VDD),<br>display on (normal display),<br>internal oscillator operating mode,<br>communication inactive,<br>Input level is V <sub>SS</sub> or V <sub>DD</sub> .                                       |      | 150     | 600   |      |

|               | ILCD              | VLCD | < Normal mode ><br>V <sub>LCD</sub> = 16.5 V (with external supply),<br>display on (normal display),<br>Voltage booster is not used.<br>Contrast adjuster is used.<br>LCD drive bias voltage generator is used.<br>Common and segment outputs are open. |      | 500     | 1,000 |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

(1) Clock timing of OSCI pad in the external clock operating mode

#### (2) When CL is stopped at the low level

#### (3) When CL is stopped at the high level

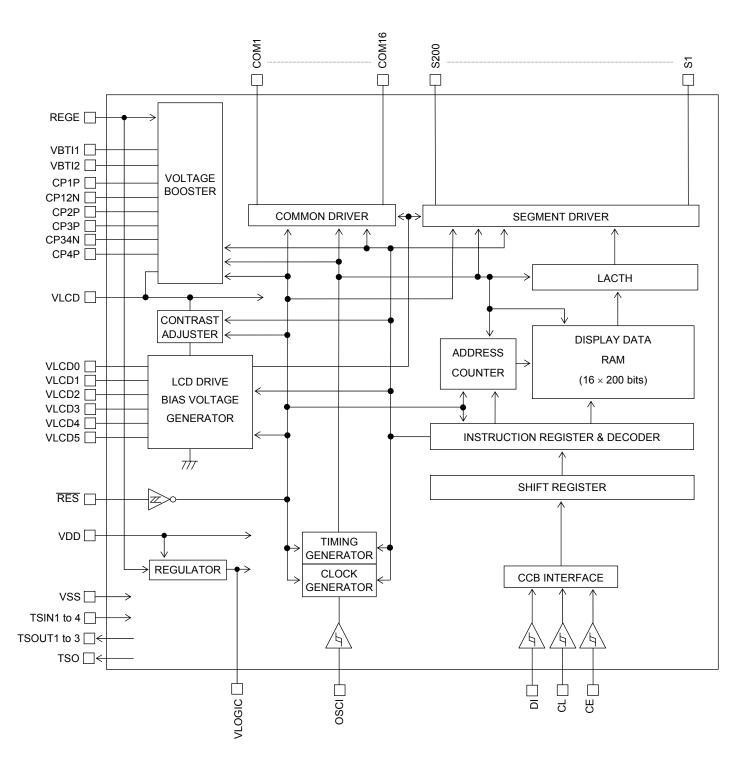

**Block Diagram**

#### **Pad Functions**

| Pad Name                                              | Pad No.                                                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Active | I/O | Handling<br>when<br>unused |

|-------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------------------------|

| VDD                                                   | 231 to 234                                                                            | This is a power supply for logic block.<br>REGE = VDD: Supply a voltage from 4.5 V to 5.5 V to VDD.<br>REGE = VSS: Supply a voltage from 2.7 V to 3.6 V to VDD.<br>In addition, make sure to connect a capacitor between VDD and VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -      | -   | -                          |

| VSS                                                   | 226 to 229,<br>235 to 243                                                             | Make sure to connect VSS to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | -   | -                          |

| VLOGIC                                                | 216                                                                                   | This is a monitor of a regulator output for logic power supply.<br>Do not use VLOGIC with an external circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -      | 0   | OPEN                       |

| REGE                                                  | 230                                                                                   | This is an input for controlling the regulator of logic power supply and the regulator of voltage booster. Depending on specification of power supply, make sure to connect REGE to VDD or VSS. REGE = VDD: 5 V Power supply is used. The regulator of logic power supply runs. The regulator of voltage booster runs. REGE = VSS: 3 V Power supply is used. The regulator of logic power supply stops. The regulator of voltage booster stops.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -      | I   | -                          |

| S1 to 200                                             | 2 to 201                                                                              | These are segment driver outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -      | 0   | OPEN                       |

| COM1 to 8,<br>COM9 to16                               | 313 to 320,<br>210 to 203                                                             | These are common driver outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -      | 0   | OPEN                       |

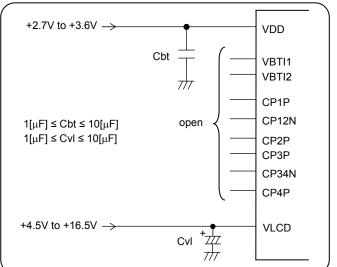

| VBTI1                                                 | 244 to 248                                                                            | This is an input for a base voltage for voltage booster.<br><u>&lt; When voltage booster is used &gt;</u><br>Make sure to connect a capacitor between VBTI1 and VSS.<br>REGE = VDD: Input the voltage from 4.5 V to V <sub>DD</sub> [V] to VBTI1.<br>REGE = VSS: Connect VBTI1 to VBTI2, and Input the voltage from 2.7 V to V <sub>DD</sub> [V] to VBTI1.<br>(When quadruple booster is used : V <sub>BTI</sub> 1 ≤ 3.6 V,<br>When quintuple booster is used : V <sub>BTI</sub> 1 ≤ 3.3 V)<br><u>&lt; When voltage booster is not used &gt;</u><br>Make sure to open VBTI1.                                                                                                                                                                                                                                                                                                                                                      | -      | I   | OPEN                       |

| VBTI2                                                 | 249 to 253                                                                            | This is an input-output for a base voltage for voltage booster.<br><u>&lt; When voltage booster is used &gt;</u><br>Make sure to connect a capacitor between VBTI2 and VSS.<br>REGE = VDD: VBTI2 outputs a base voltage for voltage booster.<br>REGE = VSS: Connect VBTI1 to VBTI2, and Input the voltage from 2.7 V to V <sub>DD</sub> [V] to<br>VBTI1.<br>(When quadruple booster is used : V <sub>BTI</sub> 1 ≤ 3.6 V,<br>When quintuple booster is used : V <sub>BTI</sub> 1 ≤ 3.3 V)<br><u>&lt; When voltage booster is not used &gt;</u><br>Make sure to open VBTI2.                                                                                                                                                                                                                                                                                                                                                        | -      | I/O | OPEN                       |

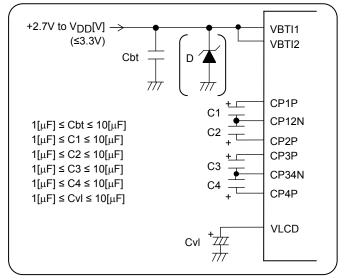

| CP1P,<br>CP12N,<br>CP2P,<br>CP3P,<br>CP34N,<br>CP34N, | 254 to 257,<br>258 to 264,<br>265 to 268,<br>269 to 272,<br>273 to 279,<br>280 to 283 | These are Input-outputs for voltage booster.<br><u>&lt; When quadruple voltage booster is used &gt;</u><br>Make sure to connect a capacitor between CP1P(+) and CP12N(-).<br>Make sure to connect a capacitor between CP3P(+) and CP12N(-).<br>Make sure to connect a capacitor between CP3P(+) and CP34N(-).<br>Make sure to connect CP4P and VLCD.<br><u>&lt; When quintuple voltage booster is used &gt;</u><br>Make sure to connect a capacitor between CP1P(+) and CP12N(-).<br>Make sure to connect a capacitor between CP2P(+) and CP12N(-).<br>Make sure to connect a capacitor between CP3P(+) and CP12N(-).<br>Make sure to connect a capacitor between CP3P(+) and CP34N(-).<br><u>&lt; When voltage booster is not used &gt;</u><br>Make sure to connect a capacitor between CP4P(+) and CP34N(-).<br><u>&lt; When voltage booster is not used &gt;</u><br>Make sure to open CP1P, CP12N, CP2P, CP3P, CP34N and CP4P. | -      | I/O | OPEN                       |

Continued on next page.

#### Continued from preceding page.

| Pad Name | Pad No.    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Active | I/O | Handling<br>when<br>unused |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------------------------|

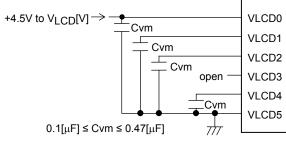

| VLCD     | 284 to 289 | This is a power supply for LCD driver block.<br>Make sure to connect a capacitor between VLCD and VSS.<br><u>&lt; When voltage booster is used &gt;</u><br>(i) When quadruple booster is used: VLCD outputs the booster voltage (V <sub>BTI</sub> 2 × 4).<br>(ii) When quintuple booster is used: VLCD outputs the booster voltage (V <sub>BTI</sub> 2 × 5).<br><u>&lt; When voltage booster is not used &gt;</u><br>Supply a voltage from 4.5 V to 16.5 V to VLCD.<br>When contrast adjuster is used, follow a condition of V <sub>LCD</sub> ≥ V <sub>LCD</sub> 0 + 2.4 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -      | I/O | -                          |

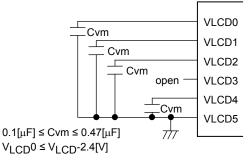

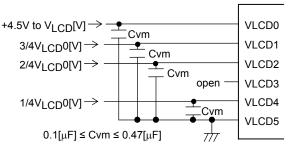

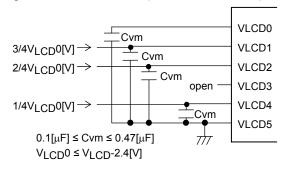

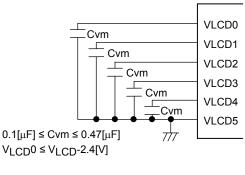

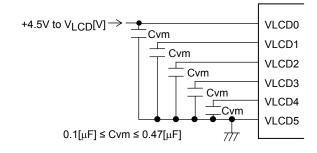

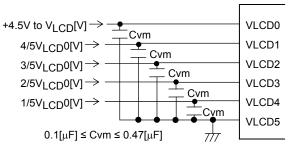

| VLCD0    | 290 to 294 | This is an input-output for the LCD drive bias voltage (High level).<br>Make sure to connect a capacitor between VLCD0 and VLCD5.<br>$\frac{< \text{When contrast adjuster is used }>}{\text{VLCD0 outputs the LCD drive bias voltage (High level) set by "Set of display contrast" instruction (CT0 to CT5).}{\text{Follow a condition of VLCD0 \leq \text{VLCD} - 2.4 \text{ V.}}\frac{< \text{When contrast adjuster is not used }>}{\text{Input the LCD drive bias voltage (High level) to VLCD0 from the outside, and follow a condition of VLCD1 < \text{VLCD0} \leq \text{VLCD}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -      | I/O | OPEN                       |

| VLCD1    | 306 to 308 | This is an input-output for the LCD drive bias voltage (3/4 level, 4/5 level).<br>Make sure to connect a capacitor between VLCD1 and VLCD5.<br>$\leq When LCD drive bias voltage generator is used >$ (i) When 1/4 bias is used: VLCD1 outputs the LCD drive bias voltage (3/4 × V <sub>LCD</sub> 0).<br>(ii) When 1/5 bias is used: VLCD1 outputs the LCD drive bias voltage (4/5 × V <sub>LCD</sub> 0).<br>$\leq When LCD drive bias voltage generator is not used >$ (i) When 1/4 bias is used: Input the LCD drive bias voltage (3/4 × V <sub>LCD</sub> 0) to VLCD1<br>from the outside, and follow a condition of V <sub>LCD</sub> 2 < V <sub>LCD</sub> 1<br>$< V_{LCD}0.$ (ii) When 1/5 bias is used: Input the LCD drive bias voltage (4/5 × V <sub>LCD</sub> 0) to VLCD1<br>from the outside, and follow a condition of V <sub>LCD</sub> 2 < V <sub>LCD</sub> 1<br>$< V_{LCD}0.$ (ii) When 1/5 bias is used: Input the LCD drive bias voltage (4/5 × V <sub>LCD</sub> 0) to VLCD1<br>from the outside, and follow a condition of V <sub>LCD</sub> 2 < V <sub>LCD</sub> 1<br>$< V_{LCD}0.$ | -      | I/O | OPEN                       |

| VLCD2    | 300 to 302 | This is an input-output for the LCD drive bias voltage (2/4 level, 3/5 level).<br>Make sure to connect a capacitor between VLCD2 and VLCD5.<br>$\leq When LCD drive bias voltage generator is used >$ (i) When 1/4 bias is used: VLCD2 outputs the LCD drive bias voltage (2/4 × V <sub>LCD</sub> 0).<br>(ii) When 1/5 bias is used: VLCD2 outputs the LCD drive bias voltage (3/5 × V <sub>LCD</sub> 0).<br>$\leq When LCD drive bias voltage generator is not used >$ (i) When 1/5 bias is used: Input the LCD drive bias voltage (2/4 × V <sub>LCD</sub> 0) to VLCD2<br>from the outside, and follow a condition of V <sub>LCD</sub> 4 < V <sub>LCD</sub> 2<br>< VLCD1. (ii) When 1/5 bias is used: Input the LCD drive bias voltage (3/5 × V <sub>LCD</sub> 0) to VLCD2<br>from the outside, and follow a condition of V <sub>LCD</sub> 3 < V <sub>LCD</sub> 2<br>< VLCD1.                                                                                                                                                                                                                    | -      | I/O | OPEN                       |

| VLCD3    | 303 to 305 | This is an input-output for the LCD drive bias voltage (2/5 level).         < When LCD drive bias voltage generator is used >         (i) When 1/4 bias is used: Make sure to open VLCD3.         (ii) When 1/5 bias is used: VLCD3 outputs the LCD drive bias voltage (2/5 × V <sub>LCD</sub> 0).         Make sure to connect a capacitor between VLCD3 and VLCD5.         < When LCD drive bias voltage generator is not used >         (i) When 1/4 bias is used: Make sure to open VLCD3.         (ii) When 1/4 bias is used: Make sure to open VLCD3.         (ii) When 1/5 bias is used: Make sure to connect a capacitor between VLCD3 and VLCD5. Input the LCD drive bias voltage (2/5 × V <sub>LCD</sub> 0) to VLCD3 from the outside, and follow a condition of V <sub>LCD</sub> 4 < V <sub>LCD</sub> 3 < V <sub>LCD</sub> 2.                                                                                                                                                                                                                                                          | -      | I/O | OPEN                       |

Continued on next page.

#### Continued from preceding page.

| Pad Name            | Pad No.          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Active | I/O | Handling<br>when<br>unused |

|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------------------------|

| VLCD4               | 309 to 311       | This is an input-output for the LCD drive bias voltage (1/4 level, 1/5 level).<br>Make sure to connect a capacitor between VLCD4 and VLCD5.<br>$\frac{< When LCD drive bias voltage generator is used >}{(i)}$ (i) When 1/4 bias is used: VLCD4 outputs the LCD drive bias voltage (1/4 × V <sub>LCD</sub> 0).<br>(ii) When 1/5 bias is used: VLCD4 outputs the LCD drive bias voltage (1/5 × V <sub>LCD</sub> 0).<br>$\frac{< When LCD drive bias voltage generator is not used >}{(i)}$ (i) When 1/4 bias is used: Input the LCD drive bias voltage (1/4 × V <sub>LCD</sub> 0) to VLCD4<br>from the outside, and follow a condition of V <sub>LCD</sub> 5 < V <sub>LCD</sub> 4<br>from the outside, and follow a condition of V <sub>LCD</sub> 5 < V <sub>LCD</sub> 4<br>from the outside, and follow a condition of V <sub>LCD</sub> 5 < V <sub>LCD</sub> 4<br>from the outside, and follow a condition of V <sub>LCD</sub> 5 < V <sub>LCD</sub> 4<br>from the outside, and follow a condition of V <sub>LCD</sub> 5 < V <sub>LCD</sub> 4<br>from the outside, and follow a condition of V <sub>LCD</sub> 5 < V <sub>LCD</sub> 4 | -      | I/O | OPEN                       |

| VLCD5               | 295 to 299       | This is an input-output for the LCD drive bias voltage (Low level).<br>Make sure to connect VLCD5 to VSS even if the LCD drive bias generator is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -      | I   | VSS                        |

| OSCI                | 221              | This is an input for the external clock, when external clock operating mode is selected.<br>By "Set of display method" instruction,<br>OC = 0 (internal oscillator operating mode): Make sure to connect OSCI to VSS.<br>OC = 1 (external clock operating mode): OSCI is used to input the external clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -      | I   | VSS                        |

| CE                  | 218              | These are Inputs for transferring serial data. These pads are connected to a controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н      | I   |                            |

| CL                  | 220              | CE: Chip enables.<br>CL: Synchronous clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 1   | VSS                        |

| DI                  | 219              | DI: Transfer data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -      | I   |                            |

| RES                 | 217              | This is an input for reset of this LSI.<br>RES = VSS: The state of this LSI is reset.<br>Refer to about the "System Reset".<br>RES = VDD: Normal state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L      | I   | VSS                        |

| TSIN1 to<br>TSIN4   | 222 to 225       | These are inputs for a test.<br>Make sure to connect these pads to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -      | I   | VSS                        |

| TSOUT1 to<br>TSOUT3 | 212 to 214       | These are outputs for a test.<br>Make sure to open these pads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -      | ο   | OPEN                       |

| TSO                 | 215              | These are output for a test.<br>Make sure to open this pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -      | 0   | OPEN                       |

| DUMMY               | 1, 202, 211, 312 | These are dummy pads.<br>These pads are not available. Don't connect between dummy pads.<br>Moreover, don't use them with an external circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -      | -   | OPEN                       |

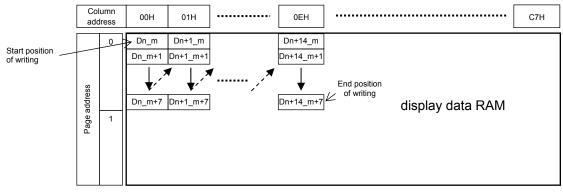

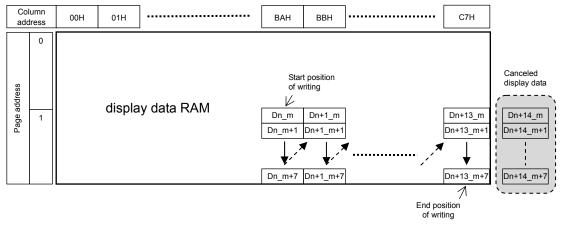

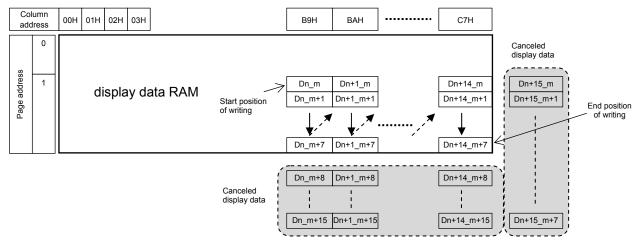

## Correspondence of RAM and Segment Output Pad

|                   |                                    |              |              |                |              |              |              |              |              | Segr     | nent outp     | ut pad |        |        |        |        |                |        |        |        |    |            |

|-------------------|------------------------------------|--------------|--------------|----------------|--------------|--------------|--------------|--------------|--------------|----------|---------------|--------|--------|--------|--------|--------|----------------|--------|--------|--------|----|------------|

| Set of column     | Normal direction<br>(SDIR = "0")   | S1           | S2           | S3             | S4           | S5           | S6           | S7           | S8           | S9       | S10           |        | S193   | S194   | S195   | S196   | S197           | S198   | S199   | S200   |    |            |

| address direction | Reversed direction<br>(SDIR = "1") | S200         | S199         | S198           | S197         | S196         | S195         | S194         | S193         | S192     | S191          |        | S8     | S7     | S6     | S5     | S4             | S3     | S2     | S1     |    |            |

|                   |                                    | D1_1         | D2_1         | D3_1           | D4_1         | D5_1         | D6_1         | D7_1         | D8_1         | D9_1     | D10_1         |        | D193_1 | D194_1 | D195_1 | D196_1 | D197_1         | D198_1 | D199_1 | D200_1 | 0H |            |

|                   |                                    | D1_2         | D2_2         | D3_2           | D4_2         | D5_2         | D6_2         | D7_2         | D8_2         | D9_2     | D10_2         |        | D193_2 | D194_2 | D195_2 | D196_2 | D197_2         | D198_2 | D199_2 | D200_2 | 1H | l          |

|                   |                                    | D1_3         | D2_3         | D3_3           | D4_3         | D5_3         | D6_3         | D7_3         | D8_3         | D9_3     | D10_3         |        | D193_3 | D194_3 | D195_3 | D196_3 | D197_3         | D198_3 | D199_3 | D200_3 | 2H | l          |

|                   | 0                                  | D1_4         | D2_4         | D3_4           | D4_4         | D5_4         | D6_4         | D7_4         | D8_4         | D9_4     | D10_4         |        | D193_4 | D194_4 | D195_4 | D196_4 | D197_4         | D198_4 | D199_4 | D200_4 | 3H | l          |

|                   | -                                  | D1_5         | D2_5         | D3_5           | D4_5         | D5_5         | D6_5         | D7_5         | D8_5         | D9_5     | D10_5         |        | D193_5 | D194_5 | D195_5 | D196_5 | D197_5         | D198_5 | D199_5 | D200_5 | 4H | 1          |

|                   |                                    | D1_6         | D2_6         | D3_6           | D4_6         | D5_6         | D6_6         | D7_6         | D8_6         | D9_6     | D10_6         |        | D193_6 | D194_6 | D195_6 | D196_6 | D197_6         | D198_6 | D199_6 | D200_6 | 5H | Line       |

| Page<br>address   |                                    | D1_7         | D2_7         | D3_7           | D4_7         | D5_7         | D6_7         | D7_7         | D8_7         | D9_7     | D10_7         |        | D193_7 | D194_7 | D195_7 | D196_7 | D197_7         | D198_7 | D199_7 | D200_7 | 6H | address    |

| address           |                                    | D1_8         | D2_8         | D3_8           | D4_8         | D5_8         | D6_8         | D7_8         | D8_8         | D9_8     | D10_8         |        |        |        |        |        | D197_8         |        |        |        | 7H | 1          |