Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

ON Semiconductor®

http://onsemi.com

# Silicon gate LCD Picture Quality Improvement IC

#### Overview

LC749402BG is a picture quality improvement IC that processes the output signals to the LCD panel for high picture quality display. This IC performs various picture quality adjustments to provide the ideal correction for the display panel.

It can support up to WVGA/SVGA panels. \*

#### **Features**

- (1) Digital input/output

- Digital YCbCr/YPbPr 24bit (4:4:4) or 16bit (4:2:2) or 8bit(ITU-R BT.656) signal input

- Digital RGB 24bit signal input

- Digital RGB 18bit/24bit signal output

- Digital YCbCr16bit (4:2:2)/24bit (4:4:4) signal output

- (2) Image quality correction

- Y image quality correction: luminance adjustment, contour correction, CDEX (Color Depth Expander), dynamic-γ, black/white stretch

- C image quality correction: color exciter, flesh tone correction, hue, color gain

- RGB image quality correction: brightness, contrast, white balance, black balance, γ correction

- (3) Panel interface

- Built-in panel driver timing controller

- Panel protection timing signal generation

- Backlight control PWM (video adaptive low power consumption processing)

- \*: The LC749402BG video input should satisfy the following conditions: 40MHz or less operating frequency, 896 dots or less horizontal size, 768 lines or less vertical size.

### **LSI Specifications**

• Supply voltage Core: 1.2V

I/O: 1.8V/2.85V/3.3V

• Maximum operating frequency: 40MHz

• Package: FBGA96

### **Principal Applications**

• LCD display equipment

### **CDEX (Color Depth Expander)**

Original

**CDEX**

### **Specifications**

Absolute Maximum Ratings at Ta = 25°C,  $DV_{SS} = 0V$ ,  $AV_{SS}\_OSC = 0V$

| Parameter                     | Symbol                                        | Conditions | Ratings                          | Unit |

|-------------------------------|-----------------------------------------------|------------|----------------------------------|------|

| Maximum supply voltage (I/O)  | DV <sub>DD</sub> IO                           |            | -0.3 to +3.96                    | ٧    |

| Maximum supply voltage (core) | DV <sub>DD</sub> CORE<br>AV <sub>DD</sub> OSC |            | -0.3 to +1.8                     | V    |

| Digital input voltage         | VI                                            |            | -0.3 to DV <sub>DD</sub> _IO+0.3 | ٧    |

| Digital output voltage        | VO                                            |            | -0.3 to DV <sub>DD</sub> _IO+0.3 | ٧    |

| Operating temperature         | Topr                                          |            | -40 to +85                       | °C   |

| Storage temperature           | Tstg                                          |            | -55 to +125                      | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### Allowable Operating Ranges at $Ta = -40 \text{ to } +85^{\circ}\text{C}$ , $DV_{SS} = 0V$ , $AV_{SS}\_OSC = 0V$

| Daramatar            | Cumbal                                        | Combal Conditions |     | Ratings |                     |      |  |  |

|----------------------|-----------------------------------------------|-------------------|-----|---------|---------------------|------|--|--|

| Parameter            | Symbol                                        | Conditions        | min | typ     | max                 | unit |  |  |

| Supply voltage (I/O) | DV <sub>DD</sub> IO                           |                   | 2.6 | 2.85    | 3.6                 | ٧    |  |  |

|                      |                                               |                   | 1.7 | 1.8     | 1.9                 | ٧    |  |  |

| Supply voltage (I/O) | DV <sub>DD</sub> CORE<br>AV <sub>DD</sub> OSC |                   | 1.0 | 1.2     | 1.3                 | ٧    |  |  |

| Input voltage range  | V <sub>IN</sub>                               |                   | 0   |         | DV <sub>DD</sub> IO | V    |  |  |

**DC Characteristics** at Ta = -40 to +85°C,  $DV_{SS} = 0V$ ,  $AV_{SS}\_OSC = 0V$ ,

$DV_{DD}$ \_IO = 1.7V to 1.9V or 2.6V to 3.6V,  $DV_{DD}$ \_CORE = 1.0V to 1.3V

| Parameter                 | Symbol            | Conditions                                                                                                                                                                                                                                                               |                           | Ratings |                         |      |  |

|---------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------|-------------------------|------|--|

| r arameter                | Symbol            | Conditions                                                                                                                                                                                                                                                               | min                       | typ     | max                     | unit |  |

| Input high-level voltage  | $v_{IH}$          | CMOS level inputs                                                                                                                                                                                                                                                        | 0.7DV <sub>DD</sub> IO    |         |                         | V    |  |

|                           |                   | CMOS level Schmitt inputs                                                                                                                                                                                                                                                | 0.7DV <sub>DD</sub> _IO   |         |                         | V    |  |

| Input low-level voltage   | V <sub>IL</sub>   | CMOS level inputs                                                                                                                                                                                                                                                        |                           |         | 0.3DV <sub>DD</sub> _IO | ٧    |  |

|                           |                   | CMOS level Schmitt inputs                                                                                                                                                                                                                                                |                           |         | 0.3DV <sub>DD</sub> _IO | ٧    |  |

| Input high-level current  | lН                | V <sub>I</sub> =DV <sub>DD</sub> _IO                                                                                                                                                                                                                                     |                           |         | 10                      | μΑ   |  |

|                           |                   | V <sub>I</sub> =DV <sub>DD</sub> IO, with pull-down resistance                                                                                                                                                                                                           |                           |         | 100                     | μΑ   |  |

| Input low-level current   | I <sub>IL</sub>   | V <sub>I</sub> =DV <sub>SS</sub>                                                                                                                                                                                                                                         | -10                       |         |                         | μΑ   |  |

| Output high-level voltage | VOH               | CMOS voltage: 2.6V to 3.6V Pin D: I <sub>OH</sub> =-2mA Pin F: I <sub>OH</sub> =-2mA (when set to 2mA) I <sub>OH</sub> =-4mA (when set to 4mA) Pin G: I <sub>OH</sub> =-4mA (when set to 4mA) I <sub>OH</sub> =-8mA (when set to 8mA) Pin H: I <sub>OH</sub> =-4mA       | DV <sub>DD</sub> IO-0.4   |         |                         | V    |  |

|                           |                   | CMOS voltage: 1.7V to 1.9V  Pin D: I <sub>OH</sub> =-1mA  Pin F: I <sub>OH</sub> =-1mA (when set to 2mA)  I <sub>OH</sub> =-2mA (when set to 4mA)  Pin G: I <sub>OH</sub> =-2mA (when set to 4mA)  I <sub>OH</sub> =-4mA (when set to 8mA)  Pin H: I <sub>OH</sub> =-2mA | DV <sub>DD</sub> _IO-0.45 |         |                         | V    |  |

| Output low-level voltage  | V <sub>OL</sub>   | CMOS                                                                                                                                                                                                                                                                     |                           |         | 0.4                     | V    |  |

| Output leak current       | loz               | At output of high-impedance                                                                                                                                                                                                                                              | -10                       |         | 10                      | μΑ   |  |

| Pull-down resistor        | R <sub>DN</sub>   | Typical conditions:  Ta=25°C  DV <sub>DD</sub> _IO=2.85V  DV <sub>DD</sub> _CORE=1.2V                                                                                                                                                                                    |                           | 98      |                         | kΩ   |  |

| Dynamic supply current    | I <sub>DDOP</sub> | Typical conditions:  Ta=25°C  DV <sub>DD</sub> IO=2.85V  DV <sub>DD</sub> CORE=1.2V  tck=10MHz 10 steps  Typical conditions:                                                                                                                                             |                           | 18      |                         | mA   |  |

|                           |                   | Ta=25°C DV <sub>DD</sub> _IO=2.85V DV <sub>DD</sub> _CORE=1.2V tck=40MHz 10 steps                                                                                                                                                                                        |                           | 57      |                         | mA   |  |

| Static supply current *1  | IDDST             | Typical conditions:  Ta=25°C  DV <sub>DD</sub> IO=2.85V  DV <sub>DD</sub> CORE=1.2V  Outputs open  V <sub>I</sub> =DV <sub>SS</sub> or DV <sub>DD</sub> IO                                                                                                               |                           | 20      |                         | μΑ   |  |

<sup>\*1:</sup> There is a input terminal which builds in pull down resistance. Please note that there is no guarantee about static consumption current depending on circuit composition.

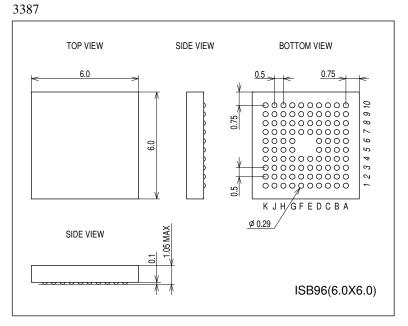

## Package Dimensions FBGA96

unit:mm (typ)

## **Pin Assignment**

LC749402BG

|   | 1       | 2       | 3       | 4       | 5       | 6       | 7       | 8       | 9       | 10      |  |

|---|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--|

|   |         |         |         |         |         |         |         |         |         |         |  |

| Α | 0       | $\circ$ | $\circ$ | 0       | $\circ$ | 0       | $\circ$ | $\circ$ | $\circ$ | 0       |  |

| В | 0       | $\circ$ | $\circ$ | 0       | $\circ$ | $\circ$ | $\circ$ | $\circ$ | $\circ$ | 0       |  |

| С | 0       | 0       | $\circ$ | $\circ$ | 0       | $\circ$ | $\circ$ | $\circ$ | 0       | $\circ$ |  |

| D | $\circ$ | 0       | $\circ$ | $\circ$ | 0       | $\circ$ | $\circ$ | $\circ$ | 0       | $\circ$ |  |

| Е | $\circ$ | 0       | $\circ$ | $\circ$ |         |         | $\circ$ | $\circ$ | 0       | $\circ$ |  |

| F | 0       | 0       | 0       | 0       |         |         | 0       | 0       | 0       | 0       |  |

| G | $\circ$ | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | $\circ$ |  |

| Н | 0       | 0       | 0       | $\circ$ | 0       | $\circ$ | $\circ$ | 0       | 0       | 0       |  |

| J | 0       | 0       | 0       | 0       | 0       | $\circ$ | $\circ$ | $\circ$ | 0       | 0       |  |

| K | 0       | 0       | 0       | 0       | 0       | 0       | $\circ$ | $\circ$ | 0       | 0       |  |

|   |         |         |         |         |         |         |         |         |         |         |  |

Top view

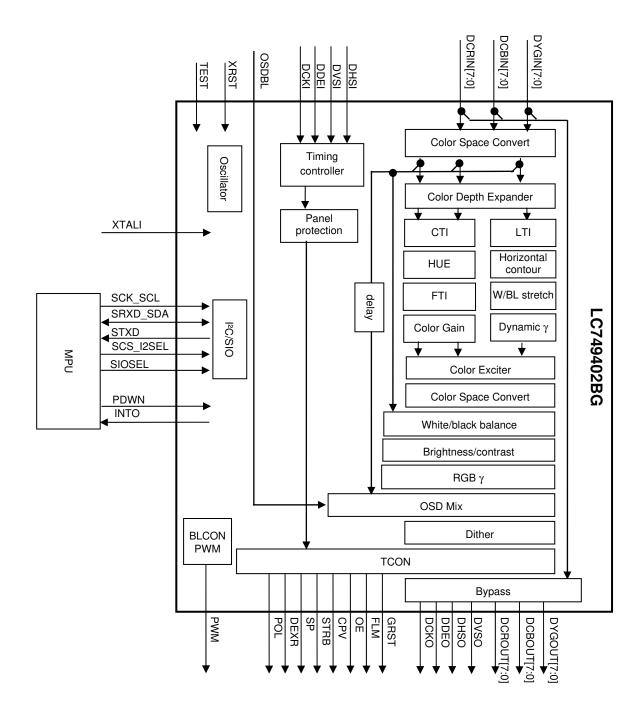

# **Block Diagram**

## **Pin Functions**

| Din M-  | In/output format      |     | ut format | Connecting   |         | Decreeded                                                              |

|---------|-----------------------|-----|-----------|--------------|---------|------------------------------------------------------------------------|

| Pin No. | Pin symbol            | I/O | Format    | destir       | nation  | Remarks                                                                |

| A1      | AV <sub>DD</sub> OSC  | Р   | -         | Core voltage | Analog  | Connect this pin to B2 without fail.                                   |

| A2      | STXD                  | 0   | D         | CMOS         | Digital | SIO data                                                               |

| A3      | SCK_SCL               | 1   | С         | CMOS         | Digital | Bus clock (common to SIO and I <sup>2</sup> C)                         |

| A4      | DBOUT7                | 0   | F         | CMOS         | Digital | B/Cb/C video (MSB)                                                     |

| A5      | DBOUT4                | 0   | F         | CMOS         | Digital | B/Cb/C video                                                           |

| A6      | DBOUT1                | 0   | F         | CMOS         | Digital | B/Cb/C video                                                           |

| A7      | DGOUT6                | 0   | F         | CMOS         | Digital | G/Y video                                                              |

| A8      | DGOUT4                | 0   | F         | CMOS         | Digital | G/Y video                                                              |

| A9      | DGOUT3                | 0   | F         | CMOS         | Digital | G/Y video                                                              |

| A10     | DV <sub>DD</sub> _IO  | Р   | -         | IO voltage   | Digital | Connect this pin to B9 without fail                                    |

| B1      | RC_BIAS               | I   | J         | resistor     | Analog  | Bias resistor connection (Connect this pin to GND with a $20k\Omega$ ) |

| B2      | AV <sub>DD</sub> OSC  | Р   | -         | Core voltage | Analog  |                                                                        |

| В3      | SRXD_SDA              | I/O | Н         | CMOS         | Digital | SIO data input/I <sup>2</sup> C data I/O                               |

| B4      | PWM                   | 0   | D         | CMOS         | Digital | Pulse width modulation waveform                                        |

| B5      | DBOUT5                | 0   | F         | CMOS         | Digital | B/Cb/C video                                                           |

| В6      | DBOUT2                | 0   | F         | CMOS         | Digital | B/Cb/C video (6-bit output mode, LSB)                                  |

| B7      | DGOUT7                | 0   | F         | CMOS         | Digital | G/Y video (MSB)                                                        |

| B8      | DGOUT5                | 0   | F         | CMOS         | Digital | G/Y video                                                              |

| В9      | DV <sub>DD</sub> IO   | Р   | -         | IO voltage   | Digital |                                                                        |

| B10     | DGOUT2                | 0   | F         | CMOS         | Digital | G/Y video (6-bit output mode, LSB)                                     |

| C1      | DCRIN0                | I   | С         | CMOS         | Digital | R/Cr video. Connect this pin to GND when not to be used.               |

| C2      | DCRIN1                | I   | С         | CMOS         | Digital | R/Cr video. Connect this pin to GND when not to be used.               |

| C3      | AV <sub>SS</sub> _OSC | Р   | -         | GND          | Analog  |                                                                        |

| C4      | INTO                  | 0   | D         | CMOS         | Digital | Interrupt                                                              |

| C5      | DBOUT6                | 0   | F         | CMOS         | Digital | B/Cb/C video                                                           |

| C6      | DBOUT3                | 0   | F         | CMOS         | Digital | B/Cb/C video                                                           |

| C7      | DBOUT0                | 0   | F         | CMOS         | Digital | B/Cb/C video (8-bit output mode, LSB)                                  |

| C8      | DV <sub>DD</sub> IO   | Р   | -         | IO voltage   | Digital |                                                                        |

| C9      | DGOUT1                | 0   | F         | CMOS         | Digital | G/Y video                                                              |

| C10     | DGOUT0                | 0   | F         | CMOS         | Digital | G/Y video (8-bit output mode, LSB)                                     |

| D1      | DCRIN2                | I   | С         | CMOS         | Digital | R/Cr video. Connect this pin to GND when not to be used.               |

| D2      | DCRIN3                | I   | С         | CMOS         | Digital | R/Cr video. Connect this pin to GND when not to be used.               |

| D3      | DCRIN4                | I   | С         | CMOS         | Digital | R/Cr video. Connect this pin to GND when not to be used.               |

| D4      | TEST                  | I   | В         | CMOS         | Digital | Test (Normally, connect this pin to GND)                               |

| D5      | XRST                  | I   | А         | CMOS         | Digital | System reset ("L" reset)                                               |

| D6      | DV <sub>DD</sub> IO   | Р   | -         | IO voltage   | Digital |                                                                        |

| D7      | DV <sub>DD</sub> IO   | Р   | -         | IO voltage   | Digital |                                                                        |

| D8      | DROUT7                | 0   | F         | CMOS         | Digital | R/Cr video (MSB)                                                       |

| D9      | DROUT6                | 0   | F         | CMOS         | Digital | R/Cr video                                                             |

| D10     | DROUT5                | 0   | F         | CMOS         | Digital | R/Cr video                                                             |

Continued on next page.

Continued from preceding page.

| Pin No.  | n No. Pin symbol In/output form |               | ut format | Conn              | ecting             | Remarks                                                              |

|----------|---------------------------------|---------------|-----------|-------------------|--------------------|----------------------------------------------------------------------|

| PIII NO. | Pin Symbol                      | I/O           | Format    | destir            | nation             | Hemarks                                                              |

| E1       | DCRIN5                          | I             | С         | CMOS              | Digital            | R/Cr video. Connect this pin to GND when not to be used.             |

| E2       | DCRIN6                          | I             | С         | CMOS              | Digital            | R/Cr video. Connect this pin to GND when not to be used.             |

| F0       | DODINZ                          |               | 0         | CMCC              | District           | R/Cr video (MSB).                                                    |

| E3       | DCRIN7                          | I             | С         | CMOS              | Digital            | Connect this pin to GND when not to be used.                         |

| E4       | DV <sub>SS</sub>                | Р             | -         | GND               | Digital            |                                                                      |

| E7       | PDWN                            | ı             | Α         | CMOS              | Digital            | "H" power down.                                                      |

|          | DDOUT4                          |               |           | 01400             | _                  | Connect this pin to GND when not to be used.                         |

| E8       | DROUT4                          | 0             | F         | CMOS              | Digital            | R/Cr video                                                           |

| E9       | DROUT3                          | 0             | F         | CMOS              | Digital            | R/Cr video                                                           |

| E10      | DROUT2                          | 0             | F         | CMOS              | Digital            | R/Cr video (6-bit output mode, LSB)                                  |

| F1       | DYGIN0                          | I             | С         | CMOS              | Digital            | G/Y/656 video (LSB).  Connect this pin to GND when not to be used.   |

|          |                                 |               |           |                   |                    | G/Y/656 video.                                                       |

| F2       | DYGIN1                          | I             | С         | CMOS              | Digital            | Connect this pin to GND when not to be used.                         |

| F3       | DYGIN2                          | ı             | С         | CMOS              | Digital            | G/Y/656 video.                                                       |

|          | Brantz                          |               | Ŭ         |                   | Digital            | Connect this pin to GND when not to be used.                         |

| F4       | DV <sub>SS</sub>                | Р             | -         | GND               | Digital            |                                                                      |

| F7       | DV <sub>DD</sub> CORE           | Р             | -         | Core voltage      | Digital            |                                                                      |

| F8       | DROUT1                          | 0             | F         | CMOS              | Digital            | R/Cr video                                                           |

| F9       | DROUT0                          | 0             | F         | CMOS              | Digital            | R/Cr video (8-bit output mode, LSB)                                  |

| F10      | DCKO                            | 0             | G         | CMOS              | Digital            | Video clock                                                          |

| G1       | DYGIN3                          | ı             | С         | CMOS              | Digital            | G/Y/656 video.                                                       |

|          |                                 |               |           |                   |                    | Connect this pin to GND when not to be used.  G/Y/656 video.         |

| G2       | DYGIN4                          | I             | С         | CMOS              | Digital            | Connect this pin to GND when not to be used.                         |

|          | D)/OINE                         |               | _         | 01400             | Divisi.            | G/Y/656 video.                                                       |

| G3       | DYGIN5                          | ı             | С         | CMOS              | Digital            | Connect this pin to GND when not to be used.                         |

| G4       | DV <sub>SS</sub>                | Р             | -         | GND               | Digital            |                                                                      |

| G5       | SCS_I2SEL                       | I             | Α         | CMOS              | Digital            | SIO chip enable/I <sup>2</sup> C slave address switching             |

| G6       | SIOSEL                          | I             | С         | CMOS              | Digital            | "L": I <sup>2</sup> C slave, "H": 4-wire SIO                         |

| G7       | DV <sub>DD</sub> CORE           | Р             | -         | Core voltage      | Digital            |                                                                      |

| G8       | DHSO/SP2                        | 0             | F         | CMOS              | Digital            | Horizontal synchronizing signal/start pulse signal for source driver |

| G9       | DVSO/FLM2                       | 0             | F         | CMOS              | Digital            | Vertical synchronizing signal/start pulse signal for gate            |

|          |                                 |               |           |                   |                    | driver                                                               |

| G10      | DDEO                            | 0             | F         | CMOS              | Digital            | Data enable signal                                                   |

| H1       | DYGIN6                          | 1             | С         | CMOS              | Digital            | G/Y/656 video.  Connect this pin to GND when not to be used.         |

|          |                                 |               |           |                   |                    | G/Y/656 video (MSB).                                                 |

| H2       | DYGIN7                          | I             | С         | CMOS              | Digital            | Connect this pin to GND when not to be used.                         |

| НЗ       | DV <sub>SS</sub>                | Р             | -         | GND               |                    |                                                                      |

| H4       | DCBIN6                          | 1             | С         | CMOS              | Digital            | B/Cb/C video.                                                        |

| 114      | DOBINO                          | '             |           | Olvios            | Digital            | Connect this pin to GND when not to be used.                         |

| H5       | DVSI                            | I             | С         | CMOS              | Digital            | Vertical synchronizing signal                                        |

| H6       | OSDBL                           | I             | С         | CMOS              | Digital            | Data enable signal for external OSD.                                 |

| LI7      | FLM                             |               | F         | CMOS              | Digital            | Connect this pin to GND when not to be used.                         |

| H7       |                                 | 0             | F         | Coro voltago      | Digital            | Start pulse signal for gate driver                                   |

| H8<br>H9 | DV <sub>DD</sub> CORE<br>DEXR   | <u>Р</u><br>О | -<br>F    | Core voltage CMOS | Digital<br>Digital | Reversed video signal output for DTR. Low output when the            |

|          |                                 |               |           |                   | _                  | DTR is OFF.                                                          |

| H10      | POL                             | 0             | F         | CMOS              | Digital            | Voltage polarity selection signal for source driver                  |

Continued on next page.

Continued from preceding page.

| Continued                           | from preceding pa     | ge. |        | T            |         | _                                                                                     |  |  |

|-------------------------------------|-----------------------|-----|--------|--------------|---------|---------------------------------------------------------------------------------------|--|--|

| Pin No. Pin symbol In/output format |                       |     |        | Connecting   |         | Remarks                                                                               |  |  |

|                                     | 6760                  | I/O | Format | destir       | nation  |                                                                                       |  |  |

| J1                                  | DCBIN0                | I   | С      | CMOS         | Digital | B/Cb/C video (LSB). Connect to GND when not to be used.                               |  |  |

| J2                                  | DV <sub>SS</sub>      | Р   | -      | GND          | Digital |                                                                                       |  |  |

| J3                                  | DCBIN3                | 1   | С      | CMOS         | Digital | B/Cb/C video.  Connect this pin to GND when not to be used.                           |  |  |

| J4                                  | DCBIN5                | 1   | С      | CMOS         | Digital | B/Cb/C video. Connect this pin to GND when not to be used.                            |  |  |

| J5                                  | DDEI                  | 1   | С      | CMOS         | Digital | Data enable signal, Connect this pin to GND in the internal generation mode           |  |  |

| J6                                  | DHSI                  | 1   | С      | CMOS         | Digital | Horizontal synchronizing signal                                                       |  |  |

| J7                                  | GRST                  | 0   | F      | CMOS         | Digital | Reset signal for gate driver                                                          |  |  |

| J8                                  | CPV                   | 0   | F      | CMOS         | Digital | Clock signal for gate driver                                                          |  |  |

| J9                                  | DV <sub>DD</sub> CORE | Р   | -      | Core voltage | Digital |                                                                                       |  |  |

| J10                                 | SP                    | 0   | F      | CMOS         | Digital | Start pulse signal for source driver                                                  |  |  |

| K1                                  | DV <sub>SS</sub>      | Р   | -      | GND          | Analog  | Connect this pin to J2 without fail                                                   |  |  |

| K2                                  | DCBIN1                | 1   | С      | CMOS         | Digital | B/Cb/C video. Connect this pin to GND when not to be used.                            |  |  |

| K3                                  | DCBIN2                | 1   | С      | CMOS         | Digital | B/Cb/C video.  Connect this pin to GND when not to be used.                           |  |  |

| K4                                  | DCBIN4                | ı   | С      | CMOS         | Digital | B/Cb/C video. Connect this pin to GND when not to be used.                            |  |  |

| K5                                  | DCBIN7                | 1   | С      | CMOS         | Digital | B/Cb/C video (MSB). Connect this pin to GND when not to be used.                      |  |  |

| K6                                  | DCKI                  | I   | С      | CMOS         | Digital | Video clock                                                                           |  |  |

| K7                                  | XTAL1                 | 1   | С      | CMOS         | Digital | Panel protection, PWM generation clock.  Connect this pin to GND when not to be used. |  |  |

| K8                                  | OE                    | 0   | F      | CMOS         | Digital | Output enable signal for gate driver                                                  |  |  |

| K9                                  | STRB                  | 0   | F      | CMOS         | Digital | Data strobe signal for source driver                                                  |  |  |

| K10                                 | DV <sub>DD</sub> CORE | Р   | -      | Core voltage | Digital | Connect this pin to J9 without fail                                                   |  |  |

## Pin Type

| In/Output form    | Function                                          | Equivalent circuit | Application Terminal                                                                                                                                                                                                                                                     |

|-------------------|---------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| III/Output IoIIII |                                                   | Equivalent circuit |                                                                                                                                                                                                                                                                          |

| А                 | Schmitt trigger<br>CMOS input                     |                    | XRST, PDWN, SCS_I2SEL                                                                                                                                                                                                                                                    |

| В                 | CMOS input with built-in pull-down resistor       |                    | TEST                                                                                                                                                                                                                                                                     |

| С                 | CMOS input                                        |                    | SCK_SCL, SIOSEL, DVSI, DHSI, DDEI, OSDBL, DYGIN7, DYGIN6, DYGIN5, DYGIN4, DYGIN3, DYGIN2, DYGIN1, DYGIN0, DCBIN7, DCBIN6, DCBIN5, DCBIN4, DCBIN3, DCBIN2, DCBIN1, DCBIN0, DCRIN7, DCRIN6, DCRIN5, DCRIN4, DCRIN7, DCRIN6, DCRIN5, DCRIN4, DCRIN3, DCRIN2, DCRIN1, DCRIN0 |

| D                 | 2mA 3-STATE drive<br>CMOS output                  |                    | STXD, PWM, INTO                                                                                                                                                                                                                                                          |

| F                 | 2mA/4mA switching<br>3-STATE drive<br>CMOS output |                    | DBOUT7, DBOUT6, DBOUT5, DBOUT4, DBOUT3, DBOUT2, DBOUT1, DBOUT0, DROUT7, DROUT6, DROUT5, DROUT4, DROUT3, DROUT2, DROUT1, DROUT0 DGOUT7, DGOUT6, DGOUT5, DGOUT4, DGOUT3, DGOUT2, DGOUT1, DGOUT0, DHSO/SP2, DVSO/FLM2, DDEO FLM, DEXR, POL, GRST, CPV, SP, OE, STRB         |

| G                 | 4mA/8mA switching<br>3-STATE drive<br>CMOS output |                    | DCKO                                                                                                                                                                                                                                                                     |

| н                 | 4mA 3-STATE drive<br>CMOS input/output            |                    | SRXD_SDA                                                                                                                                                                                                                                                                 |

| J                 | Analog input/output                               | <u> </u>           | RC_BIAS                                                                                                                                                                                                                                                                  |

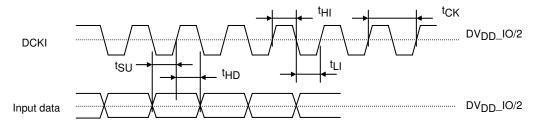

### I/O Timing

### (1) Input data timing

| Pin name                        | Parameter                                                  | Symbol          | min | typ | max | unit |

|---------------------------------|------------------------------------------------------------|-----------------|-----|-----|-----|------|

| DCKI                            | Clock cycle                                                | t <sub>CK</sub> | 25  |     |     | ns   |

| DCKI                            | Duty                                                       |                 |     | 50  |     | %    |

|                                 | Input data setup time (DV <sub>DD</sub> _IO=2.6 to 3.6V)   | <sup>t</sup> su | 3   |     |     | ns   |

| DCRIN*, DYGIN*,                 | Input data setup time (DV <sub>DD</sub> _IO=1.7 to 1.9V)   | <sup>t</sup> su | 3   |     |     | ns   |

| DCBIN*, DVSI, DHSI, DDEI, OSDBL | Input data hold time (DV <sub>DD</sub> _IO=2.6 to 3.6V)    | tHD             | 2   |     |     | ns   |

|                                 | Input data hold time<br>(DV <sub>DD</sub> _IO=1.7 to 1.9V) | tHD             | 2   |     |     | ns   |

<sup>\*:</sup> The recommended duty cycle of input clock is 50%

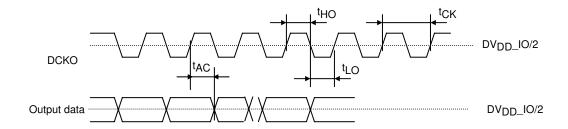

### (2) Output data timing

| Pin name                                                                                | Parameter                                                                                               | Symbol          | min | typ | max | unit |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| 2010                                                                                    | Clock cycle                                                                                             | <sup>t</sup> CK | 25  |     |     | ns   |

| DCKO                                                                                    | Duty                                                                                                    |                 |     | 50  |     | %    |

| DROUT*, DGOUT*, DBOUT*,<br>DVSO, DHSO, DDEO, DEXR, POL,<br>SP, STRB, CPV, OE, FLM, GRST | Output data delay time (DV <sub>DD</sub> _IO=2.6 to 3.6V) Pin F: when set to 4mA Pin G: when set to 8mA | <sup>t</sup> AC | -3  |     | 3   | ns   |

|                                                                                         | Output data delay time (DV <sub>DD</sub> _IO=2.6 to 3.6V) Pin F: when set to 2mA Pin G: when set to 4mA | <sup>t</sup> AC | -3  |     | 6   | ns   |

|                                                                                         | Output data delay time (DV <sub>DD</sub> _IO=1.7 to 1.9V) Pin F: when set to 4mA Pin G: when set to 8mA | <sup>t</sup> AC | -5  |     | 4   | ns   |

|                                                                                         | Output data delay time (DV <sub>DD</sub> _IO=1.7 to 1.9V) Pin F: when set to 2mA Pin G: when set to 4mA | <sup>t</sup> AC | -6  |     | 9   | ns   |

<sup>\*</sup> When DCKO is set to the forward rotation output. Output load capacity: 5pF

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa