# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

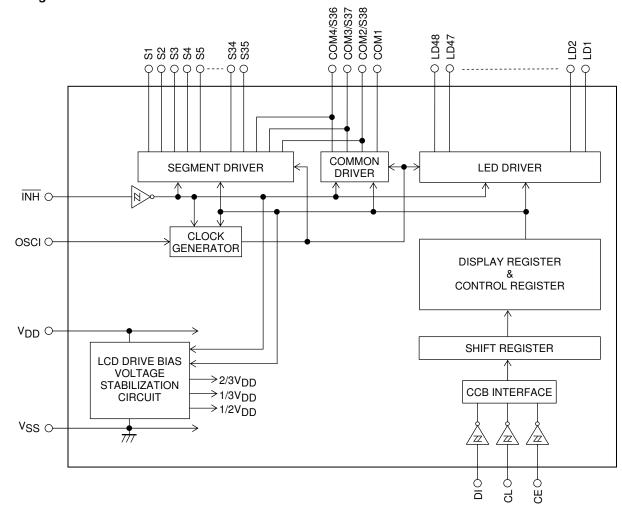

## 1/1 to 1/4 Duty General-Purpose LCD Driver with LED Driver

#### **Overview**

LC75805PE is the 1/1 to 1/4 duty general-purpose LCD display driver with the LED driver to use for the instrument panel display by control with the controller. In addition, LC75805PE is able to drive up to 48 LED and LCD of up to 140 segments directly, and has a built-in 7ch PWM function for brightness adjustment of LED. Furthermore, because of built-in the oscillator circuit, it is possible to reduce external resister and capacitor for oscillation.

#### **Features**

- Switch of Static Drive, 1/2 Duty Drive, 1/3 Duty Drive and 1/4 Duty Drive can be controlled by serial data.

- Static Drive (1/1 Duty Drive): Capable of driving up to 38 segments. 1/2 Duty Drive

- : Capable of driving up to 74 segments.

: Capable of driving up to 140 segments.

- 1/3 Duty Drive

- : Capable of driving up to 108 segments.

- 1/4 Duty Drive

- Frame frequency of common and segment output waveform can be controlled by serial data.

- Turning on/off LED can be controlled by serial data. (Capable of driving up to 48 LED)

- Built-in 7 ch PWM function for brightness adjustment of LED. (Resolution of 128 steps)

- Frame frequency of LED driver output waveform can be controlled by serial data.

- Serial data input supports CCB\* format communication with the system controller. (Support 5 V operation)

- Backup function and forced turning off all segments by power-saving mode can be controlled by serial data.

- Switch of the internal oscillator operating mode and the external clock operating mode can be controlled by serial data.

- High generality, since display data is displayed directly without the intervention of a decoder circuit.

- The INH pin allows the display to be forced to the off state.

- Built-in Oscillator circuit (Built-in resister and capacitor for oscillation)

#### **ON Semiconductor®**

www.onsemi.com

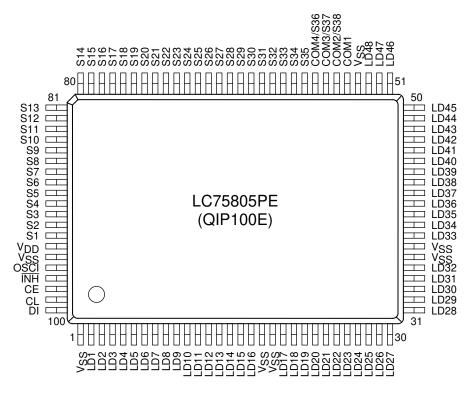

PQFP100 14x20 / QIP100E

\* Computer Control Bus (CCB) is an ON Semiconductor's original bus format and the bus addresses are controlled by ON Semiconductor.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 34 of this data sheet.

#### Specifications

#### Absolute Maximum Ratings at Ta = 25°C, $V_{SS} = 0 V$

| Parameter                   | Symbol              | Conditions              | Ratings                      | Unit |

|-----------------------------|---------------------|-------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>         | -0.3 to +6.5                 | V    |

| Input voltage               | V <sub>IN</sub> 1   | CE, CL, DI, INH, OSCI   | -0.3 to +6.5                 | V    |

| Output voltage              | VOUT1               | S1 to S38, COM1 to COM4 | –0.3 to V <sub>DD</sub> +0.3 | M    |

|                             | V <sub>OUT</sub> 2  | LD1 to LD48             | -0.3 to +35                  | V    |

| Output current              | IOUT1               | S1 to S38               | 300                          | μA   |

|                             | IOUT <sup>2</sup>   | COM1 to COM4            | 3                            |      |

|                             | IOUT3               | LD1 to LD48             | 30                           | mA   |

| Allowable power dissipation | Pd max              | Ta = 95°C               | 400                          | mW   |

| Operating temperature       | Topr                |                         | -40 to +95                   | °C   |

| Storage temperature         | Tstg                |                         | -55 to +150                  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Allowable Operating Ranges at Ta = -40 to +95°C, V<sub>SS</sub> = 0 V

| Parameter                             | Cymbol            |                 | Conditions                      |                    | Ratings |                    | Unit |

|---------------------------------------|-------------------|-----------------|---------------------------------|--------------------|---------|--------------------|------|

| Parameter                             | Symbol            | Conditions      |                                 | min                | typ     | max                | Unit |

| Supply voltage                        | V <sub>DD</sub>   | V <sub>DD</sub> |                                 | 4.5                |         | 5.5                | V    |

| Input high-level voltage              | V <sub>IH</sub> 1 | CE, CL, DI, INI | Ī                               | 0.8V <sub>DD</sub> |         | 5.5                | V    |

|                                       | V <sub>IH</sub> 2 | OSCI            |                                 | 0.8V <sub>DD</sub> |         | 5.5                | v    |

| Input low-level voltage               | V <sub>IL</sub> 1 | CE, CL, DI, INI | -<br>-                          | 0                  |         | 0.2V <sub>DD</sub> | V    |

|                                       | V <sub>IL</sub> 2 | OSCI            |                                 | 0                  |         | 0.2V <sub>DD</sub> | v    |

| Output pull-up voltage                | VOUP              | LD1 to LD48, \  | ′ <sub>DD</sub> = 4.5 to 5.5 V  | 0                  |         | 30                 | V    |

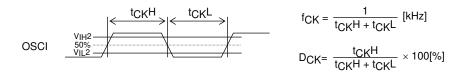

| External clock operating<br>frequency | fCK               | OSCI, Externa   | clock operating mode<br>[Fig 3] | 100                | 300     | 600                | kHz  |

| External clock duty                   | DCK               | OSCI, Externa   | clock operating mode<br>[Fig 3] | 30                 | 50      | 70                 | %    |

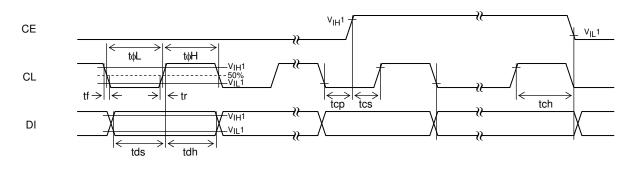

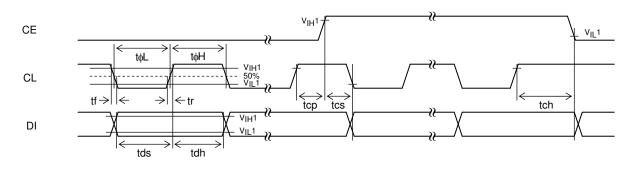

| Data setup time                       | tds               | CL, DI          | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| Data hold time                        | tdh               | CL, DI          | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| CE wait time                          | tcp               | CE, CL          | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| CE setup time                         | tcs               | CE, CL          | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| CE hold time                          | tch               | CE, CL          | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| High-level clock pulse width          | tφH               | CL              | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| Low-level clock pulse width           | tφL               | CL              | [Fig 1], [Fig 2]                | 160                |         |                    | ns   |

| Rise time                             | tr                | CE, CL, DI      | [Fig 1], [Fig 2]                |                    | 160     |                    | ns   |

| Fall time                             | tf                | CE, CL, DI      | [Fig 1], [Fig 2]                |                    | 160     |                    | ns   |

| INH switching time                    | tc                | INH, CE [Fig    | g 4], [Fig 5], [Fig 6], [Fig 7] | 10                 |         |                    | μS   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Electrical Characteristics for the Allowable Operating Ranges

| Parameter                      | Symbol             | Pin                | Conditions                                                                                                                                  |                            | Ratings            |                            | Unit |

|--------------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------|------|

| Falameter                      |                    | Conditions         | min                                                                                                                                         | typ                        | max                | UIII                       |      |

| Hysteresis                     | VH                 | CE, CL, DI, INH    |                                                                                                                                             |                            | 0.1V <sub>DD</sub> |                            | V    |

| Input high-level               | IIH1               | CE, CL, DI, INH    | V <sub>I</sub> = 5.5 V                                                                                                                      |                            |                    | 5.0                        |      |

| current                        | I <sub>IH</sub> 2  | OSCI               | V <sub>I</sub> = 5.5 V                                                                                                                      |                            |                    | 5.0                        | μA   |

| Input low-level                | IIL1               | CE, CL, DI, INH    | V <sub>I</sub> = 0 V                                                                                                                        | -5.0                       |                    |                            |      |

| current                        | I <sub>IL</sub> 2  | OSCI               | V <sub>I</sub> = 0 V                                                                                                                        | -5.0                       |                    |                            | μA   |

| Output OFF leak<br>current     | IOFFH              | LD1 to LD48        | V <sub>O</sub> = 30 V                                                                                                                       |                            |                    | 5.0                        | μA   |

| Output high-level              | V <sub>OH</sub> 1  | S1 to S38          | I <sub>O</sub> = -20 μA                                                                                                                     | V <sub>DD</sub> -0.9       |                    |                            | .,   |

| voltage                        | V <sub>OH</sub> 2  | COM1 to COM4       | I <sub>O</sub> = -100 μA                                                                                                                    | V <sub>DD</sub> -0.9       |                    |                            | V    |

| Output low-level               | V <sub>OL</sub> 1  | S1 to S38          | l <sub>O</sub> = 20 μA                                                                                                                      |                            |                    | 0.9                        |      |

| voltage                        | V <sub>OL</sub> 2  | COM1 to COM4       | I <sub>O</sub> = 100 μA                                                                                                                     |                            |                    | 0.9                        | v    |

|                                | V <sub>OL</sub> 3  | LD1 to LD48        | I <sub>O</sub> = 20 mA                                                                                                                      |                            | 0.25               | 0.5                        |      |

| Output middle-level<br>voltage | V <sub>MID</sub> 1 | S1 to S36          | 1/3 bias I <sub>O</sub> = $\pm 20 \mu$ A                                                                                                    | 2/3V <sub>DD</sub><br>-0.9 |                    | 2/3V <sub>DD</sub><br>+0.9 |      |

|                                | V <sub>MID</sub> 2 | S1 to S36          | 1/3 bias I <sub>O</sub> = ±20 µA                                                                                                            | 1/3V <sub>DD</sub><br>-0.9 |                    | 1/3V <sub>DD</sub><br>+0.9 |      |

|                                | V <sub>MID</sub> 3 | COM1 to COM4       | 1/3 bias I <sub>O</sub> = ±100 µA                                                                                                           | 2/3V <sub>DD</sub><br>-0.9 |                    | 2/3V <sub>DD</sub><br>+0.9 | v    |

|                                | V <sub>MID</sub> 4 | COM1 to COM4       | 1/3 bias I <sub>O</sub> = ±100 µA                                                                                                           | 1/3V <sub>DD</sub><br>-0.9 |                    | 1/3V <sub>DD</sub><br>+0.9 |      |

|                                | V <sub>MID</sub> 5 | COM1, COM2         | $1/2$ bias $I_{O} = \pm 100 \ \mu A$                                                                                                        | 1/2V <sub>DD</sub><br>-0.9 |                    | 1/2V <sub>DD</sub><br>+0.9 |      |

| Oscillator frequency           | fosc               | Oscillator circuit | Internal oscillator operating mode                                                                                                          | 240                        | 300                | 360                        | kHz  |

| Current drain                  | I <sub>DD</sub> 1  | V <sub>DD</sub>    | Power save mode                                                                                                                             |                            |                    | 15                         |      |

|                                | I <sub>DD</sub> 2  | VDD                | V <sub>DD</sub> = 5.5 V<br>Output open,<br>Internal oscillator operating<br>mode                                                            |                            | 750                | 1500                       |      |

|                                | I <sub>DD</sub> 3  | V <sub>DD</sub>    | $V_{DD} = 5.5 V$ Output open,<br>External clock operating<br>mode<br>$f_{CK} = 300 \text{ kHz}$ $V_{IH}2 = 0.9V_{DD}$ $V_{IL}2 = 0.1V_{DD}$ |                            | 750                | 1500                       | μA   |

\* Electrical Characteristics might be changed for the improvement without notice.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### 1. When CL is stopped at the low level.

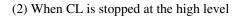

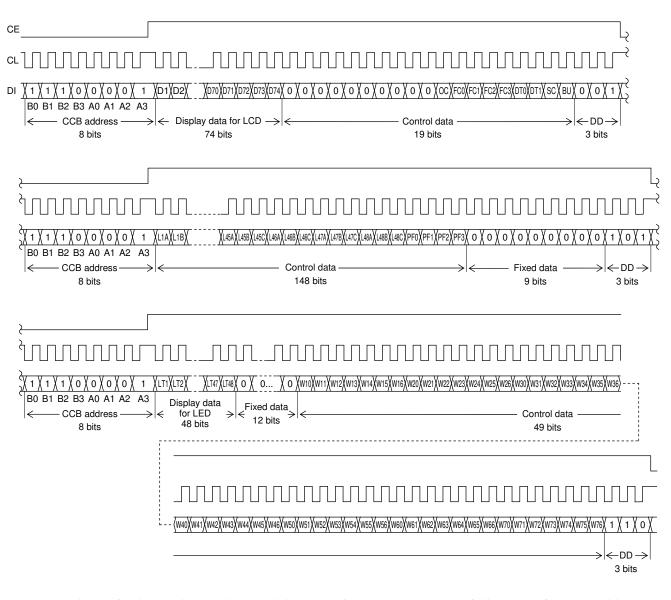

#### 2. When CL is stopped at the high level.

[Fig 2]

3. OSCI pin clock timing in external clock operating mode.

[Fig 3]

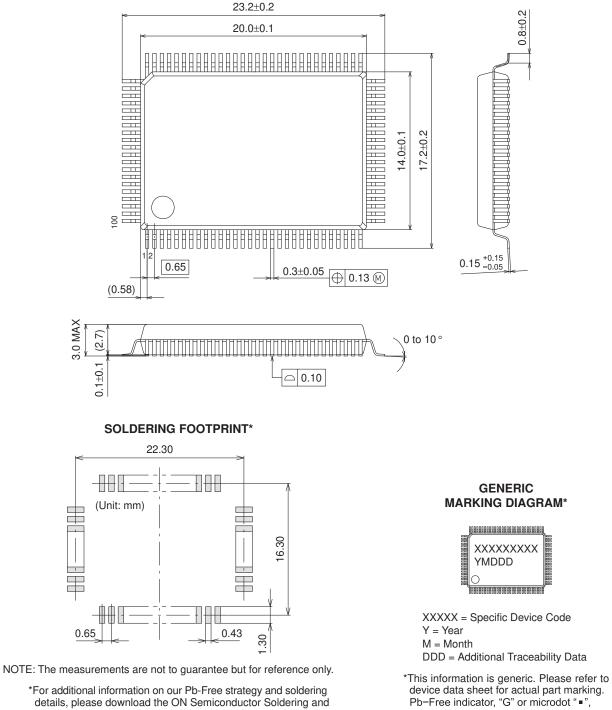

#### **Package Dimensions**

unit : mm

#### PQFP100 14x20 / QIP100E CASE 122BV

ISSUE A

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

may or may not be present.

Top view

#### **Block Diagram**

#### **Pin Functions**

| Symbol                                      | Pin No.                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Active | I/O | Handling<br>when<br>unused |

|---------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------------------------|

| LD1 to LD16<br>LD17 to LD32<br>LD33 to LD48 | 2 to 17<br>20 to 35<br>38 to 53       | These are LED driver output pins that display the display data for LED transferred<br>by serial data input, and high- voltage open-drain output pins. (Pull-up voltage is<br>30[V] maximum.) In addition, brightness adjustment of LED is possible by PWM<br>function, too.                                                                                                                                                                                                                                                                                                | -      | 0   | OPEN                       |

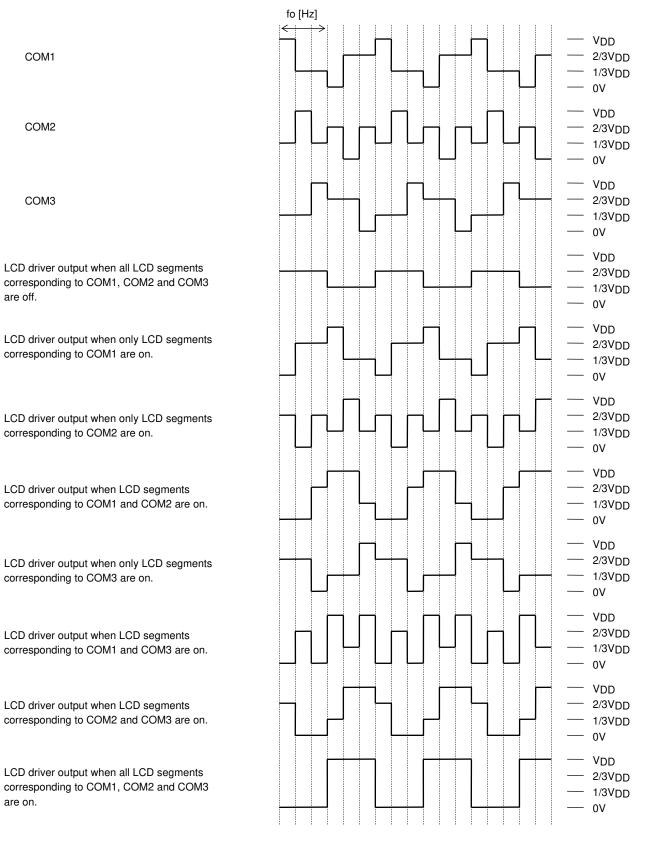

| COM1<br>COM2/S38<br>COM3/S37<br>COM4/S36    | 55<br>56<br>57<br>58                  | These are common driver output pins, and Frame frequency is fo [Hz].<br>COM2/S38, COM3/S37 and COM4/S36 are possible to be used as the segment<br>output by control data.                                                                                                                                                                                                                                                                                                                                                                                                  | -      | 0   | OPEN                       |

| S35 to S1                                   | 59 to 93                              | These are segment output pins that display the display data for LCD transferred by serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -      | 0   | OPEN                       |

| OSCI                                        | 96                                    | This is input pin for the external clock.<br>Input the clock whose frequency ( $f_{CK}$ ) is between 100 and 600[kHz] at external clock operating mode.<br>Furthermore, connect to GND at internal oscillator operating mode.                                                                                                                                                                                                                                                                                                                                              | -      | I   | GND                        |

| CE                                          | 98                                    | These are input pins for serial data transfer, and connect to the controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | н      | I   |                            |

| CL                                          | 99                                    | CE: Chip enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | I   | GND                        |

| DI                                          | 100                                   | CL: Synchronized clock<br>DI: Transfer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -      | I   |                            |

| ĪNH                                         | 97                                    | Display off control input pin<br>• INH = Low-level (V <sub>SS</sub> )Display forced off<br>LD1 to LD48 = Z (High-impedance)<br>COM1 = L (V <sub>SS</sub> )<br>COM2/S38 to COM4/S36 = L (V <sub>SS</sub> )<br>S1 to S35 = L (V <sub>SS</sub> )<br>Internal oscillator operation is stopped.<br>External clock input is forbidden.<br>• INH = High-level (V <sub>DD</sub> )Display on<br>Internal oscillator operation is possible.<br>(At Internal oscillator operating mode)<br>External clock operating mode)<br>However, serial data can be transferred during turn off. | L      | I   | GND                        |

| V <sub>DD</sub>                             | 94                                    | This is power supply pin.<br>Supply the voltage between 4.5V and 5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -      | -   | -                          |

| V <sub>SS</sub>                             | 1<br>18<br>19<br>36<br>37<br>54<br>95 | These are power supply pins.<br>Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -      | -   | -                          |

#### Serial Data Transfer Format

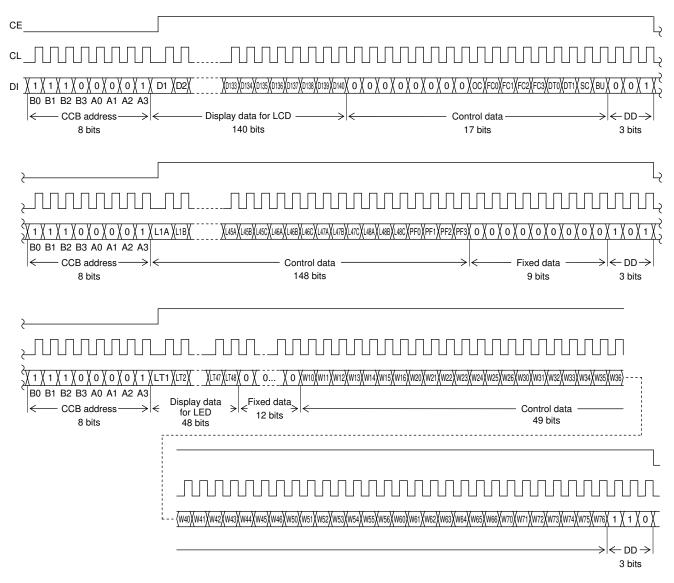

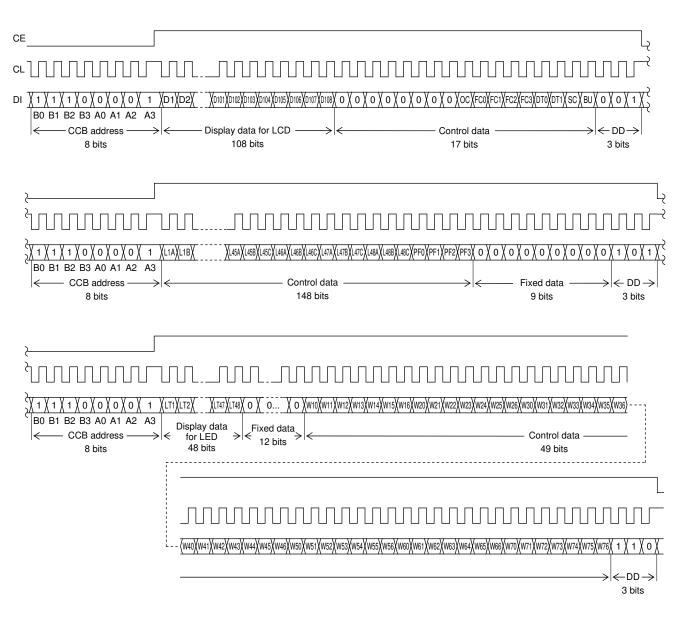

1/4 Duty Drive

(1) When CL is stopped at the low level

- (Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

- (Note 2) DD ••• Direction Data

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D140              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D140              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

|                           | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

|                           | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

|                           |                                                                                                 |

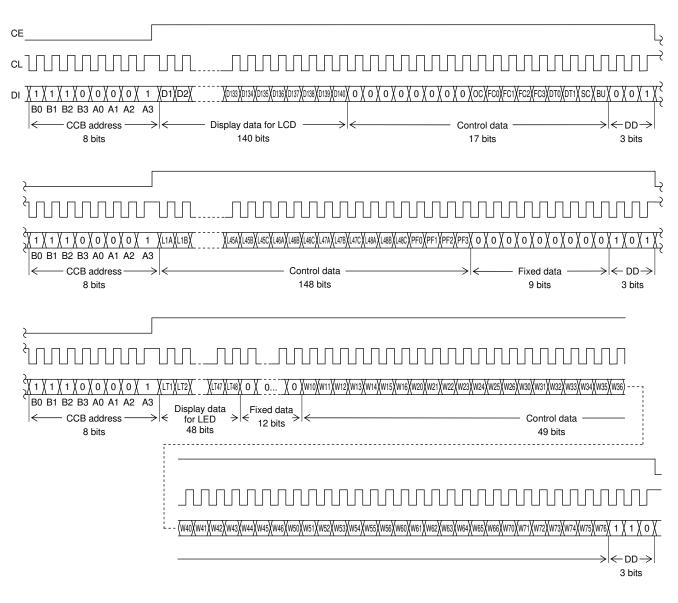

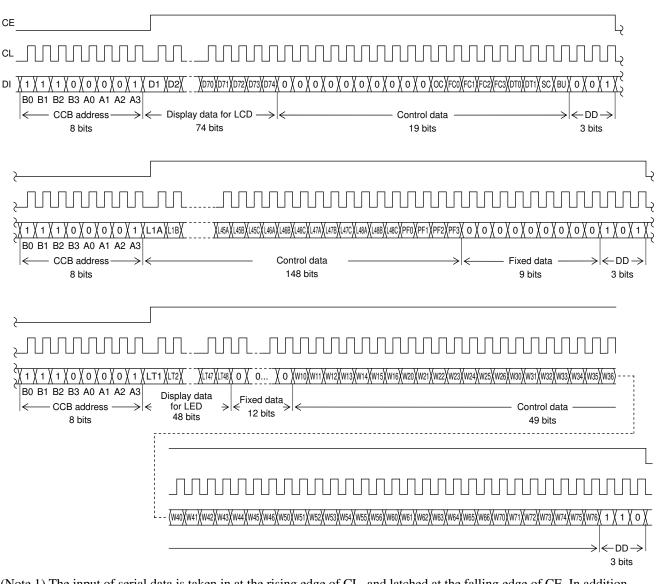

#### 1/3 Duty Drive

(1) When CL is stopped at the low level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D108              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

|                           |                                                                                                 |

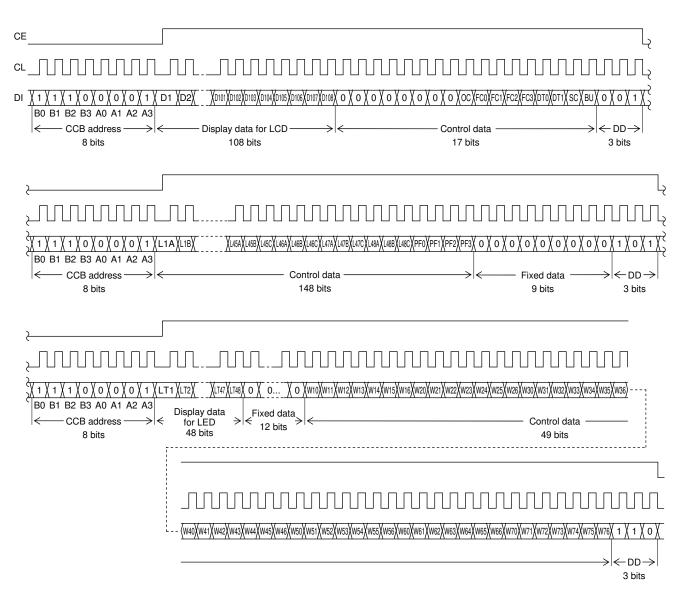

(2) When CL is stopped at the high level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address "87H"                                                                                  |

|------------------------------------------------------------------------------------------------------|

| • D1 to D108 Display data for LCD                                                                    |

| • OC Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3 Control data for setting of the frame frequency of common and segment output waveform   |

| • DT0, DT1 Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD |

| • SC Control data for turning on/off segments                                                        |

| • BU Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A, Control data for Ch settings of PWM circuits that adjust brightness of LED  |

| L48B, L48C                                                                                           |

| • PF0 to PF3 Control data for setting of the frame frequency of LED driver output waveform           |

| LT1 to LT48 Display data for LED                                                                     |

| • W10 to W16, W20 to W26, PWM data of PWM circuits of LED driver output                              |

| W30 to W36, W40 to W46,                                                                              |

| W50 to W56, W60 to W66                                                                               |

| W70 to W76                                                                                           |

|                                                                                                      |

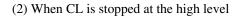

#### 1/2 Duty Drive

(1) When CL is stopped at the low level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address<br>• D1 to D74           | Display data for LCD                                                                                                                  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|                                        | Control data for switch of internal oscillator operating mode and external clock operating mode                                       |

|                                        | Control data for setting of the frame frequency of common and segment output waveform                                                 |

|                                        | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD<br>Control data for turning on/off segments |

| • BU                                   | Control data for switch of Normal mode and Power-saving mode                                                                          |

| • L1A, L1B, L1C to L48A,<br>L48B, L48C | Control data for Ch settings of PWM circuits that adjust brightness of LED                                                            |

| • PF0 to PF3                           | Control data for setting of the frame frequency of LED driver output waveform                                                         |

| • LT1 to LT48                          | Display data for LED                                                                                                                  |

| • W10 to W16, W20 to W26,              | PWM data of PWM circuits of LED driver output                                                                                         |

| W30 to W36, W40 to W46,                |                                                                                                                                       |

| W50 to W56, W60 to W66                 |                                                                                                                                       |

| W70 to W76                             |                                                                                                                                       |

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D74               | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

|                           | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

|                           | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

|                           |                                                                                                 |

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D38               | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

|                           | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

|                           | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

|                           | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             |                                                                                                 |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address           | "87H"                                                                                           |

|-------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D38             |                                                                                                 |

|                         | Control data for switch of internal oscillator operating mode and external clock operating mode |

|                         | Control data for setting of the frame frequency of common and segment output waveform           |

|                         | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

|                         | Control data for turning on/off segments                                                        |

|                         | Control data for switch of Normal mode and Power-saving mode                                    |

|                         | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C              |                                                                                                 |

| ,<br>,                  | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48           |                                                                                                 |

|                         | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46, |                                                                                                 |

| W50 to W56, W60 to W66  |                                                                                                 |

| W70 to W76              |                                                                                                 |

|                         |                                                                                                 |

#### **Control data Functions**

(1) OC ... Control data for switch of internal oscillator operating mode and external clock operating mode This control data bit selects either the internal oscillator operating mode or external clock operating mode.

| OC | Fundamental clock operating mode   | Input pin (OSCI) state                                                   |   |  |  |

|----|------------------------------------|--------------------------------------------------------------------------|---|--|--|

| 0  | Internal oscillator operating mode | Connect to GND                                                           |   |  |  |

| 1  | External clock operating mode      | Input the clock (f <sub>CK</sub> = 100 to 600 [kHz])<br>from the outside | ) |  |  |

#### (2) FC0 to FC3 ... Control data for setting of the frame frequency of common and segment output waveform. These control data bits set the frame frequency of common and segment output waveform.

| FC0 |     |     |     | Frame frequency of common and se                                                      | egment output waveform fo [Hz]                                                              |

|-----|-----|-----|-----|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|     | FC1 | FC2 | FC3 | Internal oscillator operating mode<br>(Control data OC ="0",<br>fosc = 300 [kHz] typ) | External clock operating mode<br>(Control data OC ="1",<br>f <sub>CK</sub> = 300 [kHz] typ) |

| 0   | 0   | 0   | 0   | fosc/4992                                                                             | f <sub>CK</sub> /4992                                                                       |

| 1   | 0   | 0   | 0   | fosc/4608                                                                             | f <sub>CK</sub> /4608                                                                       |

| 0   | 1   | 0   | 0   | fosc/4224                                                                             | f <sub>CK</sub> /4224                                                                       |

| 1   | 1   | 0   | 0   | fosc/3840                                                                             | f <sub>CK</sub> /3840                                                                       |

| 0   | 0   | 1   | 0   | fosc/3456                                                                             | f <sub>CK</sub> /3456                                                                       |

| 1   | 0   | 1   | 0   | fosc/3072                                                                             | f <sub>CK</sub> /3072                                                                       |

| 0   | 1   | 1   | 0   | fosc/2688                                                                             | f <sub>CK</sub> /2688                                                                       |

| 1   | 1   | 1   | 0   | fosc/2496                                                                             | f <sub>CK</sub> /2496                                                                       |

| 0   | 0   | 0   | 1   | fosc/2448                                                                             | f <sub>CK</sub> /2448                                                                       |

| 1   | 0   | 0   | 1   | fosc/2304                                                                             | f <sub>CK</sub> /2304                                                                       |

| 0   | 1   | 0   | 1   | fosc/2112                                                                             | f <sub>CK</sub> /2112                                                                       |

| 1   | 1   | 0   | 1   | fosc/1920                                                                             | f <sub>CK</sub> /1920                                                                       |

| 0   | 0   | 1   | 1   | fosc/1728                                                                             | f <sub>CK</sub> /1728                                                                       |

| 1   | 0   | 1   | 1   | fosc/1536                                                                             | f <sub>CK</sub> /1536                                                                       |

| 0   | 1   | 1   | 1   | fosc/1344                                                                             | f <sub>CK</sub> /1344                                                                       |

| 1   | 1   | 1   | 1   | fosc/1152                                                                             | f <sub>CK</sub> /1152                                                                       |

(3) DT0, DT1 ... Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD These control bits select 1/4-Duty 1/3-Bias Drive, 1/3-Duty 1/3-Bias Drive, 1/2-Duty 1/2-Bias Drive, or Static Drive (1/1-Duty Drive) of LCD.

| DTO | D.T.( |                               | Each pin state |          |          |  |  |  |

|-----|-------|-------------------------------|----------------|----------|----------|--|--|--|

| DT0 | DT1   | Drive scheme for LCD          | COM2/S38       | COM3/S37 | COM4/S36 |  |  |  |

| 0   | 0     | 1/4-Duty 1/3-Bias Drive       | COM2           | COM3     | COM4     |  |  |  |

| 1   | 0     | 1/3-Duty 1/3-Bias Drive       | COM2           | COM3     | S36      |  |  |  |

| 0   | 1     | 1/2-Duty 1/2-Bias Drive       | COM2           | S37      | S36      |  |  |  |

| 1   | 1     | Static Drive (1/1-Duty Drive) | S38            | S37      | S36      |  |  |  |

Note) COM2 to COM4: Common output / S38 to S36: Segment output

#### (4) SC ... Control data for turning on/off segments

This control data bit controls the on/off state of the segments.

| SC | Display state |  |  |  |  |  |

|----|---------------|--|--|--|--|--|

| 0  | On            |  |  |  |  |  |

| 1  | Off           |  |  |  |  |  |

Note that when the segments are turned off by setting SC to 1, the segments are turning off by outputting segment off waveforms from the segment output pins.

(5) BU ... Control data for switch of Normal mode and Power-saving mode

| This control data bit selects either Normal mode or Power-saving mode. |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| BU                                                                     | Mode                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| 0                                                                      | Normal mode                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 1                                                                      | Power-saving mode<br>The oscillation of internal oscillator circuit is stopped when internal oscillator operating mode (OC = [0]), and the receiving of external clock isn't admitted when external clock operating mode (OC = [1]). In addition, common and segment output pins are V <sub>SS</sub> level, and LED driver output pins are High impedance. |  |  |  |  |  |  |  |  |  |

(6) L1A, L1B, L1C to L48A, L48B, L48C ... Control data for Ch settings of PWM circuits that adjust brightness of LED These control data bits set the Ch of PWM circuit for LED driver output pins, LD1 to LD48.

| LnA | LnB | LnC | Ch of PWM circuit for LED driver output LDn                                                                               |

|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | PWM circuit is not selected.<br>(The setting of turning on/off of the duty 100% by Display data LTn for LED is possible.) |

| 1   | 0   | 0   | PWM circuit (Ch1) is selected.                                                                                            |

| 0   | 1   | 0   | PWM circuit (Ch2) is selected.                                                                                            |

| 1   | 1   | 0   | PWM circuit (Ch3) is selected.                                                                                            |

| 0   | 0   | 1   | PWM circuit (Ch4) is selected.                                                                                            |

| 1   | 0   | 1   | PWM circuit (Ch5) is selected.                                                                                            |

| 0   | 1   | 1   | PWM circuit (Ch6) is selected.                                                                                            |

| 1   | 1   | 1   | PWM circuit (Ch7) is selected.                                                                                            |

Note) LnA, LnB, LnC (n = 1 to 48) data are control data that set the Ch of PWM circuit for LED driver output pins LDn (n = 1 to 48).

For example, if (L1A, L1B, L1C) = (1, 0, 0), (L11A, L11B, L11C) = (1, 1, 0) and (L21A, L21B, L21C) = (0, 1, 1) is set, LED driver output pin LD1 select PWM circuit (Ch1) and LED driver output pin LD11 select PWM circuit (Ch3) and LED driver output pin LD21 select PWM circuit (Ch6).

(7) PF0 to PF3 ... Control data for setting of the frame frequency of LED driver output waveform These control data bits set the frame frequency of LED driver output waveform of LED output pin setting PWM circuit (Ch1 to Ch7).

|     |     |     |     | Frame frequency of LED drive                                                          | r output waveform fp [Hz]                                                                   |

|-----|-----|-----|-----|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| PF0 | PF1 | PF2 | PF3 | Internal oscillator operating mode<br>(Control data OC ="0",<br>fosc = 300 [kHz] typ) | External clock operating mode<br>(Control data OC ="1",<br>f <sub>CK</sub> = 300 [kHz] typ) |

| 0   | 0   | 0   | 0   | fosc/1664                                                                             | f <sub>CK</sub> /1664                                                                       |

| 1   | 0   | 0   | 0   | fosc/1536                                                                             | f <sub>CK</sub> /1536                                                                       |

| 0   | 1   | 0   | 0   | fosc/1408                                                                             | f <sub>CK</sub> /1408                                                                       |

| 1   | 1   | 0   | 0   | fosc/1280                                                                             | f <sub>CK</sub> /1280                                                                       |

| 0   | 0   | 1   | 0   | fosc/1152                                                                             | f <sub>CK</sub> /1152                                                                       |

| 1   | 0   | 1   | 0   | fosc/1024                                                                             | f <sub>CK</sub> /1024                                                                       |

| 0   | 1   | 1   | 0   | fosc/896                                                                              | f <sub>CK</sub> /896                                                                        |

| 1   | 1   | 1   | 0   | fosc/768                                                                              | f <sub>CK</sub> /768                                                                        |

| 0   | 0   | 0   | 1   | fosc/640                                                                              | f <sub>CK</sub> /640                                                                        |

| 1   | 0   | 0   | 1   | fosc/512                                                                              | f <sub>CK</sub> /512                                                                        |

Note) If (PF0, PF1, PF2, PF3) = (X, 1, 0, 1), (X, X, 1, 1) are set, the frame frequency (fosc/1408, fCK/1408) of setting (PF0, PF1, PF2, PF3) = (0, 1, 0, 0) is selected.

#### (8) W10 to W16, W20 to W26, W30 to W36, W40 to W46, W50 to W56, W60 to W66, W70 to W76

... PWM data of PWM circuit for LED driver output These control data bits set LED lighting time per 1 frame of LED driver output waveform of LED driver output pin setting PWM circuit (Ch1 to Ch7).

| outpu | t pin s | setting | ; PWN |       | uii (C |      |                                |      |        |     |     |     |     |     |     |                                |

|-------|---------|---------|-------|-------|--------|------|--------------------------------|------|--------|-----|-----|-----|-----|-----|-----|--------------------------------|

| Wn0   | Wn1     | Wn2     | Wn3   | Wn4   | Wn5    | Wn6  | LED lighting time              |      | Wn0    | Wn1 | Wn2 | Wn3 | Wn4 | Wn5 | Wn6 | LED lighting time              |

|       |         |         |       |       |        | -    | per 1 frame                    |      |        |     |     |     |     |     | _   | per 1 frame                    |

| 0     | 0       | 0       | 0     | 0     | 0      | 0    | (1/128) × Tp                   |      | 0      | 0   | 0   | 0   | 0   | 0   | 1   | (65/128) × Tp                  |

| 1     | 0       | 0       | 0     | 0     | 0      | 0    | (2/128) × Tp                   |      | 1      | 0   | 0   | 0   | 0   | 0   | 1   | (66/128) × Tp                  |

| 0     | 1       | 0       | 0     | 0     | 0      | 0    | (3/128) × Tp                   |      | 0      | 1   | 0   | 0   | 0   | 0   | 1   | (67/128) × Tp                  |

| 1     | 1       | 0       | 0     | 0     | 0      | 0    | (4/128) × Tp                   |      | 1      | 1   | 0   | 0   | 0   | 0   | 1   | (68/128) × Tp                  |

| 0     | 0       | 1       | 0     | 0     | 0      | 0    | (5/128) × Tp                   |      | 0      | 0   | 1   | 0   | 0   | 0   | 1   | (69/128) × Tp                  |

| 1     | 0       | 1       | 0     | 0     | 0      | 0    | (6/128) × Tp                   |      | 1      | 0   | 1   | 0   | 0   | 0   | 1   | (70/128) × Tp                  |

| 0     | 1       | 1       | 0     | 0     | 0      | 0    | (7/128) × Tp                   |      | 0      | 1   | 1   | 0   | 0   | 0   | 1   | (71/128) × Tp                  |

| 1     | 1       | 1       | 0     | 0     | 0      | 0    | (8/128) × Tp                   |      | 1      | 1   | 1   | 0   | 0   | 0   | 1   | (72/128) × Tp                  |

| 0     | 0       | 0       | 1     | 0     | 0      | 0    | (9/128) × Tp                   |      | 0      | 0   | 0   | 1   | 0   | 0   | 1   | (73/128) × Tp                  |

| 1     | 0       | 0       | 1     | 0     | 0      | 0    | (10/128) × Tp                  |      | 1      | 0   | 0   | 1   | 0   | 0   | 1   | (74/128) × Tp                  |

| 0     | 1       | 0       | 1     | 0     | 0      | 0    | (11/128) × Tp                  |      | 0      | 1   | 0   | 1   | 0   | 0   | 1   | (75/128) × Tp                  |

|       | 0       | 1       | 1     | 0     | 0      | 0    | (12/128) × Tp<br>(13/128) × Tp |      | 1      | 0   | 1   | 1   | 0   | 0   | 1   | (76/128) × Tp                  |

| 0     | 0       | 1       | 1     | 0     | 0      | 0    | (13/128) × Tp<br>(14/128) × Tp |      | 1      | 0   | 1   | 1   | 0   | 0   | 1   | (77/128) × Tp                  |

| 0     | 1       | 1       | 1     | 0     | 0      | 0    | (14/128) × Tp<br>(15/128) × Tp |      | 0      | 1   | 1   | 1   | 0   | 0   | 1   | (78/128) × Tp<br>(70/128) × Tp |

| 1     | 1       | 1       | 1     | 0     | 0      | 0    | (16/128) × Tp<br>(16/128) × Tp |      | 1      | 1   | 1   | 1   | 0   | 0   | 1   | (79/128) × Tp                  |

| 0     | 0       | 0       | 0     | 1     | 0      | 0    | (17/128) × Tp<br>(17/128) × Tp |      | 0      | 0   | 0   | 0   | 1   | 0   | 1   | (80/128) × Tp<br>(81/128) × Tp |

| 1     | 0       | 0       | 0     | 1     | 0      | 0    | (17/128) × Tp<br>(18/128) × Tp |      | 1      | 0   | 0   | 0   | 1   | 0   | 1   | (82/128) × Tp<br>(82/128) × Tp |

| 0     | 1       | 0       | 0     | 1     | 0      | 0    | (19/128) × Tp<br>(19/128) × Tp |      | 0      | 1   | 0   | 0   | 1   | 0   | 1   | · / /                          |

| 1     | 1       | 0       | 0     | 1     | 0      | 0    | (19/128) × Tp<br>(20/128) × Tp |      | 1      | 1   | 0   | 0   | 1   | 0   | 1   | (83/128) × Tp<br>(84/128) × Tp |

| 0     | 0       | 1       | 0     | 1     | 0      | 0    | (20/128) × Tp<br>(21/128) × Tp |      | 0      | 0   | 1   | 0   | 1   | 0   | 1   | (84/128) × Tp<br>(85/128) × Tp |

| 1     | 0       | 1       | 0     | 1     | 0      | 0    | (22/128) × Tp<br>(22/128) × Tp |      | 1      | 0   | 1   | 0   | 1   | 0   | 1   | (86/128) × Tp<br>(86/128) × Tp |

| 0     | 1       | 1       | 0     | 1     | 0      | 0    | · · · ·                        |      | 0      | 1   | 1   | 0   | 1   | 0   | 1   | · / /                          |

| 1     | 1       | 1       | 0     | 1     | 0      | 0    | (23/128) × Tp<br>(24/128) × Tp |      | 1      | 1   | 1   | 0   | 1   | 0   | 1   | (87/128) × Tp<br>(88/128) × Tp |

| 0     | 0       | 0       | 1     | 1     | 0      | 0    | (25/128) × Tp                  |      | 0      | 0   | 0   | 1   | 1   | 0   | 1   | (89/128) × Tp<br>(89/128) × Tp |

| 1     | 0       | 0       | 1     | 1     | 0      | 0    | (26/128) × Tp                  |      | 1      | 0   | 0   | 1   | 1   | 0   | 1   | (90/128) × Tp                  |

| 0     | 1       | 0       | 1     | 1     | 0      | 0    | (27/128) × Tp                  |      | 0      | 1   | 0   | 1   | 1   | 0   | 1   | (91/128) × Tp                  |

| 1     | 1       | 0       | 1     | 1     | 0      | 0    | (28/128) × Tp                  |      | 1      | 1   | 0   | 1   | 1   | 0   | 1   | (92/128) × Tp                  |

| 0     | 0       | 1       | 1     | 1     | 0      | 0    | (29/128) × Tp                  |      | 0      | 0   | 1   | 1   | 1   | 0   | 1   | (93/128) × Tp                  |

| 1     | 0       | 1       | 1     | 1     | 0      | 0    | (30/128) × Tp                  |      | 1      | 0   | 1   | 1   | 1   | 0   | 1   | (94/128) × Tp                  |

| 0     | 1       | 1       | 1     | 1     | 0      | 0    | (31/128) × Tp                  |      | 0      | 1   | 1   | 1   | 1   | 0   | 1   | (95/128) × Tp                  |

| 1     | 1       | 1       | 1     | 1     | 0      | 0    | (32/128) × Tp                  |      | 1      | 1   | 1   | 1   | 1   | 0   | 1   | (96/128) × Tp                  |

| 0     | 0       | 0       | 0     | 0     | 1      | 0    | (33/128) × Tp                  |      | 0      | 0   | 0   | 0   | 0   | 1   | 1   | (97/128) × Tp                  |

| 1     | 0       | 0       | 0     | 0     | 1      | 0    | (34/128) × Tp                  |      | 1      | 0   | 0   | 0   | 0   | 1   | 1   | (98/128) × Tp                  |

| 0     | 1       | 0       | 0     | 0     | 1      | 0    | (35/128) × Tp                  |      | 0      | 1   | 0   | 0   | 0   | 1   | 1   | (99/128) × Tp                  |

| 1     | 1       | 0       | 0     | 0     | 1      | 0    | (36/128) × Tp                  |      | 1      | 1   | 0   | 0   | 0   | 1   | 1   | (100/128) × Tp                 |

| 0     | 0       | 1       | 0     | 0     | 1      | 0    | (37/128) × Tp                  |      | 0      | 0   | 1   | 0   | 0   | 1   | 1   | (101/128) × Tp                 |

| 1     | 0       | 1       | 0     | 0     | 1      | 0    | (38/128) × Tp                  |      | 1      | 0   | 1   | 0   | 0   | 1   | 1   | (102/128) × Tp                 |

| 0     | 1       | 1       | 0     | 0     | 1      | 0    | (39/128) × Tp                  |      | 0      | 1   | 1   | 0   | 0   | 1   | 1   | (103/128) × Tp                 |

| 1     | 1       | 1       | 0     | 0     | 1      | 0    | (40/128) × Tp                  |      | 1      | 1   | 1   | 0   | 0   | 1   | 1   | (104/128) × Tp                 |

| 0     | 0       | 0       | 1     | 0     | 1      | 0    | (41/128) × Tp                  |      | 0      | 0   | 0   | 1   | 0   | 1   | 1   | (105/128) × Tp                 |

| 1     | 0       | 0       | 1     | 0     | 1      | 0    | (42/128) × Tp                  |      | 1      | 0   | 0   | 1   | 0   | 1   | 1   | (106/128) × Tp                 |

| 0     | 1       | 0       | 1     | 0     | 1      | 0    | (43/128) × Tp                  |      | 0      | 1   | 0   | 1   | 0   | 1   | 1   | (107/128) × Tp                 |

| 1     | 1       | 0       | 1     | 0     | 1      | 0    | (44/128) × Tp                  |      | 1      | 1   | 0   | 1   | 0   | 1   | 1   | (108/128) × Tp                 |

| 0     | 0       | 1       | 1     | 0     | 1      | 0    | (45/128) × Tp                  |      | 0      | 0   | 1   | 1   | 0   | 1   | 1   | (109/128) × Tp                 |

| 1     | 0       | 1       | 1     | 0     | 1      | 0    | (46/128) × Tp                  |      | 1      | 0   | 1   | 1   | 0   | 1   | 1   | (110/128) × Tp                 |

| 0     | 1       | 1       | 1     | 0     | 1      | 0    | (47/128) × Tp                  |      | 0      | 1   | 1   | 1   | 0   | 1   | 1   | (111/128) × Tp                 |

| 1     | 1       | 1       | 1     | 0     | 1      | 0    | (48/128) × Tp                  |      | 1      | 1   | 1   | 1   | 0   | 1   | 1   | (112/128) × Tp                 |

| 0     | 0       | 0       | 0     | 1     | 1      | 0    | (49/128) × Tp                  |      | 0      | 0   | 0   | 0   | 1   | 1   | 1   | (113/128) × Tp                 |

| 1     | 0       | 0       | 0     | 1     | 1      | 0    | (50/128) × Tp                  |      | 1      | 0   | 0   | 0   | 1   | 1   | 1   | (114/128) × Tp                 |

| 0     | 1       | 0       | 0     | 1     | 1      | 0    | (51/128) × Tp                  |      | 0      | 1   | 0   | 0   | 1   | 1   | 1   | (115/128) × Tp                 |

| 1     | 1       | 0       | 0     | 1     | 1      | 0    | (52/128) × Tp                  |      | 1      | 1   | 0   | 0   | 1   | 1   | 1   | (116/128) × Tp                 |

| 0     | 0       | 1       | 0     | 1     | 1      | 0    | (53/128) × Tp                  |      | 0      | 0   | 1   | 0   | 1   | 1   | 1   | (117/128) × Tp                 |

| 1     | 0       | 1       | 0     | 1     | 1      | 0    | (54/128) × Tp                  |      | 1      | 0   | 1   | 0   | 1   | 1   | 1   | (118/128) × Tp                 |

| 0     | 1       | 1       | 0     | 1     | 1      | 0    | (55/128) × Tp                  |      | 0      | 1   | 1   | 0   | 1   | 1   | 1   | (119/128) × Tp                 |

| 1     | 1       | 1       | 0     | 1     | 1      | 0    | (56/128) × Tp                  |      | 1      | 1   | 1   | 0   | 1   | 1   | 1   | (120/128) × Tp                 |

| 0     | 0       | 0       | 1     | 1     | 1      | 0    | (57/128) × Tp                  |      | 0      | 0   | 0   | 1   | 1   | 1   | 1   | (121/128) × Tp                 |

| 1     | 0       | 0       | 1     | 1     | 1      | 0    | (58/128) × Tp                  |      | 1      | 0   | 0   | 1   | 1   | 1   | 1   | (122/128) × Tp                 |

| 0     | 1       | 0       | 1     | 1     | 1      | 0    | (59/128) × Tp                  |      | 0      | 1   | 0   | 1   | 1   | 1   | 1   | (123/128) × Tp                 |

| 1     | 1       | 0       | 1     | 1     | 1      | 0    | (60/128) × Tp                  |      | 1      | 1   | 0   | 1   | 1   | 1   | 1   | (124/128) × Tp                 |

| 0     | 0       | 1       | 1     | 1     | 1      | 0    | (61/128) × Tp                  |      | 0      | 0   | 1   | 1   | 1   | 1   | 1   | (125/128) × Tp                 |

| 1     | 0       | 1       | 1     | 1     | 1      | 0    | (62/128) × Tp                  |      | 1      | 0   | 1   | 1   | 1   | 1   | 1   | (126/128) × Tp                 |

| 0     | 1       | 1       | 1     | 1     | 1      | 0    | (63/128) × Tp                  |      | 0      | 1   | 1   | 1   | 1   | 1   | 1   | (127/128) × Tp                 |

| 1     | 1       | 1       | 1     | 1     | 1      | 0    | (64/128) × Tp                  |      | 1      | 1   | 1   | 1   | 1   | 1   | 1   | (128/128) × Tp                 |

| T>    | 11/10   |         |       | 173.6 | 1      | DITA | A circuit (Ch1)/               | 1170 | 0 · 11 |     |     | 1 . | CDW | a   | •   | <b>31.6</b>                    |

Note) W10 to W16 : PWM data of PWM circuit (Ch1) / W20 to W26 : PWM data of PWM circuit (Ch2) W30 to W36 : PWM data of PWM circuit (Ch3) / W40 to W46 : PWM data of PWM circuit (Ch4) W50 to W56 : PWM data of PWM circuit (Ch5) / W60 to W66 : PWM data of PWM circuit (Ch6) W70 to W76 : PWM data of PWM circuit (Ch7)

$Tp = \frac{1}{fp}$

## Descriptions of Display data for LCD

(1) Correspondence of output pins to display data for LCD at 1/4 Duty Drive

|            |      | 1    |      |      |

|------------|------|------|------|------|

| Output Pin | COM1 | COM2 | COM3 | COM4 |

| S1         | D1   | D2   | D3   | D4   |

| S2         | D5   | D6   | D7   | D8   |

| S3         | D9   | D10  | D11  | D12  |

| S4         | D13  | D14  | D15  | D16  |

| S5         | D17  | D18  | D19  | D20  |

| S6         | D21  | D22  | D23  | D24  |

| S7         | D25  | D26  | D27  | D28  |

| S8         | D29  | D30  | D31  | D32  |

| S9         | D33  | D34  | D35  | D36  |

| S10        | D37  | D38  | D39  | D40  |

| S11        | D41  | D42  | D43  | D44  |

| S12        | D45  | D46  | D47  | D48  |

| S13        | D49  | D50  | D51  | D52  |

| S14        | D53  | D54  | D55  | D56  |

| S15        | D57  | D58  | D59  | D60  |

| S16        | D61  | D62  | D63  | D64  |

| S17        | D65  | D66  | D67  | D68  |

| S18        | D69  | D70  | D71  | D72  |

| Output Pin | COM1 | COM2 | COM3 | COM4 |

|------------|------|------|------|------|

| S19        | D73  | D74  | D75  | D76  |

| S20        | D77  | D78  | D79  | D80  |

| S21        | D81  | D82  | D83  | D84  |

| S22        | D85  | D86  | D87  | D88  |

| S23        | D89  | D90  | D91  | D92  |

| S24        | D93  | D94  | D95  | D96  |

| S25        | D97  | D98  | D99  | D100 |

| S26        | D101 | D102 | D103 | D104 |

| S27        | D105 | D106 | D107 | D108 |

| S28        | D109 | D110 | D111 | D112 |

| S29        | D113 | D114 | D115 | D116 |

| S30        | D117 | D118 | D119 | D120 |

| S31        | D121 | D122 | D123 | D124 |

| S32        | D125 | D126 | D127 | D128 |

| S33        | D129 | D130 | D131 | D132 |

| S34        | D133 | D134 | D135 | D136 |

| S35        | D137 | D138 | D139 | D140 |

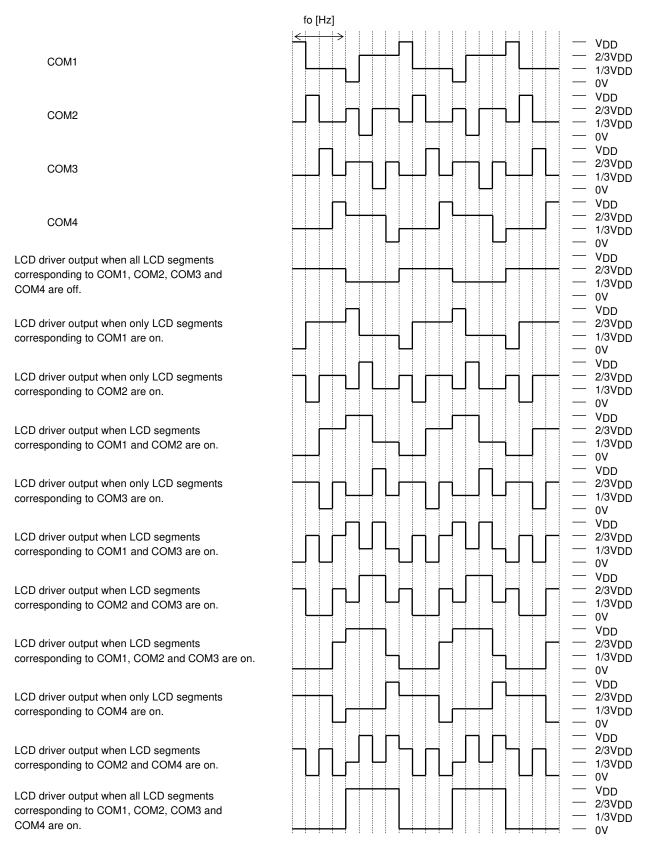

For example, the table below lists the output states for the S21 output pin.

| Display data |     |     |     |                                                                      |  |  |  |

|--------------|-----|-----|-----|----------------------------------------------------------------------|--|--|--|

| D81          | D82 | D83 | D84 | Output pin (S21) state                                               |  |  |  |

| 0            | 0   | 0   | 0   | The LCD segments corresponding to COM1, COM2, COM3 and COM4 are off. |  |  |  |

| 0            | 0   | 0   | 1   | The LCD segment corresponding to COM4 is on.                         |  |  |  |

| 0            | 0   | 1   | 0   | The LCD segment corresponding to COM3 is on.                         |  |  |  |

| 0            | 0   | 1   | 1   | The LCD segments corresponding to COM3 and COM4 are on.              |  |  |  |

| 0            | 1   | 0   | 0   | The LCD segment corresponding to COM2 is on.                         |  |  |  |

| 0            | 1   | 0   | 1   | The LCD segments corresponding to COM2 and COM4 are on.              |  |  |  |

| 0            | 1   | 1   | 0   | The LCD segments corresponding to COM2 and COM3 are on.              |  |  |  |

| 0            | 1   | 1   | 1   | The LCD segments corresponding to COM2, COM3 and COM4 are on.        |  |  |  |

| 1            | 0   | 0   | 0   | The LCD segment corresponding to COM1 is on.                         |  |  |  |

| 1            | 0   | 0   | 1   | The LCD segments corresponding to COM1 and COM4 are on.              |  |  |  |

| 1            | 0   | 1   | 0   | The LCD segments corresponding to COM1 and COM3 are on.              |  |  |  |

| 1            | 0   | 1   | 1   | The LCD segments corresponding to COM1, COM3 and COM4 are on.        |  |  |  |

| 1            | 1   | 0   | 0   | The LCD segments corresponding to COM1 and COM2 are on.              |  |  |  |

| 1            | 1   | 0   | 1   | The LCD segments corresponding to COM1, COM2 and COM4 are on.        |  |  |  |

| 1            | 1   | 1   | 0   | The LCD segments corresponding to COM1, COM2 and COM3 are on.        |  |  |  |

| 1            | 1   | 1   | 1   | The LCD segments corresponding to COM1, COM2, COM3 and COM4 are on.  |  |  |  |

| (2) | Correspondence | e of outpu | t pins to | display | data fo | or LCD | at 1/3 D | uty Drive |  |

|-----|----------------|------------|-----------|---------|---------|--------|----------|-----------|--|

|     |                |            |           |         |         |        |          |           |  |

| Output Pin | COM1 | COM2 | COM3 |

|------------|------|------|------|

| S1         | D1   | D2   | D3   |

| S2         | D4   | D5   | D6   |

| S3         | D7   | D8   | D9   |

| S4         | D10  | D11  | D12  |

| S5         | D13  | D14  | D15  |

| S6         | D16  | D17  | D18  |

| S7         | D19  | D20  | D21  |

| S8         | D22  | D23  | D24  |

| S9         | D25  | D26  | D27  |

| S10        | D28  | D29  | D30  |

| S11        | D31  | D32  | D33  |

| S12        | D34  | D35  | D36  |