# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

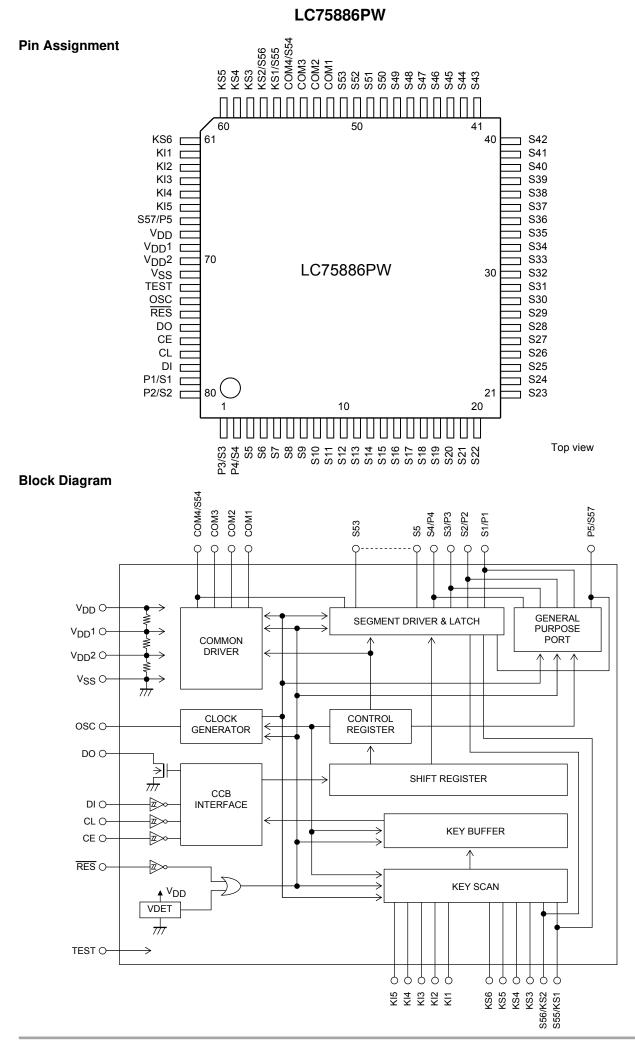

# 1/4, 1/3-Duty LCD Driver with Key Input Function

#### Overview

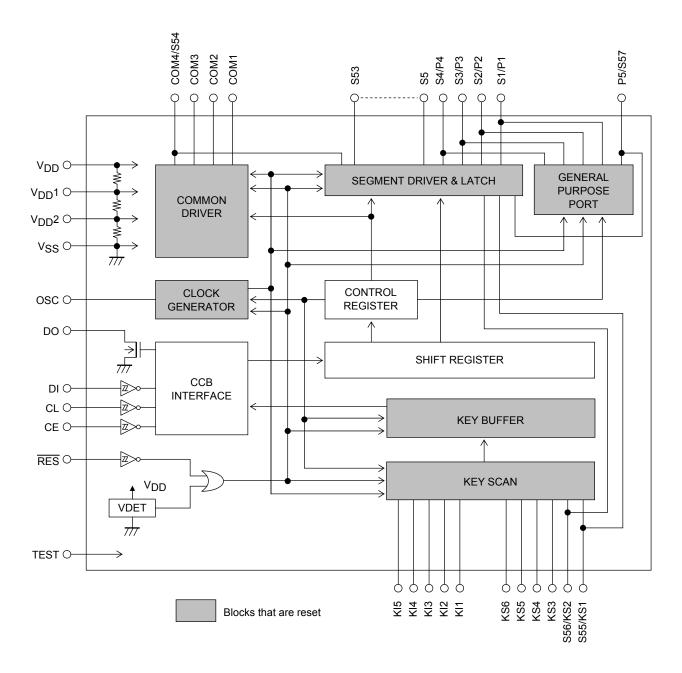

The LC75886PW is 1/4 duty and 1/3 duty LCD display driver that can directly drive up to 224 segments and can control up to 5 generalpurpose output ports. This product also incorporates a key scan circuit that accepts input from up to 30 keys to reduce printed circuit board wiring.

#### Features

- Key input function for up to 30 keys (A key scan is performed only when a key is pressed.)

- 1/4 duty 1/3 bias and 1/3 duty 1/3 bias drive schemes can be controlled from serial data.

- Capable of driving up to 224 segments using 1/4 duty and up to 171 segments using 1/3 duty.

- Switching between key scan output and segment output can be controlled from serial data.

- The key scan operation enabled/disabled state can be controlled from serial data.

- Switching between segment output port and general-purpose output port can be controlled from serial data.

- Switching between general-purpose output port, clock output port, and segment output port can be controlled from serial data.

- (Up to 5 general-purpose output ports and up to one clock output port) • Serial data I/O supports CCB\* format communication with the system controller. (Support 3.3 V and 5 V operation)

- Sleep mode and all segments off functions that are controlled from serial data.

- The frame frequency of the common and segment output waveforms can be controlled from serial data.

- Switching between RC oscillator operating mode and external clock operationg mode can be controlled from serial data.

- Direct display of display data without the use of a decoder provides high generality.

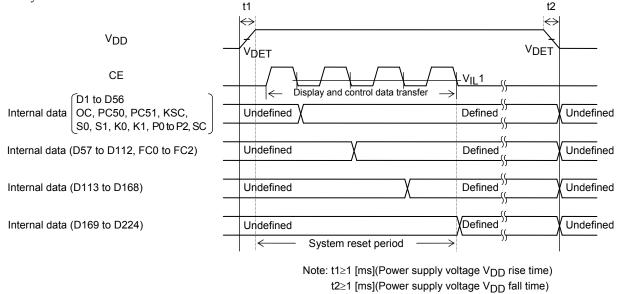

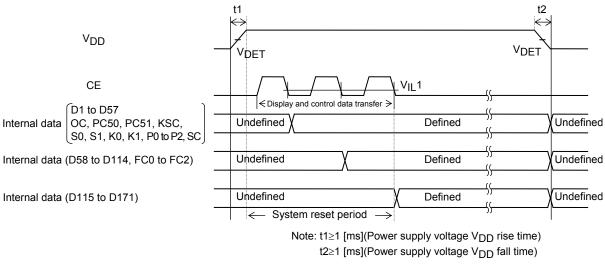

- Provision of an on-chip voltage-detection type reset circuit prevents incorrect displays.

- $\overline{\text{RES}}$  pin provided for forcibly initializing the IC internal circuits.

# **ON Semiconductor®**

www.onsemi.com

SQFP80 12x12 / SQFP80

\* Computer Control Bus (CCB) is an ON Semiconductor's original bus format and the bus addresses are controlled by ON Semiconductor.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 36 of this data sheet.

#### Specifications Absolute Maximum Ratings at Ta = 25°C, V<sub>SS</sub> = 0 V

| Parameter                   | Symbol              | Conditions                                                  | Ratings                      | Unit |

|-----------------------------|---------------------|-------------------------------------------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>                                             | -0.3 to +7.0                 | V    |

| Input voltage               | V <sub>IN</sub> 1   | CE, CL, DI, RES                                             | -0.3 to +7.0                 | v    |

|                             | V <sub>IN</sub> 2   | OSC, TEST, V <sub>DD</sub> 1, V <sub>DD</sub> 2, KI1 to KI5 | –0.3 to V <sub>DD</sub> +0.3 | v    |

| Output voltage              | V <sub>OUT</sub> 1  | DO                                                          | -0.3 to +7.0                 |      |

|                             | V <sub>OUT</sub> 2  | OSC, S1 to S57, COM1 to COM4, KS1 to KS6,<br>P1 to P5       | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current              | IOUT1               | S1 to S57                                                   | 300                          | μA   |

|                             | IOUT2               | COM1 to COM4                                                | 3                            |      |

|                             | IOUT3               | KS1 to KS6                                                  | 1                            | mA   |

|                             | IOUT <sup>4</sup>   | P1 to P5                                                    | 5                            |      |

| Allowable power dissipation | Pd max              | Ta = 85°C                                                   | 200                          | mW   |

| Operating temperature       | Topr                |                                                             | -40 to +85                   | °C   |

| Storage temperature         | Tstg                |                                                             | -55 to +125                  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Allowable Operating Ranges at Ta = -40 to +85°C, V<sub>SS</sub> = 0 V

| Deveryoter                                        | Quere hal         |                                                                               |                    |                    |                    |      |

|---------------------------------------------------|-------------------|-------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| Parameter                                         | Symbol            | Conditions                                                                    | min                | typ                | max                | Unit |

| Supply voltage                                    | V <sub>DD</sub>   | V <sub>DD</sub>                                                               | 4.5                |                    | 6.0                | V    |

| Input voltage                                     | V <sub>DD</sub> 1 | V <sub>DD</sub> 1                                                             |                    | 2/3V <sub>DD</sub> | V <sub>DD</sub>    |      |

|                                                   | V <sub>DD</sub> 2 | V <sub>DD</sub> 2                                                             |                    | 1/3V <sub>DD</sub> | V <sub>DD</sub>    | V    |

| Input high level voltage                          | V <sub>IH</sub> 1 | CE, CL, DI, RES                                                               | 0.4V <sub>DD</sub> |                    | 6.0                |      |

|                                                   | V <sub>IH</sub> 2 | KI1 to KI5                                                                    | 0.6V <sub>DD</sub> |                    | V <sub>DD</sub>    | V    |

|                                                   | V <sub>IH</sub> 3 | OSC: External clock operating mode                                            | 0.4V <sub>DD</sub> |                    | V <sub>DD</sub>    |      |

| Input low level voltage                           | V <sub>IL</sub> 1 | CE, CL, DI, RES                                                               | 0                  |                    | 0.2V <sub>DD</sub> |      |

|                                                   | V <sub>IL</sub> 2 | KI1 to KI5                                                                    | 0                  |                    | 0.2V <sub>DD</sub> | V    |

|                                                   | V <sub>IL</sub> 3 | OSC: External clock operating mode                                            | 0                  |                    | 0.2V <sub>DD</sub> |      |

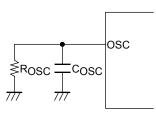

| Recommended external resistor for RC oscillation  | R <sub>OSC</sub>  | OSC: RC oscillation operating mode                                            |                    | 39                 |                    | kΩ   |

| Recommended external capacitor for RC oscillation | COSC              | OSC: RC oscillation operating mode                                            |                    | 1000               |                    | pF   |

| Guaranteed range of RC oscillation                | fosc              | OSC: RC oscillation operating mode                                            | 19                 | 38                 | 76                 | kHz  |

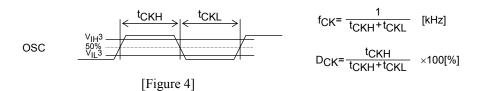

| External clock operating frequency                | fCK               | OSC: External clock operating mode<br>[Figure4]                               | 10                 | 38                 | 76                 | kHz  |

| External clock duty cycle                         | РСК               | OSC: External clock operating mode<br>[Figure4]                               | 30                 | 50                 | 70                 | %    |

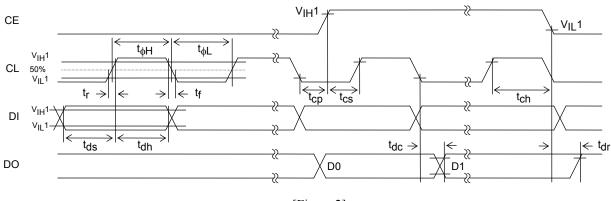

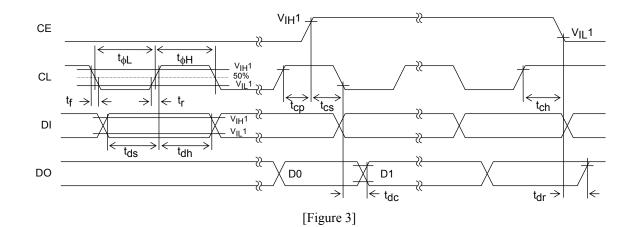

| Data setup time                                   | t <sub>ds</sub>   | CL, DI [Figure2], [Figure3]                                                   | 160                |                    |                    | ns   |

| Data hold time                                    | <sup>t</sup> dh   | CL, DI [Figure2], [Figure3]                                                   | 160                |                    |                    | ns   |

| CE wait time                                      | t <sub>cp</sub>   | CE, CL [Figure2], [Figure3]                                                   | 160                |                    |                    | ns   |

| CE setup time                                     | t <sub>cs</sub>   | CE, CL [Figure2], [Figure3]                                                   | 160                |                    |                    | ns   |

| CE hold time                                      | <sup>t</sup> ch   | CE, CL [Figure2], [Figure3]                                                   | 160                |                    |                    | ns   |

| High level clock pulse width                      | t <sub>∲H</sub>   | CL [Figure2], [Figure3]                                                       | 160                |                    |                    | ns   |

| Low level clock pulse width                       | t <sub>oL</sub>   | CL [Figure2], [Figure3]                                                       | 160                |                    |                    | ns   |

| Rise time                                         | tr                | CE, CL, DI [Figure2], [Figure3]                                               |                    | 160                |                    | ns   |

| Fall time                                         | tf                | CE, CL, DI [Figure2], [Figure3]                                               |                    | 160                |                    | ns   |

| DO output deley time                              | <sup>t</sup> dc   | DO R <sub>PU</sub> = 4.7 kΩ C <sub>L</sub> = 10 pF *1<br>[Figure2], [Figure3] |                    |                    | 1.5                | μS   |

| DO rise time                                      | <sup>t</sup> dr   | DO R <sub>PU</sub> = 4.7 kΩ C <sub>L</sub> = 10 pF *1<br>[Figure2], [Figure3] |                    |                    | 1.5                | μS   |

Note: \*1 Since the DO pin is an open-drain output, these times depend on the values of the pull-up resistor  $R_{PU}$  and the load capacitance  $C_L$ .

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Electrical Characteristics for the Allowable Operating Ranges**

| Parameter                       | Symbol             | Pin             | Conditions                                                                                                                                           |                            | Ratings              |                            | Un  |

|---------------------------------|--------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|----------------------------|-----|

|                                 | -                  | 1 111           | Conditions                                                                                                                                           | min                        | typ                  | max                        | 011 |

| Hysteresis                      | V <sub>H</sub> 1   | CE, CL, DI, RES |                                                                                                                                                      |                            | 0.03V <sub>DD</sub>  |                            | v   |

|                                 | V <sub>H</sub> 2   | KI1 to KI5      |                                                                                                                                                      |                            | 0.1V <sub>DD</sub>   |                            | v   |

| Power-down<br>detection voltage | VDET               |                 |                                                                                                                                                      | 2.0                        | 2.3                  | 2.6                        | V   |

| Input high level                | IIH1               | CE, CL, DI, RES | V <sub>I</sub> = 6.0 V                                                                                                                               |                            |                      | 5.0                        |     |

| current                         | I <sub>IH</sub> 2  | OSC             | V <sub>I</sub> = V <sub>DD</sub> : External clock<br>operating mode                                                                                  |                            |                      | 5.0                        | μ/  |

| Input low level                 | կլ1                | CE, CL, DI, RES | V <sub>I</sub> = 0 V                                                                                                                                 | -5.0                       |                      |                            |     |

| current                         | I <sub>IL</sub> 2  | OSC             | V <sub>I</sub> = 0 V : External clock<br>operating mode                                                                                              | -5.0                       |                      |                            | μ/  |

| Input floating voltage          | VIF                | KI1 to KI5      |                                                                                                                                                      |                            |                      | 0.05V <sub>DD</sub>        | V   |

| Pull-down<br>resistance         | RPD                | KI1 to KI5      | V <sub>DD</sub> = 5.0 V                                                                                                                              | 50                         | 100                  | 250                        | k۵  |

| Output off leakage current      | IOFFH              | DO              | V <sub>O</sub> = 6.0 V                                                                                                                               |                            |                      | 6.0                        | μ   |

| Output high level               | V <sub>OH</sub> 1  | KS1 to KS6      | I <sub>O</sub> = –500 μA                                                                                                                             | V <sub>DD</sub> -1.0       | V <sub>DD</sub> -0.5 | V <sub>DD</sub> -0.2       | ļ   |

| voltage                         | V <sub>OH</sub> 2  | P1 to P5        | I <sub>O</sub> = -1 mA                                                                                                                               | V <sub>DD</sub> -0.9       |                      |                            |     |

|                                 | VOH3               | S1 to S57       | I <sub>O</sub> = -20 μA                                                                                                                              | V <sub>DD</sub> -0.9       |                      |                            | v   |

|                                 | V <sub>OH</sub> 4  | COM1 to COM4    | I <sub>O</sub> = -100 μA                                                                                                                             | V <sub>DD</sub> -0.9       |                      |                            |     |

| Output low level                | V <sub>OL</sub> 1  | KS1 to KS6      | I <sub>O</sub> = 25 μA                                                                                                                               | 0.2                        | 0.5                  | 1.5                        | V   |

| voltage                         | V <sub>OL</sub> 2  | P1 to P5        | I <sub>O</sub> = 1 mA                                                                                                                                |                            |                      | 0.9                        |     |

|                                 | V <sub>OL</sub> 3  | S1 to S57       | I <sub>O</sub> = 20 μA                                                                                                                               |                            |                      | 0.9                        |     |

|                                 | V <sub>OL</sub> 4  | COM1 to COM4    | I <sub>O</sub> = 100 μA                                                                                                                              |                            |                      | 0.9                        |     |

|                                 | V <sub>OL</sub> 5  | DO              | I <sub>O</sub> = 1 mA                                                                                                                                |                            | 0.1                  | 0.3                        | 1   |

| Output middle<br>level voltage  | V <sub>MID</sub> 1 | S1 to S57       | 1/3 bias I <sub>O</sub> = $\pm 20 \ \mu$ A                                                                                                           | 2/3V <sub>DD</sub><br>-0.9 |                      | 2/3V <sub>DD</sub><br>+0.9 |     |

| *2                              | V <sub>MID</sub> 2 | S1 to S57       | 1/3 bias I <sub>O</sub> = ±20 μA                                                                                                                     | 1/3V <sub>DD</sub><br>_0.9 |                      | 1/3V <sub>DD</sub><br>+0.9 |     |

|                                 | V <sub>MID</sub> 3 | COM1 to COM4    | 1/3 bias I <sub>O</sub> = $\pm 100 \ \mu A$                                                                                                          | 2/3V <sub>DD</sub><br>_0.9 |                      | 2/3V <sub>DD</sub><br>+0.9 | ۱   |

|                                 | V <sub>MID</sub> 4 | COM1 to COM4    | 1/3 bias I_O = $\pm 100 \ \mu A$                                                                                                                     | 1/3V <sub>DD</sub><br>-0.9 |                      | 1/3V <sub>DD</sub><br>+0.9 |     |

| Oscillator<br>frequency         | fosc               | OSC             | $R_{OSC}$ = 39 k $\Omega$ ,<br>$C_{OSC}$ = 1000 pF<br>RC oscillation operating mode                                                                  | 30.4                       | 38                   | 45.6                       | k⊦  |

| Current drain                   | I <sub>DD</sub> 1  | V <sub>DD</sub> | Sleep mode                                                                                                                                           |                            |                      | 100                        |     |

|                                 | I <sub>DD</sub> 2  | V <sub>DD</sub> | $V_{DD}$ = 6.0 V, Output open,<br>RC oscillation operating mode,<br>$f_{OSC}$ = 38 kHz                                                               |                            | 450                  | 900                        |     |

|                                 | I <sub>DD</sub> 3  | V <sub>DD</sub> | $V_{DD} = 6.0 V$ , Output open,<br>External clock operating mode,<br>$f_{CK} = 38 \text{ kHz}$ ,<br>$V_{IH}3 = 0.5V_{DD}$ ,<br>$V_{IL}3 = 0.1V_{DD}$ |                            | 550                  | 1100                       | μ   |

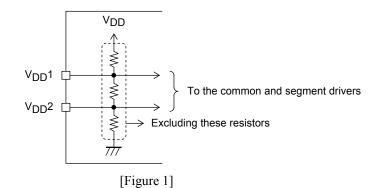

Note: \*2. Excluding the bias voltage generation divider resistor built into the VDD1 and VDD2. (See [Figure 1])

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

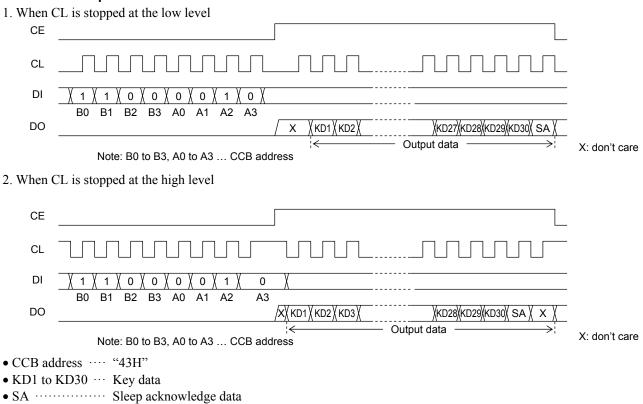

#### 1. When CL is stopped at the low level

[Figure 2]

2. When CL is stopped at the high level

3. OSC pin clock timing in external clock operating mode

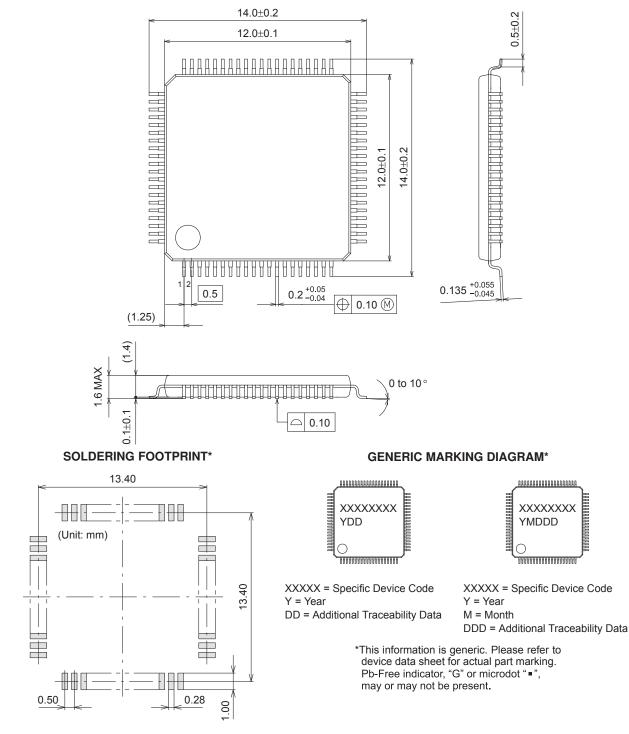

#### **Package Dimensions**

unit : mm

#### SPQFP80 12x12 / SQFP80 CASE 131AL ISSUE A

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **Pin Functions**

| Symbol             | Pin No.                                                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Active   | I/O | Handling<br>when |

|--------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|------------------|

| S1/P1 to S4/P4     | 79,80,1,2                                                                      | Segment outputs for displaying the display data transferred by serial data<br>input. The S1/P1 to S4/P4 pins can be used as general-purpose output ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 0   | unused<br>OPEN   |

| S5 to S53          | 3 to 51                                                                        | under serial data control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |     | 0. 2.1           |

| COM1 to COM3       | COM1 to COM3 52 to 54 Common driver outputs.<br>The frame frequency is fo[Hz]. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | ο   | OPEN             |

| COM4/S54           | 55                                                                             | The COM4/S54 pin can be used as a segment output in 1/3 duty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |     |                  |

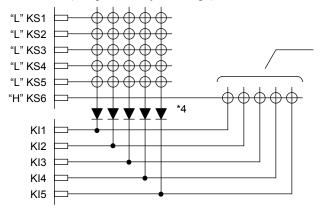

|                    |                                                                                | Key scan outputs. Although normal key scan timing lines require diodes to<br>be inserted in the timing lines to prevent shorts, since these outputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |     |                  |

| KS1/S55<br>KS2/S56 | 56<br>57                                                                       | unbalanced CMOS transistor outputs, these outputs will not be damaged by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | 0   | OPEN             |

| KS3 to KS6         | 58 to 61                                                                       | shorting when these outputs are used to form a key matrix. The KS1/S55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | U   | OFER             |

|                    |                                                                                | and KS2/S56 pins can be used as segment outputs when so specified by the<br>control data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |     |                  |

| KI1 to KI5         | 62 to 66                                                                       | Key scan inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Н        | I   | GND              |

|                    |                                                                                | These pins have built-in pull-down resistors.<br>General-purpose output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |     |                  |

| P5/S57             | 67                                                                             | This pin can be used as clock output port or segment output port under                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -        | 0   | OPEN             |

|                    |                                                                                | serial data control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |     |                  |

|                    |                                                                                | Oscillator connections. An oscillator circuit is formed by connecting an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |     |                  |

| OSC                | 73                                                                             | external resistor and capacitor at this pin. This pin can also be used as the<br>external clock input pin if the external clock operating mode is selected with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -        | I/O | V <sub>DD</sub>  |

|                    |                                                                                | the control data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |     |                  |

| CE                 | 76                                                                             | Serial data interface connections to the controller. Note that DO, being an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Н        | I   |                  |

| CL                 | 77                                                                             | open-drain output, requires a pull-up resistor.<br>CE: Chip enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\wedge$ | I   | GND              |

| DI                 | 78                                                                             | CL: Synchronization clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 1   |                  |

|                    |                                                                                | DI: Transfer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -        | -   |                  |

| DO                 | 75                                                                             | DO: Output data Reset signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -        | 0   | OPEN             |

| RES                | 74                                                                             | <ul> <li>RES=Low ···· Display off</li> <li>S1/P1 to S4/P4, KS1/S55, KS2/S56=Low<br/>(These pins are forcibly set to the segment output port function and<br/>fixed at the low level.)</li> <li>S5 to S53=Low</li> <li>COM1 to COM3=Low</li> <li>COM4/S54=Low<br/>(This pin is forcibly set to the common output function and fixed at the<br/>low level.)</li> <li>P5/S57=Low<br/>(This pin is forcibly set to the general-purpose output port function and<br/>fixed at the low level.)</li> <li>KS3 to KS6=Low</li> <li>Key scanning disabled</li> <li>All the key data is reset to low.</li> <li>OSC="Z"(High impedance)</li> <li>RC oscillation stopped</li> <li>Inhibits external clock input</li> <li>RES=High ··· Display on</li> <li>General-purpose output port state setting is enabled</li> <li>Key scanning is enabled.</li> <li>RC oscillation enabled (RC oscilltator operating mode)</li> <li>Enables external clock input (external clock operating mode)</li> </ul> | L        | I   | V <sub>DD</sub>  |

| TEST               | 72                                                                             | However, serial data can be transferred when the RES pin is low<br>This pin must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -        | I   | -                |

| V <sub>DD</sub> 1  | 69                                                                             | Used to apply the LCD drive 2/3 bias voltage externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -        | I   | OPEN             |

| V <sub>DD</sub> 2  | 70                                                                             | Used to apply the LCD drive 1/3 bias voltage externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -        | I   | OPEN             |

| V <sub>DD</sub>    | 68                                                                             | Power supply connections. Provide a voltage of between 4.5 to 6.0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -        | -   | -                |

| V <sub>SS</sub>    | 71                                                                             | Power supply connections. Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -        | -   | -                |

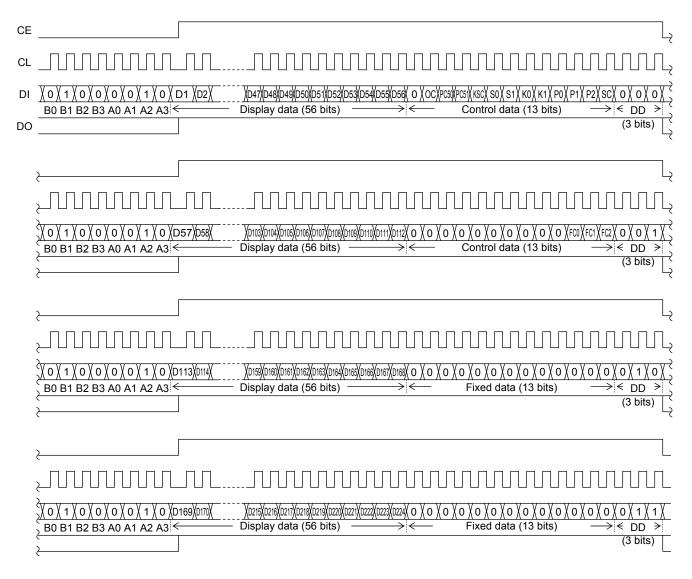

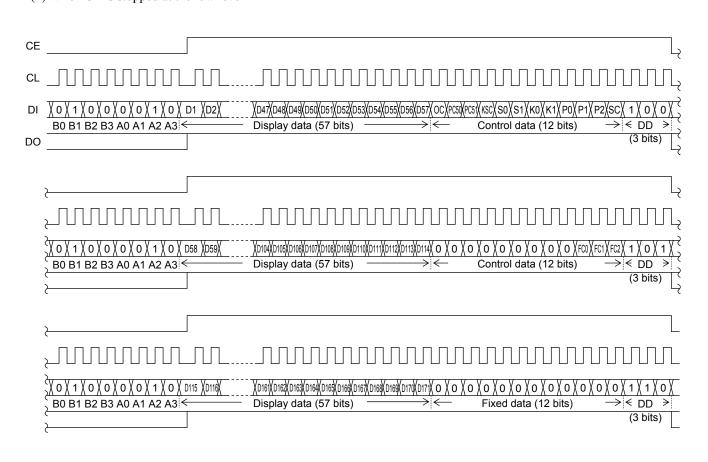

#### Serial Data Input

1. 1/4 duty

(1) When CL is stopped at the low level

Note: B0 to B3, A0 to A3 ..... CCB address DD ..... Direction data

#### (2) When CL is stopped at the high level

|    | r                                               |               |                                     |                                 |                                | 1                                            |

|----|-------------------------------------------------|---------------|-------------------------------------|---------------------------------|--------------------------------|----------------------------------------------|

| CE |                                                 |               |                                     |                                 |                                | Ļ                                            |

| CL | uuuuu                                           |               |                                     |                                 |                                |                                              |

| DI | <u>X 0 X 1 X 0 X 0 X 0 X 0 X 1 X 0</u>          | XD1XD2X       |                                     | (D54XD55XD56X 0 XOCXPC50)       | pc51XKSCXS0XS1XK0XK1XP0XP1     |                                              |

| DO | B0 B1 B2 B3 A0 A1 A2 A3                         | , ←           | Display data (56 bits) —            | ><                              | Control data (13 bits)         | $\rightarrow \in DD \Rightarrow$<br>(3 bits) |

| 00 |                                                 |               |                                     |                                 |                                | Ч стр                                        |

|    |                                                 |               |                                     |                                 |                                | Ļ                                            |

|    |                                                 |               |                                     |                                 |                                |                                              |

|    | <sup>2</sup> <u>0</u> 110101010110              | <u> </u>      | XD103XD104XD105XD106XD107XD108XD109 | (D110XD111XD112X o X o X o X    |                                |                                              |

|    | B0 B1 B2 B3 A0 A1 A2 A3                         | ; ←           | Display data (56 bits)              | $\longrightarrow$               | Control data (13 bits)         | $\rightarrow$ < DD > (3 bits)                |

|    | <u>}</u>                                        |               |                                     |                                 |                                |                                              |

|    | 、                                               |               |                                     |                                 |                                |                                              |

|    |                                                 |               |                                     |                                 |                                |                                              |

|    | <sup>2</sup><br>X o X 1 X o X o X o X o X 1 X o | XD113XD114X   |                                     |                                 | <u>ͺͺͺͺ</u>                    | <u>XoXoXoX1XoX</u>                           |

|    | B0 B1 B2 B3 A0 A1 A2 A3                         | -0 $0$ $0$ $$ | Display data (56 bits)              |                                 | Fixed data (13 bits)           | $\rightarrow \in DD \rightarrow \langle$     |

|    | <u>}</u>                                        |               |                                     |                                 |                                | (3 bits)                                     |

|    | I                                               |               |                                     |                                 |                                |                                              |

|    | <u>}</u>                                        |               |                                     |                                 |                                |                                              |

|    |                                                 |               |                                     |                                 |                                |                                              |

|    | <sup>2</sup> <u>//0//1//0//0//0//1//0</u>       | XD169XD170X   | XD215XD216XD217XD218XD219XD220XD221 | (D222)(D223)(D224)( O X O X O X | <u>(ο χο χο χο χο χο χο χο</u> |                                              |

|    | B0 B1 B2 B3 A0 A1 A2 A3                         | ; ←           | Display data (56 bits)              | $\longrightarrow$               | Fixed data (13 bits)           | $\rightarrow \in DD \Rightarrow$<br>(3 bits) |

|    |                                                 |               |                                     |                                 |                                |                                              |

Note: B0 to B3, A0 to A3 ..... CCB address DD ..... Direction data

- CCB address ··········42H"

- D1 to D224 .....Display data

- OC ·····RC oscillator operating mode/external clock operationg mode switching control data

- PC50, PC51 ······ General-purpose output port/clock output port/segment output port switching control data

- KSC ...... Key scan operation enabled/disabled state setting control data

- S0, S1 ····· Sleep control data

- K0, K1 ······Key scan output/segment output switching control data

- P0 to P2 .....Segment output port/general-purpose output port switching control data

- SC ····· Segment on/off control data

- FC0 to FC2 .....Common and segment output waveform frame frequency control data

# 2. 1/3 duty(1) When CL is stopped at the low level

Note: B0 to B3, A0 to A3 ······ CCB address DD ····· Direction data

#### (2) When CL is stopped at the high level

| <u>сг</u> |                                                                |                |                                                                |                                         |                                                              |                                                                                                  |

|-----------|----------------------------------------------------------------|----------------|----------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| CE        |                                                                |                |                                                                |                                         |                                                              | L                                                                                                |

| CL        |                                                                |                |                                                                |                                         |                                                              |                                                                                                  |

| DI        | X0X1X0X0X0X0X1X0<br>B0 B1 B2 B3 A0 A1 A2 A3                    | <u>_A_A_A_</u> | XD47XD48XD49XD50XD51XD52XD5<br>Display data (57 bits)          |                                         | נאַגאָאָאָאָאָאָאָאָאָאָאָאָאָאַגאַאַאַאַ                    | $\frac{\mathbb{P}_{2(SC)} \mathbb{I} \mathbb{I} \mathbb{O} \mathbb{O}}{\mathbb{O}} = \mathbb{O}$ |

| DO        |                                                                |                | Display data (57 bits)                                         |                                         | Control data (12 bits)                                       | (3 bits)                                                                                         |

|           | >                                                              |                |                                                                |                                         |                                                              |                                                                                                  |

|           | `<br>`<br>IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                   |                |                                                                |                                         |                                                              |                                                                                                  |

|           | X 0 X 1 X 0 X 0 X 0 X 0 X 1 X 0<br>S 0 0 1 1 2 1 3 A0 A1 A2 A3 | <u></u>        | DioyDiosCologCologCologCologCologCologCologCol                 | XD111XD112XD113XD114X O X O X C<br>→>   | 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X Fα<br>Control data (12 bits) | $\frac{\sqrt{FC1}\sqrt{FC2}}{\sqrt{FC2}} \xrightarrow{1} 0 \xrightarrow{1} 0 \xrightarrow{2} 0$  |

|           | 2                                                              |                |                                                                |                                         |                                                              | (3 bits)                                                                                         |

|           | 2                                                              |                |                                                                |                                         |                                                              | L                                                                                                |

|           |                                                                |                |                                                                |                                         |                                                              |                                                                                                  |

|           | 2<br>0 1 1 0 0 0 0 0 1 0 1 0<br>0 0 0 1 0 0 0 0                | <u> </u>       | XD161XD162XD163XD164XD165XD166XD16<br>- Display data (57 bits) | 7XD168XD169XD170XD171X O X O X C<br>→ < | 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X                      | $\frac{\langle 0 \rangle 0 \langle 1 \rangle 1 \rangle 0 \rangle}{\Rightarrow < DD >}$           |

|           | 2                                                              |                |                                                                |                                         | . ,                                                          | (3 bits)                                                                                         |

Note: B0 to B3, A0 to A3 ..... CCB address

DD ..... Direction data

- CCB address ·······"42H"

- D1 to D171 ····· Display data

- OC .....RC oscillator operating mode/external clock operationg mode switching control data

- PC50, PC51 ...... General-purpose output port/clock output port/segment output port switching control data

- KSC ......Key scan operation enabled/disabled state setting control data

- S0, S1 ····· Sleep control data

- K0, K1 ..... Key scan output/segment output switching control data

- P0 to P2 ..... Segment output port/general-purpose output port switching control data

- SC ····· Segment on/off control data

- FC0 to FC2 ..... Common and segment output waveform frame frequency control data

#### **Control Data Functions**

- 1. OC ... RC oscillator operating mode/external clock operating mode switching control data

- This control data bit selects the OSC pin function (RC oscillator operating mode or external clock operating mode)

| OC | OSC pin function              |

|----|-------------------------------|

| 0  | RC oscillator operating mode  |

| 1  | External clock operating mode |

Note: If RC oscillator operating mode is selected, connect an external resistor R<sub>OSC</sub> and an external capacitor C<sub>OSC</sub> to the OSC pin.

2. PC50, PC51 ... General-purpose output port/clock output port/segment output port switching control data These control data bits swithes the functions of the P5/S57 output pin between the general-purpose output port, the clock output port, and the segment output port.

| Control data |      | The state of DE/CE7 output his                                         |  |  |

|--------------|------|------------------------------------------------------------------------|--|--|

| PC50         | PC51 | The state of P5/S57 output pin                                         |  |  |

| 0            | 0    | General-purpose output port (P5) ("L" level output)                    |  |  |

| 1            | 0    | General-purpose output port (P5) ("H" level output)                    |  |  |

| 0            | 1    | Clock output port (P5) (Clock frequency is $f_{OSC}/2$ or $f_{CK}/2$ ) |  |  |

| 1            | 1    | Segment output port (S57)                                              |  |  |

|              |      |                                                                        |  |  |

Note: If the sleep mode is set, the P5/S57 output pin can not be used as the clock output port.

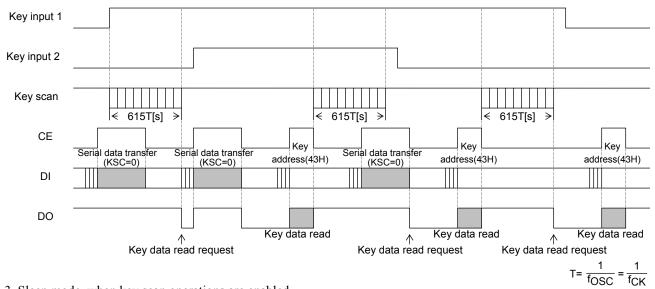

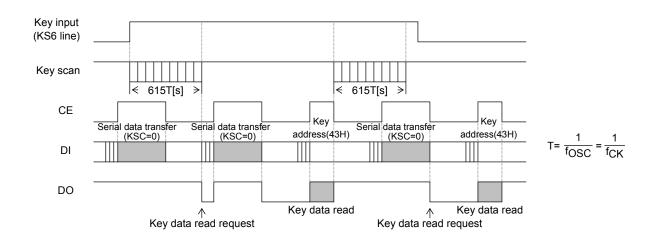

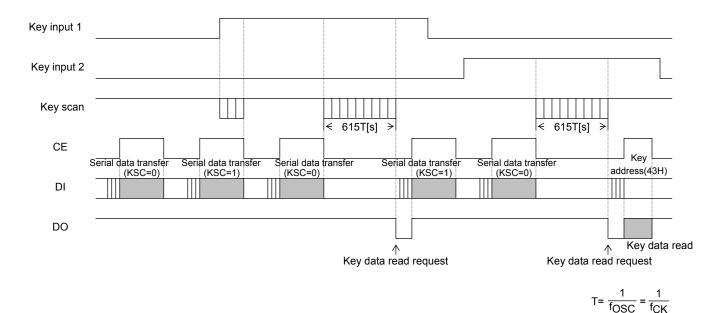

#### 3. KSC $\dots$ Key scan operation enabled/disabled state setting control data

#### This control data bit enables or disables key scan operation.

| KSC | Key scan operating state                                                                                                                                                                                                                                        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Key scan operation enabled<br>(A key scan operation is performed if any key on the lines corresponding to KS1 to KS6 pin which is set<br>high is pressed.)                                                                                                      |

| 1   | Key scan operation disabled<br>(No key scan operation is performed, even if any of the keys in the key matrix are pressed.<br>If this state is set up, the key data is forcibly reset to 0 and the key data read request is also cleared.<br>(DO is set high.)) |

#### 4. S0, S1 ... Sleep control data

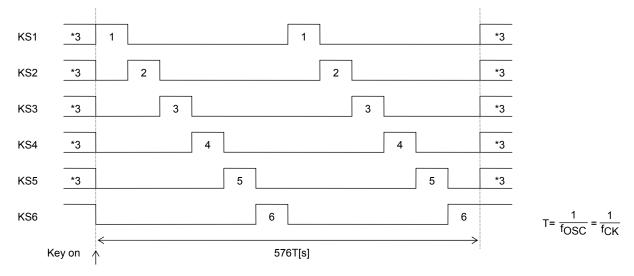

These control data bits switch between normal mode and sleep mode, and set the states of the KS1 to KS6 key scan output during key scan standby.

| Contro | ol data |        | OSC pin state                                                       | Segment                      |     | Output p | in states dur | ing key scan | i standby |     |

|--------|---------|--------|---------------------------------------------------------------------|------------------------------|-----|----------|---------------|--------------|-----------|-----|

| S0     | S1      | Mode   | (RC oscillator<br>or acceptance<br>of the external<br>clock signal) | output /<br>Common<br>output | KS1 | KS2      | KS3           | KS4          | KS5       | KS6 |

| 0      | 0       | Normal | Operating                                                           | Operating                    | Н   | H        | Н             | Н            | Н         | Н   |

| 0      | 1       | Sleep  | Stopped                                                             | L                            | L   | L        | L             | L            | L         | Н   |

| 1      | 0       | Sleep  | Stopped                                                             | L                            | L   | L        | L             | L            | Н         | Н   |

| 1      | 1       | Sleep  | Stopped                                                             | L                            | Н   | Н        | Н             | Н            | Н         | Н   |

Note: This assumes that the KS1/S55 and KS2/S56 output pins are selected for key scan output.

5. K0, K1 ... Key scan output/segment output switching control data

These control data bits switch the functions of the KS1/S55 and KS2/S56 output pins between the key scan output and the segment output.

| Contro        | ol data | Output  | pin state | Maximum number |

|---------------|---------|---------|-----------|----------------|

| K0            | K1      | KS1/S55 | KS2/S56   | of input keys  |

| 0             | 0       | KS1     | KS2       | 30             |

| 0             | 1       | S55     | KS2       | 25             |

| 1             | Х       | S55     | S56       | 20             |

| <b>X</b> 1 1/ |         |         |           |                |

Note: KSn (n=1 or 2): Key scan output Sn (n=55 or 56): Segment output

X : don't care

6. P0 to P2 ... Segment output port/general-purpose output port switching control data

These control data bits switch the functions of the S1/P1 to S4/P4 output pins between the segment output port and the general-purpose output port.

| 0  | 8         |     |                  |       |       |       |  |  |  |  |

|----|-----------|-----|------------------|-------|-------|-------|--|--|--|--|

| Co | ontrol da | ata | Output pin state |       |       |       |  |  |  |  |

| P0 | P1        | P2  | S1/P1            | S2/P2 | S3/P3 | S4/P4 |  |  |  |  |

| 0  | 0         | 0   | S1               | S2    | S3    | S4    |  |  |  |  |

| 0  | 0         | 1   | P1               | S2    | S3    | S4    |  |  |  |  |

| 0  | 1         | 0   | P1               | P2    | S3    | S4    |  |  |  |  |

| 0  | 1         | 1   | P1               | P2    | P3    | S4    |  |  |  |  |

| 1  | 0         | 0   | P1               | P2    | P3    | P4    |  |  |  |  |

Note: Sn (n=1 to 4): Segment output port Pn (n=1 to 4): General-purpose output port

The table below lists the correspondence between the display data and the output pins when these pins are selected to be general-purpose output ports.

|            | Correspondence display data |          |  |

|------------|-----------------------------|----------|--|

| Output pin | 1/4 duty                    | 1/3 duty |  |

| S1/P1      | D1                          | D1       |  |

| S2/P2      | D5                          | D4       |  |

| S3/P3      | D9                          | D7       |  |

| S4/P4      | D13                         | D10      |  |

For example, if the circuit is operated in 1/4 duty and the S4/P4 output pin is selected to be a general-purpose output port, the S4/P4 output pin will output a high level when the display data D13 is 1, and will output a low level when D13 is 0.

#### 7. SC ... Segment on/off control data

This control data bit controls the on/off state of the segments.

| SC | Display state |

|----|---------------|

| 0  | On            |

| 1  | Off           |

However, note that when the segments are turned off by setting SC to 1, the segments are turned off by outputting segment off waveforms from the segment output pins.

8. FC0 to FC2  $\ldots$  Common and segment output waveform frame frequency control data

These control data bits set the common and segment output waveform frequency.

| Control data |     | a   | Frame frequency                             |

|--------------|-----|-----|---------------------------------------------|

| FC0          | FC1 | FC2 | f <sub>O</sub> [Hz]                         |

| 1            | 1   | 0   | f <sub>OSC</sub> /768, f <sub>CK</sub> /768 |

| 1            | 1   | 1   | f <sub>OSC</sub> /576, f <sub>CK</sub> /576 |

| 0            | 0   | 0   | f <sub>OSC</sub> /384, f <sub>CK</sub> /384 |

| 0            | 0   | 1   | f <sub>OSC</sub> /288, f <sub>CK</sub> /288 |

| 0            | 1   | 0   | f <sub>OSC</sub> /192, f <sub>CK</sub> /192 |

#### **Display Data and Output Pin Correspondence**

#### 1. 1/4 duty Output pin COM1 COM2 COM3 COM4 Output pin COM1 COM2 COM3 COM4 S1/P1 D1 D2 D3 D4 D113 D114 D115 D116 S29 S2/P2 D5 D6 D7 D8 S30 D117 D118 D119 D120 S3/P3 D9 D10 D11 D12 S31 D122 D123 D124 D121 S4/P4 D13 D14 D15 D16 S32 D125 D126 D127 D128 S5 D17 D18 D19 D20 S33 D129 D130 D131 D132 D22 D23 D24 S34 D134 D136 S6 D21 D133 D135 S7 D25 D26 D27 D28 S35 D137 D138 D139 D140 D29 D30 D32 S36 D141 D142 D143 D144 S8 D31 S9 D33 D34 D35 D36 S37 D145 D146 D147 D148 S10 D37 D38 D39 D40 S38 D149 D150 D151 D152 D42 D156 S11 D41 D43 D44 S39 D153 D154 D155 S12 D45 D46 D47 D48 S40 D157 D158 D159 D160 D52 S41 D161 D162 D164 S13 D49 D50 D51 D163 S14 D53 D54 D55 D56 S42 D165 D166 D167 D168 S15 D57 D58 D59 D60 S43 D169 D170 D171 D172 S16 D61 D62 D63 D64 S44 D173 D174 D175 D176 S17 D65 D66 D67 D68 S45 D177 D178 D179 D180 S46 D182 D184 S18 D69 D70 D71 D72 D181 D183 S19 D73 D74 D75 D76 S47 D185 D186 D187 D188 S20 D77 D78 D79 D80 S48 D189 D190 D191 D192 S21 D81 D82 D83 D84 S49 D193 D194 D195 D196 D87 S22 D85 D86 D88 S50 D197 D198 D199 D200 D89 D90 D91 D92 S51 D201 D202 D204 S23 D203 S24 D93 D94 D95 D96 S52 D205 D206 D207 D208 S25 D100 S53 D210 D212 D97 D98 D99 D209 D211 S26 D101 D102 D103 D104 KS1/S55 D213 D214 D215 D216 S27 D105 D106 D107 D108 KS2/S56 D217 D218 D219 D220 D109 D112 P5/S57 S28 D110 D111 D221 D222 D223 D224

Note: This is for the case where the S1/P1 to S4/P4, KS1/S55, KS2/S56, P5/S57 output pins are selected for use as segment outputs.

For example, the table below lists the segment output states for the S11 output pin.

| Display data |     |     |     |                                                         |

|--------------|-----|-----|-----|---------------------------------------------------------|

| D41          | D42 | D43 | D44 | Output pin state (S11)                                  |

| 0            | 0   | 0   | 0   | The LCD segments for COM1, COM2, COM3 and COM4 are off. |

| 0            | 0   | 0   | 1   | The LCD segment for COM4 is on.                         |

| 0            | 0   | 1   | 0   | The LCD segment for COM3 is on.                         |

| 0            | 0   | 1   | 1   | The LCD segments for COM3 and COM4 are on.              |

| 0            | 1   | 0   | 0   | The LCD segment for COM2 is on.                         |

| 0            | 1   | 0   | 1   | The LCD segments for COM2 and COM4 are on.              |

| 0            | 1   | 1   | 0   | The LCD segments for COM2 and COM3 are on.              |

| 0            | 1   | 1   | 1   | The LCD segments for COM2, COM3 and COM4 are on.        |

| 1            | 0   | 0   | 0   | The LCD segment for COM1 is on.                         |

| 1            | 0   | 0   | 1   | The LCD segments for COM1 and COM4 are on.              |

| 1            | 0   | 1   | 0   | The LCD segments for COM1 and COM3 are on.              |

| 1            | 0   | 1   | 1   | The LCD segments for COM1, COM3 and COM4 are on.        |

| 1            | 1   | 0   | 0   | The LCD segments for COM1 and COM2 are on.              |

| 1            | 1   | 0   | 1   | The LCD segments for COM1, COM2 and COM4 are on.        |

| 1            | 1   | 1   | 0   | The LCD segments for COM1, COM2 and COM3 are on.        |

| 1            | 1   | 1   | 1   | The LCD segments for COM1, COM2, COM3 and COM4 are on.  |

| 2  | 1/3 | duty |

|----|-----|------|

| 2. | 1/3 | auty |

| Output pin | COM1 | COM2 | COM3 |

|------------|------|------|------|

| S1/P1      | D1   | D2   | D3   |

| S2/P2      | D4   | D5   | D6   |

| S3/P3      | D7   | D8   | D9   |

| S4/P4      | D10  | D11  | D12  |

| S5         | D13  | D14  | D15  |

| S6         | D16  | D17  | D18  |

| S7         | D19  | D20  | D21  |

| S8         | D22  | D23  | D24  |

| S9         | D25  | D26  | D27  |

| S10        | D28  | D29  | D30  |

| S11        | D31  | D32  | D33  |

| S12        | D34  | D35  | D36  |

| S13        | D37  | D38  | D39  |

| S14        | D40  | D41  | D42  |

| S15        | D43  | D44  | D45  |

| S16        | D46  | D47  | D48  |

| S17        | D49  | D50  | D51  |

| S18        | D52  | D53  | D54  |

| S19        | D55  | D56  | D57  |

| S20        | D58  | D59  | D60  |

| S21        | D61  | D62  | D63  |