## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## CMOS IC FROM 64K byte, RAM 4K byte on-chip 8-bit 1-chip Microcontroller with Full-Speed USB

The LC87F1D64A is an 8-bit microcomputer that, centered around a CPU running at a minimum bus cycle time of 62.5ns, integrates on a single chip a number of hardware features such as 64K-byte flash ROM (onboard programmable), 4096-byte RAM, an on-chip debugger, a sophisticated 16-bit timers/counters (may be divided into 8-bit timers), 16-bit timers/counter (may be divided into 8-bit timers/counters or 8-bit PWMs), two 8-bit timers with a prescaler, a base timer serving as a time-of-day clock, a high-speed clock counter, two synchronous SIO interface (with automatic block transmit/ receive function), an asynchronous/synchronous SIO interface, a UART interface (full duplex), a Full-Speed USB interface (function controller), 12-channel 12-bit A/D converter with 12-/8-bit resolution selector, two 12-bit PWM channels, a system clock frequency divider, an infrared remote control receiver circuit, and a 30-source 10-vector address interrupt feature.

#### Features

#### ■Flash ROM

- Capable of on-board-programming with wide range, 3.0 to 5.5V, of voltage source.

- Block-erasable in 128 byte units

- Writes data in 2-byte units

- 65536 × 8 bits

#### ■RAM

• 4096 × 9 bits

■Minimum Bus Cycle

• 62.5ns (CF=16MHz)

Note: The bus cycle time here refers to the ROM read speed.

\* This product is licensed from Silicon Storage Technology, Inc. (USA).

Minimum Instruction Cycle Time

• 188ns (CF=16MHz)

#### ■Ports

• I/O ports

| - no pons                                                       |                                                    |

|-----------------------------------------------------------------|----------------------------------------------------|

| Ports whose I/O direction can be designated in 1 bit units      | 28 (P10 to P17, P20 to P27, P30 to P34,            |

|                                                                 | P70 to P73, PWM0, PWM1, XT2)                       |

| Ports whose I/O direction can be designated in 4 bit units      | 8 (P00 to P07)                                     |

| • USB ports                                                     | 2 (D+, D-)                                         |

| <ul> <li>Dedicated oscillator ports</li> </ul>                  | 2 (CF1, CF2)                                       |

| <ul> <li>Input-only port (also used for oscillation)</li> </ul> | 1 (XT1)                                            |

| • Reset pins                                                    | $1(\overline{\text{RES}})$                         |

| • Power pins                                                    | 6 (V <sub>SS</sub> 1 to 3, V <sub>DD</sub> 1 to 3) |

|                                                                 |                                                    |

■Timers

• Timer 0: 16-bit timer/counter with a capture register.

Mode 0: 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register)  $\times 2$  channels

Mode 1: 8-bit timer with an 8-bit programmable prescaler (with an 8-bit capture register) + 8-bit counter (with an 8-bit capture register)

Mode 2: 16-bit timer with an 8-bit programmable prescaler (with a 16-bit capture register)

- Mode 3: 16-bit counter (with a 16-bit capture register)

- Timer 1: 16-bit timer/counter that supports PWM/toggle outputs

- Mode 0: 8-bit timer with an 8-bit prescaler (with toggle outputs)

- + 8-bit timer/counter with an 8-bit prescaler (with toggle outputs)

- Mode 1: 8-bit PWM with an 8-bit prescaler  $\times$  2 channels

- Mode 2: 16-bit timer/counter with an 8-bit prescaler (with toggle outputs)

- (toggle outputs also possible from the lower-order 8 bits)

- Mode 3: 16-bit timer with an 8-bit prescaler (with toggle outputs)

- (The lower-order 8 bits can be used as PWM.)

- Timer 6: 8-bit timer with a 6-bit prescaler (with toggle output)

- Timer 7: 8-bit timer with a 6-bit prescaler (with toggle output)

- Base timer

- 1) The clock is selectable from the subclock (32.768kHz crystal oscillation), system clock, and timer 0 prescaler output.

- 2) Interrupts programmable in 5 different time schemes

#### ■SIO

- SIO0: Synchronous serial interface

- 1) LSB first/MSB first mode selectable

- 2) Transfer clock cycle: 4/3 to 512/3 tCYC

- Automatic continuous data transmission (1 to 256 bits, specifiable in 1 bit units, suspension and resumption of data transmission possible in 1 byte units)

- SIO1: 8-bit asynchronous/synchronous serial interface

- Mode 0: Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 tCYC transfer clocks)

- Mode 1: Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 tCYC baudrates)

- Mode 2: Bus mode 1 (start bit, 8 data bits, 2 to 512 tCYC transfer clocks)

- Mode 3: Bus mode 2 (start detect, 8 data bits, stop detect)

- SIO4: Synchronous serial interface

- 1) LSB first/MSB first mode selectable

- 2) Transfer clock cycle: 4/3 to 1020/3 tCYC

- 3) Automatic continuous data transmission (1 to 4096 bytes, specifiable in 1 byte units, suspension and resumption of data transmission possible in 1 byte or 2 bytes units)

- 4) Auto-start-on-falling-edge function

- 5) Clock polarity selectable

- 6) CRC16 calculator circuit built in

#### ■Full Duplex UART

#### • UART1

- 1) Data length: 7/8/9 bits selectable

- 2) Stop bits: 1 bit (2 bits in continuous transmission mode)

- 3) Baud rate: 16/3 to 8192/3 tCYC

- UART2

- 1) Data length: 7/8/9 bits selectable

- 2) Stop bits: 1 bit (2 bits in continuous transmission mode)

- 3) Baud rate: 16/3 to 8192/3 tCYC

- **\blacksquare**AD Converter: 12 bits  $\times$  12 channels

- 12/8 bits AD converter resolution selectable

■PWM: Multifrequency 12-bit PWM × 2 channels

■Infrared Remote Control Receiver Circuit

1) Noise reduction function

(noise filter time constant: Approx. 120µs, when the 32.768kHz crystal oscillator is selected as the reference voltage source.)

- 2) Supports data encoding systems such as PPM (Pulse Position Modulation) and Manchester encoding

- 3) X'tal HOLD mode release function

■USB Interface (function controller)

- Compliant with USB 2.0 Full-Speed

- Supports a maximum of 4 user-defined endpoints.

| Endpoint     |           | EP0 | EP1 | EP2 | EP3 | EP4 |

|--------------|-----------|-----|-----|-----|-----|-----|

| Transfer     | Control   | 0   | -   | -   | -   | -   |

| Туре         | Bulk      | -   | 0   | 0   | 0   | 0   |

|              | Interrupt | -   | 0   | 0   | 0   | 0   |

| Isochronous  |           | -   | 0   | 0   | 0   | 0   |

| Max. payload |           | 64  | 64  | 64  | 64  | 64  |

■Watchdog Timer

• External RC watchdog timer

1) Interrupt and reset signals selectable

- Internal counter watchdog timer

- 1) Generates an internal reset signal on overflow occurring in a timer that runs on a dedicated low-speed RC oscillator clock (30kHz).

- 2) Three operating modes are selectable: continues counting, stops counting, or retains count when the CPU

#### ■Clock Output Function

1) Able to output selected oscillation clock 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64 as system clock.

2) Able to output oscillation clock of sub clock.

#### ■Interrupts

- 30 sources, 10 vector addresses

- 1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt requests of the level equal to or lower than the current interrupt are not accepted.

- 2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt into the smallest vector address takes precedence.

| No. | Vector Address | Level  | Interrupt Source                                             |

|-----|----------------|--------|--------------------------------------------------------------|

| 1   | 00003H         | X or L | INT0                                                         |

| 2   | 0000BH         | X or L | INT1                                                         |

| 3   | 00013H         | H or L | INT2/T0L/INT4/USB bus active/remote control receiver         |

| 4   | 0001BH         | H or L | INT3/INT5/base timer                                         |

| 5   | 00023H         | H or L | тон                                                          |

| 6   | 0002BH         | H or L | T1L/T1H                                                      |

| 7   | 00033H         | H or L | SIO0/USB bus reset/USB suspend/UART1 receive/UART2 receive   |

| 8   | 0003BH         | H or L | SIO1/USB endpoint/USB-SOF/SIO4/UART1 transmit/UART2 transmit |

| 9   | 00043H         | H or L | ADC/T6/T7                                                    |

| 10  | 0004BH         | H or L | Port 0/PWM0/PWM1                                             |

<sup>•</sup> Priority Level: X > H > L

Subroutine Stack Levels: 2048 levels (the stack is allocated in RAM.)

■High-speed Multiplication/Division Instructions

- 16 bits  $\times$  8 bits (5 tCYC execution time)

- 24 bits  $\times$  16 bits (12 tCYC execution time)

- 16 bits ÷ 8 bits (8 tCYC execution time)

- 24 bits  $\div$  16 bits (12 tCYC execution time)

■Oscillation Circuits

- RC oscillation circuit (internal): For system clock (1MHz)

- Low-speed RC oscillation circuit (internal): For watchdog timer (30kHz)

- CF oscillation circuit: For system clock

- Crystal oscillation circuit: For system clock, time-of-day clock

- PLL circuit (internal):

■Standby Function

• HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation. 1) Oscillation is not halted automatically.

For USB interface (see Fig.5)

- 2) There are three ways of resetting the HALT mode.

- (1) Setting the reset pin to the low level

- (2) Reset generated by watchdog timer

- (3) Interrupt generation

- HOLD mode: Suspends instruction execution and the operation of the peripheral circuits.

- 1) The PLL base clock generator, CF, RC and crystal oscillators automatically stop operation.

- 2) There are five ways of resetting the HOLD mode.

- (1) Setting the reset pin to the lower level.

- (2) Reset generated by watchdog timer

- (3) Having an interrupt source established at one of the INT0, INT1, INT2, INT4, and INT5 pins \* The INT0 and INT1 pins must be configured only for level detection.

- (4) Having an interrupt source established at port 0

- (5) Having an bus active interrupt source established in the USB interface circuit

Continued on next page.

<sup>•</sup> Of interrupts of the same level, the one with the smallest vector address takes precedence.

Continued from preceding page.

- X'tal HOLD mode: Suspends instruction execution and the operation of the peripheral circuits except the base timer and the infrared remote control receiver circuit.

- 1) The PLL base clock generator, CF and RC oscillator automatically stop operation.

- 2) The state of crystal oscillation established when the X'tal HOLD mode is entered is retained.

- 3) There are seven ways of resetting the X'tal HOLD mode.

- (1) Setting the reset pin to the low level

- (2) Reset generated by watchdog timer

- (3) Having an interrupt source established at one of the INT0, INT1, INT2, INT4, and INT5 pins \* The INT0 and INT1 pins must be configured only for level detection.

- (4) Having an interrupt source established at port 0

- (5) Having an interrupt source established in the base timer circuit

- (6) Having an bus active interrupt source established in the USB interface circuit

- (7) Having an interrupt source established in the infrared remote control receiver circuit

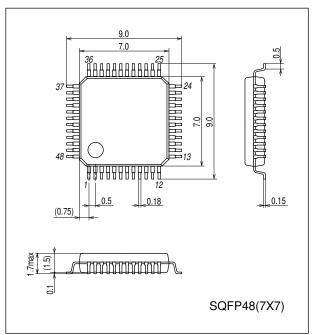

#### ■Package Form

• SQFP48(7×7): Lead-/Halogen-free type

■Development Tools

• On-chip debugger: TCB87 type B + LC87F1D64A

#### Flash ROM Programming Boards

| Package     | Programming boards |

|-------------|--------------------|

| SQFP48(7×7) | W87F55256SQ        |

#### ■Flash ROM Programmer

| Maker                                                              |                                                            | Model                                                                                         | Supported version                                                          | Device     |

|--------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|

| Flash Support Group, Inc.<br>(FSG)                                 | Single<br>Programmer                                       | AF9708<br>AF9709/AF9709B/AF9709C<br>(Including Ando Electric Co., Ltd. models)                | Rev.03.06 or later                                                         | LC87F1D64A |

| Flash Support Group, Inc.<br>(FSG)<br>+<br>Our company<br>(Note 1) | In-circuit<br>Programmer                                   | AF9101/AF9103 (main body)<br>(FSG models)<br>SIB87 (Inter Face Driver)<br>(Our company model) | (Note 2)                                                                   |            |

| Our company                                                        | Single/Gang<br>Programmer<br>In-circuit/Gang<br>Programmer | SKK/SKK Type B<br>(SANYO FWS)<br>SKK-DBG Type B<br>(SANYO FWS)                                | Application Version<br>1.04 or later<br>Chip Data Version<br>2.15 or later | LC87F1D64  |

Note1: On-board-programmer from FSG (AF9101/AF9103) and serial interface driver from Our company (SIB87) together can give a PC-less, standalone on-board-programming capabilities.

Note2: It needs a special programming devices and applications depending on the use of programming environment. Please ask FSG or Our company for the information.

#### **Package Dimensions**

unit : mm (typ) 3163B

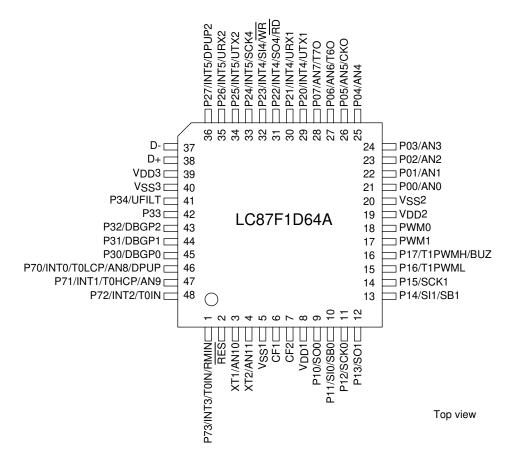

#### **Pin Assignment**

SQFP48(7×7) "Lead-/ Halogen-free Type"

| SQFP48 | NAME               |

|--------|--------------------|

| 1      | P73/INT3/T0IN/RMIN |

| 2      | RES                |

| 3      | XT1/AN10           |

| 4      | XT2/AN11           |

| 5      | V <sub>SS</sub> 1  |

| 6      | CF1                |

| 7      | CF2                |

| 8      | V <sub>DD</sub> 1  |

| 9      | P10/SO0            |

| 10     | P11/SI0/SB0        |

| 11     | P12/SCK0           |

| 12     | P13/SO1            |

| 13     | P14/SI1/SB1        |

| 14     | P15/SCK1           |

| 15     | P16/T1PWML         |

| 16     | P17/T1PWMH/BUZ     |

| 17     | PWM1               |

| 18     | PWM0               |

| 19     | V <sub>DD</sub> 2  |

| 20     | V <sub>SS</sub> 2  |

| 21     | P00/AN0            |

| 22     | P01/AN1            |

| 23     | P02/AN2            |

| 24     | P03/AN3            |

| SQFP48 | NAME                    |

|--------|-------------------------|

| 25     | P04/AN4                 |

| 26     | P05/AN5/CKO             |

| 27     | P06/AN6/T6O             |

| 28     | P07/AN7/T7O             |

| 29     | P20/INT4/UTX1           |

| 30     | P21/INT4/URX1           |

| 31     | P22/INT4/SO4/RD         |

| 32     | P23/INT4/SI4/WR         |

| 33     | P24/INT5/SCK4           |

| 34     | P25/INT5/UTX2           |

| 35     | P26/INT5/URX2           |

| 36     | P27/INT5/DPUP2          |

| 37     | D-                      |

| 38     | D+                      |

| 39     | V <sub>DD</sub> 3       |

| 40     | V <sub>SS</sub> 3       |

| 41     | P34/UFILT               |

| 42     | P33                     |

| 43     | P32/DBGP2               |

| 44     | P31/DBGP1               |

| 45     | P30/DBGP0               |

| 46     | P70/INT0/T0LCP/AN8/DPUP |

| 47     | P71/INT1/T0HCP/AN9      |

| 48     | P72/INT2/T0IN           |

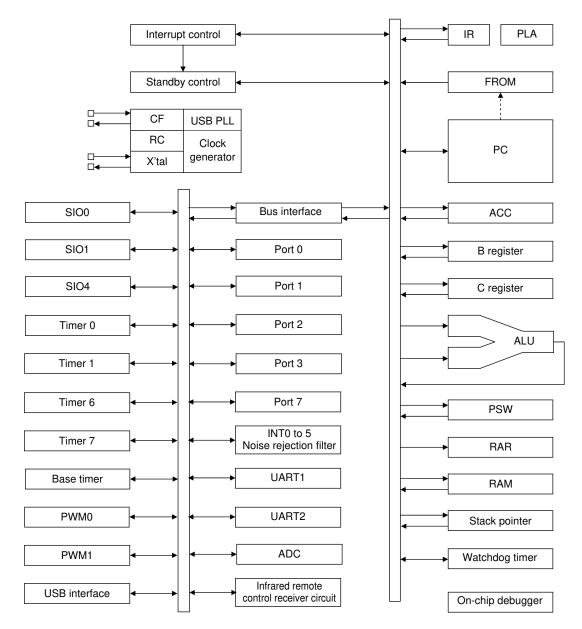

## System Block Diagram

## Pin Description

| Pin Name                                         | I/O |                                                            |                           | D                 | escription          |                   |                                       | Option |  |  |

|--------------------------------------------------|-----|------------------------------------------------------------|---------------------------|-------------------|---------------------|-------------------|---------------------------------------|--------|--|--|

| V <sub>SS</sub> 1,<br>V <sub>SS</sub> 2,<br>Voc3 | -   | -power supply p                                            | No                        |                   |                     |                   |                                       |        |  |  |

| V <sub>SS</sub> 3<br>V <sub>DD</sub> 1,          | -   | +power supply p                                            | -power supply pin         |                   |                     |                   |                                       |        |  |  |

| $V_{DD}^2$                                       | _   |                                                            | valtara nin               |                   |                     |                   |                                       | Yes    |  |  |

| V <sub>DD</sub> 3                                |     |                                                            | USB reference voltage pin |                   |                     |                   |                                       |        |  |  |

| Port 0                                           | I/O | 8-bit I/O port                                             |                           |                   |                     |                   |                                       | Yes    |  |  |

| P00 to P07                                       |     | I/O specifiable                                            |                           | d an and aff in a | 1 bit upita         |                   |                                       |        |  |  |

|                                                  |     | <ul> <li>Pull-up resisto</li> <li>HOLD reset in</li> </ul> |                           | d on and on in 2  | +-bit units.        |                   |                                       |        |  |  |

|                                                  |     | Port 0 interrup                                            |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | Pins functions                                             | imput                     |                   |                     |                   |                                       |        |  |  |

|                                                  |     |                                                            | nnut nort: AN0            | to AN7 (P00 to    | P07)                |                   |                                       |        |  |  |

|                                                  |     | P05: System C                                              |                           |                   | 10/)                |                   |                                       |        |  |  |

|                                                  |     | P06: Timer 6 t                                             | -                         |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P07: Timer 7 t                                             |                           |                   |                     |                   |                                       |        |  |  |

| Port 1                                           | I/O | • 8-bit I/O port                                           | 00 1                      |                   |                     |                   |                                       | Yes    |  |  |

| P10 to P17                                       |     | <ul> <li>I/O specifiable</li> </ul>                        | in 1-bit units            |                   |                     |                   |                                       |        |  |  |

|                                                  |     | Pull-up resisto                                            | rs can be turne           | d on and off in 1 | I-bit units.        |                   |                                       |        |  |  |

|                                                  |     | Pin functions                                              |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P10: SIO0 dat                                              | a output                  |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P11: SIO0 dat                                              | a input/bus I/O           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P12: SIO0 clos                                             | ck I/O                    |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P13: SIO1 dat                                              | a output                  |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P14: SIO1 dat                                              | -                         |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P15: SIO1 clos                                             |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P16: Timer 1 F                                             |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P17: Timer 1 F                                             | WMH output/b              | eeper output      |                     |                   |                                       |        |  |  |

| Port 2                                           | I/O | • 8-bit I/O port                                           |                           |                   |                     |                   |                                       | Yes    |  |  |

| P20 to P27                                       |     | I/O specifiable                                            |                           |                   | ( )= i4 i4          |                   |                                       |        |  |  |

|                                                  |     | Pull-up resisto                                            | rs can be turne           | d on and off in t | I-DIT UNITS.        |                   |                                       |        |  |  |

|                                                  |     | Pin functions     P20 to P22: IN                           |                           | rosot input/tim   | er 1 event input/   | timor OL capture  | input/                                |        |  |  |

|                                                  |     |                                                            | ner 0H capture            | -                 |                     | inner of capture  | ; mpu/                                |        |  |  |

|                                                  |     |                                                            |                           | -                 | er 1 event input/   | timer 01. capture | input/                                |        |  |  |

|                                                  |     |                                                            | ner 0H capture            | -                 |                     |                   | mput                                  |        |  |  |

|                                                  |     | P20: UART1 ti                                              |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P21: UART1 r                                               |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P22: SIO4 dat                                              | e I/O/parallel in         | terface RD outp   | out                 |                   |                                       |        |  |  |

|                                                  |     | P23: SIO4 dat                                              | e I/O/parallel in         | terface WR out    | out                 |                   |                                       |        |  |  |

|                                                  |     | P24: SIO4 cloo                                             |                           |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P25: UART2 ti                                              | ansmit                    |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P26: UART2 r                                               | eceive                    |                   |                     |                   |                                       |        |  |  |

|                                                  |     | P27: D+ 1.5kΩ                                              |                           | r connect pin     |                     |                   |                                       |        |  |  |

|                                                  |     | Interrupt ackno                                            | owledge type              |                   | 1                   |                   | · · · · · · · · · · · · · · · · · · · |        |  |  |

|                                                  |     |                                                            | Rising                    | Falling           | Rising &<br>Falling | H level           | L level                               |        |  |  |

|                                                  |     | INT4                                                       | enable                    | enable            | enable              | disable           | disable                               |        |  |  |

|                                                  |     | INT5                                                       | enable                    | enable            | enable              | disable           | disable                               |        |  |  |

|                                                  |     |                                                            |                           | onabio            | onabio              | alcabic           |                                       |        |  |  |

Continued on next page.

| Pin Name   | I/O        |                                             |                                                                                                                           | D                 | escription        |                  |         | Option |

|------------|------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|---------|--------|

| Port 3     | I/O        | • 5-bit I/O port                            |                                                                                                                           |                   |                   |                  |         | Yes    |

| P30 to P34 |            | • I/O specifiable in 1-bit units            |                                                                                                                           |                   |                   |                  |         |        |

|            |            | Pull-up resist                              | ors can be turne                                                                                                          | ed on and off in  | 1-bit units.      |                  |         |        |

|            |            | Pin functions                               |                                                                                                                           |                   |                   |                  |         |        |

|            |            | P34: USB inte                               | erface PLL filter                                                                                                         | pin (see Fig.5)   |                   |                  |         |        |

|            |            |                                             | gger pins: DBG                                                                                                            | P0 to DBGP2 (     | P30 to P32)       |                  |         |        |

| Port 7     | I/O        | 4-bit I/O port                              |                                                                                                                           |                   |                   |                  |         | No     |

| P70 to P73 |            | -                                           | I/O specifiable in 1-bit units                                                                                            |                   |                   |                  |         |        |

|            |            | -                                           | ors can be turne                                                                                                          | ed on and off in  | 1-bit units.      |                  |         |        |

|            |            | Pin functions                               |                                                                                                                           |                   | , .               |                  | ,       |        |

|            |            | -                                           |                                                                                                                           | -                 | apture input/wat  | tchdog timer ou  | tput/   |        |

|            |            |                                             | Ω pull-up resist                                                                                                          | •                 | antura input      |                  |         |        |

|            |            | -                                           |                                                                                                                           | input/timer 0H o  | ent input/timer ( |                  | 1       |        |

|            |            | -                                           | ed clock count                                                                                                            | -                 |                   |                  | 1       |        |

|            |            |                                             |                                                                                                                           | -                 | ent input/timer 0 | H capture input/ |         |        |

|            |            |                                             | P73: INT3 input (with noise filter)/timer 0 event input/timer 0H capture input/<br>infrared remote control receiver input |                   |                   |                  |         |        |

|            |            | AD converter input port: AN8(P70), AN9(P71) |                                                                                                                           |                   |                   |                  |         |        |

|            |            | Interrupt acknowledge type                  |                                                                                                                           |                   |                   |                  |         |        |

|            |            |                                             | iemeage type                                                                                                              |                   | Rising &          |                  |         |        |

|            |            |                                             | Rising                                                                                                                    | Falling           | Falling           | H level          | L level |        |

|            |            | INT0                                        | enable                                                                                                                    | enable            | disable           | enable           | enable  |        |

|            |            | INT1                                        | enable                                                                                                                    | enable            | disable           | enable           | enable  |        |

|            |            | INT2                                        | enable                                                                                                                    | enable            | enable            | disable          | disable |        |

|            |            | INT3                                        | enable                                                                                                                    | enable            | enable            | disable          | disable |        |

|            |            |                                             |                                                                                                                           |                   |                   |                  | 11      |        |

| PWM0       | I/O        | • PWM0 and P                                | WM1 output po                                                                                                             | rt                |                   |                  |         | No     |

| PWM1       |            | General-purp                                | ose input port                                                                                                            |                   |                   |                  |         |        |

| D-         | I/O        | • USB data I/O                              | pin D-                                                                                                                    |                   |                   |                  |         | No     |

|            |            | General-purp                                | ose I/O port                                                                                                              |                   |                   |                  |         |        |

| D+         | I/O        | • USB data I/O                              | pin D+                                                                                                                    |                   |                   |                  |         | No     |

|            |            | General-purp                                | ose I/O port                                                                                                              |                   |                   |                  |         |        |

| RES        | Input      | Reset pin                                   |                                                                                                                           |                   |                   |                  |         | No     |

| XT1        | Input      | • 32.768kHz cr                              | ystal oscillator i                                                                                                        | nput pin          |                   |                  |         | No     |

|            |            | Pin functions                               |                                                                                                                           |                   |                   |                  |         |        |

|            |            | General-purpose input port                  |                                                                                                                           |                   |                   |                  |         |        |

|            |            | AD converter input port: AN10               |                                                                                                                           |                   |                   |                  |         |        |

|            |            | Must be conn                                | ected to V <sub>DD</sub> 1                                                                                                | if not to be used | d.                |                  |         |        |

| XT2        | I/O        | -                                           | stal oscillator ou                                                                                                        | utput pin         |                   |                  |         | No     |

|            |            | Pin functions                               |                                                                                                                           |                   |                   |                  |         |        |

|            |            | General-purp                                | •                                                                                                                         |                   |                   |                  |         |        |

|            |            |                                             | input port: AN1                                                                                                           |                   |                   |                  |         |        |

|            | <u> </u> . |                                             |                                                                                                                           | d kept open if n  | ot to be used.    |                  |         |        |

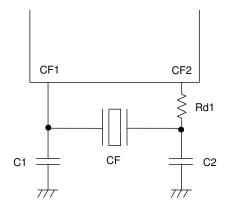

| CF1        | Input      | Ceramic reson                               | ator input pin                                                                                                            |                   |                   |                  |         | No     |

| CF2        | Output     | Ceramic reson                               | ator output pin                                                                                                           |                   |                   |                  |         | No     |

#### **Port Output Types**

The table below lists the types of port outputs and the presence/absence of a pull-up resistor. Data can be read into any input port even if it is in the output mode.

| Port Name                | Option Selected<br>in Units of | Option Type | Output Type                                                                                           | Pull-up Resistor      |

|--------------------------|--------------------------------|-------------|-------------------------------------------------------------------------------------------------------|-----------------------|

| P00 to P07               | 1 bit                          | 1           | CMOS                                                                                                  | Programmable (Note 1) |

|                          |                                | 2           | Nch-open drain                                                                                        | No                    |

| P10 to P17               | 1 bit                          | 1           | CMOS                                                                                                  | Programmable          |

| P20 to P27<br>P30 to P34 |                                | 2           | Nch-open drain                                                                                        | Programmable          |

| P70                      | -                              | No          | Nch-open drain                                                                                        | Programmable          |

| P71 to P73               | -                              | No          | CMOS                                                                                                  | Programmable          |

| PWM0, PWM1               | -                              | No          | CMOS                                                                                                  | No                    |

| D+, D-                   | -                              | No          | CMOS                                                                                                  | No                    |

| XT1                      | -                              | No          | Input only                                                                                            | No                    |

| XT2                      | -                              | No          | 32.768kHz crystal oscillator output<br>(N channel open drain when in general-<br>purpose output mode) | No                    |

Note 1: Programmable pull-up resistors for port 0 are controlled in 4-bit units (P00 to 03, P04 to 07).

#### **User Option Table**

| Option Name       | Option to be Applied on | Flash-ROM<br>Version | Option Selected in Units of | Option Selection |

|-------------------|-------------------------|----------------------|-----------------------------|------------------|

|                   | D00 to D07              | 0                    | 4 64                        | CMOS             |

|                   | P00 to P07              | 0                    | 1 bit                       | Nch-open drain   |

|                   | P10 to P17              | 0                    | 1 bit                       | CMOS             |

| Dest extend to be | P10 10 P17              | 0                    | T DIL                       | Nch-open drain   |

| Port output type  | D00 to D07              | 0                    | 4 64                        | CMOS             |

|                   | P20 to P27              | 0                    | 1 bit                       | Nch-open drain   |

|                   |                         |                      | CMOS                        |                  |

|                   | P30 to P34 O 1 bit      | Nch-open drain       |                             |                  |

| Program start     |                         | 0                    |                             | 00000h           |

| address           | -                       | 0                    | -                           | 0FE00h           |

|                   | USB Regulator           | 0                    |                             | USE              |

|                   |                         | 0                    | -                           | NONUSE           |

|                   | USB Regulator           | 0                    |                             | USE              |

| USB Regulator     | (at HOLD mode)          | 0                    | -                           | NONUSE           |

|                   | USB Regulator           | 0                    |                             | USE              |

|                   | (at HALT mode)          | 0                    | -                           | NONUSE           |

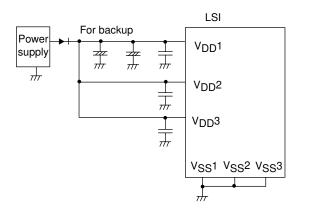

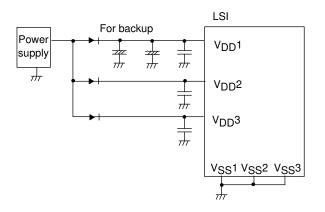

#### **Power Pin Treatment**

Connect the IC as shown below to minimize the noise input to the  $V_{DD1}$  pin. Be sure to electrically short the  $V_{SS1}$ ,  $V_{SS2}$ , and  $V_{SS3}$  pins.

Example 1: When the microcontroller is in the backup state in the HOLD mode, the power to sustain the high level of output ports is supplied by their backup capacitors.

Example 2: The high level output at ports is not sustained and unstable in the HOLD backup mode.

#### **USB Reference Power Option**

When a voltage 4.5 to 5.5V is supplied to  $V_{DD1}$  and the internal USB reference voltage circuit is activated, the reference voltage for USB port output is generated. The active/inactive state of reference voltage circuit can be switched by the option select. The procedure for marking the option selection is described below.

|                           |                            | (1)    | (2)      | (3)      | (4)      |

|---------------------------|----------------------------|--------|----------|----------|----------|

| Option select             | USB Regulator              | USE    | USE      | USE      | NONUSE   |

|                           | USB Regulator at HOLD mode | USE    | NONUSE   | NONUSE   | NONUSE   |

|                           | USB Regulator at HALT mode | USE    | NONUSE   | USE      | NONUSE   |

| Reference voltage circuit | Normal state               | active | active   | active   | inactive |

| state                     | HOLD mode                  | active | inactive | inactive | inactive |

|                           | HALT mode                  | active | inactive | active   | inactive |

• When the USB reference voltage circuit is made inactive, the level of the reference voltage for USB port output is equal to V<sub>DD</sub>1.

- Selection (2) or (3) can be used to set the reference voltage circuit inactive in HOLD or HALT mode.

- When the reference voltage circuit is activated, the current drain increase by approximately 100µA compared with when the reference voltage circuit is inactive.

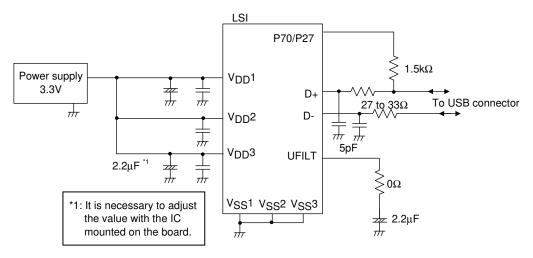

Example 1: VDD1=VDD2=3.3V

- Inactivating the reference voltage circuit (selection (4)).

- Connecting VDD3 to VDD1 and VDD2.

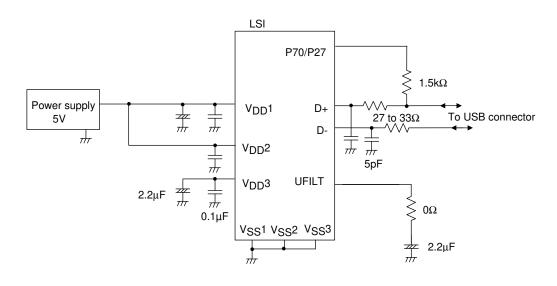

Example 2: VDD1=VDD2=5.0V

- Activating the reference voltage circuit (selection (1)).

- Isolating VDD3 from VDD1 and VDD2, and connecting capacitor between VDD3 and VSS.

|                           | Parameter                    | Symbol              | Pin/Remarks                                                                              | Conditions                                                    |                     |      | Speci | fication             | 1    |

|---------------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------|------|-------|----------------------|------|

|                           | י מומווופופו                 | -                   |                                                                                          |                                                               | V <sub>DD</sub> [V] | min  | typ   | max                  | unit |

|                           | ximum supply<br>tage         | V <sub>DD</sub> max | V <sub>DD</sub> 1, V <sub>DD</sub> 2, V <sub>DD</sub> 3                                  | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3         |                     | -0.3 |       | +6.5                 |      |

| np                        | ut voltage                   | V <sub>I</sub> (1)  | XT1, CF1                                                                                 |                                                               |                     | -0.3 |       | V <sub>DD</sub> +0.3 | V    |

|                           | out/output<br>tage           | V <sub>IO</sub> (1) | Ports 0, 1, 2, 3, 7<br>PWM0, PWM1, XT2                                                   |                                                               |                     | -0.3 |       | V <sub>DD</sub> +0.3 |      |

|                           | Peak output<br>current       | IOPH(1)             | Ports 0, 1, 2                                                                            | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -10  |       |                      |      |

|                           |                              | IOPH(2)             | PWM0, PWM1                                                                               | Per 1 applicable pin                                          |                     | -20  |       |                      |      |

|                           |                              | IOPH(3)             | PH(3) Port 3 • When CMOS output<br>P71 to P73 type is selected<br>• Per 1 applicable pin |                                                               |                     | -5   |       |                      |      |

| current                   | Average<br>output<br>current | IOMH(1)             | Ports 0, 1, 2                                                                            | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -7.5 |       |                      |      |

| tput                      | (Note 1-1)                   | IOMH(2)             | PWM0, PWM1                                                                               | Per 1 applicable pin                                          |                     | -15  |       |                      |      |

| High level output current |                              | IOMH(3)             | Port 3<br>P71 to P73                                                                     | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -3   |       |                      |      |

| Т                         | Total output                 | ΣIOAH(1)            | Ports 0, 2                                                                               | Total of all applicable pins                                  |                     | -25  |       |                      |      |

|                           | current                      | ΣIOAH(2)            | Port 1<br>PWM0, PWM1                                                                     | Total of all applicable pins                                  |                     | -25  |       |                      |      |

|                           |                              | ΣIOAH(3)            | Ports 0, 1, 2<br>PWM0, PWM1                                                              | Total of all applicable pins                                  |                     | -45  |       |                      |      |

|                           |                              | ΣIOAH(4)            | Port 3<br>P71 to P73                                                                     | Total of all applicable pins                                  |                     | -10  |       |                      | mA   |

|                           |                              | ΣIOAH(5)            | D+, D-                                                                                   | Total of all applicable pins                                  |                     | -25  |       |                      |      |

|                           | Peak output<br>current       | IOPL(1)             | P02 to P07<br>Ports 1, 2<br>PWM0, PWM1                                                   | Per 1 applicable pin                                          |                     |      |       | 20                   |      |

|                           |                              | IOPL(2)             | P00, P01                                                                                 | Per 1 applicable pin                                          |                     |      |       | 30                   |      |

|                           |                              | IOPL(3)             | Ports 3, 7, XT2                                                                          | Per 1 applicable pin                                          |                     |      |       | 10                   |      |

| tput current              | Average<br>output<br>current | IOML(1)             | P02 to P07<br>Ports 1, 2<br>PWM0, PWM1                                                   | Per 1 applicable pin                                          |                     |      |       | 15                   |      |

| outp                      | (Note 1-1)                   | IOML(2)             | P00, P01                                                                                 | Per 1 applicable pin                                          |                     |      |       | 20                   |      |

| svel                      |                              | IOML(3)             | Ports 3, 7, XT2                                                                          | Per 1 applicable pin                                          |                     |      |       | 7.5                  |      |

| Low level ou              | Total output                 | $\Sigma IOAL(1)$    | Ports 0, 2                                                                               | Total of all applicable pins                                  |                     |      |       | 45                   |      |

| Ľ                         | current                      | ΣIOAL(2)            | Port 1<br>PWM0, PWM1                                                                     | Total of all applicable pins                                  |                     |      |       | 45                   |      |

|                           |                              | ΣIOAL(3)            | Ports 0, 1, 2<br>PWM0, PWM1                                                              | Total of all applicable pins                                  |                     |      |       | 80                   |      |

|                           |                              | ΣIOAL(4)            | Ports 3, 7, XT2                                                                          | Total of all applicable pins                                  |                     |      |       | 15                   |      |

|                           |                              | ΣIOAL(5)            | D+, D-                                                                                   | Total of all applicable pins                                  |                     |      |       | 25                   |      |

|                           | owable power<br>sipation     | Pd max              | SQFP48(7×7)                                                                              | Ta=-30 to +70°C                                               |                     |      |       | 190                  | mV   |

|                           | erating ambient<br>mperature | Topr                |                                                                                          |                                                               |                     | -30  |       | +70                  | °C   |

|                           | orage ambient<br>nperature   | Tstg                |                                                                                          |                                                               |                     | -55  | _     | +125                 | - (  |

#### **Absolute Maximum Ratings** at $Ta = 25^{\circ}C$ , $V_{SS}1 = V_{SS}2 = V_{SS}3 = 0V$

Note 1-1: The mean output current is a mean value measured over 100ms.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

| Parameter                              | Symbol              | Pin/Remarks                                                                       | Conditions                                                                                                                             | r                   |                            | Specific | ation                       |      |

|----------------------------------------|---------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------|----------|-----------------------------|------|

| i didilletei                           | Gymbol              | TIMTemarks                                                                        | Conditions                                                                                                                             | V <sub>DD</sub> [V] | min                        | typ      | max                         | unit |

| Operating                              | V <sub>DD</sub> (1) | $V_{DD}1=V_{DD}2=V_{DD}3$                                                         | 0.183µs≤tCYC≤200µs                                                                                                                     |                     | 3.0                        |          | 5.5                         |      |

| supply voltage<br>(Note 2-1)           |                     |                                                                                   | 0.183µs≤tCYC≤0.383µs<br>USB circuit active                                                                                             |                     | 3.0                        |          | 5.5                         |      |

|                                        |                     |                                                                                   | 0.367µs≤tCYC≤200µs Except<br>for onboard programming                                                                                   |                     | 2.7                        |          | 5.5                         |      |

| Memory<br>sustaining<br>supply voltage | VHD                 | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3                             | RAM and register contents sustained in HOLD mode.                                                                                      |                     | 2.0                        |          | 5.5                         |      |

| High level<br>input voltage            | V <sub>IH</sub> (1) | Ports 0, 1, 2, 3<br>P71 to P73<br>P70 port input/<br>interrupt side<br>PWM0, PWM1 |                                                                                                                                        | 2.7 to 5.5          | 0.3V <sub>DD</sub><br>+0.7 |          | V <sub>DD</sub>             |      |

|                                        | V <sub>IH</sub> (2) | Port 70 watchdog<br>timer side                                                    |                                                                                                                                        | 2.7 to 5.5          | 0.9V <sub>DD</sub>         |          | V <sub>DD</sub>             | V    |

|                                        | V <sub>IH</sub> (3) | XT1, XT2, CF1, RES                                                                |                                                                                                                                        | 2.7 to 5.5          | 0.75V <sub>DD</sub>        |          | V <sub>DD</sub>             |      |

| Low level<br>input voltage             | V <sub>IL</sub> (1) | Ports 1, 2, 3<br>P71 to P73                                                       |                                                                                                                                        | 4.0 to 5.5          | V <sub>SS</sub>            |          | 0.1V <sub>DD</sub><br>+0.4  |      |

|                                        | V <sub>IL</sub> (2) | P70 port input/<br>interrupt side                                                 |                                                                                                                                        | 2.7 to 4.0          | V <sub>SS</sub>            |          | 0.2V <sub>DD</sub>          |      |

|                                        | V <sub>IL</sub> (3) | Port 0<br>PWM0, PWM1                                                              |                                                                                                                                        | 4.0 to 5.5          | V <sub>SS</sub>            |          | 0.15V <sub>DD</sub><br>+0.4 |      |

|                                        | V <sub>IL</sub> (4) |                                                                                   |                                                                                                                                        | 2.7 to 4.0          | V <sub>SS</sub>            |          | 0.2V <sub>DD</sub>          |      |

|                                        | V <sub>IL</sub> (5) | Port 70 watchdog<br>timer side                                                    |                                                                                                                                        | 2.7 to 5.5          | V <sub>SS</sub>            |          | 0.8V <sub>DD</sub><br>-1.0  |      |

|                                        | V <sub>IL</sub> (6) | XT1, XT2, CF1, RES                                                                |                                                                                                                                        | 2.7 to 5.5          | V <sub>SS</sub>            |          | 0.25V <sub>DD</sub>         |      |

| Instruction                            | tCYC                |                                                                                   |                                                                                                                                        | 3.0 to 5.5          | 0.183                      |          | 200                         |      |

| cycle time                             |                     |                                                                                   | USB circuit active                                                                                                                     | 3.0 to 5.5          | 0.183                      |          | 0.383                       |      |

| (Note 2-2)                             |                     |                                                                                   | Except for onboard programming                                                                                                         | 2.7 to 5.5          | 0.367                      |          | 200                         | μs   |

| External<br>system clock<br>frequency  | FEXCF(1)            | CF1                                                                               | CF2 pin open     System clock frequency     division ratio=1/1     External system clock duty     =50±5%                               | 3.0 to 5.5          | 0.1                        |          | 16                          |      |

|                                        |                     |                                                                                   | <ul> <li>CF2 pin open</li> <li>System clock frequency<br/>division ratio=1/1</li> <li>External system clock duty<br/>=50±5%</li> </ul> | 2.7 to 5.5          | 0.1                        |          | 8                           | MH   |

| Oscillation<br>frequency               | FmCF(1)             | CF1, CF2                                                                          | 16MHz ceramic oscillation<br>See Fig. 1.                                                                                               | 3.0 to 5.5          |                            | 16       |                             |      |

| range<br>(Note 2-3)                    | FmCF(2)             | CF1, CF2                                                                          | 8MHz ceramic oscillation<br>See Fig. 1.                                                                                                | 2.7 to 5.5          |                            | 8        |                             | MHz  |

| ,                                      | FmRC                |                                                                                   | Internal RC oscillation                                                                                                                | 2.7 to 5.5          | 0.3                        | 1.0      | 2.0                         | 1    |

|                                        | FmSLRC              |                                                                                   | Internal low-speed RC oscillation                                                                                                      | 2.7 to 5.5          | 15                         | 30       | 60                          |      |

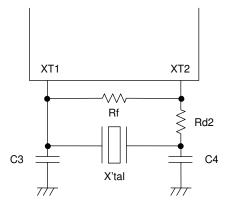

|                                        | FsX'tal             | XT1, XT2                                                                          | 32.768kHz crystal oscillation<br>See Fig. 2.                                                                                           | 2.7 to 5.5          |                            | 32.768   |                             | kH2  |

#### Allowable Operating Conditions at Ta = $-30^{\circ}$ C to $+70^{\circ}$ C, V<sub>SS</sub>1 = V<sub>SS</sub>2 = V<sub>SS</sub>3 = 0V

See Fig. 2.

2.7 to 5.5

32.768

Note 2-1: VDD must be held greater than or equal to 3.0V in the flash ROM onboard programming mode.

Note 2-2: Relationship between tCYC and oscillation frequency is 3/FmCF at a division ratio of 1/1 and 6/FmCF at a division ratio of 1/2.

Note 2-3: See Tables 1 and 2 for the oscillation constants.

## **Electrical Characteristics** at Ta = $-30^{\circ}$ C to $+70^{\circ}$ C, V<sub>SS</sub>1 = V<sub>SS</sub>2 = V<sub>SS</sub>3 = 0V

| Parameter                   | Symbol              | Pin/Remarks                                               | Conditions                                                                                           |                     |                      | Specifica          | tion |      |

|-----------------------------|---------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------|----------------------|--------------------|------|------|

| Falailletei                 | Symbol              | FINHEINARS                                                | Conditions                                                                                           | V <sub>DD</sub> [V] | min                  | typ                | max  | unit |

| High level input<br>current | I <sub>IH</sub> (1) | Ports 0, 1, 2, 3<br>Port 7<br>RES<br>PWM0, PWM1<br>D+, D- | Output disabled<br>Pull-up resistor off<br>VIN=VDD<br>(Including output Tr's off<br>leakage current) | 2.7 to 5.5          |                      |                    | 1    |      |

|                             | I <sub>IH</sub> (2) | XT1, XT2                                                  | For input port specification<br>VIN=VDD                                                              | 2.7 to 5.5          |                      |                    | 1    |      |

|                             | I <sub>IH</sub> (3) | CF1                                                       | V <sub>IN</sub> =V <sub>DD</sub>                                                                     | 2.7 to 5.5          |                      |                    | 15   |      |

| Low level input<br>current  | IIL(1)              | Ports 0, 1, 2, 3<br>Port 7<br>RES<br>PWM0, PWM1<br>D+, D- | Output disabled<br>Pull-up resistor off<br>VIN=VSS<br>(Including output Tr's off<br>leakage current) | 2.7 to 5.5          | -1                   |                    |      | μA   |

|                             | I <sub>IL</sub> (2) | XT1, XT2                                                  | For input port specification<br>VIN=VSS                                                              | 2.7 to 5.5          | -1                   |                    |      |      |

|                             | I <sub>IL</sub> (3) | CF1                                                       | V <sub>IN</sub> =V <sub>SS</sub>                                                                     | 2.7 to 5.5          | -15                  |                    |      |      |

| High level output           | V <sub>OH</sub> (1) | Ports 0, 1, 2, 3                                          | I <sub>OH</sub> =-1mA                                                                                | 4.5 to 5.5          | V <sub>DD</sub> -1   |                    |      |      |

| voltage                     | V <sub>OH</sub> (2) | P71 to P73                                                | I <sub>OH</sub> =-0.4mA                                                                              | 3.0 to 5.5          | V <sub>DD</sub> -0.4 |                    |      |      |

|                             | V <sub>OH</sub> (3) |                                                           | I <sub>OH</sub> =-0.2mA                                                                              | 2.7 to 5.5          | V <sub>DD</sub> -0.4 |                    |      |      |

|                             | V <sub>OH</sub> (4) | PWM0, PWM1<br>P05 (CK0 when                               | I <sub>OH</sub> =-10mA                                                                               | 4.5 to 5.5          | V <sub>DD</sub> -1.5 |                    |      |      |

|                             | V <sub>OH</sub> (5) | · ·                                                       | I <sub>OH</sub> =-1.6mA                                                                              | 3.0 to 5.5          | V <sub>DD</sub> -0.4 |                    |      |      |

|                             | V <sub>OH</sub> (6) | using system clock<br>output function)                    | I <sub>OH</sub> =-1mA                                                                                | 2.7 to 5.5          | V <sub>DD</sub> -0.4 |                    |      |      |

| Low level output            | V <sub>OL</sub> (1) | P00, P01                                                  | I <sub>OL</sub> =30mA                                                                                | 4.5 to 5.5          |                      |                    | 1.5  | v    |

| voltage                     | V <sub>OL</sub> (2) |                                                           | I <sub>OL</sub> =5mA                                                                                 | 3.0 to 5.5          |                      |                    | 0.4  | _    |

|                             | V <sub>OL</sub> (3) |                                                           | I <sub>OL</sub> =2.5mA                                                                               | 2.7 to 5.5          |                      |                    | 0.4  |      |

|                             | V <sub>OL</sub> (4) | Ports 0, 1, 2                                             | I <sub>OL</sub> =10mA                                                                                | 4.5 to 5.5          |                      |                    | 1.5  |      |

|                             | V <sub>OL</sub> (5) | PWM0, PWM1                                                | I <sub>OL</sub> =1.6mA                                                                               | 3.0 to 5.5          |                      |                    | 0.4  |      |

|                             | V <sub>OL</sub> (6) | XT2                                                       | I <sub>OL</sub> =1mA                                                                                 | 2.7 to 5.5          |                      |                    | 0.4  |      |

|                             | V <sub>OL</sub> (7) | Ports 3, 7                                                | I <sub>OL</sub> =1.6mA                                                                               | 3.0 to 5.5          |                      |                    | 0.4  |      |

|                             | V <sub>OL</sub> (8) |                                                           | I <sub>OL</sub> =1mA                                                                                 | 2.7 to 5.5          |                      |                    | 0.4  |      |

| Pull-up resistance          | Rpu(1)              | Ports 0, 1, 2, 3                                          | V <sub>OH</sub> =0.9V <sub>DD</sub>                                                                  | 4.5 to 5.5          | 15                   | 35                 | 80   | kΩ   |